# LIN Slave Controller for Switches

Datasheet

| 1   | 14.1         | Entering Sleep Mode by API                                | 65 |

|-----|--------------|-----------------------------------------------------------|----|

| 1   | 14.2         | Wake Up System                                            | 65 |

|     | 14.2         |                                                           |    |

|     | 14.2<br>14.2 |                                                           |    |

| 4-  |              | ·                                                         |    |

| 15. |              | rmal Shutdown                                             |    |

| 16. | Syst         | em behaviour                                              |    |

| 1   | 16.1         | Reset behaviour                                           |    |

| 1   | 16.2         | Initialising the System                                   | 67 |

| 17. | RON          | /I Patches                                                | 69 |

| 1   | 17.1         | Principle of operation                                    | 69 |

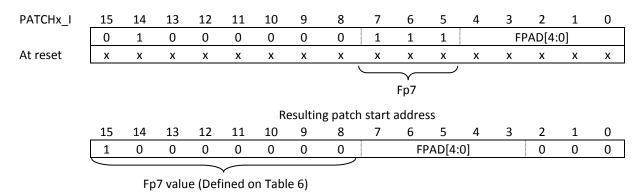

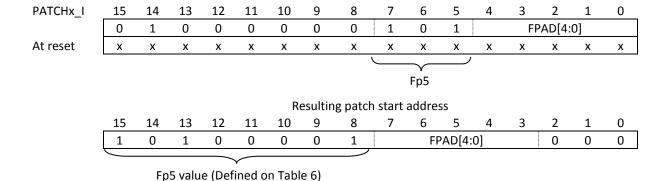

| 1   | 17.2         | Patch start address                                       | 70 |

| 1   | 17.3         | Patch jump instruction                                    |    |

| 18. | Арр          | lication Hints                                            | 72 |

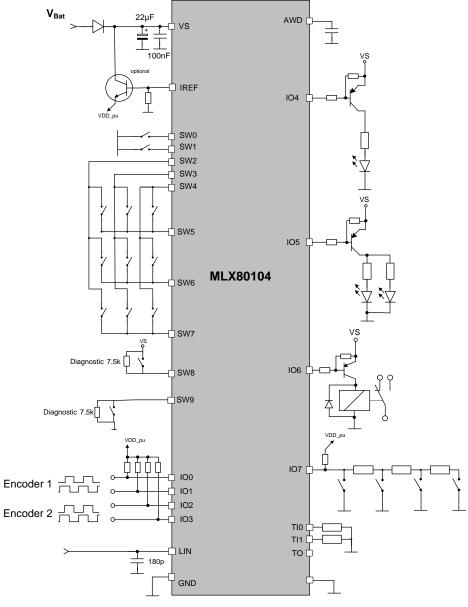

| 1   | 18.1         | Application Examples                                      | 72 |

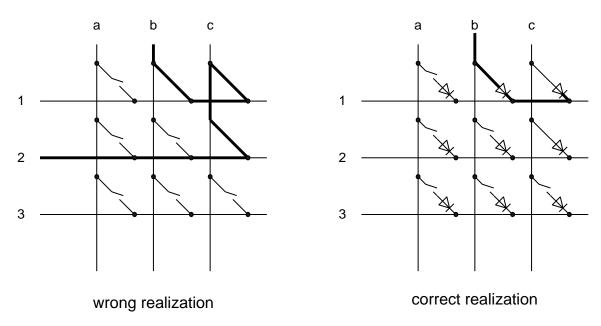

|     | 18.1         | 1. Switch Matrix Hints                                    | 73 |

| 19. | Soft         | ware Development                                          | 75 |

| 1   | 19.1         | UniROM (80104 only)                                       | 75 |

| 20. | Prog         | gramming Interface                                        | 77 |

| 2   | 20.1         | Characteristics for the interface pins                    |    |

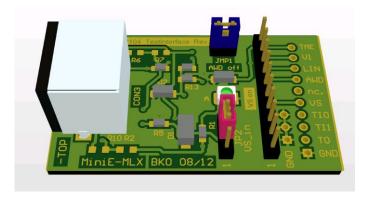

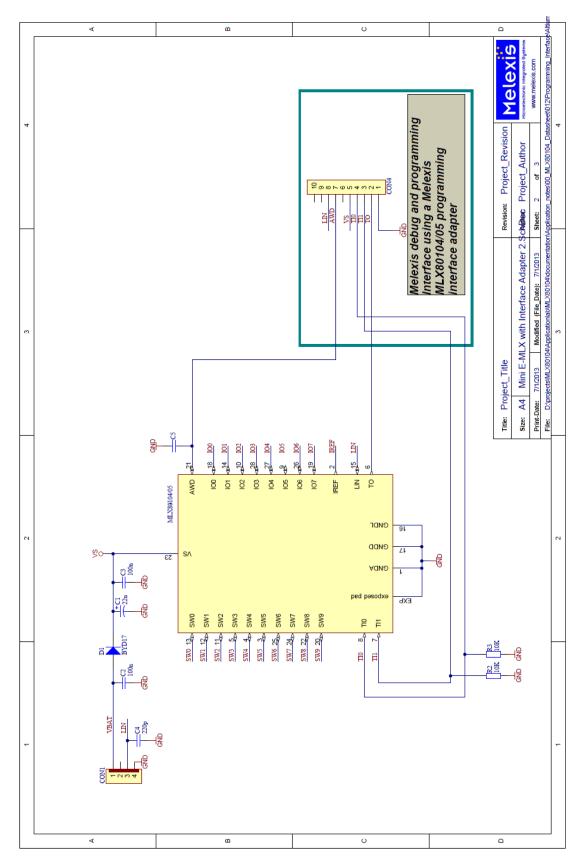

| 2   | 20.2         | Melexis Mini E-Mlx emulator                               |    |

| 2   | 20.3         | Melexis Mini E-Mlx emulator and Melexis interface adapter |    |

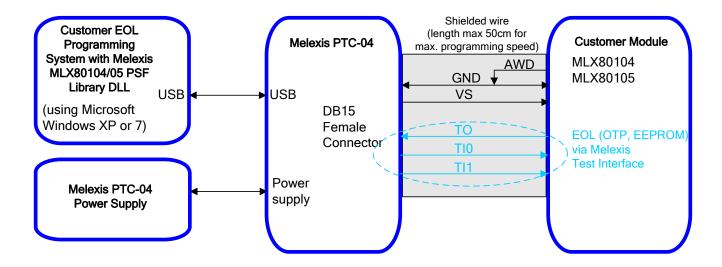

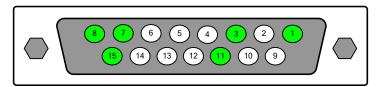

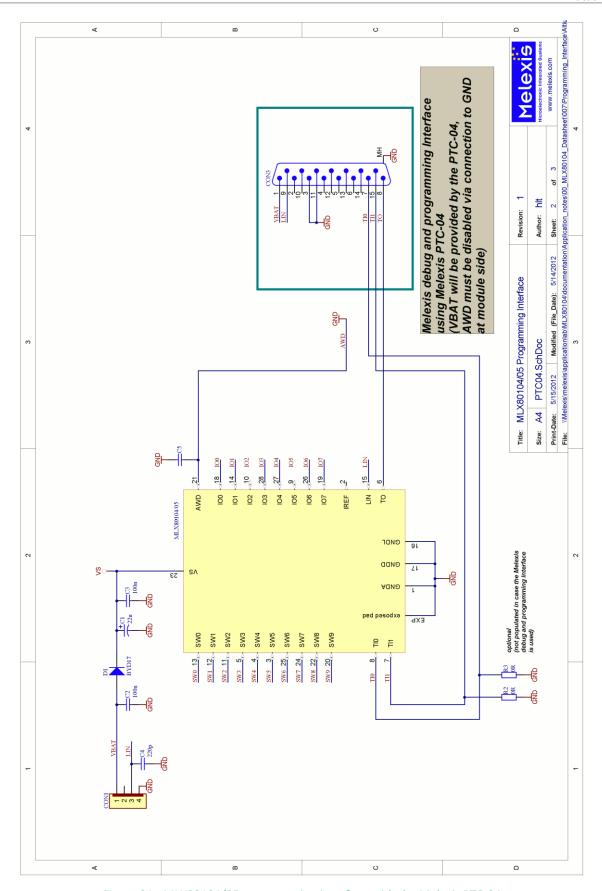

| 2   | 20.4<br>20.4 | Melexis Programmer PTC-04                                 |    |

| 2   | 20.5         | Third party programmer                                    |    |

| 21. | Ope          | rating under Disturbance                                  | 87 |

| 2   | 21.1         | Loss of battery                                           | 87 |

|     | 21.2         | Loss of Ground                                            |    |

| 2   | 21.3         | Short circuit to battery                                  | 87 |

| 2   | 21.4         | Short circuit to ground                                   | 87 |

| 2   | 21.5         | Thermal overload                                          | 87 |

| 2   | 21.6         | Undervoltage Vs                                           | 87 |

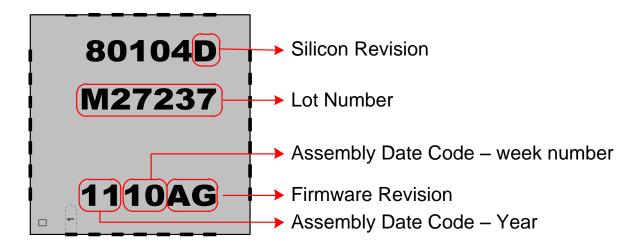

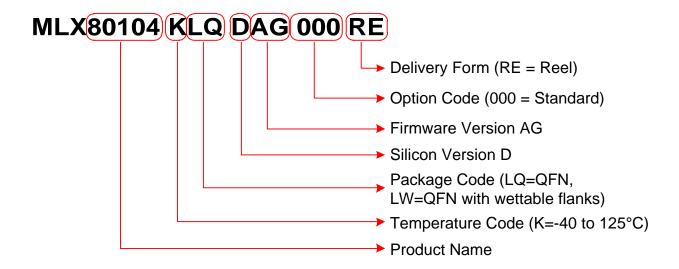

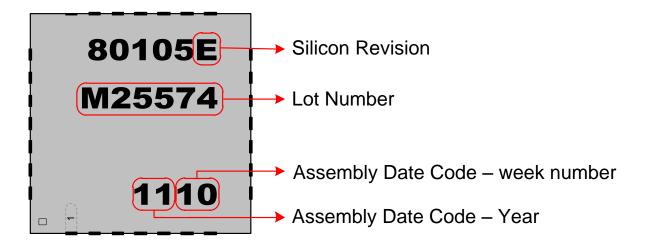

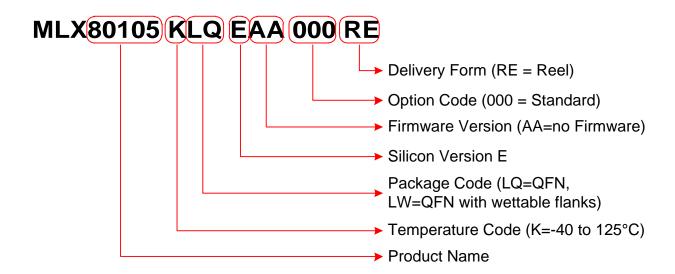

| 22. | Mar          | king/Order Code                                           | 88 |

| 2   | 22.1         | Marking MLX80104                                          | 88 |

| 2   | 22.2         | Order Code MLX80104                                       | 88 |

| 2   | 22.3         | Marking MLX80105                                          | 89 |

| 2   | 22.4         | Order Code MLX80105                                       | 89 |

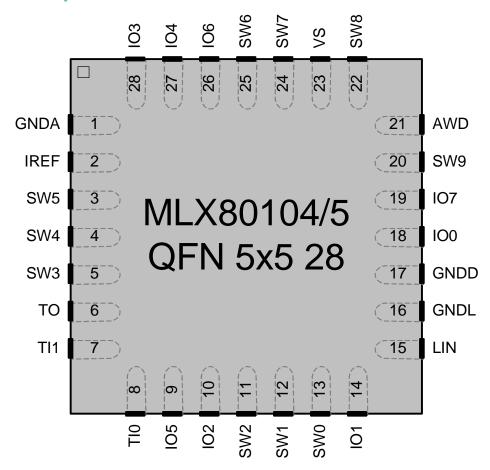

| 23. | Pin I        | Description                                               | 90 |

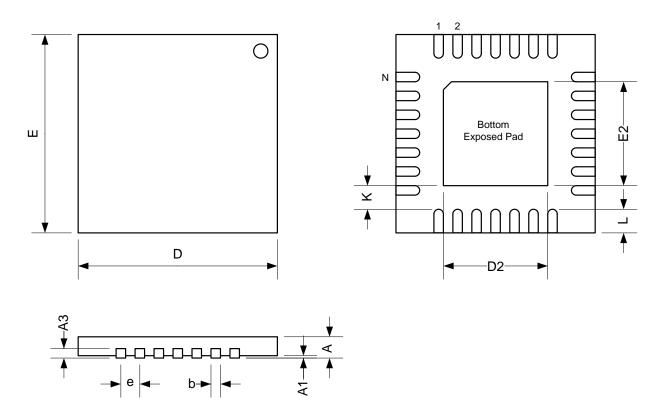

| 24. | Med          | hanical Specification                                     | 92 |

# LIN Slave Controller for Switches

Datasheet

| 25. Land Pattern Recommendations |                                                                                               |             |  |  |  |  |

|----------------------------------|-----------------------------------------------------------------------------------------------|-------------|--|--|--|--|

| 26.                              | ESD/EMC Remarks                                                                               | 94          |  |  |  |  |

| 2                                | 6.1 ESD/EMC Recommendations for the MLX80104/5                                                | 94          |  |  |  |  |

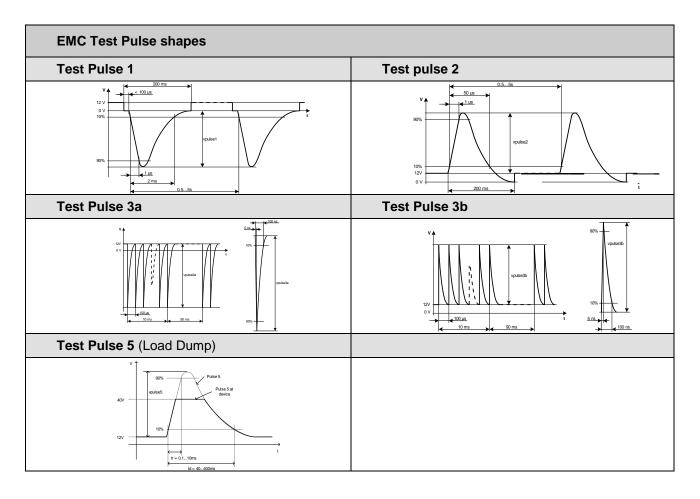

| 2                                | 6.2 Automotive Qualification Test Pulses                                                      |             |  |  |  |  |

|                                  | •                                                                                             |             |  |  |  |  |

| 20                               | 6.3 EMC Test pulse definition                                                                 | 95          |  |  |  |  |

| 27.                              | References                                                                                    | 96          |  |  |  |  |

| 28.                              | List of Abbreviations                                                                         | 96          |  |  |  |  |

| 29.                              | Revision History                                                                              | 97          |  |  |  |  |

|                                  | ·                                                                                             |             |  |  |  |  |

| 30.                              | Standard information regarding manufacturability of Melexis products with different soldering | orocesses99 |  |  |  |  |

| 31.                              | Disclaimer                                                                                    | 100         |  |  |  |  |

|                                  |                                                                                               |             |  |  |  |  |

|                                  |                                                                                               |             |  |  |  |  |

| Lis                              | st of Figures                                                                                 |             |  |  |  |  |

|                                  |                                                                                               |             |  |  |  |  |

|                                  |                                                                                               |             |  |  |  |  |

|                                  | re 1 - Block Diagram                                                                          |             |  |  |  |  |

|                                  | IRE 2 - BLOCK DIAGRAM OF MULAN CPU                                                            |             |  |  |  |  |

|                                  | IRE 3 - CPU INTERLEAVING                                                                      |             |  |  |  |  |

|                                  | IRE 4 - EEPROM READ                                                                           |             |  |  |  |  |

|                                  | IRE 5 - COMMON PIN STRUCTURE SWX AND IOX                                                      |             |  |  |  |  |

|                                  | IRE 6 - VOLTAGE DEPENDENCY OF THE SWITCH CURRENT                                              |             |  |  |  |  |

|                                  | IRE 7 - VOLTAGE DROPS EXTERNAL LS SWITCH                                                      |             |  |  |  |  |

|                                  | ire 8 - Voltage drops switch matrix                                                           |             |  |  |  |  |

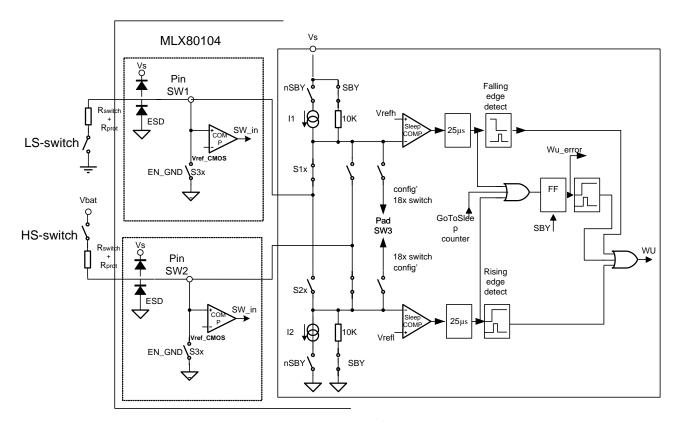

|                                  | IRE 10 - WAKE UP DETECTION FOR SWITCH INPUTS                                                  |             |  |  |  |  |

|                                  | IRE 11 - STRUCTURE OF SWX PINS                                                                |             |  |  |  |  |

|                                  | IRE 12 - STRUCTURE OF 5 WA FINS                                                               |             |  |  |  |  |

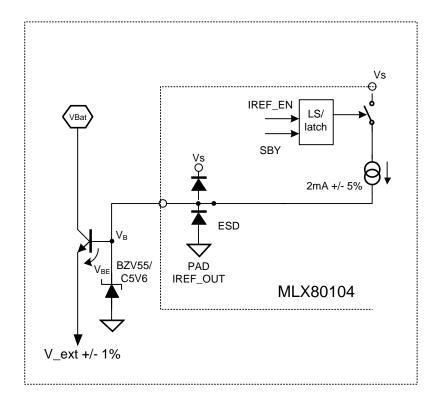

|                                  | IRE 13 - SAMPLE CIRCUITRY FOR IREF PIN                                                        |             |  |  |  |  |

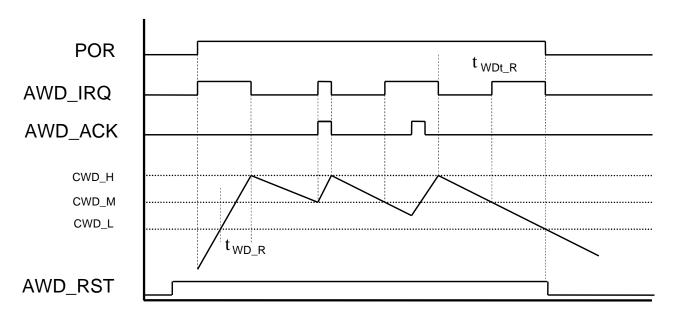

|                                  | IRE 14 - ANALOGUE WATCHDOG BEHAVIOUR                                                          |             |  |  |  |  |

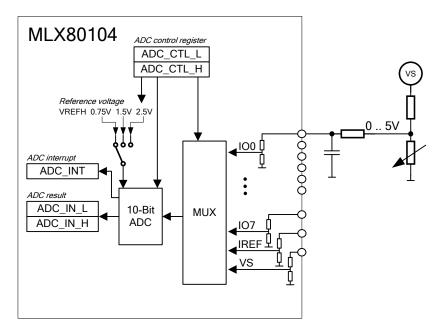

|                                  | IRE 15 - ADC COMPONENTS                                                                       |             |  |  |  |  |

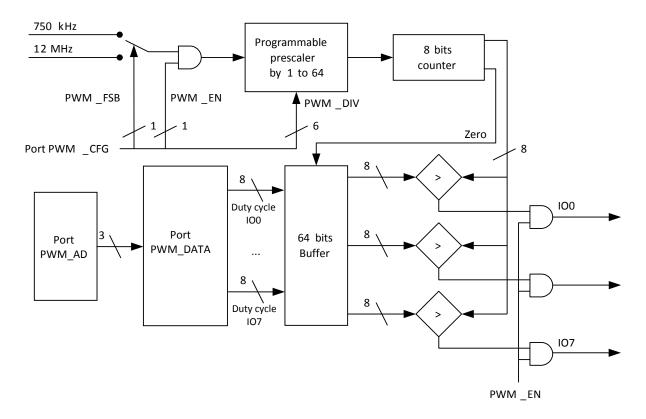

|                                  | IRE 16 - PWM UNIT                                                                             |             |  |  |  |  |

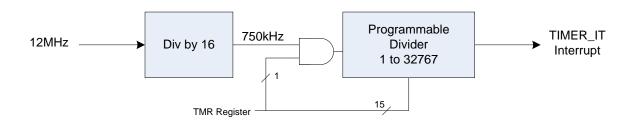

| FIGU                             | IRE 17 - BLOCK DIAGRAM OF TIMER                                                               | 60          |  |  |  |  |

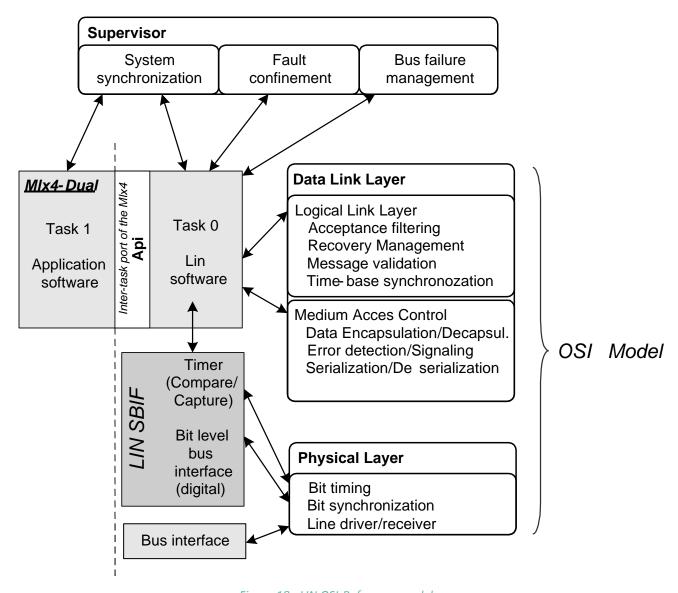

| Figu                             | IRE 18 - LIN OSI-REFERENCE MODEL                                                              | 61          |  |  |  |  |

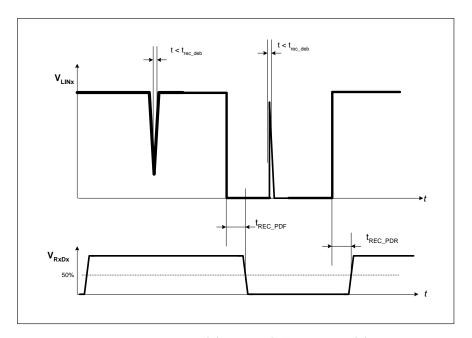

| FIGU                             | IRE 19 - RECEIVER DEBOUNCING & PROPAGATION DELAY                                              | 62          |  |  |  |  |

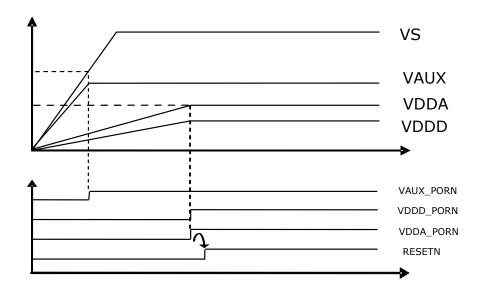

| FIGU                             | re 20 - Reset behaviour                                                                       | 67          |  |  |  |  |

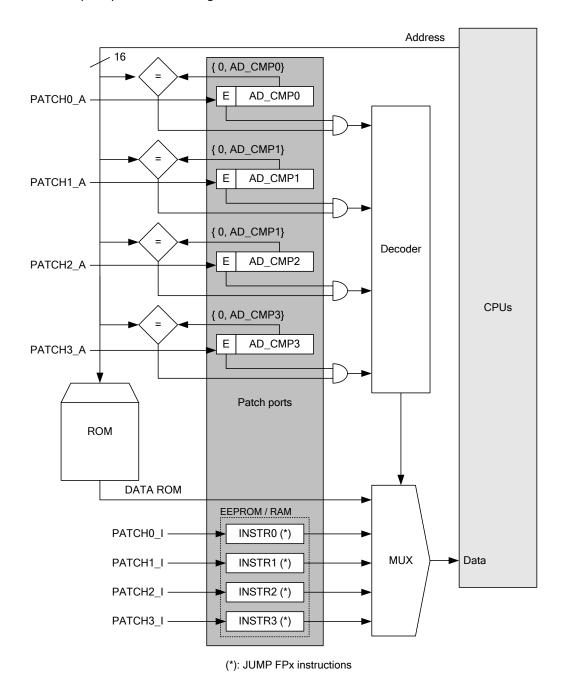

| FIGU                             | IRE 21 - PATCH HARDWARE                                                                       | 69          |  |  |  |  |

|                                  | IRE 22 - PATCH CODE IN EEPROM                                                                 |             |  |  |  |  |

|                                  | IRE 23 - PATCH CODE IN RAM                                                                    |             |  |  |  |  |

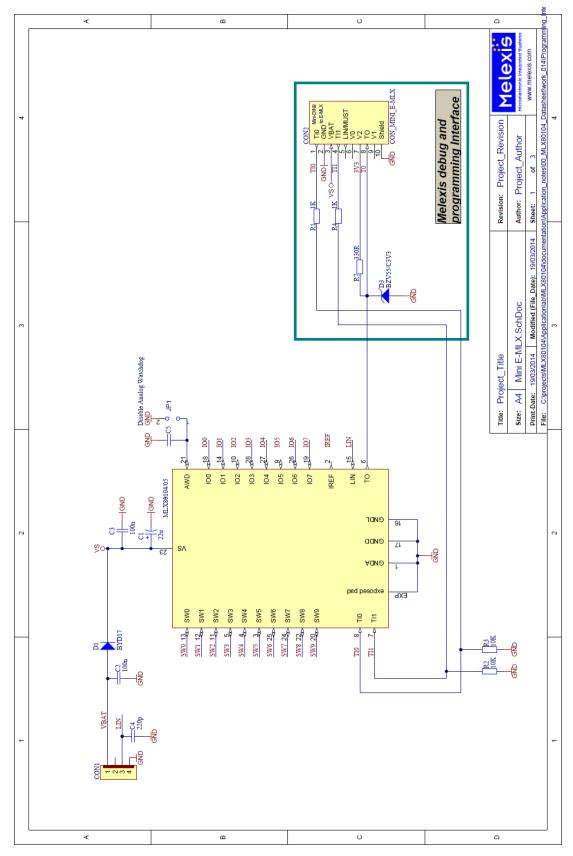

|                                  | IRE 24 - APPLICATION SCHEMATIC SAMPLE                                                         |             |  |  |  |  |

|                                  | IRE 25 - READING THE SWITCH MATRIX                                                            |             |  |  |  |  |

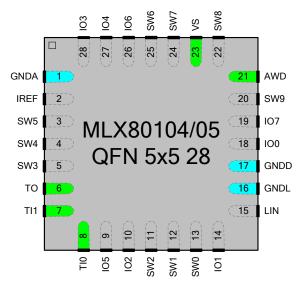

|                                  | IRE 26 - PIN OUT MLX80104/05 - TOP VIEW                                                       |             |  |  |  |  |

|                                  | IRE 27 - MLX80104/05 PROGRAMMING INTERFACE WITH THE MELEXIS MINI E-MLX EMULATOR               |             |  |  |  |  |

|                                  | IRE 28 - MELEXIS MLX80104/05 PROGRAMMING INTERFACE ADAPTER                                    |             |  |  |  |  |

| riGU                             | IRE 29 - MLX80104/05 PROGRAMMING INTERFACE WITH THE MELEXIS MINI E-MLX EMULATOR AND I         |             |  |  |  |  |

| Ercz                             | INTERFACE ADAPTER                                                                             |             |  |  |  |  |

|                                  | IRE 30 - CONNECTION DIAGRAM BETWEEN P1C-04 AND MLX80104/5                                     |             |  |  |  |  |

|                                  | IRE 31 - MLX80104/05 PROGRAMMING INTERFACE WITH THE MELEXIS PTC-04                            |             |  |  |  |  |

|                                  | INE 32 - PIN OUT IVILAOUTU4/J - TUP VIEW                                                      | 90<br>20    |  |  |  |  |

# LIN Slave Controller for Switches

Datasheet

# **List of Tables**

| Table 1 - Absolute Maximum Ratings                                                                  | 8    |

|-----------------------------------------------------------------------------------------------------|------|

| TABLE 2 - OPERATING CONDITIONS                                                                      | 9    |

| TABLE 3 - STATIC CHARACTERISTICS                                                                    | .11  |

| Table 4 - Dynamic Characteristics                                                                   | . 12 |

| TABLE 5 - UNIFIED MEMORY MAPPING                                                                    | . 15 |

| Table 6 - MLX16 pre-defined pages                                                                   | . 16 |

| Table 7 - System Protected Ports Overview                                                           | . 23 |

| Table 8 - Standard Ports Overview                                                                   | . 24 |

| Table 9 - Logic table for detection of LS input switches                                            | . 33 |

| TABLE 10 - LOGIC TABLE FOR DIAGNOSIS OF LS INPUT SWITCHES SHORT VS. BATTERY                         | . 33 |

| TABLE 11 - LOGIC TABLE FOR DIAGNOSIS OF ALL INPUT SWITCHES SHORT VS. OTHER SWITCHES BY I1           | . 33 |

| TABLE 12 - LOGIC TABLE FOR DIAGNOSIS OF ALL INPUT SWITCHES SHORT VS. OTHER SWITCHES BY I2           | . 34 |

| TABLE 13 - LOGIC TABLE FOR BREAK DETECTION OF LS INPUT SWITCHES                                     | . 34 |

| Table 14 - Logic table for detection of HS input switches                                           | . 34 |

| TABLE 15 - LOGIC TABLE FOR DIAGNOSIS OF HS INPUT SWITCHES SHORT VS. GND                             | . 34 |

| TABLE 16 - LOGIC TABLE FOR BREAK DETECTION OF HS INPUT SWITCHES                                     | . 35 |

| Table 17 - Sleep mode configuration overview (switch detection)                                     | . 37 |

| Table 18 - Active mode configuration overview SWx pins                                              | . 39 |

| Table 19 - Active mode configuration overview IOx pins                                              | .41  |

| Table 20 - ADC Input divider                                                                        | . 49 |

| Table 21 - Interrupt inputs                                                                         | .51  |

| Table 22 - Interrupt vectors                                                                        | . 52 |

| TABLE 23 - PRIO PORT ENCODING                                                                       | . 52 |

| Table 24 - Configurable PWM Frequencies                                                             |      |

| Table 25 - Duty cycle measurement and calculation in accordance to LIN physical layer specification |      |

| 2.X FOR BAUD RATES UP TO 20KBPS                                                                     | . 63 |

| Table 26 - Duty cycle measurement and calculation in accordance to LIN physical layer specification |      |

| 2.X FOR BAUD RATES OF 10.4KBPS OR BELOW                                                             | . 64 |

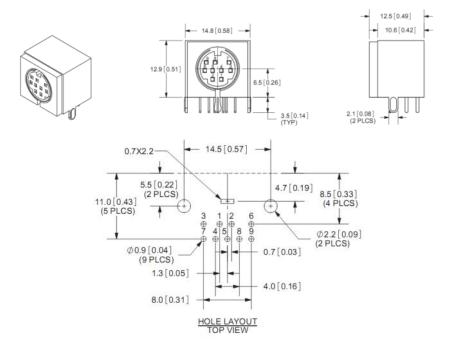

| Table 27 - Pin description 9 pin mini circular connector                                            |      |

| Table 28 - Pin description 10 pin header connector                                                  | . 81 |

| Table 29 - Connections for third party programmer                                                   | . 86 |

## 1. General Overview

### 1.1 Block Diagram

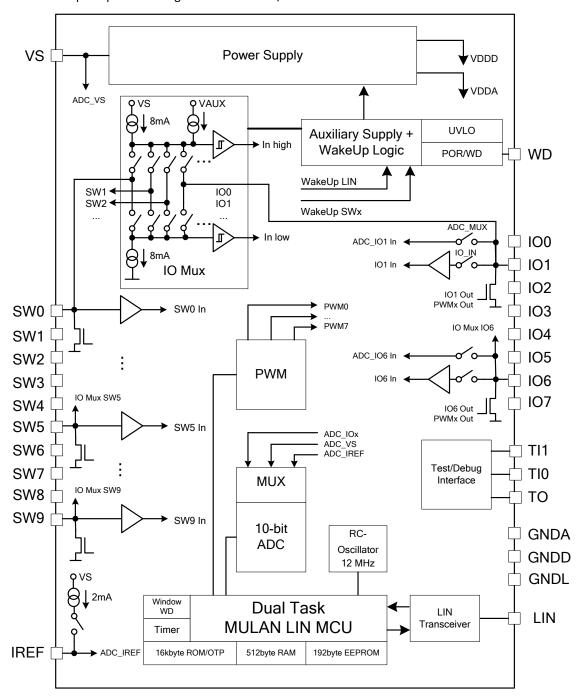

Figure 1 shows the principle block diagram of MLX80104/5.

Figure 1 - Block Diagram

Datasheet

#### **Electrical Characteristics** 2.

All voltages are referenced to ground (GND). Positive currents flow into the IC.

### **Absolute Maximum Ratings**

In accordance with the Maximum Rating System (IEC 60134). The absolute maximum ratings given in the table below are limiting values that do not lead to a permanent damage of the device but exceeding any of these limits may do so. Long term exposure to limiting values may affect the reliability of the device.

| Parameter                                              | Symbol                | Condition                                                  | Min        | Max    | Unit     |

|--------------------------------------------------------|-----------------------|------------------------------------------------------------|------------|--------|----------|

| Battery Supply Voltage                                 | Vs                    |                                                            | -0.3       | 40     | V        |

| Short term supply voltage                              | $V_{S\_Id}$           | ISO 7637/2 pulse 5; t < 400 ms                             | -0.3       | 40     | V        |

| Transients at supply voltage                           | V <sub>S_tr1</sub>    | ISO 7637/2 pulse 1 <sup>[1]</sup>                          | -100       |        | V        |

| Transients at supply voltage                           | V <sub>S_tr2</sub>    | ISO 7637/2 pulses 2 [1]                                    |            | +50    | V        |

| Transients at high voltage signal pins                 | V <sub>LINx_tr1</sub> | ISO 7637/3 pulse 1 [2]                                     | -100       |        | V        |

| Transients at high voltage signal pins                 | V <sub>LINx_tr2</sub> | ISO 7637/3 pulses 2 [2]                                    |            | +50    | V        |

| Transient at high voltage signal and power supply pins | V <sub>HV_tr3</sub>   | ISO 7637/2 pulses 3A, 3B [3]                               | -150       | +100   | V        |

| DC voltage on LIN, SWx, IOx pins                       | V <sub>LIN_DC</sub>   | T<500ms, V <sub>S</sub> = 18V<br>V <sub>S</sub> = 0V       | -22<br>-40 | 40     | ٧        |

| DC voltage on IREF, AWD pin                            | V <sub>logic_DC</sub> |                                                            | -0.3       | 7      | V        |

|                                                        | Vesdiec               | IEC 61000-4-2<br>Pin LIN, VS to GND                        | -6         | 6      | kV       |

| ESD capability                                         | Vesdhbm               | HBM (AEC-Q100-002) [4]<br>Pin LIN, VS to GND<br>Other pins | -8<br>-2   | 8<br>2 | kV<br>kV |

|                                                        | V <sub>ESDCDM</sub>   | CDM (AEC-Q100-011)                                         | -750       | 750    | V        |

| Maximum latch – up free current at any pin             | ILATCH                |                                                            | -500       | 500    | mA       |

| Maximum power dissipation                              | P <sub>tot</sub>      | T <sub>amb</sub> = +125 °C                                 |            | 0.78   | W        |

| Maximum power dissipation                              | rtot                  | T <sub>amb</sub> = + 85 °C                                 | 2          |        | VV       |

| Thermal impedance                                      | $\Theta$ JA           | JEDEC 1s2p board, none air flow                            |            | 32     | K/W      |

| Storage temperature                                    | T <sub>stg</sub>      |                                                            | -55        | +150   | °C       |

| Junction temperature                                   | T <sub>vj</sub>       |                                                            | -40        | +150   | °C       |

Table 1 - Absolute Maximum Ratings

<sup>[1]</sup> [2] [3] ISO 7637/2 test pulses are applied to VS via a reverse polarity diode and >2uF blocking capacitor.

ISO 7637/3 test pulses are applied to LIN via a coupling capacitance of 100nF.

ISO 7637/3 test pulses are applied to LIN via a coupling capacitance of 1nF.

ISO 7637/2 test pulses are applied to VS via a reverse polarity diode and >2uF blocking capacitor.

<sup>[4]</sup> Equivalent to discharging a 100pF capacitor through a 1.5Kohm resistor conforms to AEC-Q100-002

## **LIN Slave Controller for Switches**

Datasheet

### 2.2 Operating Conditions

| Parameter                             | Symbol           | Min | Max  | Unit |

|---------------------------------------|------------------|-----|------|------|

| Battery supply voltage [1]            | Vs               | 5   | 18   | V    |

| Short time battery supply voltage [2] | V <sub>S_S</sub> | 18  | 27   | V    |

| Operating ambient temperature         | T <sub>amb</sub> | -40 | +125 | °C   |

Table 2 - Operating Conditions

### 2.3 Static Characteristics

( $V_S = 5$  to 27V,  $T_A = -40$  to +125°C, unless otherwise specified)

| Parameter |                                               | Symbol                   | Condition                                                                                                   | Min      | Тур    | Max      | Unit |

|-----------|-----------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------|----------|--------|----------|------|

|           |                                               |                          | Pin VS                                                                                                      |          |        | <u> </u> |      |

| 3.00      | Supply current, active without switch current | Is                       |                                                                                                             |          | 6      | 20       | mA   |

| 3.01      | Undervoltage lockout                          | V <sub>S_UV</sub>        |                                                                                                             |          |        | 5        | V    |

| 3.02      | Supply current, sleep mode                    | I <sub>Ssl_typ</sub>     | V <sub>S</sub> = 12V                                                                                        |          | 25     | 50       | μΑ   |

| 3.03      | Supply current, sleep mode                    | I <sub>Ssl</sub>         | V <sub>S</sub> = 18V                                                                                        |          |        | 90       | μΑ   |

|           |                                               |                          | PIN LIN                                                                                                     |          |        |          |      |

| 3.10      | Short circuit bus current                     | I <sub>BUS_LIM</sub>     | V <sub>LIN</sub> = V <sub>S</sub> = 18V, T <sub>x</sub> D = 0                                               | 40       | 120    | 200      | mA   |

| 3.11      | Pull up resistor LIN                          | RSLAVE                   | V <sub>LIN</sub> =0, TxD open                                                                               | 20       | 30     | 60       | kΩ   |

| 3.12      | Pull up current LIN, Sleep mode               | IBUS_PU_Sleep            | V <sub>LIN</sub> =0, V <sub>S</sub> =12V, sleep mode                                                        | -100     | -75    |          | μΑ   |

| 3.13      | 3.13 LIN reverse current, recessive           |                          | V <sub>LIN</sub> >V <sub>S</sub> , 5V <v<sub>LIN &lt;18V,<br/>5V <v<sub>S &lt;18V, TxD open</v<sub></v<sub> |          |        | 20       | μA   |

|           | Receiver input leakage current                | I <sub>BUS_PAS_dom</sub> | V <sub>S</sub> = 12V, V <sub>LIN</sub> =0                                                                   | -1       |        |          | mA   |

| 3.14      | LIN reverse current loss of battery           | I <sub>BUS_NO_BAT</sub>  | V <sub>S</sub> =0V, 0V < V <sub>LIN</sub> < 18V                                                             |          |        | 23       | μΑ   |

| 3.15      | LIN current during loss of Ground [3]         | I <sub>BUS_NO_GND</sub>  | V <sub>S</sub> =V <sub>GND</sub> =12V, 0V <v<sub>LIN&lt;18V</v<sub>                                         | -100     |        | 20       | μΑ   |

| 3.16      | Transmitter dominant voltage                  | $V_{\text{ol\_LIN}}$     | load=500Ω, TxD=0                                                                                            |          |        | 0.2      | Vs   |

| 3.17      | Recessive output voltage                      | V <sub>oh_LIN</sub>      | TxD open                                                                                                    | 0.8      |        | 1        | Vs   |

| 3.18      | Lin input capacitance [1]                     | CLIN                     | Pulse response via $1k\Omega$ , $V_{Pulse}=12V$ , $V_{S}=14V$                                               |          | 25     | 35       | pF   |

| 3.19      | Voltage drop serial diode [1]                 | CSerDiode                |                                                                                                             | 0.4      | 0.7    | 1.0      | V    |

| 3.30      | Receiver dominant voltage                     | V <sub>BUSdom</sub>      |                                                                                                             |          |        | 0.4*Vs   | V    |

| 3.31      | Receiver recessive voltage                    | V <sub>BUSrec</sub>      |                                                                                                             | 0.6*Vs   |        |          | V    |

| 3.32      | Centre point of receiver threshold            | V <sub>BUS_cnt</sub>     | V <sub>BUS_cnt</sub> =( V <sub>th_dom</sub> + V <sub>th_rec</sub> )/2                                       | 0.475*Vs | 0.5*Vs | 0.525*Vs | V    |

| 3.33      | Receiver hysteresis                           | V <sub>HYS</sub>         | V <sub>HYS</sub> =( V <sub>th_dom</sub> -V <sub>th_rec</sub> )                                              |          |        | 0.175*Vs | V    |

<sup>[1]</sup>  $V_s$  is the IC supply voltage including voltage drop of reverse battery protection diode,  $V_{DROP} = 0.4...1V$ ,  $V_{BAT\_ECU} = 6...27V$ .

<sup>[2]</sup> Short time: t < 1 min

# LIN Slave Controller for Switches

Datasheet

| Parameter | Symbol | Condition | Min | Тур | Max | Unit |

|-----------|--------|-----------|-----|-----|-----|------|

|-----------|--------|-----------|-----|-----|-----|------|

|                                          |                                                              | PIN SW                  | x, IOx in normal mode                             |          |              |              |    |

|------------------------------------------|--------------------------------------------------------------|-------------------------|---------------------------------------------------|----------|--------------|--------------|----|

| 3.40                                     | Central current source on resistance pull up configuration   | Rih_SWx                 | Pull up mode, voltage shift max 0.1*Vs            |          |              | 1            | ΚΩ |

| 3.41                                     | Central current source on resistance pull down configuration | R <sub>il_SWx</sub>     | Pull down mode, voltage shift max 0.1*Vs          |          |              | 1            | ΚΩ |

| 3.42                                     | High level input voltage                                     | $V_{ih\_SWx}$           | Input mode                                        | 1.4      |              |              | V  |

| 3.43                                     | Low level input voltage                                      | $V_{il\_SWx}$           | Input mode                                        |          |              | 0.9          | V  |

| 3.44                                     | On resistance SWx                                            | Ron_io                  | Low side mode, V <sub>SWx</sub> =0.5V             |          | 50           | 100          | Ω  |

| 3.45                                     | Source current central current source                        | l <sub>ih_SWx</sub>     | Vs=5V<br>Vs=13V (T <sub>A</sub> = 25°C)<br>Vs=18V | 1.5<br>7 |              | 12           | mA |

| 3.46 Sink current central current source |                                                              | l <sub>il_</sub> swx    | Vs=5V<br>Vs=13V (T <sub>A</sub> = 25°C)<br>Vs=18V | 1.5<br>7 |              | 12           | mA |

| 3.47                                     | Leakage current low level input                              | I <sub>leakl_SWx</sub>  | V <sub>il_SWx</sub> = 0, V <sub>S</sub> = 18V     | -10      |              | 10           | μA |

| 3.48                                     | Leakage current high level input                             | I <sub>leakh_SWx</sub>  | V <sub>ih_SWx</sub> = 18V, V <sub>S</sub> = 18V   | -10      |              | 10           | μΑ |

|                                          |                                                              | <del>-</del>            | PIN IREF                                          |          | <del>.</del> | <del>-</del> | •  |

| 3.60                                     | Input voltage range                                          | Viref                   |                                                   | 0        |              | Vs           | V  |

| 3.61                                     | Output current                                               | liref                   |                                                   | 1.3      | 2            | 3.1          | mA |

| 3.62                                     | Leakage current low level input                              | I <sub>leakl_IREF</sub> | V <sub>IREF</sub> = 0, V <sub>S</sub> = 18V       | -10      |              | 10           | μΑ |

| 3.63                                     | Leakage current high level input                             | I <sub>leakh_IREF</sub> | V <sub>IREF</sub> = 3.4V, V <sub>S</sub> = 18V    | -10      |              | 10           | μΑ |

|                                          |                                                              | •                       | PIN AWD                                           |          | •            | •            | •  |

| 3.70                                     | Input voltage range                                          | V <sub>AWD</sub>        |                                                   | 0        |              | 3.4          | V  |

| 3.71                                     | Pull down current                                            | I <sub>PD_AWD</sub>     |                                                   |          | 2            |              | μA |

| 3.72                                     | Pull up current                                              | I <sub>PU_AWD</sub>     |                                                   |          | 20           |              | μΑ |

| 3.73                                     | RESET threshold                                              | V <sub>AWD_IRQ</sub>    |                                                   |          | 0.5          |              | V  |

| 3.74                                     | Interrupt threshold                                          | $V_{AWD\_Int}$          |                                                   |          | 1.5          |              | V  |

| 3.75                                     | Down threshold                                               | V <sub>AWD_d</sub>      |                                                   |          | 2.5          |              | V  |

|                                          |                                                              | Wakeu                   | p capability SWx,IOx                              |          |              |              |    |

| 3.80                                     | Wake up pull up resistance SWx, IOx [4]                      | R <sub>ih_WU_SWx</sub>  | Pull up mode, voltage shift max 0.1Vs             | 500      |              | 1000         | Ω  |

| 3.81                                     | Wake up pull down resistance SWx, IOx [4]                    | Ril_wu_swx              | Pull down mode, voltage shift max 0.1Vs           | 500      |              | 1000         | Ω  |

| 3.82                                     | High level input voltage                                     | Vih_WU_SWx              | Input mode                                        | 1.4      |              |              | V  |

| 3.83                                     | Low level input voltage                                      | V <sub>il_WU_SWx</sub>  | Input mode                                        |          |              | 0.9          | V  |

| 3.84                                     | On resistance in sleep mode SWx/IOx                          | R <sub>ON_WU_IO</sub>   | Low side mode (S3x), V <sub>SWx/IOx</sub> =0.5V   |          | 50           | 100          | Ω  |

## LIN Slave Controller for Switches

Datasheet

| Parameter |                      | Symbol           | Condition | Min | Тур | Max | Unit |  |

|-----------|----------------------|------------------|-----------|-----|-----|-----|------|--|

|           | Thermal Protection   |                  |           |     |     |     |      |  |

| 3.90      | Thermal shutdown [1] | $T_{sd}$         |           | 155 |     | 180 | °C   |  |

| 3.91      | Thermal recovery [1] | T <sub>rec</sub> |           | 126 |     | 150 | °C   |  |

|                      | ADC Resolution (INL)    |                        |                        |     |     |      |     |  |  |

|----------------------|-------------------------|------------------------|------------------------|-----|-----|------|-----|--|--|

| 3.67                 | ADC acquiracy           | V                      | One time measurement   |     |     | 5    | LSB |  |  |

| 3.68                 | ADC accuracy            | V <sub>mess_diff</sub> | Three time measurement |     |     | 2    | LSB |  |  |

|                      | Switches                |                        |                        |     |     |      |     |  |  |

| On - res             | On - resistance [2] [5] |                        | carbon on gold         | 0   | 150 | 1000 | Ω   |  |  |

| Off - resistance [2] |                         | R <sub>SW_off</sub>    | Open switch            | 500 |     |      | ΚΩ  |  |  |

Table 3 - Static Characteristics

Parameter not tested in production, guaranteed by qualification.

Switch parameter not determined by the IC, values are calculation basis for all currents and thresholds

The current is determined by the master pull-up. To prevent discharging of the battery, the master pull up will be disconnected under Loss of Ground conditions

Resistance is valid for the sum of switch resistance and the ESD protection resistance

<sup>[4]</sup> [5] A 500Ohm series resistor is required in case of the remote switch outside of the module and the switch is in this case directly supplied from the battery

Datasheet

### **Dynamic Characteristics**

( $V_S = 7$  to 27V,  $T_A = -40$  to +125°C, unless otherwise specified)

| Parameter |                                         | Symbol                | Condition                                                                                                   | Min   | Тур | Max          | Unit |

|-----------|-----------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------|-------|-----|--------------|------|

|           |                                         |                       | PIN LIN                                                                                                     |       |     |              |      |

| 4.01      | Propagation delay receiver [1]          | t <sub>rx_pdf</sub>   | C <sub>RxD</sub> = 25pF, rising and Falling edge                                                            |       |     | 6            | μs   |

| 4.02      | Propagation delay receiver symmetry [2] | t <sub>rx_sym</sub>   | t <sub>tx_pdf</sub> - t <sub>rx_pdr</sub>                                                                   | -2    |     | 2            | μs   |

| 4.03      | Receiver debounce time [2]              | t <sub>rx_deb</sub>   | LIN rising and falling edge                                                                                 | 0.5   |     | 4            | μs   |

| 4.04      | LIN duty cycle 1 [3,4]                  | D1                    | 20kbps operation, normal mode $t_{Bit} = 50 \mu s$ , D1= $t_{LIN\_rec(min)}/(2*t_{Bit})$                    | 0.396 |     |              |      |

| 4.05      | LIN duty cycle 2 [3,4]                  | D2                    | 20kbps operation, normal mode $t_{Bit} = 50 \mu s$ , D2= $t_{LIN\_rec(max)}/(2*t_{Bit})$                    |       |     | 0.581        |      |

| 4.06      | LIN duty cycle 3 [3,4]                  | D3                    | 10.4kbps operation, low speed, t <sub>Bit</sub> = 96µs, D3=t <sub>LIN_rec(min)</sub> /(2*t <sub>Bit</sub> ) | 0.417 |     |              |      |

| 4.07      | LIN duty cycle 4 [3,4]                  | D4                    | 10.4kbps operation, low speed, $t_{Bit} = 96\mu s$ , D3= $t_{LIN\_rec(max)}/(2*t_{Bit})$                    |       |     | 0.590        |      |

| 4.08      | trec(max) - tdom(min)                   | Δt3                   | 10.4kbps operation, low speed mode                                                                          |       |     | 15.9         | μs   |

| 4.09      | trec(min) – tdom(max)                   | Δt4                   | 10.4kbps operation, low speed mode                                                                          |       |     | 17.28        | μs   |

| 4.12      | Wake up filter time                     | twu                   | Sleep mode, LIN rising and falling edge                                                                     | 15    |     | 150          | μs   |

|           |                                         | •                     | PIN SWx/IOx                                                                                                 |       |     | <del>-</del> |      |

| 4.21      | Local wake-up filter time               | t <sub>wu_local</sub> | Sleep mode rising and falling edge                                                                          | 10    | 25  | 50           | μs   |

|           | -                                       | <u> </u>              | ADCx                                                                                                        |       |     | •            | •    |

| 4.22      | Conversion time ADC                     | t <sub>conv</sub>     |                                                                                                             | 12    |     |              | μs   |

|           |                                         |                       | PIN IOx                                                                                                     |       |     |              |      |

| 4.24      | Slew Rate IOx <sup>[5]</sup>            | t <sub>Slew_IOx</sub> | Low side mode, Vs=6V, R <sub>pullup</sub> =2.5k $\Omega$ , C <sub>load</sub> = 20pF                         |       |     | 2.5          | μs   |

|           |                                         |                       | General                                                                                                     |       |     |              |      |

|           | Device start up time [6] [7]            | t <sub>SUP</sub>      | After POR,UVR, Wakeup                                                                                       | 3     | 5   | 10           | ms   |

Table 4 - Dynamic Characteristics

<sup>[1]</sup> This parameter is tested by applying a square wave signal to the LIN. The minimum slew rate for the LIN rising and falling

See figure - Receiver debounce and propagation delay

<sup>[2]</sup> [3] [4] [5] See figure - Duty cycle measurement and calculation

Standard loads for duty cycle measurements are 1KΩ/1nF, 660Ω/6.8nF, 500Ω/10nF, internal termination disabled

Only information

Only characterization, guaranteed by design

This time contains the activation time of hardware components and the software initialisation time. To get first valid switch status information, the programmed switch debouncing time must be added.

# 3. MULAN - MULtiple CPU with Analog and Network support

### 3.1 General

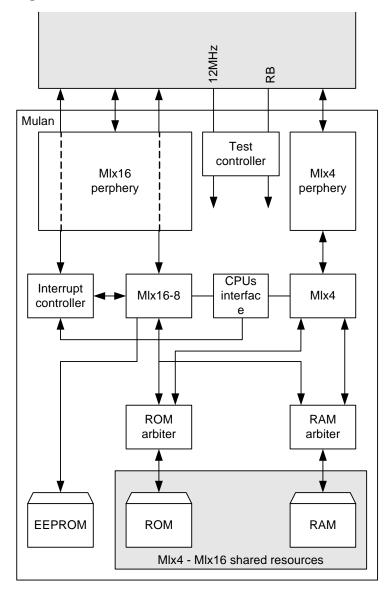

The MULAN CPU is a dual task implementation of the Melexis LIN Controller (MLX4) and the MLX16-8 CPU core. It is possible to run two tasks simultaneously with this architecture, one task for communication and the other task is free for the customer application. The communication between both tasks is done via API commands. The complete firmware including API for the LIN controller is supported by Melexis. The Customer only needs to program the application software on the MLX16-8 CPU. For a detailed description of this CPU please see the MLX16-8 data book.

### 3.2 MULAN Block Diagram

Figure 2 - Block Diagram of MULAN CPU

Datasheet

### 3.3 CPU Timing

MULAN use two CPUs:

A 4 bit CPU to handle a low speed protocol such as LIN.

A 16 bit CPU for an application firmware.

This construction has the following advantages:

The user does not need to take care of the real time problems of a protocol.

The protocol is handled by a Melexis firmware that can be updated when the protocol evolves.

The application CPU throughput is not affected by the protocol handling.

There is a native inter-task protection, e.g. an application crash does not affect the protocol handling.

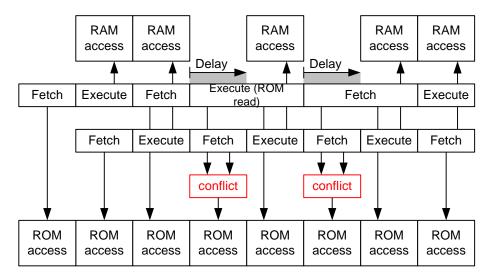

Both CPUs share a common 12 MHz clock, a common ROM for program memory and a common RAM for data. Two memory arbiters are used for resolving conflicts with a common strategy: The Mlx4 always has priority. Most of the time there is no conflict as the CPUs are interleaved as shown on Figure 3.

Figure 3 - CPU interleaving

### 3.4 MLX16-8

The 16 bit CPU is an Mlx16-8. This core is an evolution of the Mlx16 to increase GCC code generation efficiency. The change is limited to a few added instructions. A detailed description can be found in the Mlx16-8 datasheet. For readers familiar with the Mlx16, the list of instructions added is:

- CALLF : Call Far (anywhere within 64K)

- FSB : Find first bit set (in a word)

- MOVER [XIII] [XIII] : Converges of butes

MOVSB [X++], [Y++] : Copy array of bytesMOVSW [X++], [Y++] : Copy array of words

- Push #Word : Push a constant word into the stack

- SFB : Set first bit (in a word)

Moreover a new address mode has been added to allow direct access to any location. It is similar to dp: Addressing mode but allows any address within 64K at expense of an extra word of op-code.

Datasheet

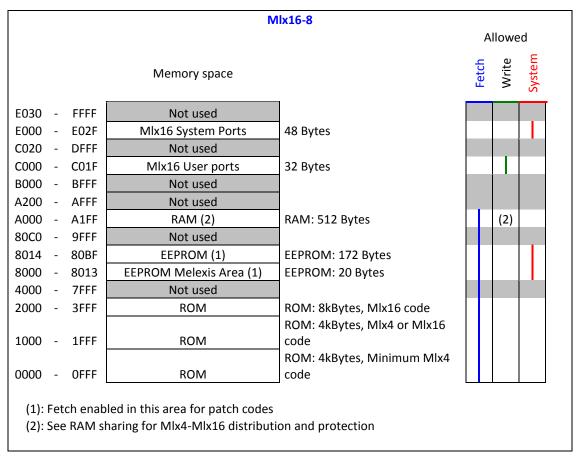

## 4. Address Space

Mlx4 and Mlx16 share a common ROM and RAM. From the 2 CPUs a unified 16 bit bus is created (Von Neumann architecture). This bus is hooked to the ROM, the RAM, the EEPROM and the Mlx16-8 peripherals. Two arbiters are in charge of creating a unique memory address and corresponding access signals for ROM and RAM.

### 4.1 Memory Mapping

The unified 16 bit bus accesses devices as shown on Table 5.

Table 5 - Unified memory mapping

There are some restrictions for accessing certain areas depending on the type of access:

- Mlx4 can fetch anywhere from 0x0000 to 0x1FFF (12 bits word address)

- Mlx16 can fetch from:

ROM: Normal caseEEPROM: For patched codeRAM: For test purposes

Mlx4 and Mlx16 can read any RAM location (limited to 256 bytes for Mlx4)

## LIN Slave Controller for Switches

Datasheet

The predefined pages of the Mlx16-8 are encoded as shown on Table 5. Some have fixed values (in grey) while others have value that depends of the ROM size. Table 6 gives examples for most common ROM sizes.

|      | ROM  |                                                      |

|------|------|------------------------------------------------------|

| Name | 16K  | Note                                                 |

| Fp0: | 3F00 | Last ROM page (used by interrupt controller)         |

| Fp1: | 3E00 | Could be used for C runtime                          |

| Fp2: | 3D00 | Could be used for C runtime                          |

| Fp3: | 3C00 | Could be used for C runtime                          |

| Fp4: | 3B00 | Could be used for C runtime                          |

| Fp5: | A100 | In (large) RAM for fast patches (copied from EEPROM) |

| Fp6: | A000 | In RAM Dp: for test routines                         |

| Fp7: | 8000 | In EEPROM to allow single instruction patch start    |

| Dp:  | A000 | Mlx16 private RAM                                    |

| lo:  | C000 | Standard Ports                                       |

| Ep:  | 8000 | EEPROM (First page)                                  |

| Legend: | _                                 |

|---------|-----------------------------------|

|         | Fixed address for any ROM size    |

|         | Address depending on the ROM size |

Table 6 - MLX16 pre-defined pages

### 4.2 RAM Sharing

A RAM size of 512 bytes is available for the MLX80104/5. This area is used by both CPUs.

While Mlx4 sees its private and shared RAM areas as 2 consecutive spaces, Mlx16 sees the private area of Mlx4 at the top of its RAM address space and the shared area at its bottom. This arrangement has the following advantages:

- Shared area is in Mlx16 Dp: address space, so Mlx16 has a fast access to it.

- The Mlx16-8 private area is in a single piece which makes GCC more efficient.

### 4.3 ROM/OTP Sharing

The MLX80104/5 has integrated 16Kbyte ROM or OTP. This area is used from both CPUs. The LIN Task + LIN API use 5kbytes while the rest (11kbytes) is available for the application running on the MLX16

Each CPU has is own separate program code in the ROM/OTP area but there is no specific mechanism to isolate them. The linker program merges the two programs and verifies that there is no overlapping, but if at execution time an error causes one CPU to jump into the code of the other one, it will of course execute unpredictable instructions and this situation will be detected either by watchdog overflow or protection error.

### LIN Slave Controller for Switches

Datasheet

#### 4.4 EEPROM

With the EEPROM it is possible to store non-volatile information. The EEPROM block is a 96 x 16bit Electrically Erasable Programmable Read Only Memory (EEPROM) with single power supply, single-error correction (SEC) and double-error detection (DED). An internal charge pump generates high voltage needed for the Erase/Write operations.

The EEPROM is Mlx16 private. The required EEPROM data for the Mlx4 execution is placed in RAM by the Mlx16 before it releases Mlx4 reset.

The EEPROM is organized in words (16 bits). Reading byte-wise is possible, but writing is only possible word-wise.

### 4.4.1. Static/dynamic Characteristics

| Parameter                    | Remark                      | min     | Тур | Max | Unit  |

|------------------------------|-----------------------------|---------|-----|-----|-------|

| Number of erase/write cycles | T <sub>amb</sub> = 25°C     | 100 000 |     |     |       |

| Number of erase/write cycles | T <sub>amb</sub> = 125°C    | 10 000  |     |     |       |

| Data retention time          | T <sub>amb</sub> = 85°C     | 10      |     |     | Years |

| Erase/Write time             | T <sub>amb</sub> = -40125°C | 4       |     | 8   | ms    |

#### 4.4.2. Reserved EEPROM Segments

| Segment name         | Segment range    | Description                                       |  |  |  |  |

|----------------------|------------------|---------------------------------------------------|--|--|--|--|

|                      | (word addresses) |                                                   |  |  |  |  |

| Melexis area         | 0x8000 - 0x8013  | Melexis calibration data                          |  |  |  |  |

| Patch0 start address | 0x8014           | start address and enable bit for firmware patch 0 |  |  |  |  |

| Patch1 start address | 0x8016           | start address and enable bit for firmware patch 1 |  |  |  |  |

| User area            | 0x8018 - 0x809E  | User data                                         |  |  |  |  |

| Patch0 area          | 0x80A0 - 0x80AE  | Patch0                                            |  |  |  |  |

| Patch1 area          | 0x80B0 - 0x80BE  | Patch1                                            |  |  |  |  |

The using of firmware patches is optional but recommended. In case no firmware patch is used, these areas can be used for user data.

#### 4.4.3. Write Timing

The EEPROM requires a 5ms delay for write and erase operations. This is generated from a 250 KHz internal clock. A write or erase access to the EEPROM starts a 5ms delay period that can be monitored by either polling port bit EE\_BUSY or waiting for the interrupt EE\_IT.

### Note:

While the EEPROM is being written, both CPUs are still running. An attempt to read or write to EEPROM by Mlx16 while it is busy generates an exception interrupt.

#### 4.4.4. Read timing

The read access time of the EEPROM is 4 clock periods. This delay is created using the master clock.

## **LIN Slave Controller for Switches**

Datasheet

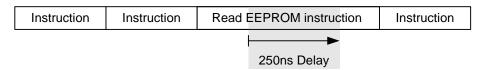

### 4.4.5. Read

A read is done "on the fly" by adding wait states in the instruction.

Figure 4 - EEPROM read

### LIN Slave Controller for Switches

Datasheet

### 4.4.6. Write/Erase

The MLx16 supports 2 operations: Read and Write, while EEPROM requires 3 operations: Read, Write, and Erase. EEPROM Write and Erase are both accomplished by an Mlx16 write instruction.

As write and erase delays are long, the Mlx16 does not delay its instruction till completion. A specific hardware buffers address and data and the CPU continues its execution while the write/erase is ongoing.

The CPU has 2 options to know when the write/erase delay is terminated. It can either poll bit EE\_BUSY (0 when not busy, 1 when busy) for a 0 value, or it can enable interrupt EE\_IT that will be triggered when EE\_BUSY goes from 1 to 0.

In order to minimize the risk of erroneous write/erase of the EEPROM, those accesses are only possible in system mode, e.g. application should call a secure system function to erase or write.

Since some applications require the EEPROM should never be written there is an extra protection for the EEPROM. The system port CONTROL has a bit EN\_EEPROM\_WE (0 at reset) that must be set to enable write and erase, or else the operation is cancelled and a protection interrupt is generated.

### **EEPROM Control register**

| Address | Name   | Bit7    | Bit6     | Bit5     | Bit4     | Bit3     | Bit2     | Bit1      | Bit0      |

|---------|--------|---------|----------|----------|----------|----------|----------|-----------|-----------|

| 0xE001  | EEPROM | EE_BUSY | Reserved | Reserved | Reserved | Reserved | Reserved | EE_CTL[1] | EE_CTL[0] |

EE\_BUSY EE\_CTL[1:0] Will be always high in case there is a write process running

Controls the EEPROM read and write mode

00 Write 01 Erase

Block write, write access to any EEPROM address will overwrite the complete EEPROM Block erase, write access to any EEPROM address will reset the complete EEPROM to 1

### System Control register

| Address | Name    | Bit7     | Bit6          | Bit5    | Bit4    | Bit3    | Bit2     | Bit1 | Bit0    |

|---------|---------|----------|---------------|---------|---------|---------|----------|------|---------|

| 0xE000  | CONTROL | Reserved | EEPROM_<br>WE | OUTC_WE | OUTB_WE | OUTA_WE | Reserved | HALT | M4_PORB |

EEPROM\_WE Write enable bit EERPOM

1 = EEPROM content can be changed

0 = EEPROM content can **not** be changed

OUTC\_WE Write enable bit

1 = ANA\_OUTC can be changed 0 = ANA\_OUTC can **not** be changed

OUTB\_WE Write enable bit

1 = ANA\_OUTB can be changed 0 = ANA\_OUTB can **not** be changed

OUTA\_WE Write enable bit

1 = ANA\_OUTA can be changed 0 = ANA\_OUTA can **not** be changed

HALT Writing to the bit will halt the MLX16

M4\_PORB MIx4 Reset: Writing to the bit resets the MLX4

## LIN Slave Controller for Switches

Datasheet

### System Various register

| Address | Name    | Bit7   | Bit6   | Bit5     | Bit4     | Bit3     | Bit2     | Bit1     | Bit0     |

|---------|---------|--------|--------|----------|----------|----------|----------|----------|----------|

| 0xE000  | VARIOUS | EE_DED | EE_SEC | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved |

EE\_DED EEPROM double-error detection

1 = EEPROM double-error detected 0 = EEPROM double-error **not** detected

EE\_SEC EEPROM single-error correction

1 = EEPROM single-error detected and corrected

0 = EEPROM single-error **not** detected

## LIN Slave Controller for Switches

Datasheet

### 4.5 OTP (MLX80105 only)

The MLX80105 has integrated 16Kbyte OTP. This area is used by both CPUs. The LIN Task + LIN API use 5kbytes while the rest (11kbytes) is available for the application running on the MLX16

Each CPU has is own separate program code in the OTP area but there is no specific mechanism to isolate them. The linker program merges the two programs and verifies that there is no overlapping, but if at execution time an error causes one CPU to jump into the code of the other one, it will of course execute unpredictable instructions and this situation will be detected either by watchdog overflow or protection error.

From the functional point of view the MLX80104 (ROM) behaves the same as the MLX80105 (OTP).

Datasheet

## 5. IO Registers

### 5.1 General

There are 2 port spaces for the Mlx16:

- System protected ports (starting at address 0xE000), Mlx16 bit USER must be cleared.

- User ports (starting at address 0xC000), not protected, Mlx16 bit USER must be set.

The Mulan port map has an open window of 16 bytes of custom user ports and of 12 bytes of custom system ports (not included in Mulan). Reading to non existing custom ports will have no effect and reading from non existent custom ports will always return 0.

### 5.2 System Protected ports

Table 7 shows the available system ports. All of these ports are system protected, meaning they are only accessible with bit USER=0. All of these registers are located outside of the IO-Segment.

| Name       | Address | Access<br>Mode | Description                                                        | Page |

|------------|---------|----------------|--------------------------------------------------------------------|------|

| MLX        | 0xE02F  | Byte           | MLX Reserved                                                       |      |

| SEL_XTAL   | 0xE02E  | Word/Byte      | Selection of internal/external Oscillator                          | 43   |

| MLX        | 0xE02D  | Byte           | MLX Reserved                                                       |      |

| STATUS     | 0xE02C  | Word/Byte      | Wakeup Source and central pull up/down input comparator            | 27   |

| SW_IN_H    | 0xE02B  | Byte           | SW89 Input comparator                                              | 28   |

| SW_IN_L    | 0xE02A  | Word/Byte      | SW07 Input comparator                                              | 28   |

| IO_IN      | 0xE029  | Byte           | IO08 Input comparator                                              | 29   |

| IO_AWD     | 0xE028  | Word/Byte      | Watchdog Acknowledge                                               | 44   |

| IO_IRQ     | 0xE027  | Byte           | Interrupt source of IO generated interrupts                        | 29   |

| IO_EN      | 0xE026  | Word/Byte      | Enable IO pins                                                     | 29   |

| IO_INT_ENF | 0xE025  | Byte           | Enable IO interrupt on falling edges                               | 29   |

| IO_INT_ENR | 0xE024  | Word/Byte      | Enable IO interrupt on rising edges                                | 29   |

| MLX        | 0xE023  | Byte           | MLX Reserved                                                       |      |

| MLX        | 0xE022  | Word/Byte      | MLX Reserved                                                       |      |

| ANA_OUTC_H | 0xE021  | Byte           | ADC reference calibration                                          | 68   |

| ANA_OUTC_L | 0xE020  | Word/Byte      | RC Oscillator trimming, enable external system clock source        | 68   |

| ANA_OUTB_H | 0xE01F  | Byte           | Current references and bandgap trimming, slew rate LIN transceiver | 68   |

| ANA_OUTB_L | 0xE01E  | Word/Byte      | Switch current source trimming, VDDD and VDDA trimming             | 68   |

| ANA_OUTA_H | 0xE01D  | Byte           | Setting EEPROM write delay, timer controlled wake up enable        | 68   |

| ANA_OUTA_L | 0xE01C  | Word/Byte      | Power down enable LIN transceiver                                  | 68   |

| PATCH3_A_H | 0xE01B  | Byte           | 4th Patch start address high byte, patch enable                    | 70   |

| PATCH3_A_L | 0xE01A  | Word/Byte      | 4th Patch start address low byte                                   | 70   |

| PATCH2_A_H | 0xE019  | Byte           | 3 <sup>rd</sup> Patch start address high byte, patch enable        | 70   |

| PATCH2_A_L | 0xE018  | Word/Byte      | 3 <sup>rd</sup> Patch start address low byte                       | 70   |

| PATCH1_A_H | 0xE017  | Byte           | 2 <sup>nd</sup> Patch start address high byte, patch enable        | 70   |

| PATCH1_A_L | 0xE016  | Word/Byte      | 2 <sup>nd</sup> Patch start address low byte                       | 70   |

| PATCH0_A_H | 0xE015  | Byte           | 1st Patch start address high byte, patch enable                    | 70   |

| PATCH0_A_L | 0xE014  | Word/Byte      | 1st Patch start address low byte                                   | 70   |

# LIN Slave Controller for Switches

Datasheet

| Name       | Address                 | Access<br>Mode | Description                                      | Page |

|------------|-------------------------|----------------|--------------------------------------------------|------|

| PATCH3_I_H | 0xE013                  | Byte           | 4th Patch jump instruction high byte             | 70   |

| PATCH3_I_L | 0xE012                  | Word/Byte      | 4th Patch jump instruction low byte              | 70   |

| PATCH2_I_H | 0xE011                  | Byte           | 3 <sup>rd</sup> Patch jump instruction high byte | 70   |

| PATCH2_I_L | 0xE010                  | Word/Byte      | 3 <sup>rd</sup> Patch jump instruction low byte  | 70   |

| PATCH1_I_H | 0xE00F                  | Byte           | 2 <sup>nd</sup> Patch jump instruction high byte | 70   |

| PATCH1_I_L | 0xE00E                  | Word/Byte      | 2 <sup>nd</sup> Patch jump instruction low byte  | 70   |

| PATCH0_I_H | 0xE00D                  | Byte           | 1st Patch jump instruction high byte             | 70   |

| PATCH0_I_L | 0xE00C                  | Word/Byte      | 1st Patch jump instruction low byte              | 70   |

| MLX        | 0xE00B                  | Byte           | MLX reserved                                     |      |

| MLX        | 0xE00A                  | Word/Byte      | MLX reserved                                     |      |

| PEND_H     | 0xE009                  | Byte           | Pending Interrupts high byte                     | 53   |

| PEND_L     | 0xE008                  | Word/Byte      | Pending Interrupts low byte                      | 53   |

| MASK_H     | 0xE007                  | Byte           | Interrupt mask high byte                         | 53   |

| MASK_L     | 0xE006                  | Word/Byte      | Interrupt mask low byte                          | 53   |

| PRIO_H     | 0xE005                  | Byte           | Interrupt priority high byte                     | 53   |

| PRIO_L     | 0xE004                  | Word/Byte      | Interrupt Priority low byte                      | 53   |

| SHRAMH     | 0xE003                  | Byte           | Upper limit for the RAM not accessible by MLX16  |      |

| SHRAML     | SHRAML 0xE002 Word/Byte |                | Lower limit for the RAM not accessible by MLX16  |      |

| EEPROM     | 0xE001                  | Byte           | EEPROM control register                          | 19   |

| CONTROL    | 0xE000                  | Byte           | System control register                          | 19   |

Table 7 - System Protected Ports Overview

Datasheet

### 5.3 Standard ports

Table 8 shows the available system ports. All of these ports are system protected, meaning they are only accessible with bit USER=1. All of these registers are located outside of the IO-Segment.

| Name           | Address | Access<br>Mode | Description                                               | Page |

|----------------|---------|----------------|-----------------------------------------------------------|------|

| MLX            | 0xC01F  | Byte           | MLX reserved                                              |      |

| MLX            | 0xC01E  | Word/Byte      | MLX reserved                                              |      |

| SW_CONFIG      | 0xC01D  | Byte           | Current configuration central current source, IREF enable | 27   |

| S3H            | 0xC01C  | Word/Byte      | IO pin open drain enable (S3)                             | 29   |

| S2H            | 0xC01B  | Byte           | IO pin central current source pull down enable (S2)       | 27   |

| S1H            | 0xC01A  | Word/Byte      | IO pin central current source pull up enable (S1)         | 27   |

| S3L_H          | 0xC019  | Byte           | SW89 pin open drain enable (S3)                           | 28   |

| S3L_L          | 0xC018  | Word/Byte      | SW07 pin open drain enable (S3)                           | 28   |

| S2L_H          | 0xC017  | Byte           | SW89 pin central current source pull down enable (S2)     | 27   |

| S2L_L          | 0xC016  | Word/Byte      | SW07 pin central current source pull down enable (S2)     | 27   |

| S1L_H          | 0xC015  | Byte           | SW89 pin central current source pull up enable (S1)       | 27   |

| S1L_L          | 0xC014  | Word/Byte      | SW07 pin central current source pull up enable (S1)       | 27   |

| PWM_DATA_READ  | 0xC013  | Byte           | PWM duty cycle value (read only)                          |      |

| PWM_DATA_WRITE | 0xC012  | Word/Byte      | PWM duty cycle write register                             |      |

| PWM_AD         | 0xC011  | Byte           | PWM channel selection                                     | 57   |

| PWM_CTL        | 0xC010  | Word/Byte      | PWM configuration register                                | 58   |

| MLX            | 0xC00F  | Byte           | MLX reserved                                              |      |

| MLX            | 0xC00E  | Word/Byte      | MLX reserved                                              |      |

| MLX            | 0xC00D  | Byte           | MLX reserved                                              |      |

| MLX            | 0xC00C  | Word/Byte      | MLX reserved                                              |      |

| ADC_IN_H       | 0xC00B  | Byte           | ADC result high byte                                      | 50   |

| ADC_IN_L       | 0xC00A  | Word/Byte      | ADC result low byte                                       | 50   |

| ADC_CTL_H      | 0xC009  | Byte           | ADC reference voltage and channel selection               | 50   |

| ADC_CTL_L      | 0xC008  | Word/Byte      | ADC configuration and status                              | 50   |

| TIMER_H        | 0xC007  | Byte           | Timer register high byte, Timer enable                    | 60   |

| TIMER_L        | 0xC006  | Word/Byte      | Timer register low byte                                   | 60   |

| XIN            | 0xC005  | Byte           | Thermal error                                             | 66   |

| WTG            | 0xC004  | Word/Byte      | Digital Watchdog tag register                             | 47   |

| WDCTRL         | 0xC003  | Byte           | Digital watchdog control register                         |      |

| WDT            | 0xC002  | Word/Byte      | Digital Watchdog timeout register                         |      |

| VER            | 0xC001  | Byte           | Hardware revision                                         |      |

| VARIOUS        | 0xC000  | Word/Byte/Bit  | System status                                             |      |

Table 8 - Standard Ports Overview

### **LIN Slave Controller for Switches**

Datasheet

### 6. IO Ports

The MLX80104/5 contains two types of ports. All of them are proof to battery voltage.

In case of ECU loss of battery (LOB) and a short of the wiring harness to an external supply line the MLX80104/5 will be reverse powered. Please refer to chapter "Operating under Disturbance".

#### 6.1 Common Features of Pin SWx and IOx

The ports *SW0..9* as well as the ports *IOO..7* allow a very flexible control of up to 18 single switches or a switch matrix or any combination of both, supplied by an internal current source of typically >7mA. The switch control is sequential and periodical, so that only one port will be supplied at the same time.

If switches are placed outside and connected via a wiring harness to the ECU the MLX80104/5 allows full diagnosis of short circuits or broken line.

All ports provide a programmable wake up function and a 10mA open drain low side switch (matrix row connection to GND).

If ports are not used for switch detection, they can be configured passive (tristate behaviour) or as general purpose 10mA open drain output with port monitor. The input thresholds are compatible to 3.3V/5V supply systems. The accuracy of the input threshold allows a monitoring of external voltages without ADC. It allows connection of external supplied encoders, halls or similar.

Furthermore this architecture supports driving of logic output signals for other ECU components via an external pull up resistor as well as the driving of high side or low side loads by providing base current for an external pnp transistor.

Datasheet

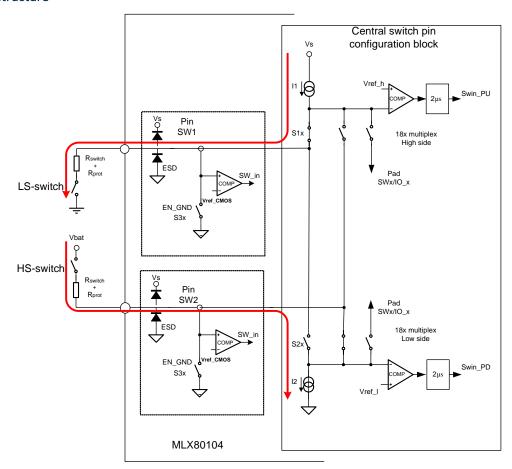

#### 6.1.1. Pin structure

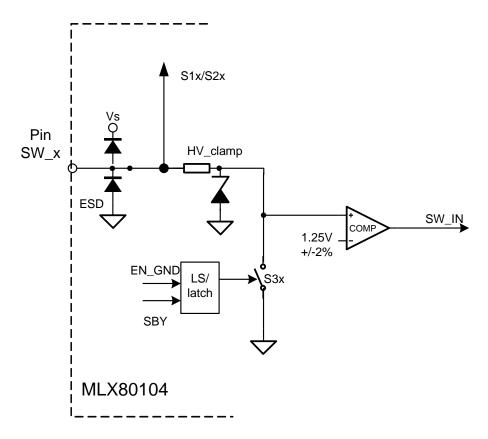

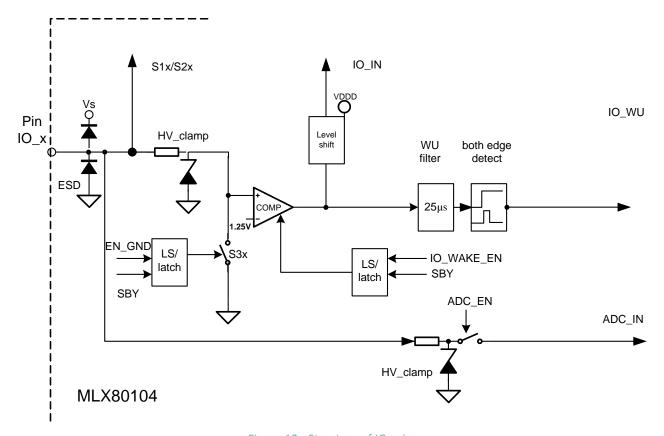

Figure 5 - Common pin Structure SWx and IOx

Figure 5 illustrates the basic structure and control of the ports for switch detection.

The default configuration of all ports after power on or wake up is tristate. After the initialisation procedure the ports will be configured by the MCU. The pull up or pull down current is provided by two central current sources I1 and I2. The currents for switch control have to be applied sequentially by the multiplex switches S1x or S2x. If a low impedance path to Ground is required (open drain buffer or matrix mode row connection), the local switch S3x has to be used.

Because of the multiplex principle only two comparators are required to detect the port input voltage levels. For RF interference as well as suppression of automotive disturbances the comparator path contains a debounce filter of typically  $2\mu s$ .

The multiplex switches S1, S2 as well as the local open drain buffer S3 are controlled by the registers S3H and S3L.

## LIN Slave Controller for Switches

Datasheet

### 6.1.2. Configuration Register Central Current Source

### Status Register pull up/down input comparator - System protected port

| Address | Name   | Bit7 | Bit6 | Bit5             | Bit4                | Bit3             | Bit2           | Bit1    | Bit0    |

|---------|--------|------|------|------------------|---------------------|------------------|----------------|---------|---------|

| 0xE02C  | STATUS | -    | -    | WAKEUP_<br>ERROR | INTERNAL_<br>WAKEUP | LOCAL_<br>WAKEUP | BUS_<br>WAKEUP | SWIN_PU | SWIN_PD |

WAKEUP\_ERROR INTERNAL\_WAKEUP Will be set if during change to sleep mode a switch state change is detected

Wakeup event generated from the internal timer

LOCAL\_WAKEUP Wakeup event generated from a wakeup configured SWx or IOx pin

BUS\_WAKEUP Wakeup event generated from the LIN bus

SWIN\_PD Input comparator of central current source pull down SWIN\_PU Input comparator of central current source pull up

### Central current source configuration

| Address | Name      | Bit7 | Bit6 | Bit5 | Bit4 | Bit3    | Bit2    | Bit1    | Bit0 |

|---------|-----------|------|------|------|------|---------|---------|---------|------|

| 0xC01D  | SW_CONFIG | -    | -    | -    | -    | IREF_EN | DIAG_S2 | DIAG_S1 | -    |

IREF\_EN Switch IREF PIN on/off (0=off)

DIAG\_S2 Configure central pull down current source to 10..20% of nominal value for switch diagnosis

DIAG\_S1 Configure central pull up current source to 10..20% of nominal value for switch diagnosis

### Central current source enable register

| Address | Name  | Bit7   | Bit6   | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0xC01B  | S2H   | IO7_S2 | IO6_S2 | IO5_S2 | IO4_S2 | IO3_S2 | IO2_S2 | IO1_S2 | IO0_S2 |

| 0xC01A  | S1H   | IO7_S1 | IO6_S1 | IO5_S1 | IO4_S1 | IO3_S1 | IO2_S1 | IO1_S1 | IO0_S1 |

| 0xC017  | S2L_H | -      | -      | -      | -      | -      | -      | SW9_S2 | SW8_S2 |

| 0xC016  | S2L_L | SW7_S2 | SW6_S2 | SW5_S2 | SW4_S2 | SW3_S2 | SW2_S2 | SW1_S2 | SW0_S2 |

| 0xC015  | S1L_H | -      | -      | -      | -      | -      | -      | SW9_S1 | SW8_S1 |

| 0xC014  | S1L_L | SW7_S1 | SW6_S1 | SW5_S1 | SW4_S1 | SW3_S1 | SW2_S1 | SW1_S1 | SW0_S1 |

| IOx_S2 | Enable central pull down current source for IOx (S2) – See Figure 5 |

|--------|---------------------------------------------------------------------|

| IOx_S1 | Enable central pull up current source for IOx (S2) – See Figure 5   |

| SWx_S2 | Enable central pull down current source for SWx (S2) – See Figure 5 |

| SWx_S1 | Enable central pull up current source for SWx (S2) – See Figure 5   |

## **LIN Slave Controller for Switches**

Datasheet

### 6.1.3. Configuration Register SWx

### Open drain output configuration register

| Address | Name  | Bit7   | Bit6   | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0xC019  | S3L_H | -      | -      | -      | -      | -      | -      | SW9_S3 | SW8_S3 |

| 0xC018  | S3L_L | SW7_S3 | SW6_S3 | SW5_S3 | SW4_S3 | SW3_S3 | SW2_S3 | SW1_S3 | SW0_S3 |

SWx\_S3 Enables open drain transistor at SWx pin (S3) – See Figure 5

### Input comparator register - System protected ports

| Address | Name    | Bit7   | Bit6   | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |

|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0xE02B  | SW_IN_H | -      | -      | -      | -      | -      | -      | SW_IN9 | SW_IN8 |

| 0xE02A  | SW_IN_L | SW_IN7 | SW_IN6 | SW_IN5 | SW_IN4 | SW_IN3 | SW_IN2 | SW_IN1 | SW_IN0 |

SW\_INx Input comparator of pin SWx

## LIN Slave Controller for Switches

Datasheet

### 6.1.4. Configuration Register IOx

### Open drain output configuration register

| Address | Name | Bit7   | Bit6   | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |

|---------|------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0xC01C  | S3H  | IO7_S3 | IO6_S3 | IO5_S3 | IO4_S3 | IO3_S3 | IO2_S3 | IO1_S3 | IO0_S3 |

IOx\_S3 Enables open drain transistor at IOx pin (S3) – See Figure 5

### Input comparator register - System protected ports

| Address | Name  | Bit7   | Bit6   | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0xE029  | IO_IN | IO7_IN | IO6_IN | IO5_IN | IO4_IN | IO3_IN | IO2_IN | IO1_IN | IO0_IN |

| 0xE026  | IO_EN | IO7_EN | IO6_EN | IO5_EN | IO4_EN | IO3_EN | IO2_EN | IO1_EN | IO0_EN |

IOx\_IN Input comparator of pin IOx IOx\_EN Enables IOx input comparator

### Interrupt register - System protected ports

| Address | Name       | Bit7     | Bit6     | Bit5     | Bit4     | Bit3     | Bit2     | Bit1     | Bit0     |

|---------|------------|----------|----------|----------|----------|----------|----------|----------|----------|

| 0xE027  | IO_IRQ     | IO7_IRQ  | IO6_IRQ  | IO5_IRQ  | IO4_IRQ  | IO3_IRQ  | IO2_IRQ  | IO1_IRQ  | IO0_IRQ  |

| 0xE025  | IO_INT_ENF | IO7_INTF | IO6_INTF | IO5_INTF | IO4_INTF | IO3_INTF | IO2_INTF | IO1_INTF | IO0_INTF |

| 0xE024  | IO_INT_ENR | IO7_INTR | IO6_INTR | IO5_INTR | IO4_INTR | IO3_INTR | IO2_INTR | IO1_INTR | IO0_INTR |

IOx\_IRQ Interrupt source of external interrupt IOx\_INTF Enables falling edge interrupt on IOx IOx\_INTR Enables rising edge interrupt on IOx

## LIN Slave Controller for Switches

Datasheet

### 6.1.5. Switch current generation

The switch level detection is limited by the following criteria:

- Battery voltage range of 5...27V

- GND or VBAT shift < 0.1\*Vs max.

- Applied current >7mA

- For switch matrix mode the voltage drop via the internal GND switch (S3) has to be lower than or equal to the maximum GND shift voltage for a low side input switch

- Contact resistance of the switch up to  $1K\Omega$

- Internal voltage drops (On resistance of multiplex switches, impedance of the current source, supply wiring resistance)

- Failure diagnosis for switches placed outside

In order to meet these requirements, the switch current has to be a function of the battery voltage and must be limited for battery voltages higher than 14V:

Figure 6 - Voltage dependency of the switch current

For normal battery operation voltages of 13..14V, a minimum current of >7mA can be guaranteed. In case of higher battery voltages the current will be limited to <10mA.

### 6.1.6. The switch detection thresholds

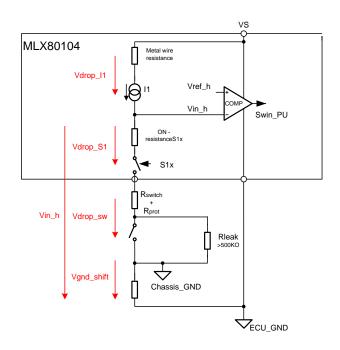

#### LS - switch

|                                | Vbat 14V | Vbat 7V |

|--------------------------------|----------|---------|

| Injection current (calibrated) | 8mA      | 3.5mA   |

| GND shift(0.1*Vbat)            | 1.4V     | 0.7V    |

| Drop switch (1kΩ)              | 8V       | 3.5V    |

| Drop S1(300Ω)                  | 2.4V     | 1.05V   |

| Drop current source I1         | 1V       | 0.5V    |

| Supply voltage Vs              | 13V      | 6V      |

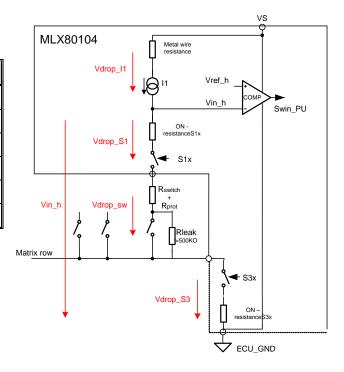

Switch closed: (maximum input low voltage)

(1) Vin\_h = Vgnd\_shift + Vdrop\_sw + Vdrop\_S1

(2) Vin\_h < VS - Vdrop\_I1 < Vref\_h

Switch open: (minimum input high voltage)

(3) Vs > Vin\_h = I1 \* Rleak > Vref\_h

These conditions will be met by Vref\_h = 0.9\*VS

Figure 7 - Voltage drops external LS switch

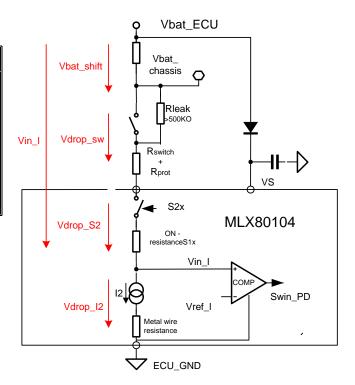

#### **Switch matrix**

|                                | Vbat 14V | Vbat 7V |

|--------------------------------|----------|---------|

| Injection current (calibrated) | 8mA      | 3.5mA   |

| Drop S3(175Ω)                  | 1.4V     | 0.6V    |

| Drop switch (1kΩ)              | 8V       | 3.5V    |

| Drop S1(300Ω)                  | 2.4V     | 1.05V   |

| Drop current source I1         | 1V       | 0.5V    |

| Supply voltage Vs              | 13V      | 6V      |

Switch closed: (maximum input low voltage)

(1) Vin\_h = Vdrop\_S3 + Vdrop\_sw + Vdrop\_S1

(2) Vin\_h < VS - Vdrop\_I1 < Vref\_h

Switch open: (minimum input high voltage)

(3) Vs > Vin\_h = I1 \* Rleak > Vref\_h

These conditions will be met by Vref\_h = 0.9\*VS

Figure 8 - Voltage drops switch matrix

Datasheet

### HS - switch

|                                | Vbat 14V | Vbat 7V |

|--------------------------------|----------|---------|

| Injection current (calibrated) | 8mA      | 3.5mA   |

| Vbat shift(0.1*Vbat)           | 1.4V     | 0.7V    |

| Drop switch (1kΩ)              | 8V       | 3.5V    |

| Drop S2(300Ω)                  | 2.4V     | 1.05V   |

| Drop current source I2         | 1V       | 0.5V    |

| Supply voltage Vs              | 13V      | 6V      |

Switch closed: (minimum input high voltage)

(1) Vbat-Vin\_I = Vdrop\_S2 + Vdrop\_sw + Vbat\_shift

(2) Vbat-Vin\_I < Vdrop\_I2 > Vref\_I

Switch open: (maximum input low voltage)