#### **Features**

- Compatible with MCS®-51Products

- 2K Bytes of Reprogrammable Flash Memory

- Endurance: 10,000 Write/Erase Cycles

- 2.7V to 6V Operating Range

- Fully Static Operation: 0 Hz to 24 MHz

- Two-level Program Memory Lock

- 128 x 8-bit Internal RAM

- 15 Programmable I/O Lines

- Two 16-bit Timer/Counters

- Six Interrupt Sources

- Programmable Serial UART Channel

- Direct LED Drive Outputs

- On-chip Analog Comparator

- Low-power Idle and Power-down Modes

- Green (Pb/Halide-free) Packaging Option

### 1. Description

The AT89C2051 is a low-voltage, high-performance CMOS 8-bit microcomputer with 2K bytes of Flash programmable and erasable read-only memory (PEROM). The device is manufactured using Atmel's high-density nonvolatile memory technology and is compatible with the industry-standard MCS-51 instruction set. By combining a versatile 8-bit CPU with Flash on a monolithic chip, the Atmel AT89C2051 is a powerful microcomputer which provides a highly-flexible and cost-effective solution to many embedded control applications.

The AT89C2051 provides the following standard features: 2K bytes of Flash, 128 bytes of RAM, 15 I/O lines, two 16-bit timer/counters, a five vector two-level interrupt architecture, a full duplex serial port, a precision analog comparator, on-chip oscillator and clock circuitry. In addition, the AT89C2051 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port and interrupt system to continue functioning. The power-down mode saves the RAM contents but freezes the oscillator disabling all other chip functions until the next hardware reset.

# 8-bit Microcontroller with 2K Bytes Flash

## AT89C2051

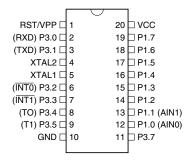

## 2. Pin Configuration

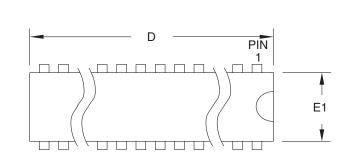

#### 2.1 20-lead PDIP/SOIC

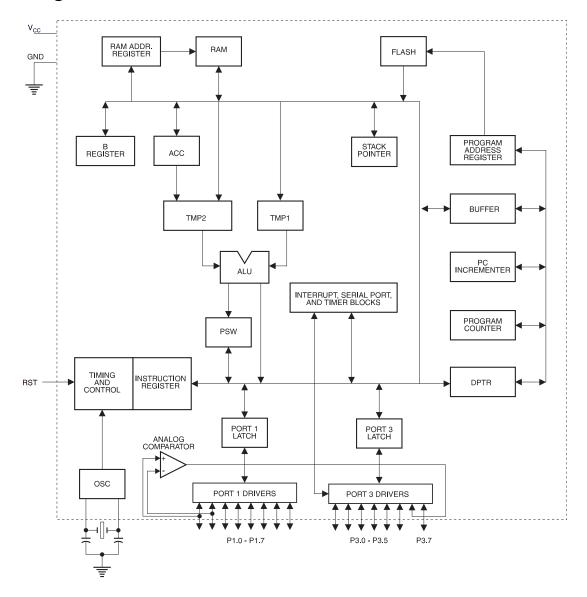

## 3. Block Diagram

2

## 4. Pin Description

4.1 VCC

Supply voltage.

4.2 GND

Ground.

#### 4.3 Port 1

The Port 1 is an 8-bit bi-directional I/O port. Port pins P1.2 to P1.7 provide internal pull-ups. P1.0 and P1.1 require external pull-ups. P1.0 and P1.1 also serve as the positive input (AIN0) and the negative input (AIN1), respectively, of the on-chip precision analog comparator. The Port 1 output buffers can sink 20 mA and can drive LED displays directly. When 1s are written to Port 1 pins, they can be used as inputs. When pins P1.2 to P1.7 are used as inputs and are externally pulled low, they will source current ( $I_{II}$ ) because of the internal pull-ups.

Port 1 also receives code data during Flash programming and verification.

#### 4.4 Port 3

Port 3 pins P3.0 to P3.5, P3.7 are seven bi-directional I/O pins with internal pull-ups. P3.6 is hard-wired as an input to the output of the on-chip comparator and is not accessible as a general-purpose I/O pin. The Port 3 output buffers can sink 20 mA. When 1s are written to Port 3 pins they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current ( $I_{II}$ ) because of the pull-ups.

Port 3 also serves the functions of various special features of the AT89C2051 as listed below:

| Port Pin | Alternate Functions         |

|----------|-----------------------------|

| P3.0     | RXD (serial input port)     |

| P3.1     | TXD (serial output port)    |

| P3.2     | INT0 (external interrupt 0) |

| P3.3     | INT1 (external interrupt 1) |

| P3.4     | T0 (timer 0 external input) |

| P3.5     | T1 (timer 1 external input) |

Port 3 also receives some control signals for Flash programming and verification.

#### 4.5 RST

Reset input. All I/O pins are reset to 1s as soon as RST goes high. Holding the RST pin high for two machine cycles while the oscillator is running resets the device.

Each machine cycle takes 12 oscillator or clock cycles.

#### 4.6 XTAL1

Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

#### 4.7 XTAL2

Output from the inverting oscillator amplifier.

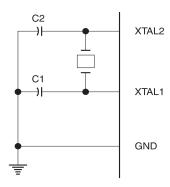

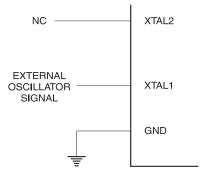

#### 5. Oscillator Characteristics

The XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in Figure 5-1. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 5-2. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low time specifications must be observed.

Figure 5-1. Oscillator Connections

Note: C1, C2 = 30 pF  $\pm$  10 pF for Crystals = 40 pF  $\pm$  10 pF for Ceramic Resonators

Figure 5-2. External Clock Drive Configuration

## 6. Special Function Registers

A map of the on-chip memory area called the Special Function Register (SFR) space is shown in the table below.

Note that not all of the addresses are occupied, and unoccupied addresses may not be implemented on the chip. Read accesses to these addresses will in general return random data, and write accesses will have an indeterminate effect.

User software should not write 1s to these unlisted locations, since they may be used in future products to invoke new features. In that case, the reset or inactive values of the new bits will always be 0.

Table 6-1. AT89C2051 SFR Map and Reset Values

|      |                  |                  |                 |                 |                 |                 |                  | •    |

|------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|------------------|------|

| 0F8H |                  |                  |                 |                 |                 |                 |                  | 0FFH |

| 0F0H | B<br>00000000    |                  |                 |                 |                 |                 |                  | 0F7H |

| 0E8H |                  |                  |                 |                 |                 |                 |                  | 0EFH |

| 0E0H | ACC<br>00000000  |                  |                 |                 |                 |                 |                  | 0E7H |

| 0D8H |                  |                  |                 |                 |                 |                 |                  | 0DFH |

| 0D0H | PSW<br>00000000  |                  |                 |                 |                 |                 |                  | 0D7H |

| 0C8H |                  |                  |                 |                 |                 |                 |                  | 0CFH |

| 0C0H |                  |                  |                 |                 |                 |                 |                  | 0C7H |

| 0B8H | IP<br>XXX00000   |                  |                 |                 |                 |                 |                  | 0BFH |

| 0B0H | P3<br>11111111   |                  |                 |                 |                 |                 |                  | 0B7H |

| H8A0 | IE<br>0XX00000   |                  |                 |                 |                 |                 |                  | 0AFH |

| 0A0H |                  |                  |                 |                 |                 |                 |                  | 0A7H |

| 98H  | SCON<br>00000000 | SBUF<br>XXXXXXXX |                 |                 |                 |                 |                  | 9FH  |

| 90H  | P1<br>11111111   |                  |                 |                 |                 |                 |                  | 97H  |

| 88H  | TCON<br>00000000 | TMOD<br>00000000 | TL0<br>00000000 | TL1<br>00000000 | TH0<br>00000000 | TH1<br>00000000 |                  | 8FH  |

| 80H  |                  | SP<br>00000111   | DPL<br>00000000 | DPH<br>00000000 |                 |                 | PCON<br>0XXX0000 | 87H  |

#### 7. Restrictions on Certain Instructions

The AT89C2051 and is an economical and cost-effective member of Atmel's growing family of microcontrollers. It contains 2K bytes of Flash program memory. It is fully compatible with the MCS-51 architecture, and can be programmed using the MCS-51 instruction set. However, there are a few considerations one must keep in mind when utilizing certain instructions to program this device.

All the instructions related to jumping or branching should be restricted such that the destination address falls within the physical program memory space of the device, which is 2K for the AT89C2051. This should be the responsibility of the software programmer. For example, LJMP 7E0H would be a valid instruction for the AT89C2051 (with 2K of memory), whereas LJMP 900H would not.

#### 7.1 Branching Instructions

LCALL, LJMP, ACALL, AJMP, SJMP, JMP @A+DPTR — These unconditional branching instructions will execute correctly as long as the programmer keeps in mind that the destination branching address must fall within the physical boundaries of the program memory size (locations 00H to 7FFH for the 89C2051). Violating the physical space limits may cause unknown program behavior.

**CJNE** [...], **DJNZ** [...], **JB**, **JNB**, **JC**, **JNC**, **JBC**, **JZ**, **JNZ** – With these conditional branching instructions the same rule above applies. Again, violating the memory boundaries may cause erratic execution.

For applications involving interrupts the normal interrupt service routine address locations of the 80C51 family architecture have been preserved.

#### 7.2 MOVX-related Instructions, Data Memory

The AT89C2051 contains 128 bytes of internal data memory. Thus, in the AT89C2051 the stack depth is limited to 128 bytes, the amount of available RAM. External DATA memory access is not supported in this device, nor is external PROGRAM memory execution. Therefore, no MOVX [...] instructions should be included in the program.

A typical 80C51 assembler will still assemble instructions, even if they are written in violation of the restrictions mentioned above. It is the responsibility of the controller user to know the physical features and limitations of the device being used and adjust the instructions used correspondingly.

## 8. Program Memory Lock Bits

On the chip are two lock bits which can be left unprogrammed (U) or can be programmed (P) to obtain the additional features listed in the Table 8-1.

**Table 8-1.** Lock Bit Protection Modes<sup>(1)</sup>

| Program Lock Bits |   |     |                                              |

|-------------------|---|-----|----------------------------------------------|

| LB1 LB2           |   | LB2 | Protection Type                              |

| 1                 | U | U   | No program lock features                     |

| 2                 | Р | U   | Further programming of the Flash is disabled |

| 3                 | Р | Р   | Same as mode 2, also verify is disabled      |

Note: 1. The Lock Bits can only be erased with the Chip Erase operation.

#### 9. Idle Mode

In idle mode, the CPU puts itself to sleep while all the on-chip peripherals remain active. The mode is invoked by software. The content of the on-chip RAM and all the special functions registers remain unchanged during this mode. The idle mode can be terminated by any enabled interrupt or by a hardware reset.

The P1.0 and P1.1 should be set to "0" if no external pull-ups are used, or set to "1" if external pull-ups are used.

It should be noted that when idle is terminated by a hardware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a port pin when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory.

#### 10. Power-down Mode

In the power-down mode the oscillator is stopped, and the instruction that invokes power-down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values until the power-down mode is terminated. The only exit from power-down is a hardware reset. Reset redefines the SFRs but does not change the on-chip RAM. The reset should not be activated before  $V_{\rm CC}$  is restored to its normal operating level and must be held active long enough to allow the oscillator to restart and stabilize.

The P1.0 and P1.1 should be set to "0" if no external pull-ups are used, or set to "1" if external pull-ups are used.

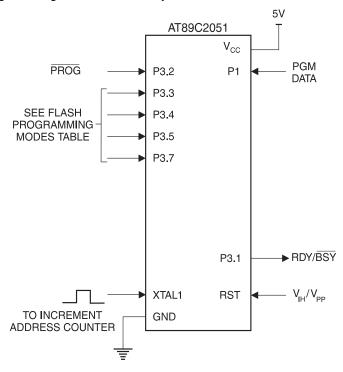

## 11. Programming The Flash

The AT89C2051 is shipped with the 2K bytes of on-chip PEROM code memory array in the erased state (i.e., contents = FFH) and ready to be programmed. The code memory array is programmed one byte at a time. Once the array is programmed, to re-program any non-blank byte, the entire memory array needs to be erased electrically.

**Internal Address Counter:** The AT89C2051 contains an internal PEROM address counter which is always reset to 000H on the rising edge of RST and is advanced by applying a positive going pulse to pin XTAL1.

**Programming Algorithm:** To program the AT89C2051, the following sequence is recommended.

- Power-up sequence: Apply power between V<sub>CC</sub> and GND pins Set RST and XTAL1 to GND

- 2. Set pin RST to "H" Set pin P3.2 to "H"

- 3. Apply the appropriate combination of "H" or "L" logic levels to pins P3.3, P3.4, P3.5, P3.7 to select one of the programming operations shown in the PEROM Programming Modes table.

To Program and Verify the Array:

- 4. Apply data for Code byte at location 000H to P1.0 to P1.7.

- 5. Raise RST to 12V to enable programming.

- 6. Pulse P3.2 once to program a byte in the PEROM array or the lock bits. The byte-write cycle is self-timed and typically takes 1.2 ms.

- 7. To verify the programmed data, lower RST from 12V to logic "H" level and set pins P3.3 to P3.7 to the appropriate levels. Output data can be read at the port P1 pins.

- 8. To program a byte at the next address location, pulse XTAL1 pin once to advance the internal address counter. Apply new data to the port P1 pins.

- 9. Repeat steps 6 through 8, changing data and advancing the address counter for the entire 2K bytes array or until the end of the object file is reached.

- Power-off sequence: set XTAL1 to "L" set RST to "L" Turn V<sub>CC</sub> power off

Data Polling: The AT89C2051 features Data Polling to indicate the end of a write cycle. During a write cycle, an attempted read of the last byte written will result in the complement of the written data on P1.7. Once the write cycle has been completed, true data is valid on all outputs, and the next cycle may begin. Data Polling may begin any time after a write cycle has been initiated.

**Ready/Busy:** The Progress of byte programming can also be monitored by the RDY/BSY output signal. Pin P3.1 is pulled low after P3.2 goes High during programming to indicate BUSY. P3.1 is pulled High again when programming is done to indicate READY.

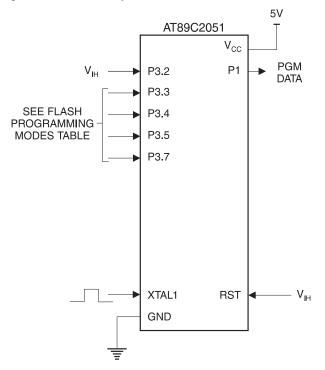

**Program Verify:** If lock bits LB1 and LB2 have not been programmed code data can be read back via the data lines for verification:

- 1. Reset the internal address counter to 000H by bringing RST from "L" to "H".

- 2. Apply the appropriate control signals for Read Code data and read the output data at the port P1 pins.

- 3. Pulse pin XTAL1 once to advance the internal address counter.

- 4. Read the next code data byte at the port P1 pins.

- 5. Repeat steps 3 and 4 until the entire array is read.

The lock bits cannot be verified directly. Verification of the lock bits is achieved by observing that their features are enabled.

**Chip Erase:** The entire PEROM array (2K bytes) and the two Lock Bits are erased electrically by using the proper combination of control signals and by holding P3.2 low for 10 ms. The code array is written with all "1"s in the Chip Erase operation and must be executed before any non-blank memory byte can be re-programmed.

**Reading the Signature Bytes:** The signature bytes are read by the same procedure as a normal verification of locations 000H, 001H, and 002H, except that P3.5 and P3.7 must be pulled to a logic low. The values returned are as follows.

```

(000H) = 1EH indicates manufactured by Atmel (001H) = 21H indicates 89C2051

```

## 12. Programming Interface

Every code byte in the Flash array can be written and the entire array can be erased by using the appropriate combination of control signals. The write operation cycle is self-timed and once initiated, will automatically time itself to completion.

Most major worldwide programming vendors offer support for the Atmel AT89 microcontroller series. Please contact your local programming vendor for the appropriate software revision.

## 13. Flash Programming Modes

| Mode                              |         | RST/VPP | P3.2/PROG | P3.3 | P3.4 | P3.5 | P3.7 |

|-----------------------------------|---------|---------|-----------|------|------|------|------|

| Write Code Data <sup>(1)(3)</sup> |         | 12V     |           | L    | Н    | Н    | Н    |

| Read Code Data <sup>(1)</sup>     |         | Н       | Н         | L    | L    | Н    | Н    |

| Meita Lagle                       | Bit - 1 | 12V     |           | Н    | Н    | н    | Н    |

| Write Lock                        | Bit - 2 | 12V     |           | Н    | Н    | L    | L    |

| Chip Erase                        |         | 12V     | (2)       | Н    | L    | L    | L    |

| Read Signature Byte               |         | Н       | Н         | L    | L    | L    | L    |

Notes: 1. The internal PEROM address counter is reset to 000H on the rising edge of RST and is advanced by a positive pulse at XTAL1 pin.

- 2. Chip Erase requires a 10 ms PROG pulse.

- 3. P3.1 is pulled Low during programming to indicate RDY/BSY.

Figure 13-1. Programming the Flash Memory

Figure 13-2. Verifying the Flash Memory

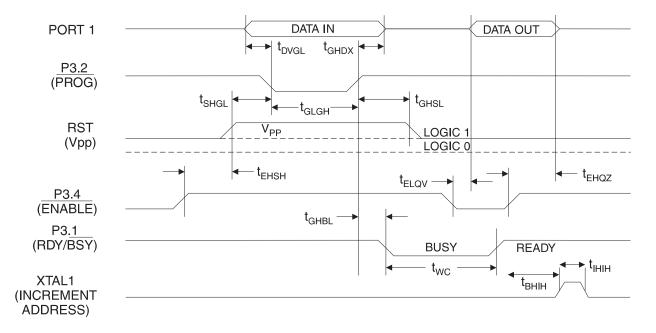

# 14. Flash Programming and Verification Characteristics

$T_A = 0$ °C to 70°C,  $V_{CC} = 5.0 \pm 10\%$

| Symbol            | Parameter                                      | Min  | Max  | Units |

|-------------------|------------------------------------------------|------|------|-------|

| V <sub>PP</sub>   | Programming Enable Voltage                     | 11.5 | 12.5 | V     |

| I <sub>PP</sub>   | Programming Enable Current                     |      | 250  | μA    |

| t <sub>DVGL</sub> | Data Setup to PROG Low                         | 1.0  |      | μs    |

| t <sub>GHDX</sub> | Data Hold after PROG                           | 1.0  |      | μs    |

| t <sub>EHSH</sub> | P3.4 (ENABLE) High to V <sub>PP</sub>          | 1.0  |      | μs    |

| t <sub>SHGL</sub> | V <sub>PP</sub> Setup to PROG Low              | 10   |      | μs    |

| t <sub>GHSL</sub> | V <sub>PP</sub> Hold after PROG                | 10   |      | μs    |

| t <sub>GLGH</sub> | PROG Width                                     | 1    | 110  | μs    |

| t <sub>ELQV</sub> | ENABLE Low to Data Valid                       |      | 1.0  | μs    |

| t <sub>EHQZ</sub> | Data Float after ENABLE                        | 0    | 1.0  | μs    |

| t <sub>GHBL</sub> | PROG High to BUSY Low                          |      | 50   | ns    |

| t <sub>WC</sub>   | Byte Write Cycle Time                          |      | 2.0  | ms    |

| t <sub>BHIH</sub> | RDY/ <del>BSY</del> \ to Increment Clock Delay | 1.0  |      | μs    |

| t <sub>IHIL</sub> | Increment Clock High                           | 200  |      | ns    |

Note: 1. Only used in 12-volt programming mode.

# 15. Flash Programming and Verification Waveforms

## 16. Absolute Maximum Ratings\*

| Operating Temperature                     | -55°C to +125°C |

|-------------------------------------------|-----------------|

| Storage Temperature                       | -65°C to +150°C |

| Voltage on Any Pin with Respect to Ground | 1.0V to +7.0V   |

| Maximum Operating Voltage                 | 6.6V            |

| DC Output Current                         | 25.0 mA         |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## 17. DC Characteristics

$T_A = -40$ °C to 85°C,  $V_{CC} = 2.7$ V to 6.0V (unless otherwise noted)

| Symbol           | Parameter                                         | Condition                                                                         | Min                       | Max                       | Units |

|------------------|---------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------|---------------------------|-------|

| V <sub>IL</sub>  | Input Low-voltage                                 |                                                                                   | -0.5                      | 0.2 V <sub>CC</sub> - 0.1 | V     |

| V <sub>IH</sub>  | Input High-voltage                                | (Except XTAL1, RST)                                                               | 0.2 V <sub>CC</sub> + 0.9 | V <sub>CC</sub> + 0.5     | V     |

| V <sub>IH1</sub> | Input High-voltage                                | (XTAL1, RST)                                                                      | 0.7 V <sub>CC</sub>       | V <sub>CC</sub> + 0.5     | V     |

| V <sub>OL</sub>  | Output Low-voltage <sup>(1)</sup><br>(Ports 1, 3) | $I_{OL} = 20 \text{ mA}, V_{CC} = 5V$<br>$I_{OL} = 10 \text{ mA}, V_{CC} = 2.7V$  |                           | 0.5                       | V     |

|                  |                                                   | $I_{OH} = -80 \mu A, V_{CC} = 5V \pm 10\%$                                        | 2.4                       |                           | V     |

| $V_{OH}$         | Output High-voltage (Ports 1, 3)                  | I <sub>OH</sub> = -30 μA                                                          | 0.75 V <sub>CC</sub>      |                           | V     |

|                  | (1 0110 1, 0)                                     | I <sub>OH</sub> = -12 μA                                                          | 0.9 V <sub>CC</sub>       |                           | V     |

| I <sub>IL</sub>  | Logical 0 Input Current (Ports 1, 3)              | V <sub>IN</sub> = 0.45V                                                           |                           | -50                       | μΑ    |

| I <sub>TL</sub>  | Logical 1 to 0 Transition Current (Ports 1, 3)    | $V_{IN} = 2V, V_{CC} = 5V \pm 10\%$                                               |                           | -750                      | μΑ    |

| I <sub>LI</sub>  | Input Leakage Current<br>(Port P1.0, P1.1)        | 0 < V <sub>IN</sub> < V <sub>CC</sub>                                             |                           | ±10                       | μΑ    |

| V <sub>OS</sub>  | Comparator Input Offset Voltage                   | V <sub>CC</sub> = 5V                                                              |                           | 20                        | mV    |

| V <sub>CM</sub>  | Comparator Input Common<br>Mode Voltage           |                                                                                   | 0                         | V <sub>cc</sub>           | V     |

| RRST             | Reset Pull-down Resistor                          |                                                                                   | 50                        | 300                       | kΩ    |

| C <sub>IO</sub>  | Pin Capacitance                                   | Test Freq. = 1 MHz, T <sub>A</sub> = 25°C                                         |                           | 10                        | pF    |

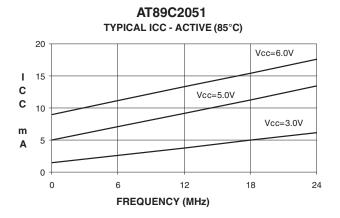

|                  |                                                   | Active Mode, 12 MHz, V <sub>CC</sub> = 6V/3V                                      |                           | 15/5.5                    | mA    |

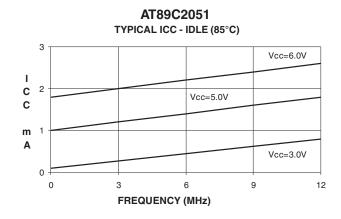

| I <sub>cc</sub>  | Power Supply Current                              | Idle Mode, 12 MHz, V <sub>CC</sub> = 6V/3V<br>P1.0 & P1.1 = 0V or V <sub>CC</sub> |                           | 5/1                       | mA    |

| -0               | Davier davis Mada(2)                              | V <sub>CC</sub> = 6V, P1.0 & P1.1 = 0V or V <sub>CC</sub>                         |                           | 100                       | μA    |

|                  | Power-down Mode <sup>(2)</sup>                    | V <sub>CC</sub> = 3V, P1.0 & P1.1 = 0V or V <sub>CC</sub>                         |                           | 20                        | μA    |

Notes: 1. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

Maximum I<sub>OL</sub> per port pin: 20 mA

Maximum total I<sub>OL</sub> for all output pins: 80 mA

If I<sub>OL</sub> exceeds the test condition, V<sub>OL</sub> may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

2. Minimum V<sub>CC</sub> for Power-down is 2V.

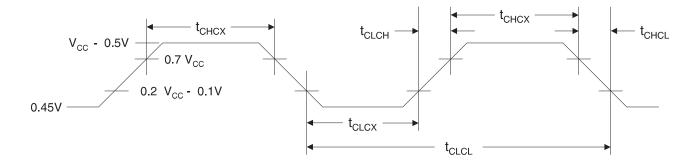

## 18. External Clock Drive Waveforms

## 19. External Clock Drive

|                     |                      | V <sub>CC</sub> = 2.7V to 6.0V |     | $V_{CC} = 4.0V \text{ to } 6.0V$ |     |       |

|---------------------|----------------------|--------------------------------|-----|----------------------------------|-----|-------|

| Symbol              | Parameter            | Min                            | Max | Min                              | Max | Units |

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0                              | 12  | 0                                | 24  | MHz   |

| t <sub>CLCL</sub>   | Clock Period         | 83.3                           |     | 41.6                             |     | ns    |

| t <sub>CHCX</sub>   | High Time            | 30                             |     | 15                               |     | ns    |

| t <sub>CLCX</sub>   | Low Time             | 30                             |     | 15                               |     | ns    |

| t <sub>CLCH</sub>   | Rise Time            |                                | 20  |                                  | 20  | ns    |

| t <sub>CHCL</sub>   | Fall Time            |                                | 20  |                                  | 20  | ns    |

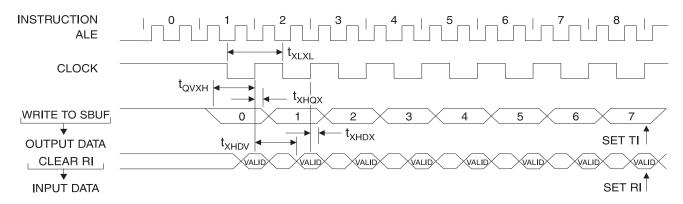

# 20. Serial Port Timing: Shift Register Mode Test Conditions

$V_{CC}$  = 5.0V ±20%; Load Capacitance = 80 pF

|                   |                                          | 12 MI | 12 MHz Osc Variable Oscillator |                           | Oscillator                |       |

|-------------------|------------------------------------------|-------|--------------------------------|---------------------------|---------------------------|-------|

| Symbol            | Parameter                                | Min   | Max                            | Min                       | Max                       | Units |

| t <sub>XLXL</sub> | Serial Port Clock Cycle Time             | 1.0   |                                | 12 t <sub>CLCL</sub>      |                           | μs    |

| t <sub>QVXH</sub> | Output Data Setup to Clock Rising Edge   | 700   |                                | 10 t <sub>CLCL</sub> -133 |                           | ns    |

| t <sub>XHQX</sub> | Output Data Hold after Clock Rising Edge | 50    |                                | 2 t <sub>CLCL</sub> -117  |                           | ns    |

| t <sub>XHDX</sub> | Input Data Hold after Clock Rising Edge  | 0     |                                | 0                         |                           | ns    |

| t <sub>XHDV</sub> | Clock Rising Edge to Input Data Valid    |       | 700                            |                           | 10 t <sub>CLCL</sub> -133 | ns    |

## 21. Shift Register Mode Timing Waveforms

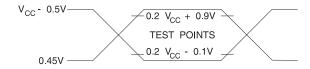

# 22. AC Testing Input/Output Waveforms<sup>(1)</sup>

Note: 1. AC Inputs during testing are driven at V<sub>CC</sub> - 0.5V for a logic 1 and 0.45V for a logic 0. Timing measurements are made at V<sub>IH</sub> min. for a logic 1 and V<sub>IL</sub> max. for a logic 0.

## 23. Float Waveforms<sup>(1)</sup>

Note: 1. For timing purposes, a port pin is no longer floating when a 100 mV change from load voltage occurs. A port pin begins to float when 100 mV change from the loaded V<sub>OH</sub>/V<sub>OL</sub> level occurs.

# 24. I<sub>CC</sub> (Active Mode) Measurements

# 25. $I_{CC}$ (Idle Mode) Measurements

# 26. I<sub>CC</sub> (Power Down Mode) Measurements

AT89C2051

TYPICAL ICC vs. VOLTAGE- POWER DOWN (85°C)

1 15

C C 10

H A 5

0 3.0V 4.0V 5.0V 6.0V

Vcc VOLTAGE

Notes: 1. XTAL1 tied to GND

2. P.1.0 and P1.1 =  $V_{CC}$  or GND

3. Lock bits programmed

# 27. Ordering Information

# 27.1 Green Package Option (Pb/Halide-free)

| Speed<br>(MHz) | Power<br>Supply | Ordering Code                    | Package     | Operation Range                 |

|----------------|-----------------|----------------------------------|-------------|---------------------------------|

| 12             | 2.7V to 6.0V    | AT89C2051-12PU<br>AT89C2051-12SU | 20P3<br>20S | Industrial<br>(-40° C to 85° C) |

| 24             | 4.0V to 6.0V    | AT89C2051-24PU<br>AT89C2051-24SU | 20P3<br>20S | Industrial<br>(-40° C to 85° C) |

| Package Type |                                                              |  |  |  |

|--------------|--------------------------------------------------------------|--|--|--|

| 20P3         | 20-lead, 0.300" Wide, Plastic Dual In-line Package (PDIP)    |  |  |  |

| 20S          | 20-lead, 0.300" Wide, Plastic Gull Wing Small Outline (SOIC) |  |  |  |

# 28. Package Information

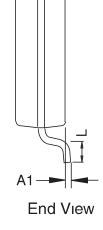

#### 28.1 20P3 - PDIP

- 1. This package conforms to JEDEC reference MS-001, Variation AD.

- 2. Dimensions D and E1 do not include mold Flash or Protrusion. Mold Flash or Protrusion shall not exceed 0.25 mm (0.010").

### **COMMON DIMENSIONS**

(Unit of Measure = mm)

| SYMBOL | MIN    | NOM     | MAX    | NOTE   |

|--------|--------|---------|--------|--------|

| Α      | _      | _       | 5.334  |        |

| A1     | 0.381  | _       | _      |        |

| D      | 24.892 | _       | 26.924 | Note 2 |

| E      | 7.620  | _       | 8.255  |        |

| E1     | 6.096  | _       | 7.112  | Note 2 |

| В      | 0.356  | _       | 0.559  |        |

| B1     | 1.270  | _       | 1.551  |        |

| L      | 2.921  | _       | 3.810  |        |

| С      | 0.203  | _       | 0.356  |        |

| eB     | -      | _       | 10.922 |        |

| eC     | 0.000  | _       | 1.524  |        |

| е      |        | 2.540 7 | YP     |        |

1/23/04

| TITLE |                                                 |         |      |

|-------|-------------------------------------------------|---------|------|

|       | 20-lead (0.300"/7.62 mm Wide)<br>Package (PDIP) | Plastic | Dual |

| DRAWING NO. | REV. |  |

|-------------|------|--|

| 20P3        | D    |  |

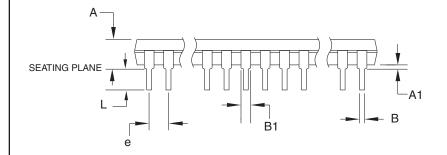

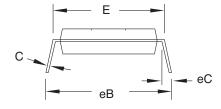

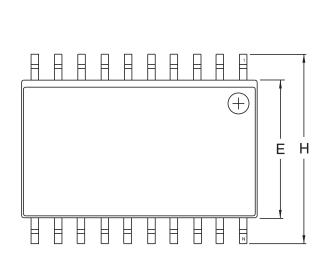

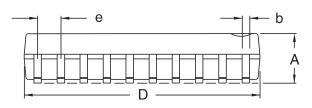

#### 28.2 20S - SOIC

Side View

## **COMMON DIMENSIONS**

(Unit of Measure - mm)

| SYMBOL | MIN      | NOM | MAX   | NOTE |

|--------|----------|-----|-------|------|

| Α      | 2.35     |     | 2.65  |      |

| A1     | 0.10     |     | 0.30  |      |

| b      | 0.33     |     | 0.51  | 4    |

| С      | 0.23     |     | 0.32  |      |

| D      | 12.60    |     | 13.00 | 1    |

| Е      | 7.40     |     | 7.60  | 2    |

| Н      | 10.00    |     | 10.65 |      |

| L      | 0.40     |     | 1.27  | 3    |

| е      | 1.27 BSC |     |       |      |

Notes. 1. This drawing is for general information only; refer to JEDEC Drawing MS-013, Variation AC for additional information.

- 2. Dimension 'D' does not include mold Flash, protrusions or gate burrs. Mold Flash, protrusions and gate burrs shall not exceed 0.15 mm (0.006') per side.

- 3. Dimension 'E' does not include inter-lead Flash or protrusion. Inter-lead Flash and protrusions shall not exceed 0.25 mm (0.010') per side.

- 4. 'L' is the length of the terminal for soldering to a substrate.

- 4. 'L' is the length of the terminal for soldering to a substrate.

5. The lead width 'b', as measured 0.36 mm (0.014') or greater above the seating plane, shall not exceed a maximum value of 0.61 mm. 11/6/06 (0.024') per side.

|                                            | TITLE                                                                                   | DRAWING NO. | REV. |

|--------------------------------------------|-----------------------------------------------------------------------------------------|-------------|------|

| 2325 Orchard Parkway<br>San Jose, CA 95131 | <b>20S2</b> , 20-lead, 0.300' Wide Body, Plastic Gull Wing Small Outline Package (SOIC) | 20S2        | В    |

AT89C2051

#### Headquarters

Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA

Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369 Atmel Europe

Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex

France

Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site

www.atmel.com

Technical Support mcu@atmel.com

Sales Contact

www.atmel.com/contacts

Literature Requests

www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2008 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Microchip Technology