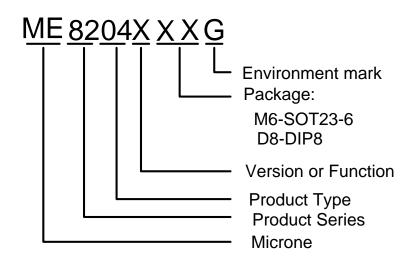

## **Current Mode PWM Controller With Frequency Shuffling ME8204 Series**

## **General Description**

ME8204 is a highly integrated current mode PWM control IC optimized for high performance, low standby power (<100mW) and cost effective offline flyback converter applications in 40W~60W range. ME8204 offers complete protection coverage with self-recovery feature automatic including Cycle-by-Cycle current limiting (OCP), CS short protection, over load protection (OLP), and VDD under voltage lockout (UVLO) and latch feature including over temperature protection (OTP), over voltage (fixed or adjustable) protection(OVP). Excellent EMI performance is achieved with frequency shuffling technique together with soft switching control at the totem pole gate drive output. Tone energy at below 20KHz is minimized in the design and audio noise is eliminated during operation.

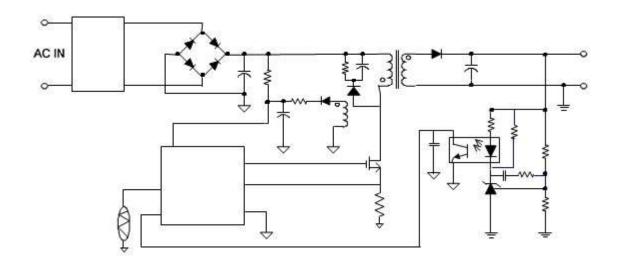

## **Typical Application**

Offline AC/DC flyback converter for

- AC/DC adapter

- PDA power supplies

- Digital cameras and camcorder adapter

- VCR,SVR, STB, DVD&DVCD player SMPS

- Set-top box power

- Auxiliary power supply for PC and server

- Open-frame SMPS

## **Features**

- Power on Soft Start Reducing MOSFET V<sub>DS</sub> Stress

- Frequency shuffling for EMI

- Audio Noise Free Operation

- Extended Burst Mode Control For Improved

Efficiency and Minimum Standby Power Design

- •Internal Synchronized Slope Compensation

- Fixed 65KHz Switching Frequency (8204, 8204B)

- Fixed 100KHz Switching Frequency (8204C)

- Good protection coverage with auto self-recovery

- \* VDD Under Voltage Lockout with Hysteresis (UVLO)

- \* Over Temperature Protection (OTP) with latch shut down(8204) or auto-recovery(8204B,8204C)

- \* Cycle-by-cycle over current threshold setting for constant output power limiting over universal input voltage range

- \* Overload Protection (OLP) with auto-recovery

- \* VDD Over voltage Protection(OVP) with latch shut down(8204) or auto-recovery(8204B.8204C)

- \* Adjustable OVP through external Zener

- \* CS floating protection with auto-recovery

- \* CS short protection with auto-recovery

## **Package**

- 6-pin SOT23-6

- 8-pin DIP8

# **Typical Application**

## **Selection Guide**

| Product Series | VDD OVP       | ОТР                 | Frequency  | Package |  |

|----------------|---------------|---------------------|------------|---------|--|

| ME8204M6G      | Latch         | Latch               | atch 65KHz |         |  |

| ME8204BM6G     | Auto-recovery | Auto-recovery 65KHz |            | SOT23-6 |  |

| ME8204BD8G     | Auto-recovery | Auto-recovery       | 65KHz      | DIP8    |  |

| ME8204CM6G     | Auto-recovery | Auto-recovery       | 100KHz     | SOT23-6 |  |

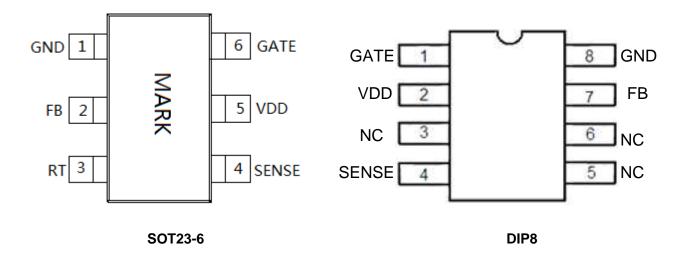

# **Pin Configuration**

# **PIN Assignments**

| Pin Num.<br>(SOT23-6) | Pin Num.<br>(DIP8) | Symbol | Description                                                                                                                                                                                |

|-----------------------|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                     | 8                  | GND    | Ground                                                                                                                                                                                     |

| 2                     | 7                  | FB     | Feedback input pin. The PWM duty cycle is determined by voltage level into this pin and the current-sense signal at PIN 3.                                                                 |

| 3                     |                    | RT     | Dual function PIN. Either connected through a NTC resistor to ground for over temperature shutdown/latch control or connected through Zener to VDD for adjustable over voltage protection. |

| 4                     | 4                  | SENSE  | Current sense input pin. Connected to MOSFET current sensing resistor node.                                                                                                                |

| 5                     | 2                  | VDD    | Chip DC power supply pin.                                                                                                                                                                  |

| 6                     | 1                  | GATE   | Totem-pole gate drive output for the power MOSFET.                                                                                                                                         |

|                       | 3,5,6              | NC     | No connect                                                                                                                                                                                 |

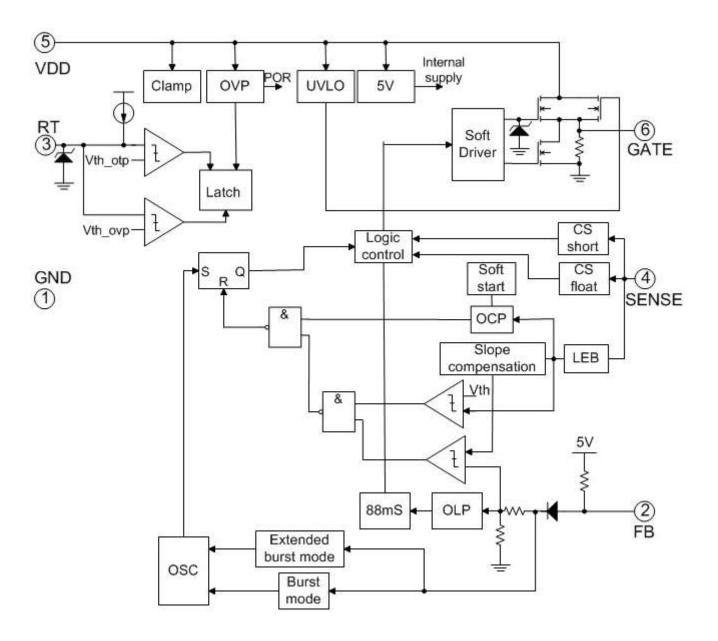

## **Block Diagram**

## **Absolute Maximum Ratings**

| Parameter                                                                                                          | Rai                    | Unit |      |

|--------------------------------------------------------------------------------------------------------------------|------------------------|------|------|

| VDD/VIN DC Supply Voltage                                                                                          | 4                      | V    |      |

| VDD Zener Clamp Voltage <sup>Note</sup>                                                                            | VDD_Cla                | V    |      |

| VDD DC Clamp Continuous Current                                                                                    | 10                     |      | mA   |

| V <sub>FB</sub> ,V <sub>SENSE</sub> ,V <sub>RI</sub> ,V <sub>RT</sub> (Voltage at FB,SENSE,RI,RT to GND) -0.3 to 7 |                        | V    |      |

| Min/Max Operating Junction Temperature T <sub>J</sub>                                                              | -20 to 150             |      | °C   |

| Min/Max Storage Temperature Tstg                                                                                   | -55 to 150             |      | °C   |

| R <sub>θJA</sub> thermal Resistance                                                                                | SOT23-6 200            |      | °C/W |

| Soldering temperature and time                                                                                     | +260 (Recommended 10S) |      | °C   |

Caution: The absolute maximum ratings are rated values exceeding which the product could suffer physical damage.

These values must therefore not be exceeded under any conditions.

Note: VDD\_Clamp has a nominal value of 32V.

# **Recommended Operating Condition**

| Parameter                                    | Range     | Unit |

|----------------------------------------------|-----------|------|

| VDD Supply Voltage                           | 10 to 30  | V    |

| T <sub>A</sub> Operating Ambient Temperature | -20 to 85 | °C   |

# $\textbf{Electrical Characteristics}(T_{\text{A}} = 25^{\circ}\text{C}, \text{VDD} = 16\text{V}, \text{ if not otherwise noted})$

| Symbol                                       | Parameter                                         | Test Conditions                                                       |                              | Min | Тур.  | Max  | Unit |

|----------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------|------------------------------|-----|-------|------|------|

|                                              | Supply                                            | / Voltage (VI                                                         | DD)                          |     | •     | •    |      |

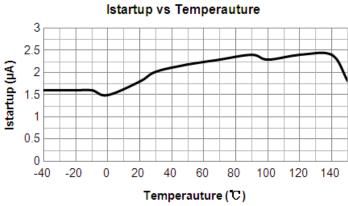

| Startup VDD Start up Current VDD=11V,Measure |                                                   | Measure 1                                                             | _                            | 2   | 20    | μA   |      |

| Startup                                      | VDD Glart up Gurrent                              | leakage cur                                                           | rent into VDD                |     |       |      | μ/ ( |

|                                              |                                                   |                                                                       | 8204                         | -   | 1.8   | 3    | mA   |

| I <sub>VDD_ Operation</sub>                  | Operation Current                                 | $V_{FB}=3V$                                                           | 8204B                        |     | 1.8   | 3    | mA   |

|                                              |                                                   |                                                                       | 8204C                        |     | 3.3   | 4.5  | mA   |

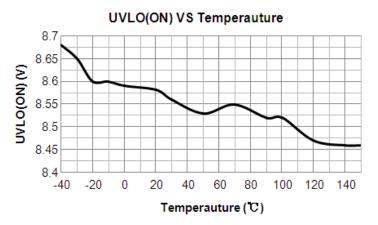

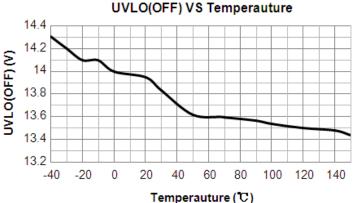

| $UVLO_ON$                                    | VDD Under Voltage Lockout Enter                   |                                                                       |                              | 8   | 9     | 10   | V    |

| UVLO <sub>OFF</sub>                          | VDD Under Voltage Lockout Exit (Recovery)         |                                                                       |                              | 13  | 14    | 15.5 | V    |

| V <sub>PULL-UP</sub>                         | Pull-up PMOS active                               |                                                                       |                              | -   | 13    | -    | V    |

| V <sub>DD_ Clamp</sub>                       |                                                   | $I_{VDD} = 10 \text{ m}$                                              | A                            | 30  | 32    | 34   | V    |

| OVP <sub>ON</sub>                            | VDD Over voltage protection enter                 | I                                                                     | :3V Ramp up ate clock is off | 24  | 26    | 28   | V    |

| V <sub>LATCH_REASE</sub>                     | Latch release voltage                             |                                                                       |                              | -   | 5     | -    | V    |

|                                              | Feedback Ir                                       | put Section                                                           | (FB Pin)                     |     |       |      |      |

| AV <sub>CS</sub>                             | PWM Input Gain ΔV <sub>FB</sub> /ΔV <sub>CS</sub> |                                                                       |                              | -   | 2     | -    | V/V  |

| Maximum duty cycle                           | Max duty cycle                                    | V <sub>DD</sub> =16V,V <sub>FB</sub> =3V, V <sub>CS</sub> =0V         |                              | 75  | 80    | 85   | %    |

| V <sub>FB_Open</sub>                         | V <sub>FB</sub> Open Loop Voltage                 |                                                                       |                              | 3.9 | 4.2   | -    | V    |

| FB_ Short                                    | FB pin short circuit current                      | Short FB pin to GND, measure current                                  |                              | -   | 0.3   | -    | mA   |

| V <sub>REF_GREEN</sub>                       | The threshold enter green mode                    |                                                                       |                              | -   | 1.4   | -    | V    |

| $V_{REF\_BURST\_H}$                          | The threshold exit burst mode                     |                                                                       |                              | ı   | 0.675 | -    | V    |

| $V_{REF\_BURST\_L}$                          | The threshold enter burst mode                    |                                                                       |                              | ı   | 0.575 | -    | V    |

| $V_{TH\_PL}$                                 | Power Limiting FB Threshold Voltage               |                                                                       |                              | -   | 3.7   | -    | V    |

| T <sub>D_PL</sub>                            | Power limiting Debounce Time                      |                                                                       |                              | 80  | 88    | 96   | mS   |

| $Z_{FB\_IN}$                                 | Input Impedance                                   |                                                                       |                              | ı   | 4     | -    | ΚΩ   |

|                                              | Current Ser                                       | nse Input(Se                                                          | nse Pin)                     |     |       |      |      |

| Soft start time                              |                                                   |                                                                       |                              | -   | 4     | -    | mS   |

| T_ blanking                                  | Leading edge blanking time                        |                                                                       |                              | -   | 220   | -    | nS   |

| Z <sub>SENSE_IN</sub>                        | Input Impedance                                   |                                                                       |                              | ı   | 40    | -    | ΚΩ   |

| $T_{D\_OC}$                                  | Over Current Detection and Control Delay          | From over current occurs till the gate drive output start to turn off |                              | -   | 120   | -    | nS   |

| V <sub>TH_OC</sub>                           | Internal current limiting threshold voltage       | FB=3.3V                                                               |                              | -   | 0.875 | -    | V    |

ME8204

| V <sub>OCP_CLAMPER</sub>                                   | CS voltage clamper              |                                 |       | -    | 0.95 | -    | V     |  |

|------------------------------------------------------------|---------------------------------|---------------------------------|-------|------|------|------|-------|--|

| Oscillator                                                 |                                 |                                 |       |      |      |      |       |  |

|                                                            |                                 | VDD=16V,                        | 8204  | 60   | 65   | 70   | KHz   |  |

| Fosc                                                       | Normal Oscillation Frequency    | FB=3V,CS=0                      | 8204B | 60   | 65   | 70   | KHz   |  |

|                                                            |                                 | V                               | 8204C | 95   | 100  | 105  | KHz   |  |

| Δf_ OSC                                                    | Frequency jittering             |                                 |       | -    | ±4   | -    | %     |  |

| Δf_ Temp                                                   | Frequency Temperature Stability | -20°C to 100 °C                 | ;     | -    | 1    | -    | %     |  |

|                                                            |                                 |                                 | 8204  | -    | 32   | -    | Hz    |  |

| F_ shuffling                                               | Shuffling frequency             |                                 | 8204B |      | 32   | -    | Hz    |  |

|                                                            |                                 |                                 | 8204C |      | 50   | -    | Hz    |  |

| Δf_ VDD                                                    | Frequency Voltage Stability     |                                 |       | -    | 1    | -    | %     |  |

|                                                            | Burst Mode Base Frequency       |                                 | 8204  | -    | 22   | -    | KHz   |  |

| F_ Burst                                                   |                                 |                                 | 8204B |      | 22   | -    | KHz   |  |

|                                                            |                                 |                                 | 8204C |      | 32   | -    | KHz   |  |

|                                                            | Gate                            | Drive Output                    |       |      |      |      |       |  |

| $V_{OL}$ Output Low Level $V_{DD}=16V, I_{O}=5 \text{ mA}$ |                                 |                                 | mA    | -    | -    | 1    | V     |  |

| V <sub>OH</sub>                                            | Output High Level               | V <sub>DD</sub> =16V,lo = 20 mA |       | 6    | -    | -    | V     |  |

| V_ Clamp                                                   | Output Clamp Voltage            |                                 |       | -    | 12   | -    | V     |  |

| T_ r                                                       | Output Rising Time 1V~12V       | C <sub>L</sub> = 1000pF         |       | -    | 175  | -    | nS    |  |

| T_ f                                                       | Output Falling Time 12V~1V      | C <sub>L</sub> = 500pF          |       | -    | 85   | -    | nS    |  |

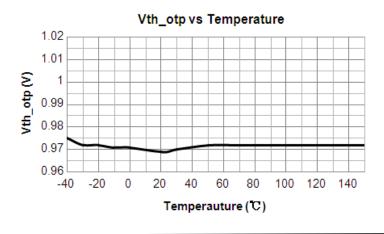

| Over Temperature Protection                                |                                 |                                 |       |      |      |      |       |  |

| I <sub>RT</sub>                                            | Output current of RT pin        |                                 |       | 95   | 100  | 105  | μA    |  |

| V <sub>OTP</sub>                                           | Threshold voltage for OTP       |                                 |       | 0.95 | 1    | 1.05 | V     |  |

| V <sub>OTP_FL</sub>                                        | Float voltage at RT pin         |                                 |       | -    | 2.3  | -    | V     |  |

| T <sub>D_OTP</sub>                                         | OTP De-bounce time              |                                 |       | -    | 32   | -    | Cycle |  |

| V <sub>RT_OVP</sub>                                        | RT Pin open voltage             |                                 |       | -    | 4    | -    | V     |  |

## **Typical performance characteristics**

$V_{DD}$  = 16V,  $T_A$  = 25°C condition applies if not otherwise noted

## **Operation Description**

The ME8204 is a low power off-line SMPS Switcher optimized for off-line flyback converter applications in 40W~60W power range. The 'Extended burst mode' control greatly reduces the standby power consumption and helps the design easily to meet the international power conservation requirements.

#### Startup Current and Start up Control

Startup current of ME8204 is designed to be very low so that VDD could be charged up above UVLO threshold level and device starts up quickly. A large value startup resistor can therefore be used to minimize the power loss yet provides reliable startup in application. For a typical AC/DC adaptor with universal input range design, a 2 M $\Omega$ , 1/8 W startup

resistor could be used together with a VDD capacitor to provide a fast startup and low power dissipation design solution.

### Operating Current

The Operating current of ME8204 is low at 1.8mA. Good efficiency is achieved with ME8204 low operating current together with extended burst mode control features.

### •Frequency shuffling for EMI improvement

The frequency Shuffling/jittering (switching frequency modulation) is implemented in ME8204. The oscillation frequency is modulated with a random source so that the tone energy is spread out. The spread spectrum minimizes the conduction band EMI and therefore reduces system design challenge.

### •Extended Burst Mode Operation

At zero load or light load condition, majority of the power dissipation in a switching mode power supply is from switching loss on the MOSFET transistor, the core loss of the transformer and the loss on the snubber circuit. The magnitude of power loss is in proportion to the switching frequency. Lower switching frequency leads to the reduction on the power loss and thus conserves the energy.

The switching frequency is internally adjusted at no load or light load condition. The switch frequency reduces at light/no load condition to improve the conversion efficiency. At light load or no load condition, the FB input drops below burst mode threshold level and device enters Burst Mode control. The Gate drive output switches only when VDD voltage drops below a preset level and FB input is active to output an on state. Otherwise the gate drive remains at off state to minimize the switching loss and reduces the standby power consumption to the greatest extend. The nature of high frequency switching also reduces the audio noise at any loading conditions.

#### Oscillator Operation

The switching frequency of ME8204 is internally fixed at 65KHz. No external frequency setting components are required for PCB design simplification.

### Current Sensing and Leading Edge Blanking

Cycle-by-Cycle current limiting is offered in ME8204 current mode PWM control. The switch current is detected by a sense resistor into the sense pin. An internal leading edge blanking circuit chops off the sense voltage spike at initial MOSFET on state due to Snubber diode reverse recovery so that the external RC filtering on sense input is no longer required. The current limiting comparator is disabled and thus cannot turn off the external MOSFET during the blanking period. PWM duty cycle is determined by the current sense input voltage and the FB input voltage.

### •Internal Synchronized Slope Compensation

Built-in slope compensation circuit adds voltage ramp onto the current sense input voltage for PWM generation. This greatly improves the close loop stability at CCM and prevents the sub-harmonic oscillation and thus reduces the output ripple voltage.

#### Gate Drive

The power MOSFET is driven by a dedicated gate driver for power switch control. Too weak the gate drive strength results in higher conduction and switch loss of MOSFET while too strong gate drive output compromises the EMI. A good trade-off is achieved through the built-in totem pole gate design with right output strength and dead time control. The low idle loss and good EMI system design is easier to achieve with this dedicated control scheme.

### Over Temperature Protection

A NTC resistor in series with a regular resistor should connect between RT and GND for temperature sensing and protection.NTC resistor value becomes lower when the ambient temperature rises. With the fixed internal current  $I_{RT}$  flowing through the resistors, the voltage at RT pin becomes lower at high temperature. The internal OTP circuit is triggered and shutdown the MOSFET when the sensed input voltage is lower than  $V_{TH\ OTP}$ .

#### Protection Controls

Good power supply system reliability is achieved with its rich protection features including Cycle-by-Cycle current limiting (OCP), Over Load Protection (OLP), CS short protection, CS floating including over protection, and latch features temperature protection (OTP), fixed or adjustable over voltage protection (OVP), and Under Voltage Lockout on VDD (UVLO).

The OCP is line voltage compensated to achieve constant output power limit over the universal input voltage range.

At overload condition, When FB input exceeds power limit threshold value for more than  $T_{D\_PL}$ , control circuit reacts to shut down the output power MOSFET. Similarly, control circuit reacts to shut down the switcher. Switcher restarts when VDD voltage drops below UVLO limit. For latch mode, control circuit shutdowns (latch) the power MOSFET when an

Over Temperature condition or Over Voltage condition is detected until VDD drops below 5V (Latch release voltage) , and device enters power on restart-up sequence thereafter.

# **Packaging Information**

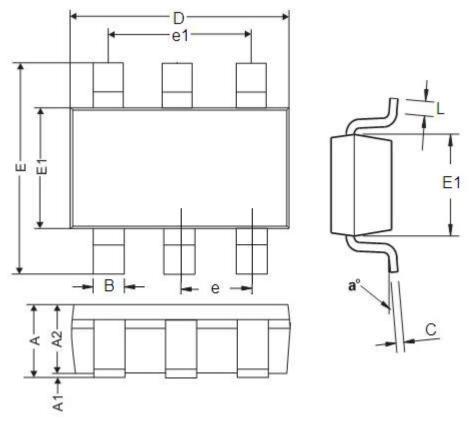

Package type: SOT23-6

| DIM   | Millimeters |      | Inches    |                 |  |

|-------|-------------|------|-----------|-----------------|--|

| DIM   | Min         | Max  | Min       | Max             |  |

| А     | 0.9         | 1.45 | 0.0354    | 0.0570          |  |

| A1    | 0           | 0.15 | 0         | 0.0059          |  |

| A2    | 0.9         | 1.3  | 0.0354    | 0.0511          |  |

| В     | 0.2         | 0.5  | 0.0078    | 0.0196          |  |

| С     | 0.09        | 0.26 | 0.0035    | 0.0102          |  |

| D     | 2.7         | 3.10 | 0.1062    | 0.1220          |  |

| Е     | 2.2         | 3.2  | 0.0866    | 0.1181          |  |

| E1    | 1.30        | 1.80 | 0.0511    | 0.0708          |  |

| е     | 0.95        | REF  | 0.0374REF |                 |  |

| e1    | 1.90        | REF  | 0.0       | 748REF          |  |

| L     | 0.10        | 0.60 | 0.0039    | 0.0236          |  |

| $a^0$ | 00          | 30°  | 00        | 30 <sup>0</sup> |  |

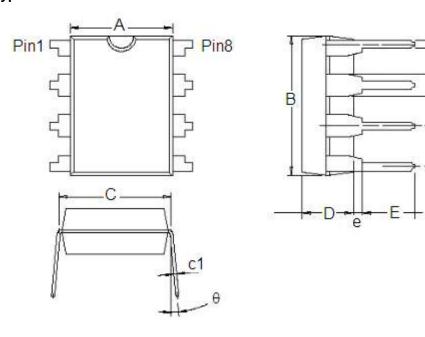

## • Package type: DIP8

| DIM | Millimeters |                 | Inches      |       |  |

|-----|-------------|-----------------|-------------|-------|--|

|     | Min         | Max             | Min         | Max   |  |

| А   | 6.200       | 6.600           | 0.244       | 0.260 |  |

| В   | 9.000       | 9.400           | 0.354       | 0.370 |  |

| С   | 7.620       | (Тур.)          | 0.300(Typ.) |       |  |

| D   | 3.200       | 3.600           | 0.126       | 0.142 |  |

| E   | 3.000       | 3.600           | 0.118       | 0.142 |  |

| а   | 0.360       | 0.560           | 0.014       | 0.022 |  |

| b   | 1.524(Typ.) |                 | 0.060(Typ.) |       |  |

| С   | 2.54(Typ.)  |                 | 0.100(Typ.) |       |  |

| c1  | 0.204       | 0.360           | 0.008       | 0.014 |  |

| е   | 0.510(Min)  |                 | 0.020       | (Min) |  |

| θ   | 00          | 15 <sup>0</sup> | 00          | 150   |  |

- The information described herein is subject to change without notice.

- Nanjing Micro One Electronics Inc is not responsible for any problems caused by circuits or diagrams

described herein whose related industrial properties, patents, or other rights belong to third parties.

The application circuit examples explain typical applications of the products, and do not guarantee the

success of any specific mass-production design.

- Use of the information described herein for other purposes and/or reproduction or copying without the express permission of Nanjing Micro One Electronics Inc is strictly prohibited.

- The products described herein cannot be used as part of any device or equipment affecting the human body, such as exercise equipment, medical equipment, security systems, gas equipment, or any apparatus installed in airplanes and other vehicles, without prior written permission of Nanjing Micro One Electronics Inc.

- Although Nanjing Micro One Electronics Inc exerts the greatest possible effort to ensure high quality and reliability, the failure or malfunction of semiconductor products may occur. The user of these products should therefore give thorough consideration to safety design, including redundancy, fire-prevention measures, and malfunction prevention, to prevent any accidents, fires, or community damage that may ensue.

单击下面可查看定价,库存,交付和生命周期等信息

>>MICRONE(南京微盟)