**NXT4556**

SIM card interface level translator Rev. 2 — 15 June 2022

### 1. General description

The NXT4556 device is built for interfacing a SIM card with a single low-voltage host side interface. The NXT4556 has three level translators to convert the data, RST and CLK signals between a SIM card and a host microcontroller. A high speed level translation capable of supporting class-B, class-C SIM cards.  $V_{CC\_SIM}$  power-down initiates a shutdown sequence on SIM card pins in accordance with ISO-7816-3.

The NXT4556 is compliant with all ETSI, IMT-2000 and ISO-7816 SIM/Smart card interface requirements.

### 2. Features and benefits

- Support SIM cards and eSIM with supply voltages 1.62 V to 3.3 V

- Host micro-controller operating voltage range: 1.08 V to 1.98 V

- Automatic level translation of I/O, RST and CLK between SIM card and host side interface with capacitance isolation

- Incorporates shutdown feature for the SIM card signals according to ISO-7816-3

- High  $V_{dis(UVLO AC)}$  switching level, arranging quick shut down when  $V_{CC SIM}$  powers down

- Integrated pull-up resistors; no external resistor required

- Integrated EMI Filters suppresses higher harmonics of digital I/O's

- Low current shutdown mode < 1 µA</li>

- Supports clock speed beyond 5 MHz clock

- Pb-free, Restriction of Hazardous Substances (RoHS) compliant and free of halogen and antimony (Dark Green compliant)

- ESD protection:

- HBM ANSI/ESDA/JEDEC JS-001 exceeds 2 kV

- CDM ANSI/ESDA/JEDEC JS-002 exceeds 1 kV

- IEC61000-4-2 level 4, contact and air discharge on all SIM card-side pins exceeds 8 kV and 15 kV

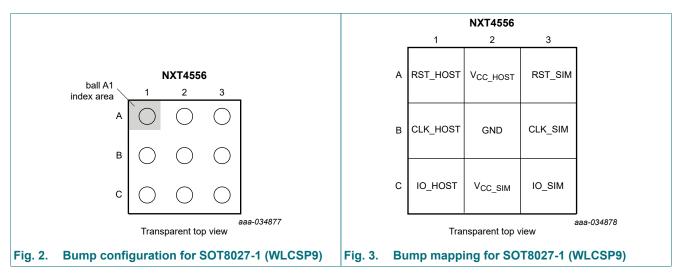

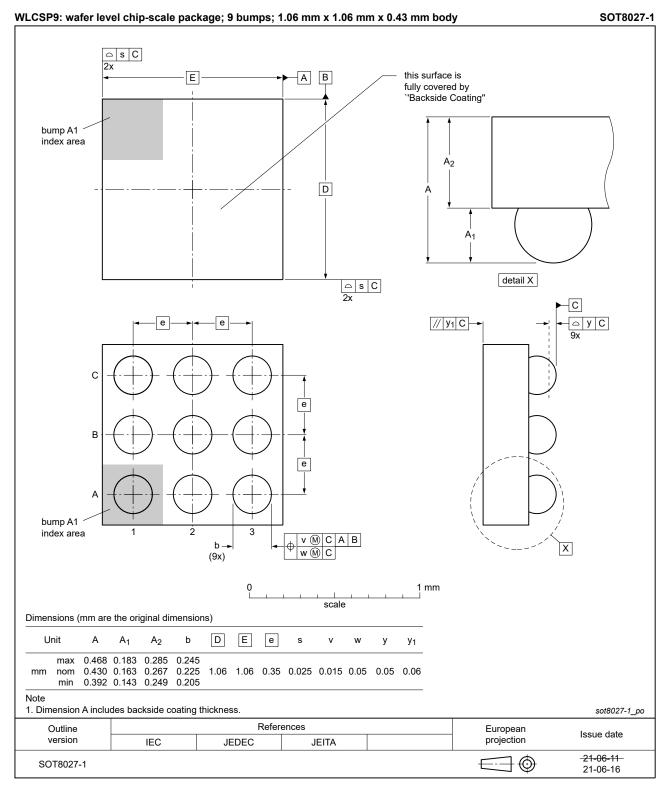

- Available in 9-pin wafer level chip-scale package (WLCSP); 9 bumps; 1.06 mm x 1.06 mm x 0.43 mm body; 0.35 mm pitch

### 3. Applications

NXT4556 can be used with a range of SIM card attached devices including:

- Mobile and personal phones

- Wireless modems

- SIM card terminals

# nexperia

# 4. Ordering information

| Table 1. Ordering information |                   |        |                                                                        |                  |  |

|-------------------------------|-------------------|--------|------------------------------------------------------------------------|------------------|--|

| Туре                          | Package           |        |                                                                        |                  |  |

| number                        | Temperature range | Name   | Description                                                            | Version          |  |

| NXT4556UP                     | -40 °C to +85 °C  | WLCSP9 | wafer level chip-scale package; 9 bumps;<br>1.06 × 1.06 × 0.43 mm body | <u>SOT8027-1</u> |  |

# 5. Marking

| Table 2. Marking |                 |

|------------------|-----------------|

| Type number      | Marking code[1] |

| NXT4556UP        | z6              |

[1] The pin 1 indicator is located on the lower left corner of the device, below the marking code.

# 6. Functional diagram

3 / 19

# 7. Pinning information

### 7.2. Pin description

#### Table 3. Pin description

| Symbol               | Bump | Туре   | Description                                                                                                                                                                                |  |  |

|----------------------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RST_HOST             | A1   | I      | Reset input from host controller.                                                                                                                                                          |  |  |

| V <sub>CC_HOST</sub> | A2   | power  | Supply voltage for the host controller side input/output pins (CLK_HOST, RST_HOST, IO_HOST). This pin should be bypassed with a 0.1 $\mu$ F ceramic capacitor close to the pin.            |  |  |

| RST_SIM              | A3   | 0      | Reset output pin for the SIM card.                                                                                                                                                         |  |  |

| CLK_HOST             | B1   | I      | Clock input from host controller.                                                                                                                                                          |  |  |

| GND                  | B2   | ground | Ground for the SIM card and host controller. Proper grounding and bypassing are required to meet ESD specifications.                                                                       |  |  |

| CLK_SIM              | B3   | 0      | Clock output pin for the SIM card.                                                                                                                                                         |  |  |

| IO_HOST              | C1   | I/O    | Host controller bidirectional data input/output. This pin can be driven from push-pull as well as open-drain drivers.                                                                      |  |  |

| V <sub>CC_SIM</sub>  | C2   | power  | Supply voltage for the SIM CARD side input/output pins. This input voltage ranges from 1.62 V to 3.3 V. This pin should be bypassed with a 0.1 $\mu$ F ceramic capacitor close to the pin. |  |  |

| IO_SIM               | C3   | I/O    | SIM card bidirectional data input/output. The SIM card output must be on an open-drain driver.                                                                                             |  |  |

## 8. Functional description

### 8.1. Functional behavior

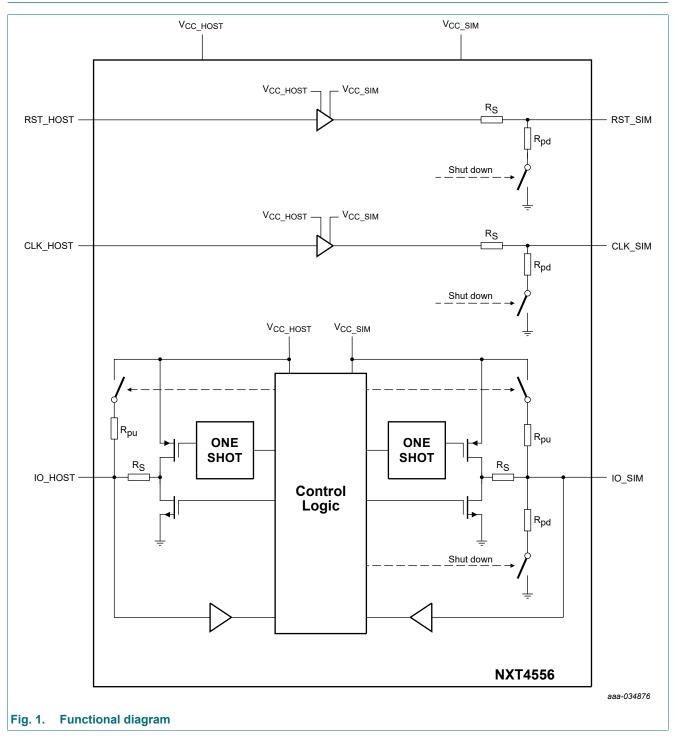

The functional diagram of the NTX4556 is shown in Fig. 1.

The upper part of  $\underline{Fig. 1}$  shows the RST and CLK channels which are uni-directional level shifters from the host to the SIM card side.

The bottom part shows the architecture of the bidirectional I/O channel. Both on IO\_HOST and IO\_SIM a resistor  $R_{pu}$  pulls up the I/O node. On both sides an output stage is present that consists of a PMOST and an NMOST device. Each output stage drives the output through a series resistor  $R_{s}$ . Input stages sense the I/O nodes and pass LOW/HIGH information to the control logic that controls the translator outputs and several pull-up and pull-down resistors.

The NXT4556 I/O channel does not require a dedicated input signal to control the direction of data flow from IO\_HOST to IO\_SIM or from IO\_SIM to IO\_HOST. Change in driving direction is possible when both sides are at HIGH state. The control logic recognizes the I/O node with the first falling edge and grants control over the opposite I/O node. When for example the IO\_HOST is turned LOW, the control circuit will turn on the NMOST on the IO\_SIM side, pulling LOW IO\_SIM. The IO\_SIM pin is then an output only, until IO\_HOST is turned HIGH and the translator has turned IO\_SIM HIGH again.

The PMOST devices are used to actively turn high the outputs. Each PMOST is driven by a oneshot circuit that generates a pulse. For example: Assuming HOST to SIM communication, when the IO\_HOST is turned HIGH, it will activate the one shot circuit on the IO\_SIM side. A pulse starts, arranging a fast LOW to HIGH transition on IO\_SIM. When the pulse has finished, the PMOST is released. At that stage, the system returns to a standard open drain state whereby the pull resistors keep the I/O nodes HIGH.

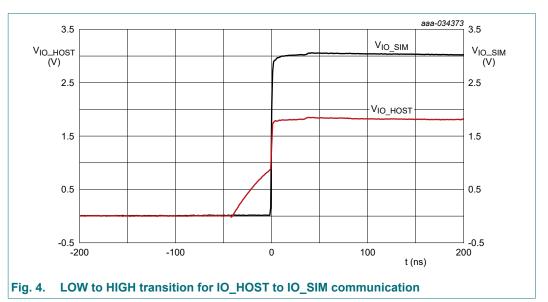

At the same time, at a LOW to HIGH transition, the one shot on the input side is activated as well. In an open drain application, this creates a typical input LOW to HIGH waveform. Fig. 4 shows an example of a LOW to HIGH transition in an open drain application.

Looking at the input signal, the first part of the LOW to HIGH transition is an exponential curve caused by the I/O node capacitance being charged via the pull-up resistor. The second part starts when the input signal crosses the input switching level. The rising edge is accelerated dramatically by the PMOST that is turned on by the one shot on the input side.

In case of a communication error or some other unforeseen incident that may drive both connected sides of the drivers at the same time, the internal logic automatically prevents stuck-at situation. This ensures that both I/Os will return to HIGH level once released from being driven LOW.

© Nexperia B.V. 2022. All rights reserved

In shut down mode, the control circuit disables all output stages. Additionally, in shut down mode, the pull-up resistor on IO\_SIM side is disabled, and all pull-down resistors  $R_{pd}$  on SIM side are enabled, pulling LOW the pins on the SIM side. The shut down sequence is explained in more detail in <u>Section 8.3</u>.

### 8.2. Window of I/O communication

When the translator is in operating mode, I/O communication can take place through the I/O channel. Communication can take place in both directions IO\_HOST  $\leftrightarrow$  IO\_SIM. Additionally, during operating mode, the RST\_HOST and CLK\_HOST signals are passed to RST\_SIM and CLK\_SIM respectively.

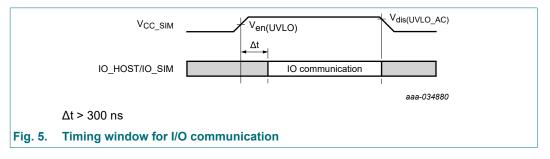

The translator is active when V<sub>CC\_HOST</sub> and V<sub>CC\_SIM</sub> are at a proper level. <u>Fig. 5</u> shows how V<sub>CC\_SIM</sub> controls the translator mode. V<sub>CC\_HOST</sub> is assumed to be default present and is not shown in the waveform.

When V<sub>CC\_SIM</sub> has turned HIGH, I/O communication can commence after a certain amount of time:  $\Delta t$  > 300 ns.

It is assumed that during the power up sequence, the nodes of IO\_HOST and and IO\_SIM are not pulled down by the host controller and the SIM card. The translator has integrated pull-up resistors and will turn HIGH both IO\_HOST and IO\_SIM. The pull-up resistors  $R_{pu}$  are pointed out in Fig. 1.

When  $V_{CC\_SIM}$  drops below  $V_{dis(UVLO)}$ , the translator turns to shutdown mode. Section 8.3 illustrates the shutdown sequence in more detail.

### 8.3. Shutdown sequence

The ISO 7816-3 specification specifies the shutdown sequence for the SIM card signals to ensure that the card is properly disabled for power savings. Also, during hot swap, the orderly shutdown of these signals helps to avoid any improper write and corruption of data.

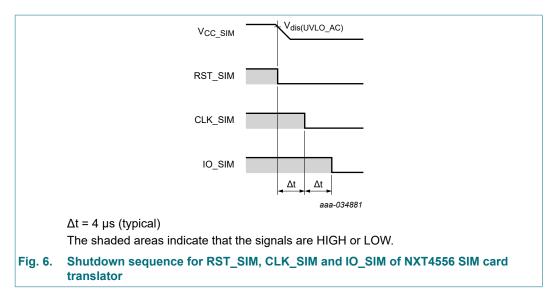

When  $V_{CC\_SIM}$  drops below  $V_{dis(UVLO\_AC)}$ , the shutdown sequence is initiated. Fig. 6 illustrates the shutdown sequence initiated by  $V_{CC\_SIM}$  being powered down.

The shut down sequence starts by pulling down the RST\_SIM output. Once RST\_SIM is turned LOW, CLK\_SIM and IO\_SIM are pulled LOW sequentially, one-by-one. Internal pull-down resistors on the SIM pins are used to pull the SIM channels LOW. The internal pull-down resistors,  $R_{pd}$ , that pull down the three pins on the SIM side are shown in Fig. 1. The shutdown sequence is completed in a few microseconds. The interval time ( $\Delta t$ ), is typically 4 µs.

### 8.4. UVLO

When  $V_{CC\_SIM}$  drops below  $V_{dis(UVLO\_AC)}$ , the translator goes to shut down mode. This is illustrated in Fig. 5. The switching level  $V_{dis(UVLO\_AC)}$  has a high value of approximately 86 %xV<sub>CC\\_SIM</sub>. The circuitry uses an AC detection mechanism that operates accurately with a falling slope that is typical in the SIM card application. Next to this AC detection, a standard UVLO detection is in place that has no condition with respect to the slope of the rising or falling V<sub>CC\\_SIM</sub>. For the standard UVLO, the parameters V<sub>en(UVLO</sub> and V<sub>dis(UVLO</sub>) are involved which have lower values than V<sub>dis(UVLO\\_AC)</sub>. When V<sub>CC\\_SIM</sub> is powered up, the translator is enabled when V<sub>CC\\_SIM</sub> crosses V<sub>en(UVLO</sub>). This is illustrated in Fig. 5.

### 8.5. EMI filter

All output driver stages of I/O, RST and CLK channels are equipped with EMI filters to reduce interference towards sensitive mobile communication.

### 8.6. ESD protection

The device has robust ESD protections on all SIM card pins. The architecture prevents any stress for the host: the voltage translator discharges any stress to supply ground.

# 9. Limiting values

#### Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol               | Parameter                          | Conditions                                               | Min       | Max  | Unit |

|----------------------|------------------------------------|----------------------------------------------------------|-----------|------|------|

| V <sub>ESD</sub>     | electrostatic discharge<br>voltage | SIM card side; IEC 61000-4-2; level 4; contact discharge | -         | ±8   | kV   |

|                      |                                    | SIM card side; IEC 61000-4-2; level 4; air discharge     | -         | ±15  | kV   |

|                      |                                    | all other pins; IEC 61000-4-2; level 4                   | -         | ±2   | kV   |

|                      |                                    | all other pins; HBM [1]                                  | -         | ±2   | kV   |

|                      |                                    | all other pins; CDM [2]                                  | -         | ±1   | kV   |

| V <sub>CC_HOST</sub> | supply voltage                     |                                                          | GND - 0.5 | 4.6  | V    |

| V <sub>CC_SIM</sub>  | SIM card supply voltage            |                                                          | GND - 0.5 | 4.6  | V    |

| VI                   | input voltage                      | CLK_HOST; input signal voltage, HOST side                | GND - 0.5 | 4.6  | V    |

|                      |                                    | RST_HOST; input signal voltage, HOST side                | GND - 0.5 | 4.6  | V    |

|                      |                                    | IO_HOST; input signal voltage, HOST side                 | GND - 0.5 | 4.6  | V    |

|                      |                                    | CLK_SIM; input signal voltage, SIM side                  | GND - 0.5 | 4.6  | V    |

|                      |                                    | RST_SIM; input signal voltage, SIM side                  | GND - 0.5 | 4.6  | V    |

|                      |                                    | IO_SIM; input signal voltage, SIM side                   | GND - 0.5 | 4.6  | V    |

| T <sub>stg</sub>     | storage temperature                |                                                          | -55       | +125 | °C   |

[1] Human Body Model (HBM) according to JESD22-A-A114.

[2] Charged-Device Model (CDM) according to JESD22-C101.

# 10. Recommended operating conditions

#### Table 5. Operating conditions

| Symbol               | Parameter                | Conditions | Min  | Тур | Мах                        | Unit |

|----------------------|--------------------------|------------|------|-----|----------------------------|------|

| V <sub>CC_HOST</sub> | supply voltage           | [1]        | 1.08 | -   | 1.98 V                     | V    |

| V <sub>CC_SIM</sub>  | card side supply voltage | [1]        | 1.62 | -   | 3.3                        | V    |

| VI                   | input voltage            | HOST side  | -0.3 | -   | V <sub>CC_HOST</sub> + 0.3 | V    |

|                      |                          | SIM side   | -0.3 | -   | V <sub>CC_SIM</sub> + 0.3  | V    |

| T <sub>amb</sub>     | ambient temperature      |            | -40  | +25 | +85                        | °C   |

[1]  $V_{CC\_SIM} \ge V_{CC\_HOST}$

# **11. Electrical characteristics**

#### **Table 6. Electrical characteristics**

1.08 V  $\leq$  V<sub>CC HOST</sub>  $\leq$  1.98 V; 1.62 V  $\leq$  V<sub>CC SIM</sub>  $\leq$  3.3 V; GND = 0 V; unless otherwise specified.

| Symbol                    | Parameter                                  | Conditions                                                                   | nditions |      | <sub>nb</sub> = -40 °C to +8 | 5 °C | Unit |

|---------------------------|--------------------------------------------|------------------------------------------------------------------------------|----------|------|------------------------------|------|------|

|                           |                                            |                                                                              | F        | Min  | Typ[1]                       | Max  |      |

| I <sub>CC_HOST</sub>      | supply current                             | operating mode; f <sub>clk</sub> = 1 MHz;<br>IO_HOST = IO_SIM = HIGH         | [2]      | -    | 5                            | 10   | μA   |

|                           |                                            | shutdown mode; IO_HOST = HIGH                                                | [3]      | -    | -                            | 1    | μA   |

| I <sub>CC_SIM</sub>       | card side supply current                   | operating mode; [2]<br>IO_HOST = IO_SIM = HIGH;<br>CLK_HOST = RST_HOST = LOW |          | -    | 2                            | 8    | μA   |

| V <sub>en(UVLO)</sub>     | undervoltage<br>lockout enable<br>voltage  | V <sub>CC_SIM</sub> rising; V <sub>CC_HOST</sub> = 1.8 V 0                   |          | 0.85 | 1.2                          | 1.6  | V    |

| V <sub>dis(UVLO)</sub>    | undervoltage<br>lockout disable<br>voltage | V <sub>CC_SIM</sub> falling; V <sub>CC_HOST</sub> = 1.8 V                    |          | 0.65 | 1.0                          | 1.3  | V    |

| V <sub>dis(UVLO_AC)</sub> | undervoltage                               | V <sub>CC_SIM</sub> falling;                                                 |          |      |                              |      |      |

|                           | lockout disable<br>voltage                 | -dV/dt = 0.9 V/ms to 9 V/ms;<br>V <sub>CC_SIM</sub> = 1.8 V                  |          | -    | 1.55                         | -    | V    |

|                           |                                            | -dV/dt = 1.5 V/ms to 15 V/ms;<br>V <sub>CC_SIM</sub> = 3.0 V                 |          | -    | 2.58                         | -    | V    |

|                           |                                            | -dV/dt = 0.9 V/ms to 9 V/ms;<br>V <sub>CC_SIM</sub> = 1.71 V to 1.89 V       |          | -    | 0.86V <sub>CC_SIM</sub>      | -    | V    |

|                           |                                            | -dV/dt = 1.5 V/ms to 15 V/ms;<br>V <sub>CC_SIM</sub> = 2.85 V to 3.15 V      |          | -    | 0.86V <sub>CC_SIM</sub>      | -    | V    |

[1] Typical values measured at 25 °C.

[2] Internal pull-up resistance active on IO\_HOST and IO\_SIM

[3] Internal pull-up resistance active on IO\_HOST

### Table 7. Static characteristics

1.08 V  $\leq$  V<sub>CC HOST</sub>  $\leq$  1.98 V; 1.62 V  $\leq$  V<sub>CC SIM</sub>  $\leq$  3.3 V; GND = 0 V; unless otherwise specified.

| Symbol          | Parameter                   | Parameter Conditions                      |                          | T <sub>amb</sub> = -40 °C to +85 °C |                            |    |  |

|-----------------|-----------------------------|-------------------------------------------|--------------------------|-------------------------------------|----------------------------|----|--|

|                 |                             |                                           | Min                      | Typ[1]                              | Max                        |    |  |

| Level st        | nifter                      |                                           | · · ·                    |                                     |                            |    |  |

| V <sub>IH</sub> | HIGH-level                  | RST_HOST, CLK_HOST [2]                    | 0.65V <sub>CC_HOST</sub> | -                                   | V <sub>CC_HOST</sub> + 0.3 | V  |  |

|                 | input voltage               | IO_HOST                                   | 0.5V <sub>CC_HOST</sub>  | -                                   | V <sub>CC_HOST</sub> + 0.3 | V  |  |

|                 |                             | IO_SIM [2]                                | 0.5V <sub>CC_SIM</sub>   | -                                   | V <sub>CC_SIM</sub> + 0.3  | V  |  |

| V <sub>IL</sub> | LOW-level                   | RST_HOST, CLK_HOST [2]                    |                          | -                                   | 0.35V <sub>CC_HOST</sub>   | V  |  |

|                 | input voltage               | IO_HOST [2]                               | -0.3                     | -                                   | 0.3V <sub>CC_HOST</sub>    | V  |  |

|                 |                             | IO_SIM [2]                                | -0.3                     | -                                   | 0.25V <sub>CC_SIM</sub>    | V  |  |

| R <sub>pu</sub> | pull-up                     | IO_SIM connected to V <sub>CC_SIM</sub>   | 3.3                      | 5.3                                 | 7.3                        | kΩ |  |

|                 | resistance                  | IO_HOST connected to V <sub>CC_HOST</sub> | 2.8                      | 4.3                                 | 6                          | kΩ |  |

| V <sub>OH</sub> | HIGH-level                  | RST_SIM, CLK_SIM; I <sub>OH</sub> = -1 mA | 0.85V <sub>CC_SIM</sub>  | -                                   | V <sub>CC_SIM</sub> +0.3   | V  |  |

|                 | output voltage              | IO_SIM; I <sub>OH</sub> = -10 μA          | 0.85V <sub>CC_SIM</sub>  | -                                   | V <sub>CC_SIM</sub> +0.3   | V  |  |

|                 |                             | ΙΟ_HOST; Ι <sub>ΟΗ</sub> = -10 μΑ         | 0.85V <sub>CC_HOST</sub> | -                                   | V <sub>CC_HOST</sub> +0.3  | V  |  |

| V <sub>OL</sub> | LOW-level<br>output voltage | RST_SIM, CLK_SIM; I <sub>OL</sub> = 1 mA  | -                        | 50                                  | 200                        | mV |  |

|                 |                             | IO_SIM; I <sub>OL</sub> = 1 mA            | -                        | 50                                  | 300                        | mV |  |

|                 |                             | IO_HOST; I <sub>OL</sub> = 1 mA           | -                        | 50                                  | 300                        | mV |  |

| R <sub>pd</sub> | pull-down<br>resistance     | CLK_SIM, RST_SIM, IO_SIM                  | -                        | 400                                 | -                          | Ω  |  |

| EMI filte       | r                           |                                           |                          |                                     |                            |    |  |

| Rs              | series                      | IO_SIM                                    | -                        | 44                                  | -                          | Ω  |  |

|                 | resistance                  | RST_SIM                                   | -                        | 44                                  | -                          | Ω  |  |

|                 |                             | CLK_SIM                                   | -                        | 44                                  | -                          | Ω  |  |

| C <sub>io</sub> | input/output                | IO_SIM                                    | -                        | 10                                  | -                          | pF |  |

|                 | capacitance                 | RST_SIM                                   | -                        | 10                                  | -                          | pF |  |

|                 |                             | CLK_SIM                                   | -                        | 10                                  | -                          | pF |  |

|                 |                             | 1                                         | 1                        |                                     |                            |    |  |

[1] Typical values measured at 25 °C.

[2]  $V_{IL}$ ,  $V_{IH}$  depend on the individual supply voltage per interface.

**Product data sheet**

### Table 8. Dynamic characteristics

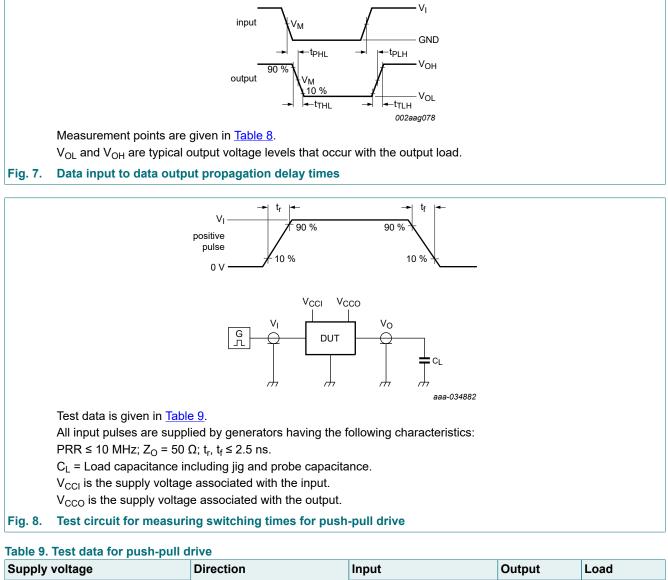

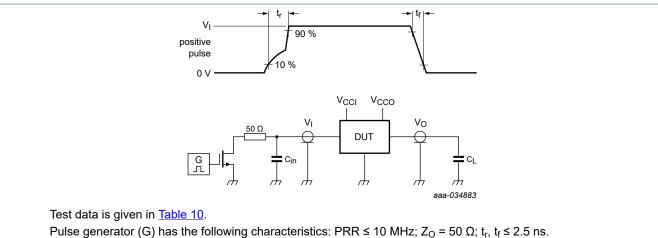

Push-pull: test circuit see Fig. 8;  $C_L$  = 50 pF. Open-drain: test circuit see Fig. 9;  $C_{IO\_HOST}$  = 10 pF;  $C_{IO\_SIM}$  = 30 pF. For waveform see Fig. 7.

| Symbol              | Parameter                 | er Conditions                                  |     | T <sub>amb</sub> = -40 °C to +85 °C; |             |          |                    |                      |         |      |

|---------------------|---------------------------|------------------------------------------------|-----|--------------------------------------|-------------|----------|--------------------|----------------------|---------|------|

|                     |                           |                                                |     | V <sub>CC_SIN</sub>                  | ₄ = 1.8 V ± | : 0.18 V | V <sub>cc_si</sub> | <sub>M</sub> = 3.0 V | ± 0.3 V |      |

|                     |                           |                                                |     | Min                                  | Typ[1]      | Мах      | Min                | Typ[1]               | Max     |      |

| V <sub>CC_HOS</sub> | $T = 1.2 V \pm 0.12$      | V                                              |     |                                      |             |          |                    |                      |         |      |

| t <sub>pd</sub>     | propagation               | I/O channel; push-pull                         | [2] | -                                    | 12          | 20       | -                  | 12                   | 20      | ns   |

|                     | delay                     | I/O channel; open-drain                        |     | -                                    | 15          | 25       | -                  | 15                   | 25      | ns   |

|                     |                           | CLK and RST channels;<br>push-pull             |     | -                                    | 12          | 20       | -                  | 12                   | 20      | ns   |

| t <sub>t</sub>      | transition time           | IO_HOST; push-pull                             | [3] | -                                    | -           | 10       | -                  | -                    | 10      | ns   |

|                     |                           | IO_SIM; RST_SIM; CLK_SIM;<br>push-pull         |     | -                                    | -           | 10       | -                  | -                    | 10      | ns   |

| t <sub>sk</sub>     | skew time                 | between channels IO_SIM and CLK_SIM; push-pull |     | -                                    | 2           | -        | -                  | 2                    | -       | ns   |

| f <sub>clock</sub>  | clock<br>frequency        | CLK channel; push-pull                         | [4] | -                                    | -           | 25       | -                  | -                    | 25      | MHz  |

| f <sub>data</sub>   | data rate                 | I/O channel; push-pull                         | [4] | -                                    | -           | 5        | -                  | -                    | 5       | Mbps |

|                     |                           | I/O channel; open-drain;<br>see <u>Fig. 9</u>  | [4] | -                                    | -           | 800      | -                  | -                    | 800     | kbps |

| V <sub>CC_HOS</sub> | $_{\rm T}$ = 1.8 V ± 0.18 | V                                              |     |                                      |             |          |                    |                      |         |      |

| t <sub>pd</sub>     | propagation               | I/O channel; push-pull                         | [2] | -                                    | 7           | 12       | -                  | 7                    | 12      | ns   |

|                     | delay                     | I/O channel; open-drain                        |     | -                                    | 8           | 15       | -                  | 8                    | 15      | ns   |

|                     |                           | CLK and RST channels;<br>push-pull             |     | -                                    | 7           | 12       | -                  | 7                    | 12      | ns   |

| t <sub>t</sub>      | transition time           | IO_HOST; push-pull                             | [3] | -                                    | -           | 10       | -                  | -                    | 10      | ns   |

|                     |                           | IO_SIM; RST_SIM; CLK_SIM;<br>push-pull         |     | -                                    | -           | 10       | -                  | -                    | 10      | ns   |

| t <sub>sk</sub>     | skew time                 | between channels IO_SIM and CLK_SIM; push-pull |     | -                                    | 2           | -        | -                  | 2                    | -       | ns   |

| f <sub>clock</sub>  | clock<br>frequency        | CLK channel; push-pull                         | [4] | -                                    | -           | 25       | -                  | -                    | 25      | MHz  |

| f <sub>data</sub>   | data rate                 | I/O channel; push-pull                         | [4] | -                                    | -           | 5        | -                  | -                    | 5       | Mbps |

|                     |                           | I/O channel; open-drain;<br>see <u>Fig. 9</u>  | [4] | -                                    | -           | 800      | -                  | -                    | 800     | kbps |

Typical values measured at 25 °C. [1]

[2]  $t_{\text{pd}}$  is the same as  $t_{\text{PHL}}$  and  $t_{\text{PLH}}.$

[3]

$t_t$  is the same as  $t_{THL}$  and  $t_{TLH}$ . Criteria: duty cycle between 40% and 60%; Voltage swing between 10% V<sub>CCI</sub> and 90% V<sub>CCI</sub>. [4]

### 11.1. Waveforms and test circuits

| Supply voltage       | oply voltage Direction I |                            | Input                |                         | Output                  | Load  |

|----------------------|--------------------------|----------------------------|----------------------|-------------------------|-------------------------|-------|

| V <sub>CC_HOST</sub> | V <sub>CC_SIM</sub>      |                            | VI                   | V <sub>M</sub>          | V <sub>M</sub>          | CL    |

| 1.08 V to 1.98 V     | 1.62 V to 3.3 V          | host side to SIM card side | V <sub>CC_HOST</sub> | 0.5V <sub>CC_HOST</sub> | $0.5V_{CC_SIM}$         | 50 pF |

| 1.08 V to 1.98 V     | 1.62 V to 3.3 V          | SIM card side to host side | V <sub>CC_SIM</sub>  | 0.5V <sub>CC_SIM</sub>  | 0.5V <sub>CC_HOST</sub> | 50 pF |

# NXT4556

### SIM card interface level translator

$C_L$  = Load capacitance including jig and probe capacitance.

V<sub>CCI</sub> is the supply voltage associated with the input.

V<sub>CCO</sub> is the supply voltage associated with the output.

Rise time on input pin strongly depends on source impedance, internal pull-up resistor and load capacitance (Cin).

#### Fig. 9. Test circuit for measuring switching times for open drain drive

#### Table 10. Test data for open drain drive

| Supply voltage       | voltage Direc       |                               | Input               |                         | Input                   |                 | Input |  | Direction Input |  | Output | Load |  |

|----------------------|---------------------|-------------------------------|---------------------|-------------------------|-------------------------|-----------------|-------|--|-----------------|--|--------|------|--|

| V <sub>CC_HOST</sub> | V <sub>CC_SIM</sub> |                               | VI                  | V <sub>M</sub>          | V <sub>M</sub>          | C <sub>in</sub> | CL    |  |                 |  |        |      |  |

| 1.08 V to 1.98 V     | 1.62 V to 3.3 V     | host side to<br>SIM card side |                     | 0.6V <sub>CC_HOST</sub> | 0.6V <sub>CC_SIM</sub>  | 10 pF           | 30 pF |  |                 |  |        |      |  |

| 1.08 V to 1.98 V     |                     | SIM card side to host side    | V <sub>CC_SIM</sub> | 0.5V <sub>CC_SIM</sub>  | 0.5V <sub>CC_HOST</sub> | 30 pF           | 10 pF |  |                 |  |        |      |  |

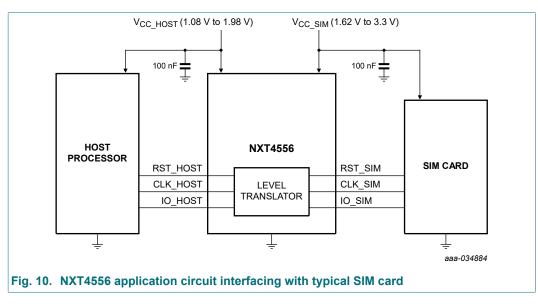

### 12. Application information

The application circuit for the NXT4556, which shows the typical interface with a SIM card, is shown in <u>Fig. 10</u>. Supply decoupling capacitors (100 nF) are recommended and should be placed close to the translator product.

# 13. Design and assembly recommendations

### 13.1. PCB design guidelines

For optimum performance, use a Non-Solder Mask PCB Design (NSMD), also known as a copper-definied design, incorporating laser-drilled micro-vias connecting the ground pads to a buried ground-plane layer. This results in the lowest possible ground inductance and provides the best high frequency and ESD performance. For this case, refer to <u>Table 11</u> for the recommended PCB design parameters.

#### Table 11. Recommended PCB design parameters

| Parameter                  | Value or specification |  |  |  |  |

|----------------------------|------------------------|--|--|--|--|

| PCB Cu pad shape           | circular               |  |  |  |  |

| PCB Cu pad diameter        | 200 µm                 |  |  |  |  |

| PCB solder resist diameter | 270 µm                 |  |  |  |  |

| WLCSP pad diameter (UBM)   | 200 µm                 |  |  |  |  |

### 13.2. PCB assembly guidelines for Pb-free soldering

| Table 12. Assembly recommendations |                            |  |  |  |  |

|------------------------------------|----------------------------|--|--|--|--|

| Parameter                          | Value or specification     |  |  |  |  |

| PCB stencil shape                  | circular                   |  |  |  |  |

| PCB stencil aperture diameter      | 200 µm                     |  |  |  |  |

| PCB stencil thickness              | 80 µm                      |  |  |  |  |

| Solder paste material              | SnAg₄Cu (Cu 0.5%) (SAC405) |  |  |  |  |

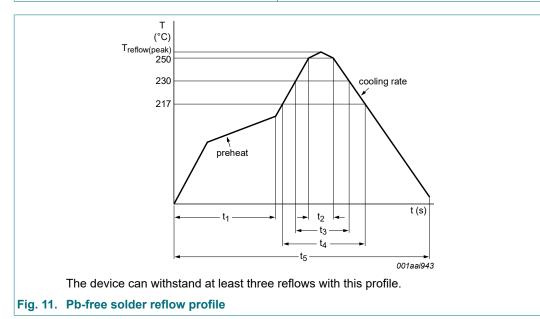

| Solder reflow profile              | see <u>Fig. 11</u>         |  |  |  |  |

14 / 19

#### Table 13. Reflow soldering process characteristics

$T_{amb}$  = 25 °C; unless otherwise specified.

| Symbol                    | Parameter                     | Conditions             | Min | Тур | Max | Unit |

|---------------------------|-------------------------------|------------------------|-----|-----|-----|------|

| t <sub>reflow(peak)</sub> | peak reflow temperature       |                        | 230 | -   | 260 | °C   |

| t <sub>1</sub>            | time 1                        | soak time              | 60  | -   | 180 | s    |

| t <sub>2</sub>            | time 2                        | time during T ≥ 250 °C | -   | -   | 30  | s    |

| t <sub>3</sub>            | time 3                        | time during T ≥ 230 °C | 10  | -   | 50  | s    |

| t <sub>4</sub>            | time 4                        | time during T ≥ 217 °C | 30  | -   | 150 | s    |

| t <sub>5</sub>            | time 5                        |                        | -   | -   | 540 | s    |

| dT/dt                     | rate of change of temperature | cooling rate           | -   | -   | -6  | °C/s |

|                           |                               | preheat                | 2.5 | -   | 4.0 | °C/s |

15 / 19

# 14. Package outline

#### Fig. 12. Package outline SOT8027-1 (WLCSP16)

# 15. Abbreviations

| Acronym | Description                      |

|---------|----------------------------------|

| CDM     | Charged-Device Model             |

| ESD     | ElectroStatic Discharge          |

| HBM     | Human Body Model                 |

| MSL     | Moisture Sensitivity Level       |

| PCB     | Printed-Circuit Board            |

| SIM     | Subscriber Identification Module |

# 16. Revision history

### Table 15. Revision history

| Document ID    | Release date                                                                                                                                  | Data sheet status  | Change notice | Supersedes  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------|-------------|

| NXT4556 v.2    | 20220615                                                                                                                                      | Product data sheet | -             | NXT4556 v.1 |

| Modifications: | <ul> <li><u>Table 3</u> corrected (errata).</li> <li><u>Fig. 4</u> corrected (errata).</li> <li><u>Fig. 10</u> corrected (errata).</li> </ul> |                    |               |             |

| NXT4556 v.1    | 20220502                                                                                                                                      | Product data sheet | -             | -           |

# 17. Legal information

#### **Data sheet status**

| Document status<br>[1][2]         | Product<br>status [3] | Definition                                                                                  |

|-----------------------------------|-----------------------|---------------------------------------------------------------------------------------------|

| Objective [short]<br>data sheet   | Development           | This document contains data from<br>the objective specification for<br>product development. |

| Preliminary [short]<br>data sheet | Qualification         | This document contains data from the preliminary specification.                             |

| Product [short]<br>data sheet     | Production            | This document contains the product specification.                                           |

Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the internet at <u>https://www.nexperia.com</u>.

#### **Definitions**

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

**Right to make changes** — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal

#### SIM card interface level translator

injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). Nexperia does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — Nexperia products are sold subject to the general terms and conditions of commercial sale, as published at <u>http://www.nexperia.com/profile/terms</u>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of Nexperia products by customer.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific Nexperia product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. Nexperia accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without Nexperia's warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond Nexperia's specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies Nexperia for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond Nexperia's standard warranty and Nexperia's product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### **Trademarks**

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

All information provided in this document is subject to legal disclaimers.

**Product data sheet**

Rev. 2 — 15 June 2022

# Contents

| 1. General description                              | 1  |

|-----------------------------------------------------|----|

| 2. Features and benefits                            | 1  |

| 3. Applications                                     | 1  |

| 4. Ordering information                             | 2  |

| 5. Marking                                          | 2  |

| 6. Functional diagram                               | 3  |

| 7. Pinning information                              | 4  |

| 7.1. Pinning                                        | 4  |

| 7.2. Pin description                                | 4  |

| 8. Functional description                           | 5  |

| 8.1. Functional behavior                            | 5  |

| 8.2. Window of I/O communication                    | 6  |

| 8.3. Shutdown sequence                              | 6  |

| 8.4. UVLO                                           | 7  |

| 8.5. EMI filter                                     | 7  |

| 8.6. ESD protection                                 | 7  |

| 9. Limiting values                                  | 8  |

| 10. Recommended operating conditions                |    |

| 11. Electrical characteristics                      | 9  |

| 11.1. Waveforms and test circuits                   | 12 |

| 12. Application information                         | 13 |

| 13. Design and assembly recommendations             |    |

| 13.1. PCB design guidelines                         | 14 |

| 13.2. PCB assembly guidelines for Pb-free soldering |    |

| 14. Package outline                                 | 16 |

| 15. Abbreviations                                   |    |

| 16. Revision history                                |    |

| 17. Legal information                               | 18 |

|                                                     |    |

© Nexperia B.V. 2022. All rights reserved

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com Date of release: 15 June 2022

单击下面可查看定价,库存,交付和生命周期等信息

>>Nexperia(安世)