# **NCA9700**

Level translating Fm+ I<sup>2</sup>C bus repeater/accelerator Rev. 1 — 10 September 2024

### Product data sheet

### 1. General description

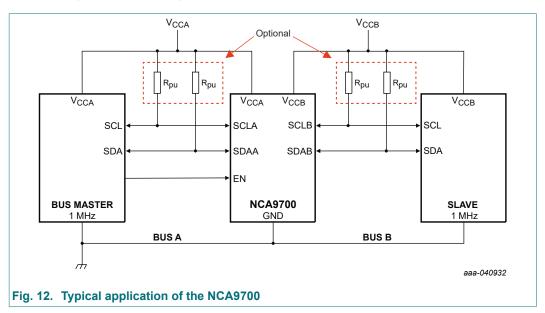

The NCA9700 is a dual-channel bidirectional repeater for I<sup>2</sup>C and SMBus/PMBus applications. It targets the Fast-mode Plus (Fm+) of the I<sup>2</sup>C protocol, making the true 1 MHz operation possible without violating I<sup>2</sup>C timing specifications. This is achieved by using edge accelerators added at all NCA9700 ports that speed up the LOW-to-HIGH transitions of I<sup>2</sup>C input and output signals.

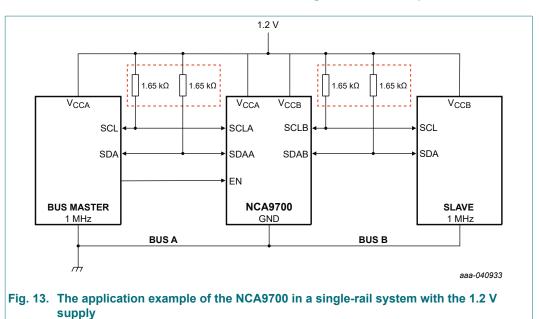

The NCA9700 provides the buffering for both clock (SCL) and data (SDA) I<sup>2</sup>C signals with the voltage level translation possibility (up and down) at the same time. The unique feature of the IC is the same operating voltage range of 1.08 V to 3.6 V that can be applied at both port A and port B of the device. This offers more flexibility in how the device can be used in the target application. Multiple NCA9700s can be connected in series or in star, and their ports A and B can be exchanged. Only when the I<sup>2</sup>C clock stretching needs to be supported, the NCA9700 port A must be connected to the I<sup>2</sup>C Master side and the NCA9700 port B to the I<sup>2</sup>C Slave side.

The NCA9700 features integrated pull-up resistors of 4.3 k $\Omega$  at each I/O pin. This simplifies the system implementation and reduces BOM count. Though external pull-up resistors are not required, they might be added to shorten the rise times of I<sup>2</sup>C signals even further.

The NCA9700 provides true signal buffering as the device implementation does not use the pass-FET topology. No static or incremental offsets are needed either, and the lock-free operation is guaranteed by an innovative implementation of the buffers. The very low V<sub>OL</sub> levels on port A and B improve the noise margin in the application and the potential noise components of input signals are filtered out by Schmitt trigger inputs. To reduce EMI, the negative edges of output signals are slew-controlled.

The NCA9700 is well suited for high-performance low-power applications which use the I<sup>2</sup>C communication protocol.

### 2. Features and benefits

- Two-channel bidirectional I<sup>2</sup>C buffer

- Voltage level translation from 1.08 V to 3.6 V at both port A and port B with unconstrained combination of the supply voltage levels

- Guaranteed 1 MHz operation (true I<sup>2</sup>C Fast-mode Plus, Fm+)

- Support for the I<sup>2</sup>C Standard-mode (Sm) and Fast-mode (Fm) operation

- No static voltage offset

- Very low V<sub>OL</sub> on I/O pins of the port A; V<sub>OL</sub> regulated to 0.1V<sub>CCB</sub> on I/O pins of the port B

- Input and output rising-edge signal accelerators at all I/Os

- Active-HIGH enable input referenced to V<sub>CCA</sub> supply

- Lock-free operation

- Glitch-free and sequence-independent IC power-up

- Open-drain input/outputs

- Series connection and star connection of NCA9700 devices possible

- I<sup>2</sup>C clock stretching support

- Compatibility with I<sup>2</sup>C bus and SMBus protocols

- Latch-up performance exceeds 100 mA per JESD 78B Class II

# nexperia

- ESD protection:

- HBM: ANSI/ESDA/JEDEC JS-001 class 2 exceeds 2 kV

- CDM: ANSI/ESDA/JEDEC JS-002 class C3 exceeds 1 kV

- Very small footprint

# 3. Applications

- Smart phones and tablets

- Portable medical devices

- Portable instrumentation and test equipment

- Devices for IoT applications

- Power-sensitive applications

## 4. Ordering information

### Table 1. Ordering information

| Type number | Package           | Package |                                                                        |          |  |  |  |  |

|-------------|-------------------|---------|------------------------------------------------------------------------|----------|--|--|--|--|

|             | Temperature range | Name    | Description                                                            | Version  |  |  |  |  |

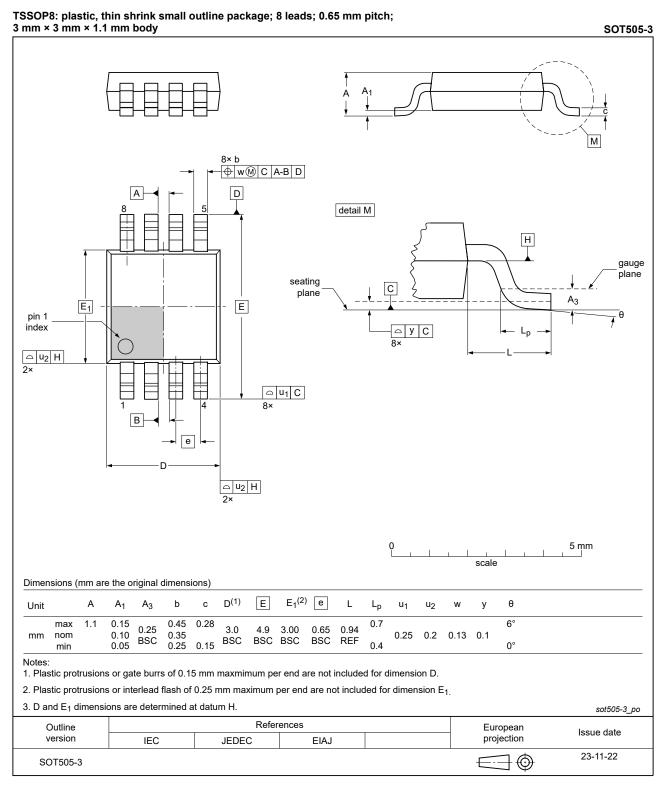

| NCA9700DQ   | -40 °C to +85 °C  | TSSOP8  | plastic thin shrink small outline package; 8 leads;<br>body width 3 mm | SOT505-3 |  |  |  |  |

## 5. Marking

| Table 2. Marking |              |

|------------------|--------------|

| Type number      | Marking code |

| NCA9700DQ        | z3           |

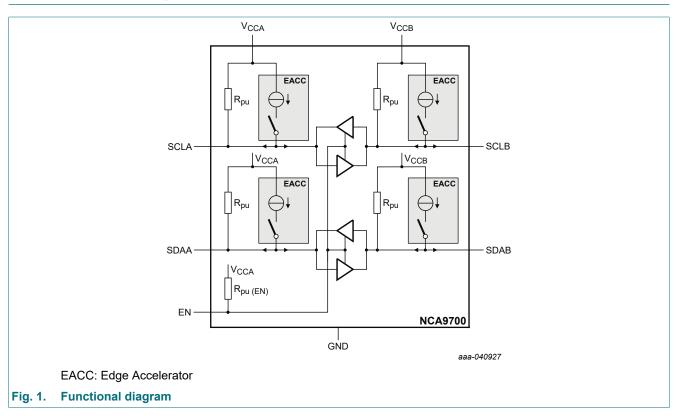

# 6. Functional diagram

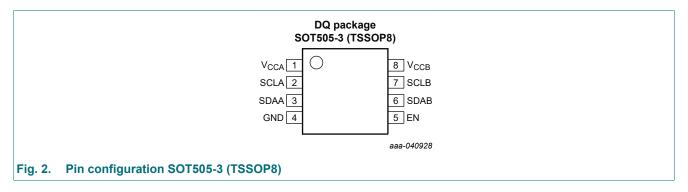

# 7. Pinning information

### 7.1. Pinning

### 7.2. Pin description

| Table 3. Pin descrip |     |                                                                               |

|----------------------|-----|-------------------------------------------------------------------------------|

| Symbol               | Pin | Description                                                                   |

| V <sub>CCA</sub>     | 1   | port A supply voltage                                                         |

| SCLA                 | 2   | serial clock port A bus                                                       |

| SDAA                 | 3   | serial data port A bus                                                        |

| GND                  | 4   | supply ground (0 V)                                                           |

| EN                   | 5   | active HIGH repeater enable input; referenced to $V_{\mbox{\scriptsize CCA}}$ |

| SDAB                 | 6   | serial data port B bus                                                        |

| SCLB                 | 7   | serial clock port B bus                                                       |

| V <sub>CCB</sub>     | 8   | port B supply voltage                                                         |

# 8. Functional description

### 8.1. Overview

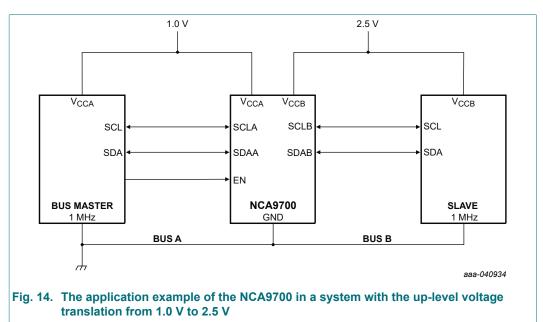

The NCA9700 is a dual-channel bidirectional voltage translating repeater intended for I<sup>2</sup>C and SMBus/PMBus applications. It includes two bidirectional open-drain buffers for the clock (SCL) and data (SDA) buses of an I<sup>2</sup>C system. The levels of signals transferred via I<sup>2</sup>C buses can be up- or down-translated by the NCA9700 within the voltage range of 1.08 V to 3.6 V. The operating supply voltage range of the NCA9700 port A and port B is the same and there are no restrictions in the supply voltage choice nor dependencies between them.

The NCA9700 provides three main functions:

- 1. Signal regeneration: the device receives I<sup>2</sup>C signals and retransmits them regenerated; since no pass-FET based topology is used, an I<sup>2</sup>C bus is effectively split into two isolated bus segments with a reduced load capacitance. As a result, higher capacitive loads can be driven than it is possible without the NCA9700.

- **2. Signal acceleration:** the NCA9700 reduces the LOW-to-HIGH transition time of input and output I<sup>2</sup>C signals. This is especially relevant for systems with heavy loaded I<sup>2</sup>C-buses as a large bus RC time constant means a long signal rise time. The signal acceleration is realized by Edge Accelerators available at all NCA9700 I/Os. Thanks to the Edge Accelerators, the I<sup>2</sup>C timing, and the data set-up time in particular, can be improved without using low-ohmic pull-up resistors and thus without additional static current consumption.

**3.** Voltage translation: the NCA9700 offers an up- and down-level translation of transmitted signals. The supported voltage range is from 1.08 V to 3.6 V for both NCA9700 ports; there are no restrictions on the voltage level selection for port A and B.

### 8.2. Key features

### Bidirectional voltage translation at symmetrical operating voltage range

Unlike most traditional I<sup>2</sup>C repeaters, the NCA9700 features a symmetrical operating supply voltage range of 1.08 V to 3.6 V. This means that the supply voltages at port A and B can be exactly the same. There are no restrictions or dependencies between them.

The NCA9700 provides bidirectional, up and down, voltage-level translation over its whole operating voltage range. For example, a voltage down-translation from 3.6 V at port A to 1.08 V at port B or the operation at the lowest allowed voltage of the NCA9700, that is 1.08 V, at both port A and port B (no voltage translation) can be easily realized. This is not possible with other I<sup>2</sup>C repeaters, which typically are implemented with the minimum supply voltage at port B higher than the supply voltage at port A.

### Edge acceleration

The edge acceleration is another unique feature of the NCA9700. The edge accelerators installed at all four I/Os of the NCA9700 speed-up LOW-to-HIGH transitions of I<sup>2</sup>C signals. By this, the LOW-to-HIGH transition times are less dependent on the I<sup>2</sup>C-bus RC time constant, which is defined by a pull-up resistor ( $R_{pu}$ ) and a load capacitor ( $C_L$ ) on the bus. Especially the choice of the pull-up resistor value requires a careful consideration. Too large pull-up resistor value means long LOW-to-HIGH transition times, while too small resistance value results in a high current consumption. The use of edge accelerators in the NCA9700 simplifies this trade-off. The accelerators modify the charging characteristic of the bus capacitors from exponential to partially-and fully-linear for input and output bus load capacitors, respectively.

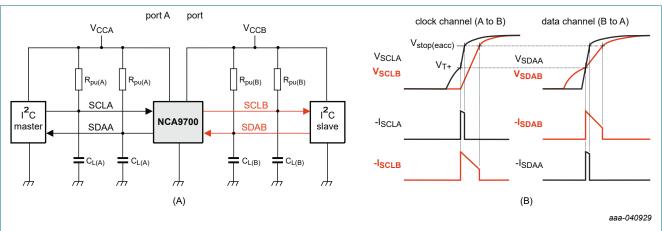

The NCA9700 edge accelerators are implemented as voltage-controlled current sources, see Fig. 1. Let's assume that an I<sup>2</sup>C signal with a LOW-to-HIGH transition needs to be transmitted from port A to port B of the NCA9700. When an (input) I<sup>2</sup>C signal at port A crosses V<sub>T+</sub> threshold level, which corresponds to the voltage of  $0.425V_{CCA}$ , the input Edge Accelerator (EACC) is activated. As a result, the current starts flowing out of an input pin at port A and the capacitance at port A (C<sub>L(A)</sub>) is getting charged. When the input signal at port A reaches the Edge Accelerator stop level, V<sub>stop(eacc)</sub>, equal to  $0.8V_{CCA}$ , the input Edge Accelerator is disabled and the current flow stopped. Since the Edge Accelerator current actively helps to charge the input bus capacitance, the input signal transition is accelerated. This happens without a current consumption penalty as the Edge Accelerator current is provided shortly, only during the most critical timing window of the input signal.

The output Edge Accelerator is activated at the same time as the input Edge Accelerator. It monitors the NCA9700 output port, that is port B in case of the A to B transition. Since the output port is normally at logic 0 before a LOW-to-HIGH signal transition takes place, the capacitance of the output port needs to be fully charged from the  $V_{OL}$  level to the target voltage level. The output Edge Accelerator current flowing out of the output pin at port B does most of the charging as the charge current via the pull-up resistor(s) is typically smaller. Therefore, unlike in case of the input Edge Accelerator, the charging characteristic of the output port bus capacitor is fully linear till the Edge Accelerator gets deactivated. As for the input Edge Accelerator, this happens when the stop level  $V_{stop(eacc)}$  of the output signal, here  $0.8V_{CCB}$ , is reached.

In Fig. 3, the NCA9700 I/O pin voltages and Edge Accelerator currents for LOW-to-HIGH transitions on the I<sup>2</sup>C clock and data signals are shown. The timing relations between input and output signals, assuming that the bus capacitance at port A is much lower than the bus capacitance at port B, are indicated. Clearly, a larger bus capacitance results in less steeper charging curve and a longer charging current pulse.

It may happen that when the output bus is very lightly loaded compared to the input bus, the accelerated output signal precedes the input signal. This results in the negative LOW-to-HIGH propagation delay,  $t_{PLH}$ , as seen for some cases reported in <u>Table 9</u>.

The activation times of the Edge Accelerators and their current capability depend on the bus capacitance values, pull-up resistance values, and the supply voltages at port A and port B. These parameters impact directly the charging times of the input bus and output bus capacitors and thus the transition times of the input and output signals.

(A) Example I<sup>2</sup>C system; arrows indicate the assumed signal flow.

(B) I/O pin voltages and corresponding Edge Accelerator currents assuming  $C_{L(A)} \ll C_{L(B)}$  (for simplicity, static currents due to pull-up resistors are omitted in the shown current waveforms).

#### Fig. 3. The acceleration of LOW-to-HIGH I<sup>2</sup>C clock and data signal transitions by the NCA9700

The current capability of the NCA9700 Edge Accelerators for clock and data channels is different. The currents of the input and output Edge Accelerators for the clock channel (SCLA and SCLB pins) are about 25 % to 30 % lower than the currents of the input and output Edge Accelerators for the data channel (SDAA and SDAB pins). This stems from the fact that the activation window of the input Edge Accelerator (corresponding to the input signal voltage levels from 0.425V<sub>CC</sub> to 0.8V<sub>CC</sub>, where V<sub>CC</sub> is V<sub>CCA</sub> or V<sub>CCB</sub>) lies outside the timing window of an I<sup>2</sup>C clock signal (corresponding to the input signal voltage range from 0 V to 0.3V<sub>CC</sub>, where V<sub>CC</sub> is V<sub>CCA</sub> or V<sub>CCB</sub>) that is critical for I<sup>2</sup>C parameters such as the data set-up time (see next section for more details). The Edge Accelerator current is thus reduced to save the total device power.

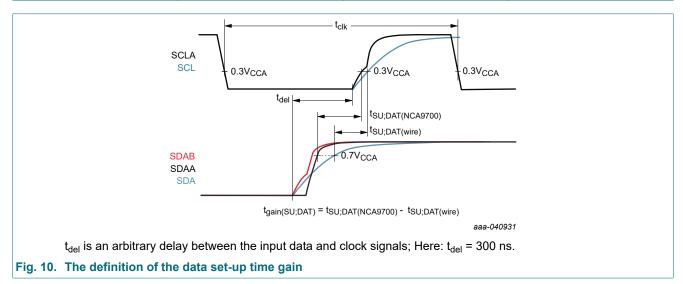

### Data set-up time gain

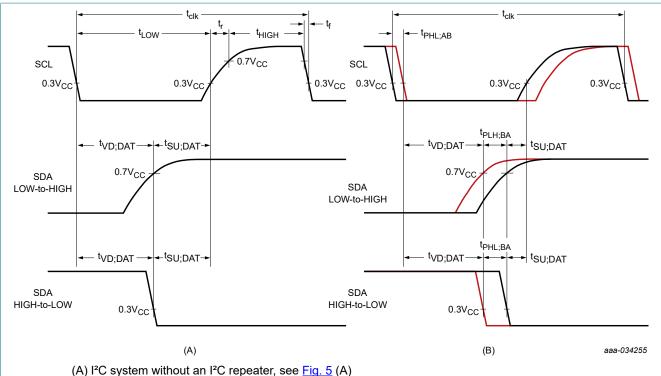

The timing of I<sup>2</sup>C signals is governed by strict specifications of the I<sup>2</sup>C protocol. The parameters such as:

- LOW and HIGH periodes, t<sub>LOW</sub> and t<sub>HIGH</sub> (for I<sup>2</sup>C clock signal, SCL)

- rise and fall times, t<sub>r</sub> and t<sub>f</sub> (for I<sup>2</sup>C clock and data signals, SCL and SDA)

- data valid time, t<sub>VD;DAT</sub>

- data set-up time, t<sub>SU;DAT</sub>

play the key role. The definitions of these parameters are shown in Fig. 4 (A), and their values for the  $I^2C$  Fast-mode Plus are listed in Table 4.

# NCA9700

### Level translating Fm+ I<sup>2</sup>C bus repeater/accelerator

(B) I<sup>2</sup>C system with an I<sup>2</sup>C repeater (black: port A signals, red: port B signals), see Fig. 5 (B).

### Fig. 4. Timing diagram of I<sup>2</sup>C clock and data signals

| Table 4. Critical timing parameters of the I <sup>2</sup> C protocol and their values for Fm+ |                                                      |                           |     |      |  |  |  |

|-----------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------|-----|------|--|--|--|

| Parameter                                                                                     | Description                                          | Min                       | Мах | Unit |  |  |  |

| t <sub>LOW</sub>                                                                              | LOW period of I <sup>2</sup> C clock signal          | 500                       | -   | ns   |  |  |  |

| t <sub>HIGH</sub>                                                                             | HIGH per period of I <sup>2</sup> C clock signal     | 260                       | -   | ns   |  |  |  |

| t <sub>r</sub>                                                                                | Rise time of I <sup>2</sup> C clock and data signals | -                         | 120 | ns   |  |  |  |

| t <sub>f</sub>                                                                                | Fall time of I <sup>2</sup> C clock and data signals | 20x(V <sub>CC</sub> /5.5) | 120 | ns   |  |  |  |

| t <sub>VD;DAT</sub>                                                                           | Data valid time                                      | -                         | 450 | ns   |  |  |  |

| t <sub>SU;DAT</sub>                                                                           | Data set-up time                                     | 50                        | -   | ns   |  |  |  |

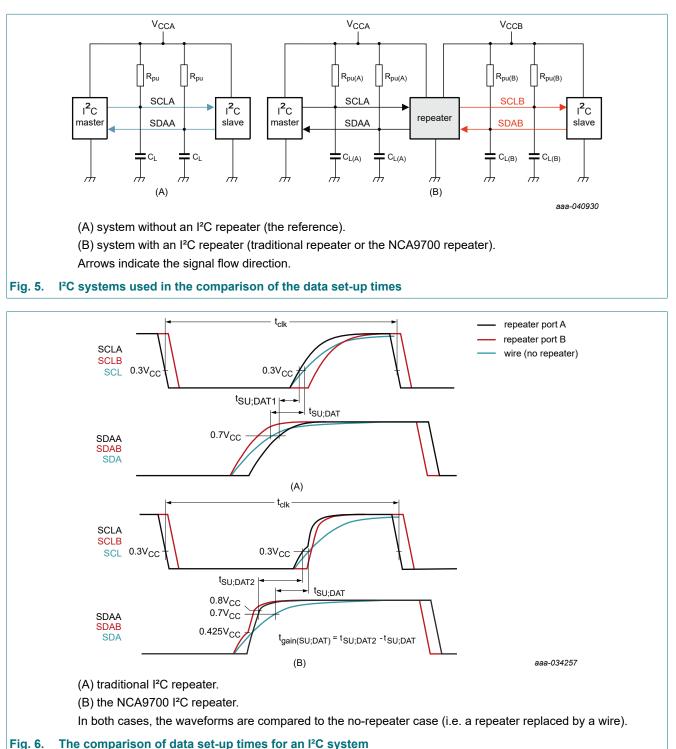

When an I<sup>2</sup>C repeater is introduced to the I<sup>2</sup>C system for bus capacitance buffering, the repeater propagation delays are added and the signal timing changed. The new situation is shown in Fig. 4 (B) with the depicted waveforms corresponding to the I<sup>2</sup>C system shown in Fig. 5 (B). Clearly, the timing budget is now reduced and reaching the target clock frequency of 1 MHz is often not possible. This is because in the Fm+ there is no time margin left for the repeater delays (i.e. in the worst case,  $t_{LOW} + t_{HIGH} + t_r + t_f = t_{clk} = 1000$  ns, which is, the clock period of 1 MHz clock).

The Edge Accelerators of the NCA9700 address exactly this problem. By the acceleration of I<sup>2</sup>C input and output signals, the timing margin is regained. In particular, the propagation delay of the NCA9700 repeater during a LOW-to-HIGH transition is considerably reduced. This is because the output Edge Accelerator, which speeds up the output signal, is activated as soon as a LOW-to-HIGH transition of the input signal is detected.

The impact of this is illustrated in the following figures. In Fig. 5,  $I^2C$  systems with and without an  $I^2C$  repeater are compared. The arrows in the figures indicate the signal flow reflecting the worst case situation from the  $I^2C$  timing point of view, that is the  $I^2C$  clock provided by the Master (A to B

communication) and the I<sup>2</sup>C data read out from the Slave (B to A communication).<sup>1</sup>

NCA9700

<sup>1</sup> Assuming that the repeater is symmetrical, an alternative worst-case timing-wise signal flow is: B to A for an I<sup>2</sup>C clock signal, and A to B for an I<sup>2</sup>C data signal.

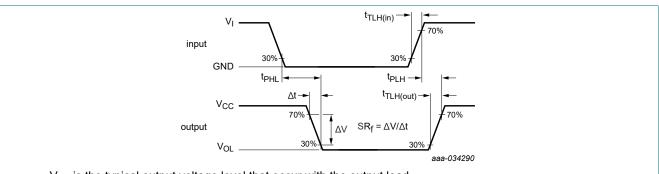

In Fig. 6, the corresponding timing diagrams with the focus on the data set-up time parameter for the LOW-to-HIGH transition<sup>2</sup> are shown. The data set-up time is measured between  $l^2C$  data and clock signals at port A of the  $l^2C$  repeaters.

In <u>Fig. 6</u> (A), data and clock signals for an I<sup>2</sup>C system with a traditional I<sup>2</sup>C repeater are shown. They are compared with similar signals of the system without a repeater (i.e. a repeater replaced with a wire). The slopes of the data and clock signals in the system with a repeater are steeper

2 The LOW-to-HIGH transition improvement is addressed only.

because the effective I<sup>2</sup>C bus capacitance is reduced. The data set-up time of the I<sup>2</sup>C system with a traditional repeater,  $t_{SU:DAT1}$ , is very short.

In Fig. 6 (B), the same waveforms but for the NCA9700 replacing a traditional I<sup>2</sup>C repeater are presented, and compared with the waveforms of the system with no repeater (the same as in Fig. 6 (A)). The slopes of the input and output data and clock signals are much steeper thanks to the NCA9700 Edge Accelerators. Especially the timing of the data signal is improved (the start and stop levels of the input Edge Accelerator are indicated on the input data signal waveform). Besides, the data signal propagation delay is shorten considerably as the generation of the output signal is speeded up by the output Edge Accelerator. The data set-up time in this case,  $t_{SU;DAT2}$ , is much longer. To illustrate the true advantage of the NCA9700 repeater with respect to the no-repeater case, the data set-up time gain,  $t_{gain(SU;DAT)}$ , is introduced. This parameter is calculated as the difference between the data set-up times of the NCA9700 and a wire (no repeater case). The data set-up time gain is one of the key parameters of the NCA9700 and it is specified in Table 10.

### Schmitt trigger inputs

Each I/O pin of the NCA9700 includes a Schmitt trigger comparator for detecting the logic level of an input signal. The same comparator activates also the NCA9700 input Edge Accelerator. When a positive going input signal (LOW-to-HIGH transition) crosses the comparator  $V_{T+}$  level, that is  $0.425V_{CCA}$  and  $0.425V_{CCB}$  for input stages at port A and B, respectively, it is interpreted as logic 1 (HIGH). Similarly, when a negative going input signal (HIGH-to-LOW transition) crosses the comparator  $V_{T-}$  level, that is  $0.25V_{CCA}$  and  $0.25V_{CCB}$  for input stages at port A and B, respectively, it is interpreted as logic 0 (LOW). The difference between switching levels of the input comparator, thus  $V_{T+} - V_{T-}$ , defines the comparator hysteresis. It is guaranteed that the comparator hysteresis is never smaller than  $0.130V_{CC}$ , which helps with noise rejection on input signals.

### Integrated pull-up resistors

The NCA9700 has integrated pull-up resistors of 4.3 k $\Omega$  on all I/O pins. Therefore, no additional external pull-up resistors are required to pull-up I<sup>2</sup>C data and clock buses. However, a user may add external pull-up resistors on all or selected bus segments to reduce the effective pull-up resistance. This has a two-fold effect: it reduces the bus capacitor initial charging time (i.e. from 0V to 0.425V<sub>CC</sub>), defined by the bus RC time constant, and provides an extra current when the Edge Accelerator is already activated. This is especially relevant for heavy-loaded I<sup>2</sup>C buses but comes at the cost of extra static current consumption. It is recommended, though not required, to use external pull-up resistors on buses connected to port B. This improves the output signal settle time as the V<sub>OL</sub> of the pins at port B are regulated.

As long as the NCA9700 supply is present, the internal resistors always pull the I<sup>2</sup>C buses up. This is to prevent that these buses are floating when the NCA9700 is disabled (EN = LOW) and no external pull-up resistors are present. When the supply at the NCA9700 port A or B is not available (below the supply V<sub>UVLO</sub> level), the internal pull-up resistors are deactivated to block the leakage path from an I/O to supply pin.

### **Ultra-low power consumption**

The NCA9700 implementation facilitates the system-level power consumption reduction. When disabled (EN = LOW), the IC keeps only internal bias/reference blocks active. This allows nearly a factor of 3 reduction of the total IC current consumption compared to the enable state (EN = HIGH).

The NCA9700 partial power down, when the supply of port A or port B is removed, is also possible. In this mode, the active power supply does not consume any current. Obviously, the IC drivers are switched off then so signal transmission is not possible.

### No static voltage offset

The NCA9700 does not use a static offset voltage to determine the driving side of the NCA9700. The device self-locking is prevented by an innovative implementation technique of the buffers. As

a result, this simple and reliable solution eliminates constraints on the NCA9700 connectivity and communication with other system components.

### **Regulated output voltage**

The NCA9700 pins at port B (SCLB and SDAB) have their  $V_{OL}$  level regulated to about 0.1 $V_{CCB}$ . This allows keeping  $V_{OL}$  levels very low, even at port B of the repeater where the clock stretching and acknowledge from a Slave device must be handled properly. Since the  $V_{OL}$  level is supplydependent rather than at the (nearly) fixed level, such a implementation relaxes the requirement on the external driver strength. It also makes the detection of the bus pull-down by an external driver more reliable especially when ground bouncing is present.

### **Clock stretching**

Although the NCA9700 ports are symmetrical and can be exchanged, when I<sup>2</sup>C clock stretching is used, an I<sup>2</sup>C Master must be connected to port A and I<sup>2</sup>C Slaves to port B. Also, the NCA9700 clock channel needs to be used for the transmission of the I<sup>2</sup>C clock signal.

The I<sup>2</sup>C protocol assumes that the clock signal is always generated by the Master. But when the clock stretching is applied, a Slave is allowed to hold down the I<sup>2</sup>C clock bus to communicate to the Master that the Slave is not ready. This means that the clock bus at port B is concurrently driven by two independent drivers: the NCA9700 internal clock driver of port B (clock transfer from the Master from port A to port B) and the external driver at port B (clock bus held by the Slave is communicated from port B to port A). Therefore, for a successful transmission of logic LOW from port B to port A while clock stretching, a correct detection of the presence of an external driver is critical. For this, the NCA9700 V<sub>ILC</sub>, contention LOW-level input voltage, needs to be satisfied. V<sub>ILC</sub> defines the minimum input voltage at the NCA9700 SCLB pin required for the correct detection of the clock bus pull down by an external driver (i.e. an internal driver of an I<sup>2</sup>C Slave). The maximum V<sub>ILC</sub> is equal to half of the V<sub>OL</sub> level for the SCLB pin.

As already mentioned, the V<sub>OL</sub> of the SCLB pin is regulated to about 0.1V<sub>CCB</sub>. For the clock stretching to be detected, an external driver needs to pull down the SCLB pin to V<sub>ILC</sub> level or below. To calculate the required strength (resistance) of the internal pull- down MOSFET in the I<sup>2</sup>C Slave output driver, the V<sub>OL</sub> value at given I<sub>OL</sub> current from <u>Table 8</u> can be used. Alternatively, a user can measure the V<sub>OL</sub> level of the SCLB pin at the known effective pull-up resistance.

### Acknowledgment signal handling

In the I<sup>2</sup>C protocol, each group of eight bits transmitted on the data bus must be followed by an acknowledgement (ACK) bit. The ACK bit is a logic 0 (LOW) and is sent by a receiver of the data (e.g. by an I<sup>2</sup>C Slave when an I<sup>2</sup>C Master sends data to the Slave). The correct acknowledgement signal handling means the correct detection of a bus pull-down initiated by an external driver (e.g. of an I<sup>2</sup>C Slave device) in different transmission conditions. This is fundamentally difficult when the V<sub>OL</sub> level of the pin where the pull-down must be detected is low or when an edge accelerator is present, like in the NCA9700. The external pull-down detection is also influenced by system parameters, such a supply voltage, bus load capacitance, and pull-up resistance.

To resolve this, the NCA9700 provides a multi-level solution. If the ACK bit is proceeded by the last data bit (of a 8-bit package) being a logic 0 (an equivalent of a LOW to LOW transition), the NCA9700 uses the same mechanism as it is used on the clock pin (SCLB pin) for the clock stretching detection (which can also be seen as a LOW to LOW transition).

If the ACK bit is proceeded by the data bit being a logic 0 (LOW) but the ACK signal is a bit delayed with respect to the clock signal (I<sup>2</sup>C protocol defines the time window of  $t_{VD;ACK}$ , data valid acknowledgement time, for sending the acknowledgement), the data bus is released and it will be pulled up by pull-up resistor(s) and the Edge Accelerator. In this case, the pull-up elements will be working against the driver of an external device that tries to pull the bus down; as a result, the bus will probably settle at some intermediate level. For this situation the NCA9700 provides a timer-based solution. The 120 ns-timer (typical) is started at the same instance as the output Edge Accelerator on this pin is activated. The timer defines the time window in which the data bus

voltage is monitored by the NCA9700 internal circuitry. If the bus voltage remains below the start level of the output Edge Accelerator when the timer times out, the ACK signal is detected. If the data bus voltage crosses the Edge Accelerator start level before the timer times out, the timer is reset and re-started at the crossing level again. The bus voltage is again monitored and compared against the output Edge Accelerator stop level. If the stop level is not crossed before the timer times out, the ACK signal is detected.

If the ACK signal is proceeded by the data bit being a logic 1 (HIGH), the ACK signal sent by an external device is interpreted as a HIGH to LOW transition and it will be always resolved correctly by the NCA9700.

The timer-based solution for the acknowledgement signal handling is present at both the SDAA pin (port A) and the SDAB pin (port B). In this way, the ACK signals sent by both Master and Slave devices can be handled properly.

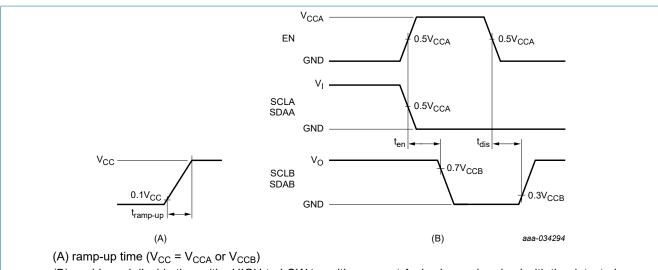

### Active high enable input

The NCA9700 is disabled when the V<sub>CCA</sub> and V<sub>CCB</sub> supply voltages are below the supply V<sub>start</sub> level. When the V<sub>start</sub> level is reached and the EN pin is left unconnected, the NCA9700 will be enabled by default as the EN pin, referenced to the V<sub>CCA</sub> supply, is pulled up internally. By driving the EN pin externally, enabling or disabling of the NCA9700 is possible under system control, for example to isolate a badly behaved I<sup>2</sup>C Slave on the system power up.

The logic level of the enable pin is sensed by a comparator with hysteresis. A small filter placed on the EN pin prevent incorrect switching on/off of the IC in case of noise on this pin.

The NCA9700 can be started correctly only when all buses connected to the repeater ports are in the idle state (i.e. pulled up). Not complying with this may lead to the device lockup. To prevent system failures, the EN pin should change state only when I<sup>2</sup>C buses are idle too.

It is not allowed in the application to drive the EN pin from the source with a voltage higher than the  $V_{CCA}$  supply voltage. Therefore, at the power up it is recommended to tight the EN pin to the  $V_{CCA}$  pin or left it floating so that the EN pin voltage will follow the supply.

### Slew control for the falling edges

The HIGH-to-LOW transition times of output signals in an I<sup>2</sup>C repeater depend on the effective pull-up resistance at the given node and the resistance of the internal pull-down MOSFET. In the NCA9700, the internal pull-down MOSFETs are made strong to guarantee low  $V_{OL}$  levels over the full operating voltage range of the IC. Typically, this would result in very fast falling edges of output signals, especially for high supply voltages and low output capacitors, and could lead to EMI issues. To prevent this without compromising the timing of I<sup>2</sup>C signals, the output signals' falling edges are slew-controlled in the NCA9700. By this, a good independence on the I<sup>2</sup>C bus load conditions is achieved.

NCA9700

10 / 26

### 8.3. Functional modes

<u>Table 5</u> describes the functionality of the NCA9700 voltage-translating repeater dependent on the state of the EN pin.

### Table 5. Function table of the NCA9700

| EN pin | Function                                                                                            |

|--------|-----------------------------------------------------------------------------------------------------|

| LOW    | IC disabled; outputs disabled; buses at port A and port B pulled up (by internal pull-up resistors) |

| HIGH   | IC enabled; outputs enabled:<br>SCLA = SCLB<br>SDAA = SDAB                                          |

## 9. Limiting values

### Table 6. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

| Symbol                | Parameter                       | Conditions                                     | Min   | Max   | Unit |  |  |  |

|-----------------------|---------------------------------|------------------------------------------------|-------|-------|------|--|--|--|

| Voltages and currents |                                 |                                                |       |       |      |  |  |  |

| V <sub>CCA</sub>      | supply voltage port A           |                                                | -0.5  | +4.0  | V    |  |  |  |

| V <sub>CCB</sub>      | supply voltage port B           |                                                | -0.5  | +4.0  | V    |  |  |  |

| V <sub>I(EN)</sub>    | input voltage                   | EN pin                                         | -0.5  | +4.0  | V    |  |  |  |

| V <sub>I/O</sub>      | input/output voltage            | I <sup>2</sup> C bus voltage port A and port B | -0.5  | +4.0  | V    |  |  |  |

| I <sub>OL</sub>       | LOW-level output current        | I/Os port A and port B                         | -     | 25    | mA   |  |  |  |

| T <sub>stg</sub>      | storage temperature             |                                                | -65   | +150  | °C   |  |  |  |

| T <sub>j(max)</sub>   | maximum junction temperature    |                                                | -     | +125  | °C   |  |  |  |

| Electros              | tatic discharge                 |                                                |       |       |      |  |  |  |

| V <sub>ESD</sub>      | electrostatic discharge voltage | HBM: ANSI/ESDA/JEDEC JS-001 class 2            | -2000 | +2000 | V    |  |  |  |

|                       |                                 | CDM: ANSI/ESDA/JEDEC JS-002 class C3           | -1000 | +1000 | V    |  |  |  |

# 10. Recommended operating conditions

| Symbol           | Parameter             | Conditions | Min  | Max              | Unit |

|------------------|-----------------------|------------|------|------------------|------|

| V <sub>CCA</sub> | supply voltage port A |            | 1.08 | 3.6              | V    |

| V <sub>CCB</sub> | supply voltage port B |            | 1.08 | 3.6              | V    |

| V <sub>I/O</sub> | input/output voltage  | SCLA, SCLB | 0    | 3.6              | V    |

|                  |                       | SDAA, SDAB | 0    | 3.6              | V    |

|                  |                       | EN         | 0    | V <sub>CCA</sub> | V    |

| T <sub>amb</sub> | ambient temperature   |            | -40  | +85              | °C   |

# **11. Static characteristics**

### Table 8. Typical static characteristics

At recommended operating conditions; voltages are referenced to GND (ground = 0 V);

V<sub>CCA</sub> = 1.08 V to 3.6 V; V<sub>CCB</sub> = 1.08 V to 3.6 V; unless otherwise specified; Internal pull-up resistors used.

| Symbol             | Parameter                       | neter Conditions                                                                                                                                                       |     | T <sub>amb</sub> = −40 °C to +85 °C |      |    |  |

|--------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------|------|----|--|

|                    |                                 |                                                                                                                                                                        | Min | Typ[1]                              | Max  |    |  |

| Supplies           | S                               | 1                                                                                                                                                                      |     | 11                                  |      | I  |  |

| V <sub>start</sub> | start voltage                   | $V_{CCA}$ ; $V_{CCA}$ rising; $V_{CCB}$ = 1.08 V to 3.6 V or $V_{CCB}$ ; $V_{CCB}$ rising; $V_{CCA}$ = 1.08 V to 3.6 V                                                 | 495 | 680                                 | 1080 | mV |  |

| V <sub>UVLO</sub>  | undervoltage<br>lockout voltage | $V_{CCA}$ ; $V_{CCA}$ falling; $V_{CCB}$ = 1.08 V to 3.6 V or $V_{CCB}$ ; $V_{CCB}$ falling; $V_{CCA}$ = 1.08 V to 3.6 V                                               | -   | 485                                 | 800  | mV |  |

| I <sub>CCA</sub>   | supply current<br>port A        | SCLA = SDAA = V <sub>CCA</sub><br>(with internal pull-up resistors);<br>SCLB = SDAB = open<br>(with internal pull-up resistors);<br>V <sub>CCB</sub> = 1.2 V; EN = GND |     |                                     |      |    |  |

|                    |                                 | V <sub>CCA</sub> = 1.08 V                                                                                                                                              | -   | 4                                   | 7    | μA |  |

|                    |                                 | V <sub>CCA</sub> = 1.2 V                                                                                                                                               | -   | 5                                   | 8    | μA |  |

|                    |                                 | V <sub>CCA</sub> = 1.8 V                                                                                                                                               | -   | 8                                   | 12   | μA |  |

|                    |                                 | V <sub>CCA</sub> = 3.6 V                                                                                                                                               | -   | 17                                  | 24   | μA |  |

|                    |                                 | SCLA = SDAA = $V_{CCA}$<br>(with internal pull-up resistors);<br>SCLB = SDAB = open<br>(with internal pull-up resistors);<br>$V_{CCB}$ = 1.2 V; EN = $V_{CCA}$         |     |                                     |      |    |  |

|                    |                                 | V <sub>CCA</sub> = 1.08 V                                                                                                                                              | -   | 16                                  | 32   | μA |  |

|                    |                                 | V <sub>CCA</sub> = 1.2 V                                                                                                                                               | -   | 18                                  | 34   | μA |  |

|                    |                                 | V <sub>CCA</sub> = 1.8 V                                                                                                                                               | -   | 29                                  | 54   | μA |  |

|                    |                                 | V <sub>CCA</sub> = 3.6 V                                                                                                                                               | -   | 51                                  | 94   | μA |  |

|                    |                                 | SCLA = SDAA = GND; SCLB = SDAB = open<br>(with internal pull-up resistors);<br>V <sub>CCB</sub> = 1.2 V; EN = V <sub>CCA</sub>                                         |     |                                     |      |    |  |

|                    |                                 | V <sub>CCA</sub> = 1.08 V                                                                                                                                              | -   | 0.5                                 | 0.8  | mA |  |

|                    |                                 | V <sub>CCA</sub> = 1.2 V                                                                                                                                               | -   | 0.6                                 | 0.9  | mA |  |

|                    |                                 | V <sub>CCA</sub> = 1.8 V                                                                                                                                               | -   | 0.9                                 | 1.32 | mA |  |

|                    |                                 | V <sub>CCA</sub> = 3.6 V                                                                                                                                               | -   | 1.9                                 | 2.7  | mA |  |

|                    |                                 | SCLA = SDAA = open<br>(with internal pull-up resistors);<br>SCLB = SDAB = GND;<br>V <sub>CCB</sub> = 1.2 V; EN = V <sub>CCA</sub>                                      |     |                                     |      |    |  |

|                    |                                 | V <sub>CCA</sub> = 1.08 V                                                                                                                                              | -   | 0.5                                 | 0.8  | mA |  |

|                    |                                 | V <sub>CCA</sub> = 1.2 V                                                                                                                                               | -   | 0.6                                 | 0.9  | mA |  |

|                    |                                 | V <sub>CCA</sub> = 1.8 V                                                                                                                                               | -   | 0.9                                 | 1.32 | mA |  |

|                    |                                 | V <sub>CCA</sub> = 3.6 V                                                                                                                                               | -   | 1.9                                 | 2.7  | mA |  |

| Symbol               | Parameter                | Conditions                                                                                                                                                                                                                                                                                 | T,  | Unit   |      |    |

|----------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|------|----|

|                      |                          |                                                                                                                                                                                                                                                                                            | Min | Typ[1] | Max  |    |

| I <sub>CCB</sub>     | supply current<br>port B | $\begin{aligned} & \text{SCLB} = \text{SDAB} = \text{V}_{\text{CCB}} \\ & \text{(with internal pull-up resistors);} \\ & \text{SCLA} = \text{SDAA} = \text{open} \\ & \text{(with internal pull-up resistors);} \\ & \text{V}_{\text{CCA}} = 1.2 \text{ V; EN} = \text{GND} \end{aligned}$ |     |        |      |    |

|                      |                          | V <sub>CCB</sub> = 1.08 V                                                                                                                                                                                                                                                                  | -   | 4      | 7    | μA |

|                      |                          | V <sub>CCB</sub> = 1.2 V                                                                                                                                                                                                                                                                   | -   | 5      | 8    | μA |

|                      |                          | V <sub>CCB</sub> = 1.8 V                                                                                                                                                                                                                                                                   | -   | 8      | 11   | μA |

|                      |                          | V <sub>CCB</sub> = 3.6 V                                                                                                                                                                                                                                                                   | -   | 17     | 24   | μA |

|                      |                          | SCLB = SDAB = $V_{CCB}$<br>(with internal pull-up resistors);<br>SCLA = SDAA = open<br>(with internal pull-up resistors);<br>$V_{CCA}$ = 1.2 V; EN = $V_{CCA}$                                                                                                                             |     |        |      |    |

|                      |                          | V <sub>CCB</sub> = 1.08 V                                                                                                                                                                                                                                                                  | -   | 13     | 27   | μA |

|                      |                          | V <sub>CCB</sub> = 1.2 V                                                                                                                                                                                                                                                                   | -   | 15     | 27   | μA |

|                      |                          | V <sub>CCB</sub> = 1.8 V                                                                                                                                                                                                                                                                   | -   | 25     | 40   | μA |

|                      |                          | V <sub>CCB</sub> = 3.6 V                                                                                                                                                                                                                                                                   | -   | 44     | 72   | μA |

|                      |                          | SCLB = SDAB = GND; SCLA = SDAA = open<br>(with internal pull-up resistors);<br>$V_{CCA} = 1.2 V$ ; EN = $V_{CCA}$                                                                                                                                                                          |     |        |      |    |

|                      |                          | V <sub>CCB</sub> = 1.08 V                                                                                                                                                                                                                                                                  | -   | 0.5    | 0.8  | mA |

|                      |                          | V <sub>CCB</sub> = 1.2 V                                                                                                                                                                                                                                                                   | -   | 0.6    | 0.9  | mA |

|                      |                          | V <sub>CCB</sub> = 1.8 V                                                                                                                                                                                                                                                                   | -   | 0.9    | 1.32 | mA |

|                      |                          | V <sub>CCB</sub> = 3.6 V                                                                                                                                                                                                                                                                   | -   | 1.9    | 2.7  | mA |

|                      |                          | SCLB = SDAB = open<br>(with internal pull-up resistors);<br>SCLA = SDAA = GND;<br>$V_{CCA} = 1.2 V$ ; EN = $V_{CCA}$                                                                                                                                                                       |     |        |      |    |

|                      |                          | V <sub>CCB</sub> = 1.08 V                                                                                                                                                                                                                                                                  | -   | 0.2    | 0.4  | mA |

|                      |                          | V <sub>CCB</sub> = 1.2 V                                                                                                                                                                                                                                                                   | -   | 0.3    | 0.5  | mA |

|                      |                          | V <sub>CCB</sub> = 1.8 V                                                                                                                                                                                                                                                                   | -   | 0.5    | 0.8  | mA |

|                      |                          | V <sub>CCB</sub> = 3.6 V                                                                                                                                                                                                                                                                   | -   | 1.1    | 1.6  | mA |

| I <sub>CC(tot)</sub> | total supply<br>current  | $I_{CCA} + I_{CCB}$ ; SCLA = SDAA = $V_{CCA}$ (with<br>internal pull-up resistors); SCLB = SDAB = $V_{CCB}$<br>(with internal pull-up resistors);<br>$V_{CCA} = V_{CCB} = 1.2 V$                                                                                                           |     |        |      |    |

|                      |                          | EN = V <sub>CCA</sub>                                                                                                                                                                                                                                                                      | -   | 35     | -    | μA |

|                      |                          | EN = GND                                                                                                                                                                                                                                                                                   | -   | 11     | -    | μA |

13 / 26

| Symbol                      | Parameter                              | Conditions                                                                                                                                       | Ta                  | <sub>mb</sub> = -40 °C | to +85 °C                    | Unit     |

|-----------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|------------------------------|----------|

|                             |                                        |                                                                                                                                                  | Min                 | Typ[1]                 | Max                          | 1        |

| Input an                    | d output SCLA,                         | SDAA, SCLB, SDAB pins                                                                                                                            | 1                   |                        | 1                            |          |

| V <sub>T+</sub>             | positive-going<br>threshold<br>voltage | input of I/O circuit;<br>input edge accelerator start voltage;<br>SCLA; SDAA; SCLB; SDAB;<br>$V_{CC}$ : $V_{CCA}$ or $V_{CCB}$ = 1.08 V to 3.6 V | 0.35V <sub>CC</sub> | 0.43V <sub>CC</sub>    | 0.50V <sub>CC</sub>          | V        |

| V <sub>T</sub> -            | negative-going<br>threshold<br>voltage | input of I/O circuit;<br>SCLA; SDAA; SCLB; SDAB;<br>$V_{CC}$ : $V_{CCA}$ or $V_{CCB}$ = 1.08 V to 3.6 V                                          | 0.19V <sub>CC</sub> | 0.25V <sub>CC</sub>    | 0.32V <sub>CC</sub>          | V        |

| V <sub>HYS</sub>            | hysteresis<br>voltage                  | input of I/O circuit;<br>SCLA; SDAA; SCLB; SDAB; $(V_{T+} - V_{T-})$<br>$V_{CC}$ : $V_{CCA}$ or $V_{CCB}$ = 1.08 V to 3.6 V                      | 0.13V <sub>CC</sub> | 0.17V <sub>CC</sub>    | 0.22V <sub>CC</sub>          | V        |

| V <sub>stop</sub><br>(eacc) | edge<br>accelerator<br>stop voltage    | SCLA; SDAA; SCLB; SDAB;<br>V <sub>CC</sub> : V <sub>CCA</sub> or V <sub>CCB</sub> = 1.08 V to 3.6 V                                              | 0.70V <sub>CC</sub> | 0.80V <sub>CC</sub>    | 0.89V <sub>CC</sub>          | V        |

| I <sub>O(eacc)</sub>        | edge<br>accelerator                    | SCLA; $V_I = 0.5V_{CCA}$ or<br>SCLB; $V_I = 0.5V_{CCB}$                                                                                          |                     |                        |                              |          |

|                             | output current                         | V <sub>CCA</sub> or V <sub>CCB</sub> = 1.08 V                                                                                                    | -                   | -1.6                   | -                            | mA       |

|                             |                                        | V <sub>CCA</sub> or V <sub>CCB</sub> = 1.2 V                                                                                                     | -                   | -2.3                   | -                            | mA       |

|                             |                                        | V <sub>CCA</sub> or V <sub>CCB</sub> = 1.8 V                                                                                                     | -                   | -6.3                   | -                            | mA       |

|                             |                                        | V <sub>CCA</sub> or V <sub>CCB</sub> = 3.6 V                                                                                                     | -                   | -19                    | -                            | mA       |

|                             |                                        | SDAA; $V_I = 0.5V_{CCA}$ or<br>SDAB; $V_I = 0.5V_{CCB}$                                                                                          |                     |                        |                              |          |

|                             |                                        | V <sub>CCA</sub> or V <sub>CCB</sub> = 1.08 V                                                                                                    | -                   | -2.2                   | -                            | mA       |

|                             |                                        | $V_{CCA}$ or $V_{CCB}$ = 1.2 V                                                                                                                   | -                   | -3.2                   | -                            | mA       |

|                             |                                        | V <sub>CCA</sub> or V <sub>CCB</sub> = 1.8 V                                                                                                     | -                   | -8.0                   | -                            | mA       |

|                             |                                        | $V_{CCA}$ or $V_{CCB}$ = 3.6 V                                                                                                                   | -                   | -23                    | -                            | mA       |

| V <sub>OL</sub>             | LOW-level                              | SCLA; SDAA                                                                                                                                       |                     |                        |                              |          |

|                             | output voltage                         | $I_{OL} = 0 \text{ mA}$ (internal current only);<br>$V_{IB} = 0 \text{ V or } V_{IA} = 0 \text{ V}$                                              | -                   | 5                      | 45                           | mV       |

|                             |                                        | $I_{OL}$ = 2 mA (external current; internal current<br>added); V <sub>IB</sub> = 0 V or V <sub>IA</sub> = 0 V                                    | -                   | 30                     | 190                          | mV       |

|                             |                                        | SCLB; SDAB                                                                                                                                       |                     |                        |                              |          |

|                             |                                        | I <sub>OL</sub> = 0 mA (internal current only); V <sub>IA</sub> = 0 V                                                                            |                     |                        |                              |          |

|                             |                                        | V <sub>CCB</sub> = 1.08 V to 1.2 V                                                                                                               | 65                  |                        | 175                          | mV       |

|                             |                                        | V <sub>CCB</sub> = 1.8 V                                                                                                                         | 125                 | 0.1V <sub>CCB</sub>    | 235                          | mV       |

|                             |                                        | V <sub>CCB</sub> = 3.6 V                                                                                                                         | 300                 |                        | 400                          | mV       |

|                             |                                        | $I_{OL}$ = 2 mA (external current; internal current<br>added); $V_{IA}$ = 0 V                                                                    |                     |                        |                              |          |

|                             |                                        | V <sub>CCB</sub> = 1.08 V to 1.2 V                                                                                                               | 65                  |                        | 175                          | mV       |

|                             |                                        |                                                                                                                                                  |                     | 0.1V <sub>CCB</sub>    | 235                          | mV       |

|                             |                                        | V <sub>CCB</sub> = 3.6 V                                                                                                                         | 300                 |                        | 400                          | mV       |

| V <sub>ILC</sub>            | contention                             | SCLB                                                                                                                                             |                     |                        |                              | <u> </u> |

| -                           | LOW-level                              | clock stretching; V <sub>CCB</sub> = 1.08 V to 1.2 V                                                                                             | -                   | -                      | 0.45V <sub>OL(SCLB)min</sub> | mV       |

|                             | input voltage                          | clock stretching; V <sub>CCB</sub> = 1.8 V                                                                                                       | -                   | -                      | 0.50V <sub>OL(SCLB)min</sub> | mV       |

|                             |                                        | clock stretching; V <sub>CCB</sub> = 3.6 V                                                                                                       | -                   | _                      | 0.60V <sub>OL(SCLB)min</sub> | mV       |

| Symbol              | Parameter                              | Conditions                                                                      | Ta                   | T <sub>amb</sub> = −40 °C to +85 °C |                      |    |  |

|---------------------|----------------------------------------|---------------------------------------------------------------------------------|----------------------|-------------------------------------|----------------------|----|--|

|                     |                                        |                                                                                 | Min                  | Typ <mark>[1]</mark>                | Мах                  |    |  |

| R <sub>pu</sub>     | pull-up<br>resistance                  | internal pull-up resistance<br>SCLA; SCLB; SDAA; SDAB                           |                      |                                     |                      |    |  |

|                     |                                        | V <sub>CCA</sub> or V <sub>CCB</sub> = 1.08 V                                   | 3.2                  | 4.4                                 | 6.0                  | kΩ |  |

|                     |                                        | V <sub>CCA</sub> or V <sub>CCB</sub> = 1.2 V                                    | 3.1                  | 4.3                                 | 5.9                  | kΩ |  |

|                     |                                        | V <sub>CCA</sub> or V <sub>CCB</sub> = 1.8 V                                    | 3.0                  | 4.25                                | 5.8                  | kΩ |  |

|                     |                                        | V <sub>CCA</sub> or V <sub>CCB</sub> = 3.6 V                                    | 2.9                  | 4.2                                 | 5.7                  | kΩ |  |

|                     |                                        | external pull-up resistance<br>SCLA; SCLB; SDAA; SDAB                           | 0.3                  | -                                   | -                    | kΩ |  |

| կ                   | input leakage                          | SCLA; SDAA                                                                      |                      |                                     |                      |    |  |

|                     | current                                | V <sub>I</sub> = V <sub>CCA</sub> ; EN = GND                                    | -                    | -                                   | 1                    | μA |  |

|                     |                                        | V <sub>I</sub> = 3.6 V; V <sub>CCA</sub> = 0 V                                  | -                    | -                                   | 1                    | μA |  |

|                     |                                        | SCLB; SDAB                                                                      |                      |                                     |                      |    |  |

|                     |                                        | V <sub>I</sub> = V <sub>CCB</sub> ; EN = GND                                    | -                    | -                                   | 1                    | μA |  |

|                     |                                        | V <sub>I</sub> = 3.6 V; V <sub>CCB</sub> = 0 V                                  | -                    | -                                   | 1                    | μA |  |

| C <sub>I/O</sub>    | input/output<br>capacitance            | SCLA; SDAA                                                                      |                      |                                     |                      |    |  |

|                     |                                        | V <sub>I</sub> = 3.6 V or 0 V; V <sub>CCA</sub> = 3.6 V; f = 1 MHz;<br>EN = GND | -                    | -                                   | 5                    | pF |  |

|                     |                                        | V <sub>I</sub> = 3.6 V or 0 V; V <sub>CCA</sub> = 0 V; f = 1 MHz                | -                    | -                                   | 7                    | pF |  |

|                     |                                        | SCLB; SDAB                                                                      |                      |                                     |                      |    |  |

|                     |                                        | V <sub>I</sub> = 3.6 V or 0 V; V <sub>CCB</sub> = 3.6 V; f = 1 MHz;<br>EN = GND | -                    | -                                   | 6                    | pF |  |

|                     |                                        | V <sub>I</sub> = 3.6 V or 0 V; V <sub>CCB</sub> = 0 V; f = 1 MHz                | -                    | -                                   | 8                    | pF |  |

| Enable              |                                        |                                                                                 |                      |                                     |                      |    |  |

| V <sub>T+(EN)</sub> | positive-going<br>threshold<br>voltage | EN pin                                                                          | 0.36V <sub>CCA</sub> | 0.55V <sub>CCA</sub>                | 0.68V <sub>CCA</sub> | V  |  |

| V <sub>T-(EN)</sub> | negative-going<br>threshold<br>voltage | EN pin                                                                          | 0.2V <sub>CCA</sub>  | 0.33V <sub>CCA</sub>                | 0.44V <sub>CCA</sub> | V  |  |

| R <sub>pu(EN)</sub> | pull-up<br>resistance                  | EN pin                                                                          | 1.67                 | 2.30                                | 4.20                 | MΩ |  |

| I                   | input leakage                          | V <sub>I</sub> = V <sub>CCA</sub>                                               | -                    | -                                   | 1                    | μA |  |

|                     | current                                | V <sub>I</sub> = 0 V; V <sub>CCA</sub> = 3.6 V                                  | -2                   | -                                   | -                    | μA |  |

| CI                  | input<br>capacitance                   | V <sub>I</sub> = 3.6 V; V <sub>CCA</sub> = 3.6 V; f = 1 MHz                     | -                    | -                                   | 5                    | pF |  |

[1] Typical values are measured at  $T_{amb}$  = 25 °C,  $V_{CCA}$  = 1.2 V and  $V_{CCB}$  = 1.2 V; unless otherwise specified.

# **12. Dynamic characteristics**

### Table 9. Dynamic characteristics

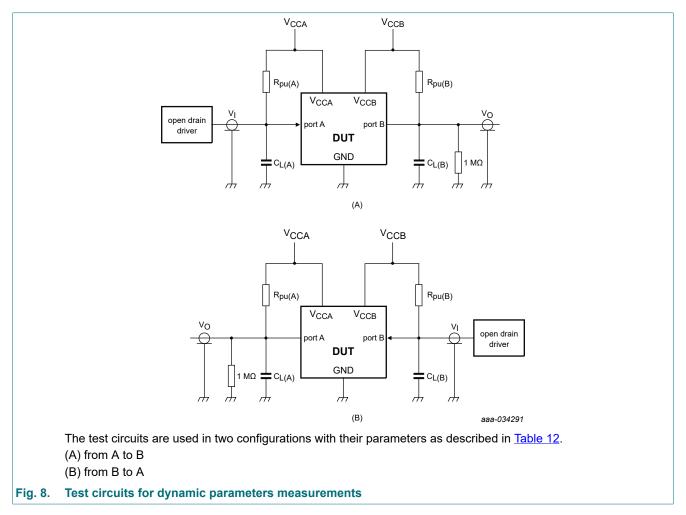

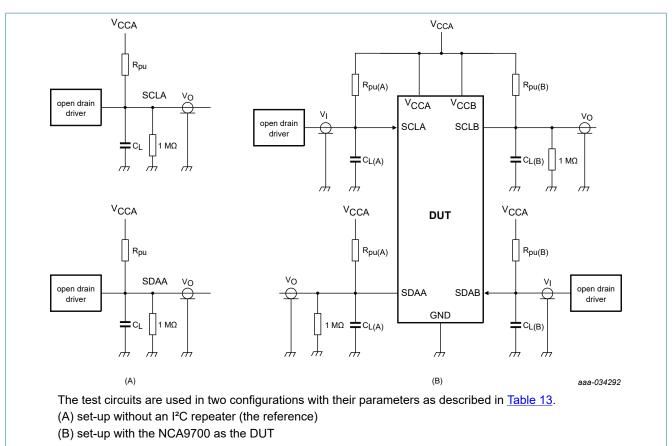

At recommended operating conditions; voltages are referenced to GND (ground = 0 V); For waveforms see Fig. 7; For test circuits see Fig. 8.

| Symbol                | Parameter                               | Conditions                                                                                     |         | T <sub>amb</sub> = -40 °C to +85 °C |     |      |                        |     |     |

|-----------------------|-----------------------------------------|------------------------------------------------------------------------------------------------|---------|-------------------------------------|-----|------|------------------------|-----|-----|

|                       |                                         |                                                                                                |         | Port A: 10<br>rt B: 160             |     |      | ort A: 85<br>t B: 85 p | -   |     |

|                       |                                         |                                                                                                | Min     | Min Typ[3]                          | Max | Min  | Typ[3]                 | Мах |     |

| f <sub>clk(max)</sub> | maximum clock<br>frequency              | SCLA; SCLB                                                                                     | 4] 1000 | ) _                                 | -   | 1000 | -                      | -   | kHz |

| t <sub>PLH</sub>      | LOW to HIGH<br>propagation<br>delay     | SCLA; SCLB;<br>V <sub>CCA</sub> = 1.08 V to 3.6 V;<br>V <sub>CCB</sub> = 1.08 V to 3.6 V       |         |                                     |     |      |                        |     |     |

|                       |                                         | port A to port B                                                                               | 10      | 53                                  | 124 | -6   | 37                     | 59  | ns  |

|                       |                                         | port B to port A                                                                               | -36     | -11                                 | 11  | -7   | 37                     | 60  | ns  |

|                       |                                         | SDAA; SDAB;<br>V <sub>CCA</sub> = 1.08 V to 3.6 V;<br>V <sub>CCB</sub> = 1.08 V to 3.6 V       |         |                                     |     |      |                        |     |     |

|                       |                                         | port A to port B                                                                               | 7       | 39                                  | 97  | -6   | 23                     | 38  | ns  |

|                       |                                         | port B to port A                                                                               | -30     | -11                                 | 9   | -5   | 26                     | 43  | ns  |

| t <sub>PHL</sub>      | HIGH to LOW<br>propagation<br>delay     | SCLA; SCLB;<br>V <sub>CCA</sub> = 1.08 V to 3.6 V;<br>V <sub>CCB</sub> = 1.08 V to 3.6 V       |         |                                     |     |      |                        |     |     |

|                       |                                         | port A to port B                                                                               | 20      | 55                                  | 117 | 18   | 67                     | 109 | ns  |

|                       |                                         | port B to port A                                                                               | 20      | 57                                  | 118 | 23   | 82                     | 128 | ns  |

|                       |                                         | SDAA; SDAB;<br>V <sub>CCA</sub> = 1.08 V to 3.6 V;<br>V <sub>CCB</sub> = 1.08 V to 3.6 V       |         |                                     |     |      |                        |     |     |

|                       |                                         | port A to port B                                                                               | 24      | 67                                  | 143 | 22   | 72                     | 130 | ns  |

|                       |                                         | port B to port A                                                                               | 20      | 57                                  | 123 | 23   | 88                     | 132 | ns  |

| t <sub>TLH(in)</sub>  | input LOW to<br>HIGH transition<br>time | SCLA, SCLB input;<br>V <sub>CCA</sub> = 1.08 V to 3.6 V;<br>V <sub>CCB</sub> = 1.08 V to 3.6 V |         |                                     |     |      |                        |     |     |

|                       |                                         | port A to port B                                                                               | 7       | 14                                  | 16  | 28   | 47                     | 71  | ns  |

|                       |                                         | port B to port A                                                                               | 48      | 78                                  | 110 | 28   | 49                     | 72  | ns  |

|                       |                                         | SDAA, SDAB input;<br>V <sub>CCA</sub> = 1.08 V to 3.6 V;<br>V <sub>CCB</sub> = 1.08 V to 3.6 V |         |                                     |     |      |                        |     |     |

|                       |                                         | port A to port B                                                                               | 7       | 14                                  | 16  | 28   | 47                     | 69  | ns  |

|                       |                                         | port B to port A                                                                               | 48      | 75                                  | 112 | 28   | 48                     | 74  | ns  |

16 / 26

| Symbol                | Parameter                                | Conditions                                                                                      |                                    | T <sub>amb</sub> = -40 °C to +85 °C |       |                                   |        |       |      |

|-----------------------|------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------|-------|-----------------------------------|--------|-------|------|

|                       |                                          |                                                                                                 | Port A: 10 pF<br>Port B: 160 pF[1] |                                     |       | Port A: 85 pF<br>Port B: 85 pF[2] |        |       |      |

|                       |                                          |                                                                                                 | Min                                | Typ[3]                              | Max   | Min                               | Typ[3] | Max   |      |

| t <sub>TLH(out)</sub> | output LOW to<br>HIGH transition<br>time | SCLA, SCLB output;<br>V <sub>CCA</sub> = 1.08 V to 3.6 V;<br>V <sub>CCB</sub> = 1.08 V to 3.6 V |                                    |                                     |       |                                   |        |       |      |

|                       |                                          | port A to port B                                                                                | 8                                  | 32                                  | 66    | 4                                 | 16     | 37    | ns   |

|                       |                                          | port B to port A                                                                                | 0                                  | 3                                   | 7     | 4                                 | 15     | 37    | ns   |

|                       |                                          | SDAA, SDAB output;<br>V <sub>CCA</sub> = 1.08 V to 3.6 V;<br>V <sub>CCB</sub> = 1.08 V to 3.6 V |                                    |                                     |       |                                   |        |       |      |

|                       |                                          | port A to port B                                                                                | 7                                  | 25                                  | 54    | 3                                 | 14     | 33    | ns   |