### 1 Product profile

#### 1.1 General description

The device is designed to protect high-speed interfaces such as SuperSpeed USB, High-Definition Multimedia Interface (HDMI), DisplayPort, external Serial Advanced Technology Attachment (eSATA) and Low Voltage Differential Signaling (LVDS) interfaces against ElectroStatic Discharge (ESD).

The device includes four high-level ESD protection diode structures for ultra high-speed signal lines and is encapsulated in a leadless small DFN2510A-10 (SOT1176-1) plastic package.

All signal lines are protected by a special diode configuration offering ultra low line capacitance of only 0.5 pF. These diodes utilize a unique snap-back structure in order to provide protection to downstream components from ESD voltages up to  $\pm 10$  kV contact exceeding IEC 61000-4-2, level 4.

#### 1.2 Features and benefits

- System ESD protection for USB 2.0 and SuperSpeed USB 3.1, HDMI 2.0, DisplayPort, eSATA and LVDS

- All signal lines with integrated rail-to-rail clamping diodes for downstream ESD protection of ±10 kV exceeding IEC 61000-4-2, level 4

- Matched 0.5 mm trace spacing

- Signal lines with ≤ 0.05 pF matching capacitance between signal pairs

- Line capacitance of only 0.5 pF for each channel

- · Design-friendly 'pass-through' signal routing

### 1.3 Applications

The device is designed for high-speed receiver and transmitter port protection:

- TVs and monitors

- DVD recorders and players

- · Notebooks, main board graphic cards and ports

- · Set-top boxes and game consoles

## 2 Pinning information

#### Table 1. Pinning

| Pin | Symbol | Description              | Simplified outline   | Graphic symbol    |

|-----|--------|--------------------------|----------------------|-------------------|

| 1   | CH1    | channel 1 ESD protection |                      |                   |

| 2   | CH2    | channel 2 ESD protection | 10 9 8 7 6           | 1 2 4 5           |

| 3   | GND    | ground                   |                      |                   |

| 4   | CH3    | channel 3 ESD protection | 1 2 3 4 5            |                   |

| 5   | CH4    | channel 4 ESD protection | Transparent top view |                   |

| 6   | n.c.   | not connected            |                      |                   |

| 7   | n.c.   | not connected            |                      | 3, 8<br>018aaa001 |

| 8   | GND    | ground                   |                      |                   |

| 9   | n.c.   | not connected            |                      |                   |

| 10  | n.c.   | not connected            |                      |                   |

# 3 Ordering information

#### **Table 2. Ordering information**

| Type number | Package |                                                                                                          |           |  |  |  |

|-------------|---------|----------------------------------------------------------------------------------------------------------|-----------|--|--|--|

|             | Name    | Description                                                                                              | Version   |  |  |  |

| PUSB3FA0    |         | plastic extremely thin small outline package; no leads;10 terminals; body 1 $\times$ 2.5 $\times$ 0.5 mm | SOT1176-1 |  |  |  |

## 4 Marking

Table 3. Marking codes

| Type number | Marking code |

|-------------|--------------|

| PUSB3FA0    | 96           |

## 5 Limiting values

#### Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter                       | Conditions             |     | Min  | Max  | Unit |

|------------------|---------------------------------|------------------------|-----|------|------|------|

| VI               | input voltage                   |                        |     | -0.5 | +1.5 | V    |

| $V_{ESD}$        | electrostatic discharge voltage | IEC 61000-4-2, level 4 | [1] |      |      |      |

|                  |                                 | contact discharge      |     | -10  | +10  | kV   |

|                  |                                 | air discharge          |     | -15  | +15  | kV   |

| T <sub>amb</sub> | ambient temperature             |                        |     | -40  | +85  | °C   |

| T <sub>stg</sub> | storage temperature             |                        |     | -55  | +125 | °C   |

[1] All pins to ground.

PUSB3FA0

All information provided in this document is subject to legal disclaimers.

© Nexperia B.V. 2018. All rights reserved.

### **Characteristics**

#### **Table 5. Characteristics**

$T_{amb}$  = 25 °C unless otherwise specified.

| Symbol            | Parameter                   | Conditions                             |     | Min | Тур  | Max | Unit |

|-------------------|-----------------------------|----------------------------------------|-----|-----|------|-----|------|

| $V_{BR}$          | breakdown voltage           | I <sub>I</sub> = 1 mA                  |     | 6   | -    | -   | V    |

| I <sub>LR</sub>   | reverse leakage current     | per channel; V <sub>I</sub> = 1.5 V    |     | -   | -    | 1   | μA   |

| V <sub>F</sub>    | forward voltage             | I <sub>I</sub> = 1 mA                  |     | -   | 0.7  | -   | V    |

| C <sub>line</sub> | line capacitance            | f = 1 MHz; V <sub>I</sub> = 1.5 V      | [1] |     | 0.5  | 0.6 | pF   |

| $\Delta C_{line}$ | line capacitance difference | f = 1 MHz; V <sub>I</sub> = 1.5 V      | [1] | -   | 0.05 | -   | pF   |

| r <sub>dyn</sub>  | dynamic resistance          | surge                                  | [2] |     |      |     |      |

|                   |                             | <ul> <li>positive transient</li> </ul> |     | -   | 0.41 | -   | Ω    |

|                   |                             | negative transient                     |     | -   | 0.26 | -   | Ω    |

|                   |                             | TLP                                    | [3] |     |      |     |      |

|                   |                             | positive transient                     |     | -   | 0.43 | -   | Ω    |

|                   |                             | negative transient                     |     | -   | 0.28 | -   | Ω    |

| V <sub>CL</sub>   | clamping voltage            | I <sub>PP</sub> = 5.2 A                | [2] |     |      |     |      |

|                   |                             | <ul> <li>positive transient</li> </ul> |     | -   | 4.6  | -   | V    |

|                   |                             | I <sub>PP</sub> = -4.4 A               | [2] |     |      |     |      |

|                   |                             | <ul> <li>negative transient</li> </ul> |     | -   | -2.2 | -   | V    |

This parameter is guaranteed by design.

According to IEC 61000-4-5 (8/20  $\mu$ s current waveform). 100 ns Transmission Line Pulse (TLP); 50  $\Omega$ ; pulser at 80 ns.

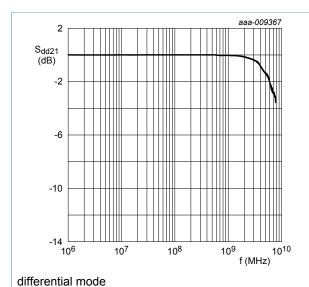

Figure 1. Insertion loss; typical values

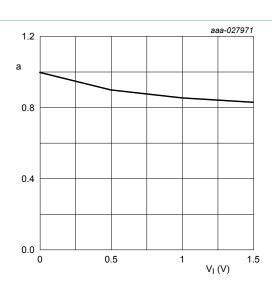

$$a = \frac{C_{\text{line}}}{C_{\text{line}(V_I = 0 \text{ V})}}$$

Figure 2. Relative capacitance as a function of input voltage; typical values

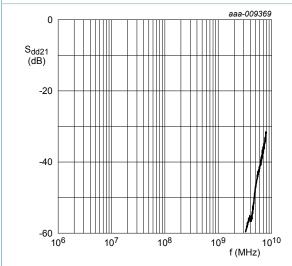

Sdd21 normalized to 100  $\Omega;\!differential$  pairs CH1/CH2 versus CH3/CH4

Figure 3. Crosstalk; typical values

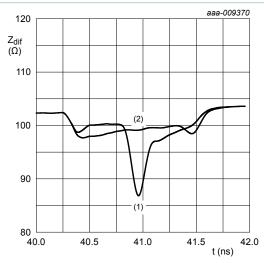

$t_r$  = 200 ps; differential pair CH1 + CH2

(1) PUSB3FA0 on reference board

(2) Reference board without device under test (DUT)

Figure 4. Differential Time Domain Reflectometer (TDR) plot; typical values

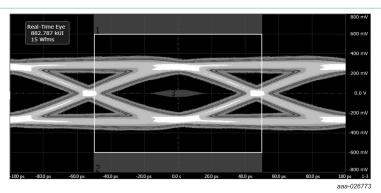

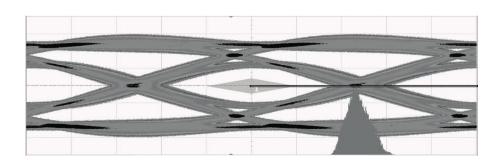

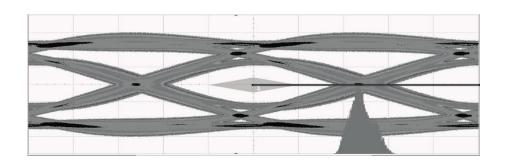

Data rate: 10 Gbit/s; Vertical scale: 200 mV/div; Horizontal scale: 20 ps/div

3.1 dB de-emphasis 2.2 dB pre-shoot

Figure 5. USB 3.1 eye diagram, Printed-Circuit Board (PCB) with PUSB3FA0

aaa-02

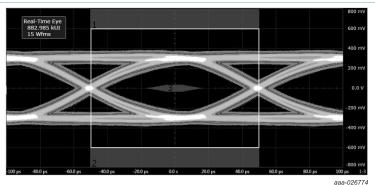

Data rate: 10 Gbit/s; Vertical scale: 200 mV/div; Horizontal scale: 20 ps/div

3.1 dB de-emphasis 2.2 dB pre-shoot

Figure 6. USB 3.1 eye diagram, PCB without PUSB3FA0 (reference)

aaa-014159

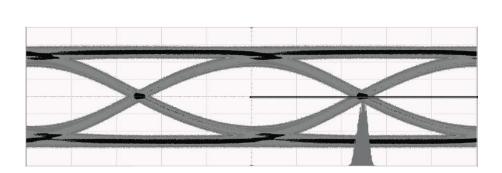

Test frequency: 148.5 MHz Differential swing voltage: 810 mV Horizontal scale: 34 ps/div

Figure 7. HDMI 2.0 TP1 eye diagram, PCB with PUSB3FA0 (2160p, 60 Hz

aaa-014160

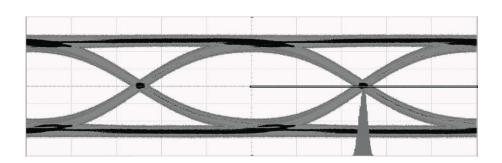

Test frequency: 148.5 MHz Differential swing voltage: 800 mV Horizontal scale: 34 ps/div

Figure 8. HDMI 2.0 TP1 eye diagram, PCB without PUSB3FA0 (2160p, 60 Hz, reference)

aaa-014161

Test frequency: 148.5 MHz Differential swing voltage: 809 mV Horizontal scale: 34 ps/div

Remark: Measured at Test Point 2 (TP2) worst cable emulator, reference cable equalizer and worst case positive skew.

Figure 9. HDMI 2.0 TP2 eye diagram, PCB with PUSB3FA0 (2160p, 60 Hz)

aaa-014162

Test frequency: 148.5 MHz Differential swing voltage: 820 mV Horizontal scale: 34 ps/div

Remark: Measured at Test Point 2 (TP2) worst cable emulator, reference cable equalizer and worst case positive skew.

Figure 10. HDMI 2.0 TP2 eye diagram, PCB without PUSB3FA0 (2160p, 60 Hz, reference)

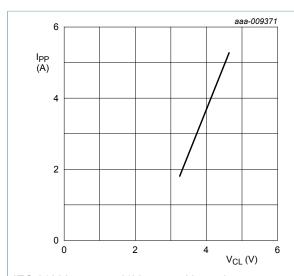

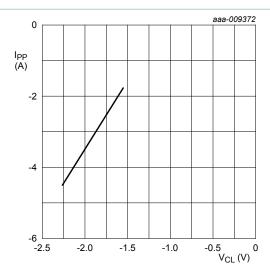

IEC 61000-4-5;  $t_p$  = 8/20  $\mu$ s; positive pulse

Figure 11. Dynamic resistance with positive clamping; typical values

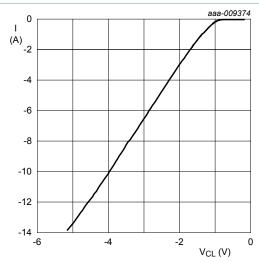

$t_p$  = 100 ns; Transmission Line Pulse (TLP)

Figure 13. Dynamic resistance with positive clamping; typical values

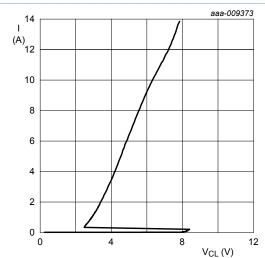

IEC 61000-4-5;  $t_p$  = 8/20 µs; negative pulse

Figure 12. Dynamic resistance with negative clamping; typical values

t<sub>p</sub> = 100 ns; Transmission Line Pulse (TLP)

Figure 14. Dynamic resistance with negative clamping; typical values

The device uses an advanced clamping structure showing a negative dynamic resistance. This snap-back behavior strongly reduces the clamping voltage to the system behind the ESD protection during an ESD event. Do not connect unlimited DC current sources to the data lines to avoid keeping the ESD protection device in snap-back state after exceeding breakdown voltage (due to an ESD pulse for instance).

## 7 Application information

The device is designed to provide high-level ESD protection for high-speed serial data buses such as HDMI, DisplayPort, eSATA and LVDS data lines.

When designing the Printed-Circuit Board (PCB), give careful consideration to impedance matching and signal coupling. Do not connect the signal lines to unlimited current sources like, for example, a battery.

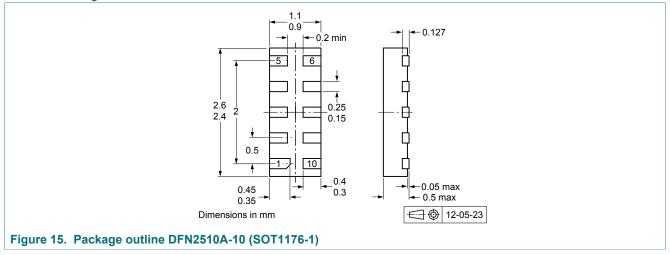

## 8 Package outline

Table 6. Package outline

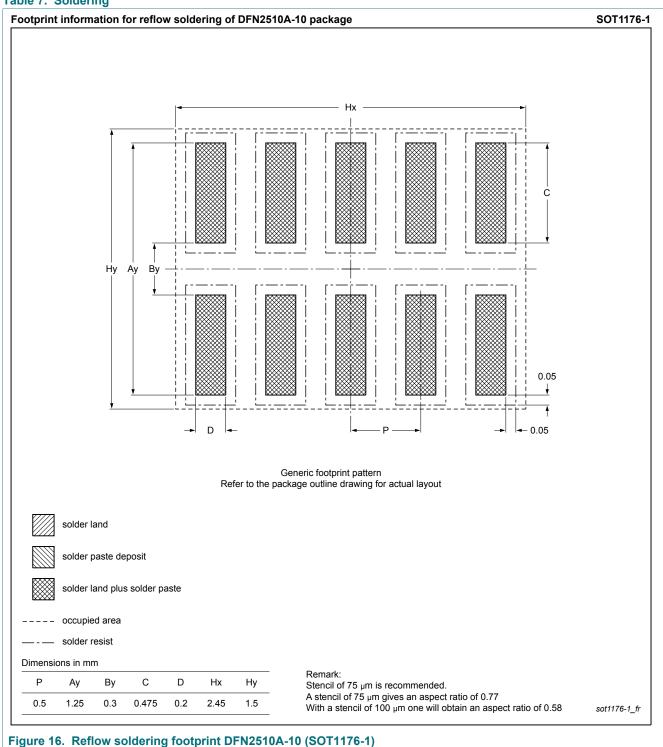

## **Soldering**

Table 7. Soldering

All information provided in this document is subject to legal disclaimers.

© Nexperia B.V. 2018. All rights reserved.

# 10 Revision history

#### Table 8. Revision history

| Document ID  | Release date | Data sheet status  | Change notice | Supersedes |

|--------------|--------------|--------------------|---------------|------------|

| PUSB3FA0 v.1 | 20180201     | Product data sheet | -             | -          |

# **PUSB3FA0**

## ESD protection for ultra high-speed interfaces

### **Contents**

| 1   | Product profile         | 1 |

|-----|-------------------------|---|

| 1.1 | General description     |   |

| 1.2 | Features and benefits   |   |

| 1.3 | Applications            |   |

| 2   | Pinning information     | 2 |

| 3   | Ordering information    |   |

| 4   | Marking                 |   |

| 5   | Limiting values         |   |

| 6   | Characteristics         | 3 |

| 7   | Application information |   |

| 8   | Package outline         |   |

| 9   | Soldering               |   |

| 10  | Revision history        |   |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© Nexperia B.V. 2018.

All rights reserved.

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com 单击下面可查看定价,库存,交付和生命周期等信息

>>Nexperia(安世)