## 16-bit I2C-bus I/O port with interrupt

Datasheet (EN) 1.3

#### **Product Overview**

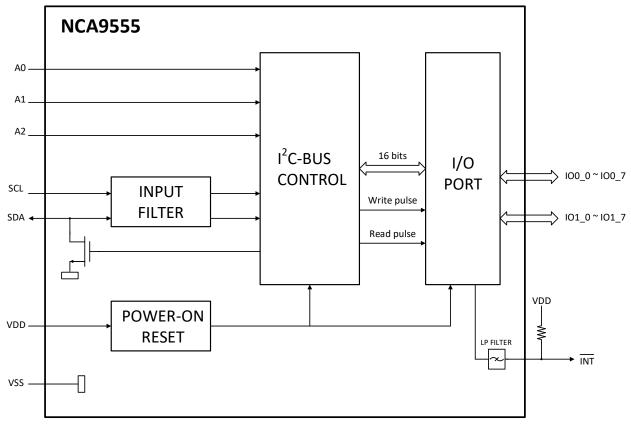

The NCA9555 is a 24-pin CMOS device that provides 16 bits of general-purpose parallel Input/Output (GPIO) expansion for I2C-bus applications. It provides a simple solution when additional I/O is needed for ACPI power switches, sensors, push buttons, LEDs, fans, etc.

The NCA9555 consists of two 8-bit Configuration (Input or Output selection); Input, Output and Polarity Inversion (active HIGH or active LOW operation) registers. The system master can enable the I/Os as either inputs or outputs by writing to the I/O configuration bits. The data for each Input or Output is kept in the corresponding Input or Output register. The polarity of the read register can be inverted with the Polarity Inversion register. All registers can be read by the system master.

The NCA9555 open-drain interrupt output is activated when any input state differs from its corresponding input port register state and is used to indicate to the system master that an input state has changed. The power-on reset sets the registers to their default values and initializes the device state machine.

Three hardware pins (A0, A1, A2) vary the fixed I2C-bus address and allow up to eight devices to share the same I2C-bus.

## **Key Features**

- Operating power supply voltage range of 2.3 V to 5.5 V

- 5 V tolerant I/Os

- I2C to Parallel Port Expander

- Polarity Inversion register

- Active LOW interrupt output

- Compatible With Most Microcontrollers

- Address by Three Hardware Address Pins for Use of up to Eight Devices

- Latched Outputs With High-Current Drive Capability for Directly Driving LEDs

- Low standby current

- Noise filter on SCL/SDA inputs

- No glitch on power-up

- Internal power-on reset

- 16 I/O pins which default to 16 inputs

- 0 Hz to 400 kHz clock frequency

- ESD protection exceeds 2000 V HBM, 200 V MM, and 1000 V CDM

- Latch-up testing exceeds 100 mA

### **Applications**

- GPIO expansion for I2C-bus applications

- Servers

- Routers (Telecom Switching Equipment)

- Personal Computers

- Personal Electronics

- Products with GPIO-Limited Processors

#### **Device Information**

| Part Number | Package | Body Size     |  |  |

|-------------|---------|---------------|--|--|

| NCA9555     | TSSOP24 | 7.80mm*4.40mm |  |  |

## **Functional Block Diagrams**

Figure 1. NCA9555 Block Diagram

## **NCA9555**

## **INDEX**

| 1. PIN CONFIGURATION AND FUNCTIONS                                                                                                                                                                                                                                              | 3  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2. ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                     | 5  |

| 3. RECOMMENDED OPERATING CONDITIONS                                                                                                                                                                                                                                             | 6  |

| 4. THERMAL INFORMATION                                                                                                                                                                                                                                                          | 6  |

| 5. SPECIFICATIONS                                                                                                                                                                                                                                                               | 7  |

| 5.1. ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                 |    |

| 6. REGISTER DESCRIPTION                                                                                                                                                                                                                                                         |    |

| 6.1. DEVICE ADDRESS. 6.2. COMMAND BYTE. 6.3. REGISTERS 0 AND 1: INPUT PORT REGISTERS. 6.4. REGISTERS 2 AND 3: OUTPUT PORT REGISTERS. 6.5. REGISTERS 4 AND 5: POLARITY INVERSION REGISTERS. 6.6. REGISTERS 6 AND 7: CONFIGURATION REGISTERS. 6.7. POWER-ON RESET. 6.8. I/O PORT. |    |

| 7. BUS TRANSACTIONS                                                                                                                                                                                                                                                             | 15 |

| 7.1. WRITING TO THE PORT REGISTERS  7.2. READING THE PORT REGISTERS  7.3. INTERRUPT OUTPUT                                                                                                                                                                                      | 16 |

| 8. CHARACTERISTICS OF THE I <sup>2C</sup> -BUS                                                                                                                                                                                                                                  | 17 |

| 8.1. BIT TRANSFER  8.2. START AND STOP CONDITIONS  8.3. SYSTEM CONFIGURATION  8.4. ACKNOWLEDGE                                                                                                                                                                                  |    |

| 9. APPLICATION DESIGN-IN INFORMATION                                                                                                                                                                                                                                            | 19 |

| 10. TEST INFORMATION                                                                                                                                                                                                                                                            | 21 |

| 11. PACKAGE INFORMATION                                                                                                                                                                                                                                                         | 22 |

| 11.1. PACKAGE OUTLINE                                                                                                                                                                                                                                                           | 23 |

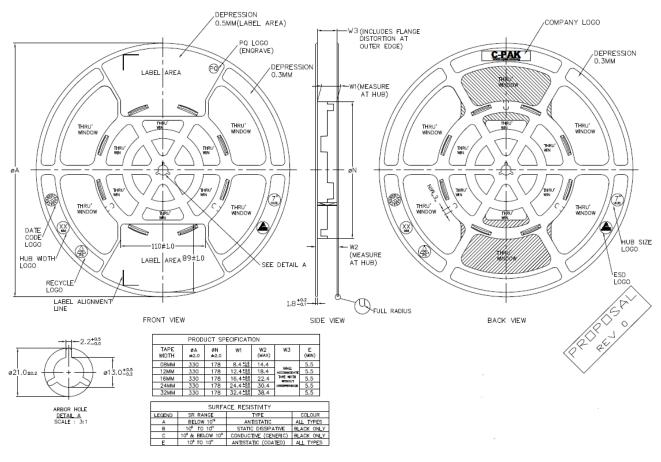

| 12. TAPE AND REEL INFORMATION                                                                                                                                                                                                                                                   | 23 |

| 13. ORDER INFORMATION                                                                                                                                                                                                                                                           | 24 |

| 14. DOCUMENTATION SUPPORT                                                                                                                                                                                                                                                       | 25 |

| 15 DEVISION HISTORY                                                                                                                                                                                                                                                             | 26 |

# 1. Pin Configuration and Functions

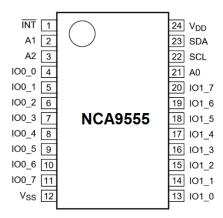

Figure 1.1. NCA9555 Package

Table 1.1. Pin Description

| Symbol | Pin | Description                   |

|--------|-----|-------------------------------|

| /INT   | 1   | interrupt output (open-drain) |

| A1     | 2   | address input 1               |

| A2     | 3   | address input 2               |

| 100_0  | 4   | port 0 input/output           |

| 100_1  | 5   |                               |

| 100_2  | 6   |                               |

| 100_3  | 7   |                               |

| 100_4  | 8   |                               |

| 100_5  | 9   |                               |

| 100_6  | 10  |                               |

| 100_7  | 11  |                               |

| VSS    | 12  | supply ground                 |

| 101_0  | 13  | port 1 input/output           |

| 101_1  | 14  |                               |

| IO1_2  | 15  |                               |

| IO1_3  | 16  |                               |

| IO1_4  | 17  |                               |

| IO1_5  | 18  |                               |

| IO1_6  | 19  |                               |

| IO1_7  | 20  |                               |

| A0     | 21  | address input 0               |

| SCL    | 22  | serial clock line             |

| SDA    | 23  | serial data line              |

| VDD    | 24  | supply voltage                |

# 2. Absolute Maximum Ratings

| Parameters                     | Symbol              | Min     | Мах  | Unit         | Conditions    |

|--------------------------------|---------------------|---------|------|--------------|---------------|

| Supply voltage                 | V <sub>DD</sub>     | -0.5    | +6.0 | V            |               |

| Voltage on an input/output pin | V <sub>I/O</sub>    | VSS-0.5 | 6.0  | V            |               |

| Output current                 | Io                  | -       | ±50  | mA           | On an I/O pin |

| Input current                  | I <sub>I</sub>      | -       | ±20  | mA           |               |

| Supply current                 | I <sub>DD</sub>     | -       | 160  | mA           |               |

| Ground supply current          | I <sub>SS</sub>     | -       | 200  | mA           |               |

| Total power dissipation        | P <sub>tot</sub>    | -       | 200  | mW           |               |

| Maximum junction temperature   | T <sub>j(max)</sub> | -       | 125  | $^{\circ}$   |               |

| Storage temperature            | T <sub>stg</sub>    | -65     | +150 | $^{\circ}$ C |               |

| Ambient temperature            | T <sub>amb</sub>    | -40     | +85  | $^{\circ}$ C | Operating     |

# 3. Recommended Operating Conditions

| Parameters                                | Symbol          | Min     | Max | Unit    | Conditions |

|-------------------------------------------|-----------------|---------|-----|---------|------------|

| Supply voltage                            | $V_{CCA}$       | 2.3     |     | 5.5     | V          |

| High-level input voltage                  | V <sub>IH</sub> | 0.7*VCC |     | 5.5     | V          |

| Low-level input voltage                   | V <sub>IL</sub> | -0.5    |     | 0.3*VCC | V          |

| High-level output current                 | I <sub>OH</sub> |         |     | -10     | mA         |

| Low-level output current(P00-P07,P10-P17) | I <sub>OL</sub> |         |     | 10      | mA         |

| Low-level output current(/INT,SDA)        | I <sub>OL</sub> |         |     | 3.5     | mA         |

| Operating free-air temperature            | T <sub>A</sub>  | -40     |     | 85      | $^{\circ}$ |

## 4. Thermal Information

| Parameters                               | Symbol              | SOW-16 | Unit |

|------------------------------------------|---------------------|--------|------|

| Junction-to-ambient thermal resistance   | $\theta_{JA}$       | 108.8  |      |

| Junction-to-case(top) thermal resistance | $\theta_{JC}$ (top) | 54     | °C/W |

| Junction-to-board thermal resistance     | $\theta_{JB}$       | 62.8   |      |

## 5. SPECIFICATIONS

### 5.1. Electrical characteristics

$V_{CC}$  = 2.3V to 5.5V; $T_{amb}$  = -40  $^{\circ}\mathrm{C}$  to +85  $^{\circ}\mathrm{C}$ ; unless otherwise noted.

| Parameters               | Symbol           | Min                 | Тур      | Max                 | Unit | Conditions                                                                                    |

|--------------------------|------------------|---------------------|----------|---------------------|------|-----------------------------------------------------------------------------------------------|

| Supplies                 |                  |                     |          |                     |      |                                                                                               |

| Supply voltage<br>Range  | $V_{DD}$         | 2.3                 | -        | 5.5                 | V    |                                                                                               |

| Power On Reset           | V <sub>POR</sub> | -                   | 0.94     | 1.5                 | V    | no load; VI = VDD or VSS                                                                      |

| Supply current           | I <sub>DD</sub>  | -                   | 5.74     | 90                  | μΑ   | Operating mode; V <sub>DD</sub> = 5.5 V; no load; f <sub>SCL</sub> = 100 kHz                  |

| Standby current          | I <sub>stb</sub> | -                   | 0.9      | 1.5                 | mA   | Standby mode; $V_{DD}$ = 5.5 V; no load; $V_{I}$ = $V_{SS}$ ; $f_{SCL}$ = 0 kHz; I/O = inputs |

|                          |                  | -                   | 0.25     | 1                   | μА   | Standby mode; VDD = 5.5 V; no load; $V_1 = V_{DD}$ ; $f_{SCL} = 0$ kHz; I/O = inputs          |

| Input SCL; Input a       | nd Output SL     | DA .                |          |                     |      |                                                                                               |

| LOW-level input voltage  | V <sub>IL</sub>  | -0.5                | -        | 0.3*V <sub>DD</sub> | V    |                                                                                               |

| HIGH-level input voltage | V <sub>IH</sub>  | 0.7*V <sub>DD</sub> | -        | 5.5                 | V    |                                                                                               |

| LOW-level output current | I <sub>OL</sub>  | 3                   | -        | -                   | mA   | V <sub>DD</sub> = 2.3 V to 5.5 V; V <sub>OL</sub> = 0.4 V                                     |

| Input leakage current    | IL               | -1                  | -        | +1                  | μА   | $V_{DD}$ = 2.3 V to 5.5 V; $V_{I}$ = $V_{DD}$ or $V_{SS}$                                     |

| Input capacitance        | C <sub>i</sub>   | -                   | 6        | 10                  | pF   | $V_1 = V_{SS}$                                                                                |

| I/Os                     |                  |                     |          |                     |      |                                                                                               |

| LOW-level input voltage  | V <sub>IL</sub>  | -0.5                | -        | 0.3*V <sub>DD</sub> | V    |                                                                                               |

| HIGH-level input voltage | V <sub>IH</sub>  | 0.7*V <sub>DD</sub> | -        | 5.5                 | V    |                                                                                               |

| LOW-level                | I <sub>OL</sub>  | 8                   | 13 to 23 | -                   | mA   | VDD = 2.3 V to 5.5 V; VOL = 0.5 V <sup>[2]</sup>                                              |

| output current           |                  | 10                  | 16 to 32 | -                   | mA   | VDD = 2.3 V to 5.5 V; VOL = 0.7 V <sup>[2]</sup>                                              |

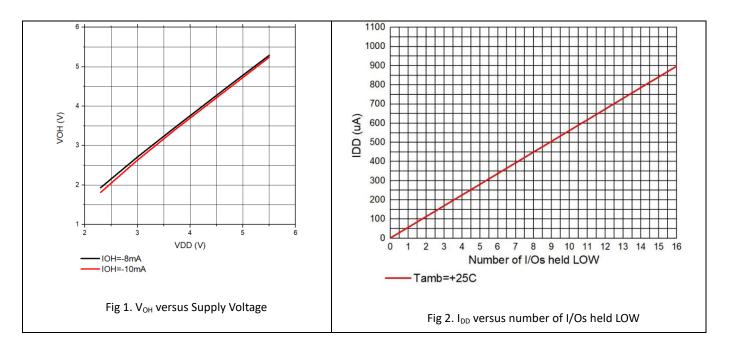

|                          | V <sub>OH</sub>  | 1.8                 | -        | -                   | V    | IOH = -8 mA; VDD = 2.3 V <sup>[3]</sup>                                                       |

|                                     |                  |                     |     |                     | •  | T                                        |

|-------------------------------------|------------------|---------------------|-----|---------------------|----|------------------------------------------|

| HIGH-level                          |                  | 1.7                 | -   | -                   | V  | IOH = -10 mA; VDD = 2.3 V <sup>[3]</sup> |

| output voltage                      |                  | 2.6                 | -   | -                   | V  | IOH = -8 mA; VDD = 3.0 V <sup>[3]</sup>  |

|                                     |                  | 2.5                 | -   | -                   | V  | IOH = -10 mA; VDD = 3.0 V <sup>[3]</sup> |

|                                     |                  | 4.3                 | -   | -                   | ٧  | IOH = -8 mA; VDD = 4.75V <sup>[3]</sup>  |

|                                     |                  | 4.0                 | -   | -                   | V  | IOH = -10 mA; VDD = 4.75V <sup>[3]</sup> |

| HIGH-level input<br>leakage current | Ішн              | -                   | -   | 1                   | μА | VDD = 5.5 V; VI = VDD                    |

| LOW-level input<br>leakage current  | I <sub>LIL</sub> | -                   | -   | -100                | μΑ | VDD = 5.5 V; VI = VSS                    |

| Input capacitance                   | Ci               | -                   | 3.7 | 5                   | pF |                                          |

| Output capacitance                  | Со               | -                   | 3.7 | 5                   | pF |                                          |

| Interrupt INT                       |                  |                     |     |                     |    |                                          |

| LOW-level output current            | I <sub>OL</sub>  | 3                   | -   | -                   | mA | VDD = 2.3 V to 5.5 V; VOL=0.4V           |

| Select Inputs A0, A                 | A1, A2           |                     |     |                     |    |                                          |

| LOW-level input voltage             | V <sub>IL</sub>  | ?-0.5               | -   | 0.3*V <sub>DD</sub> | v  |                                          |

| HIGH-level input voltage            | V <sub>IH</sub>  | 0.7*V <sub>DD</sub> | -   | 5.5                 | V  |                                          |

| Input leakage current               | I <sub>LI</sub>  | ?-1                 | -   | +1                  | μА | VDD = 2.3 V to 5.5 V; VI = VDD or VSS    |

$<sup>1.\</sup>text{VDD}$  must be lowered to 0.2V for at least  $50\mu\text{s}$  in order to reset part.

<sup>2.</sup>Each I/O must be externally limited to a maximum of 25 mA and each octal (IOO\_0 to IOO\_7 and IO1\_0 to IO1\_7) must be limited to a maximum current of 100 mA for a device total of 200 mA.

<sup>3.</sup>The total current sourced by all I/Os must be limited to 160 mA.

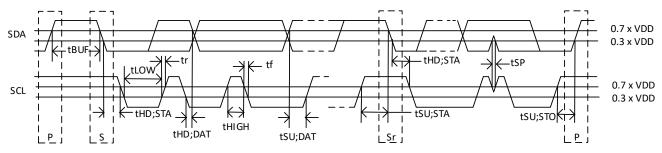

### 5.2. Dynamic Characteristics

| Parameters                                       | Symbol                             | Standard-mode I2C-bus |      | Fast-mode I2C-bus                     |     | Unit |

|--------------------------------------------------|------------------------------------|-----------------------|------|---------------------------------------|-----|------|

|                                                  |                                    | Min                   | Max  | Min                                   | Max |      |

| SCL clock frequency                              | f <sub>SCL</sub>                   | 0                     | 100  | 0                                     | 400 | kHz  |

| bus free time between a STOP and START condition | t <sub>BUF</sub>                   | 4.7                   | -    | 1.3                                   | -   | μs   |

| hold time (repeated) START condition             | t <sub>HD;STA</sub>                | 4.0                   | -    | 0.6                                   | -   | μs   |

| set-up time for a repeated START condition       | t <sub>SU;STA</sub>                | 4.7                   | -    | 0.6                                   | -   | μs   |

| set-up time for STOP condition                   | t <sub>su;sto</sub>                | 4.0                   | -    | 0.6                                   | -   | μs   |

| data valid acknowledge time                      | t <sub>VD;ACK</sub> <sup>[1]</sup> | 0.3                   | 3.45 | 0.1                                   | 0.9 | μs   |

| data hold time                                   | t <sub>HD;DAT</sub>                | 0                     | -    | 0                                     | -   | ns   |

| data valid time                                  | t <sub>VD;DAT</sub> <sup>[2]</sup> | 300                   | -    | 50                                    | -   | ns   |

| data set-up time                                 | t <sub>SU;DAT</sub>                | 250                   | -    | 100                                   | -   | ns   |

| LOW period of the SCL clock                      | t <sub>LOW</sub>                   | 4.7                   | -    | 1.3                                   | -   | μs   |

| HIGH period of the SCL clock                     | t <sub>HIGH</sub>                  | 4.0                   | -    | 0.6                                   | -   | μs   |

| fall time of both SDA and SCL signals            | t <sub>f</sub>                     | -                     | 300  | 20 + 0.1C <sub>b</sub> <sup>[3]</sup> | 300 | ns   |

| rise time of both SDA and SCL signals            | tr                                 | -                     | 1000 | 20 + 0.1C <sub>b</sub> <sup>[3]</sup> | 300 | ns   |

| pulse width of spikes that must be suppressed by the input filter | t <sub>SP</sub>             | -   | 50  | -   | 50  | ns |

|-------------------------------------------------------------------|-----------------------------|-----|-----|-----|-----|----|

| data output valid time                                            | t <sub>v(Q)</sub>           | -   | 200 | -   | 200 | ns |

| data input set-up time                                            | t <sub>su(D)</sub>          | 150 | -   | 150 | -   | ns |

| data input hold time                                              | t <sub>h(D)</sub>           | 1   | -   | 1   | -   | μs |

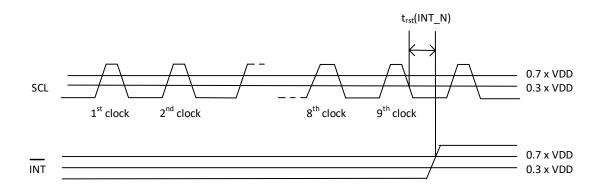

| valid time on pin /INT                                            | t <sub>v(INT_N)</sub> [4]   | -   | 4   | -   | 4   | μs |

| reset time on pin /INT                                            | t <sub>rst(INT_N)</sub> [5] | -   | 4   | -   | 4   | μs |

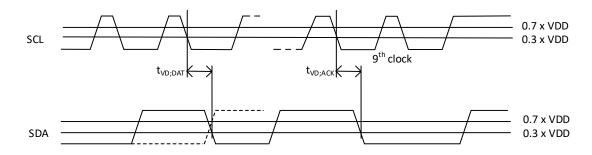

<sup>1.</sup>t  $_{

m VD:ACK}$  = time for acknowledgement signal from SCL LOW to SDA (out) LOW, see Figure 22.

$<sup>5.</sup>t_{\rm rst(INT\_N)}$  is measured from 0.3VDD on SCL to 0.7VDD on /INT.

Fig 3. Definition of timing on I<sup>2</sup>C-bus

## 6. Register Description

The register map of the NCA9555 includes input port registers, output port registers, polarity inversion port registers and configuration registers.

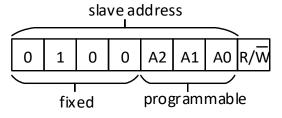

#### 6.1. Device address

Fig 4. NCA9555 device address

#### 6.2. command byte

The command byte is the first byte to follow the address byte during a write transmission. It is used as a pointer to determine which

<sup>2.</sup>t VD:DAT = minimum time for SDA data out to be valid following SCL LOW, see Figure 22.

<sup>3.</sup>C = total capacitance of one bus line in pF.

$<sup>4.</sup>t_{V(INT\_N)}$  is measured from 50% IO input to 0.3VDD on /INT

of the following registers will be written or read.

Table 4. Command byte

| Command | Register                  |

|---------|---------------------------|

| 0       | Input port 0              |

| 1       | Input port 1              |

| 2       | Output port 0             |

| 3       | Output port 1             |

| 4       | Polarity Inversion port 0 |

| 5       | Polarity Inversion port 1 |

| 6       | Configuration port 0      |

| 7       | Configuration port 1      |

#### 6.3. registers 0 and 1: input port registers

This register is an input-only port. It reflects the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by Register 3. Writes to this register have no effect.

The default value 'X' is determined by the externally applied logic level.

Table 5. Input Port 0 Register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | 10.7 | 10.6 | 10.5 | 10.4 | 10.3 | 10.2 | 10.1 | 10.0 |

| Default | х    | х    | Х    | Х    | Х    | Х    | Х    | Х    |

Table 6. Input Port 1 Register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | 11.7 | I1.6 | I1.5 | I1.4 | 11.3 | I1.2 | 11.1 | I1.0 |

| Default | х    | Х    | Х    | Х    | Х    | х    | Х    | х    |

#### 6.4. registers 2 and 3: output port registers

This register is an output-only port. It reflects the outgoing logic levels of the pins defined as outputs by Registers 6 and 7. Bit values in this register have no effect on pins defined as inputs. In turn, reads from this register reflect the value that is in the flip-flop controlling the output selection, not the actual pin value.

Table 7. Output Port 0 Register

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|---|

|     |   |   |   |   |   |   |   |   |

| Symbol  | 00.7 | O0.6 | O0.5 | O0.4 | O0.3 | O0.2 | O0.1 | 00.0 |

|---------|------|------|------|------|------|------|------|------|

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

Table 8. Output Port 1 Register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | 01.7 | O1.6 | O1.5 | 01.4 | 01.3 | 01.2 | 01.1 | 01.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### 6.5. registers 4 and 5 : polarity inversion registers

This register allows the user to invert the polarity of the Input port register data. If a bit in this register is set (written with '1'), the Input port data polarity is inverted. If a bit in this register is cleared (written with a '0'), the Input port data polarity is retained.

**Table 9. Polarity Inversion Port 0 Register**

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | N0.7 | N0.6 | N0.5 | N0.4 | N0.3 | N0.2 | N0.1 | N0.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

Table 10. Polarity Inversion Port 1 Register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | N1.7 | N1.6 | N1.5 | N1.4 | N1.3 | N1.2 | N1.1 | N1.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### 6.6. Registers 6 and 7 : CONFIGURATION registers

This register configures the directions of the I/O pins. If a bit in this register is set (written with '1'), the corresponding port pin is enabled as an input with high-impedance output driver. If a bit in this register is cleared (written with '0'), the corresponding port pin is enabled as an output. Note that there is a high value resistor tied to VDD at each pin. At reset, the device's ports are inputs with a pull-up to VDD.

**Table 11. Configuration Port 0 Register**

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | C0.7 | C0.6 | C0.5 | C0.4 | C0.3 | C0.2 | C0.1 | C0.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

Table 12. Configuration Port 1 Register

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | C1.7 | C1.6 | C1.5 | C1.4 | C1.3 | C1.2 | C1.1 | C1.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### 6.7. POWER-ON RESET

When power is applied to VDD, an internal power-on reset holds the NCA9555 in a reset condition until VDD has reached VPOR. At that point, the reset condition is released and the NCA9555 registers and I2C state machine will initialize to their default states. The power-on reset typically completes the reset and enables the part by the time the power supply is above VPOR. However, when it is required to reset the part by lowering the power supply, it is necessary to lower it below 0.2 V for at least 50µs.

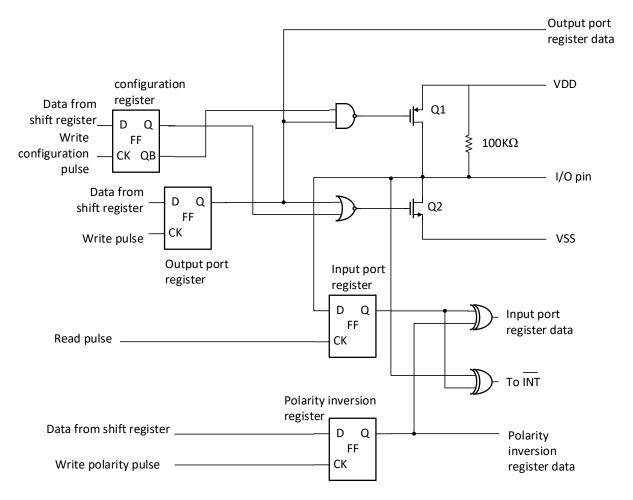

#### 6.8. I/O PORT

When an I/O is configured as an input, FETs Q1 and Q2 are off, creating a high-impedance input with a weak pull-up to VDD. The input voltage may be raised above VDD to a maximum of 5.5 V.

If the I/O is configured as an output, then either Q1 or Q2 is on, depending on the state of the Output Port register. Care should be exercised if an external voltage is applied to an I/O configured as an output because of the low-impedance path that exists between the pin and either VDD or VSS.

Fig 5. Simplified schematic of I/Os

#### 7. BUS TRANSACTIONS

Fig 6. Block Diagram of NCA9555

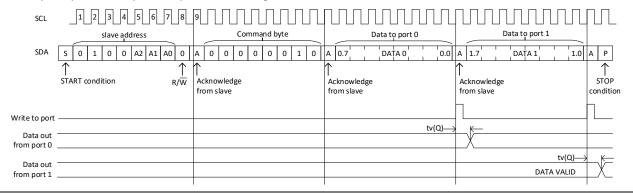

#### 7.1. WRITING TO THE PORT REGISTERS

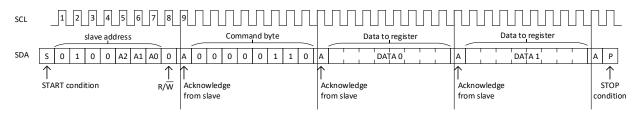

Data is transmitted to the NCA9555 by sending the device address and setting the least significant bit to a logic 0 (see Figure 4 "NCA9555 device address"). The command byte is sent after the address and determines which register will receive the data following the command byte.

The eight registers within the NCA9555 are configured to operate as four register pairs. The four pairs are Input Ports, Output Ports, Polarity Inversion Ports, and Configuration Ports. After sending data to one register, the next data byte will be sent to the other register in the pair (see Figure 7 and Figure 8). For example, if the first byte is sent to Output Port 1 (register 3), then the next byte will be stored in Output Port 0 (register 2). There is no limitation on the number of data bytes sent in one write transmission. In this way, each 8-bit register may be updated independently of the other registers.

Copyright © 2020, NOVOSENSE

#### Fig 7. Write to output port registers

Fig 8. Write to config registers

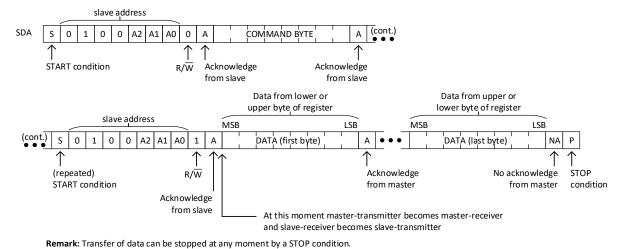

#### 7.2. READING THE PORT REGISTERS

In order to read data from the NCA9555, the bus master must first send the NCA9555 address with the least significant bit set to a logic 0 (see Figure 4 "NCA9555 device address"). The command byte is sent after the address and determines which register will be accessed. After a restart, the device address is sent again, but this time the least significant bit is set to a logic 1. Data from the register defined by the command byte will then be sent by the NCA9555 (see Figure 9, Figure 10 and Figure 11). Data is clocked into the register on the rising edge of the acknowledge clock pulse. After the first byte is read, additional bytes may be read but the data will now reflect the information in the other register in the pair. For example, if you read Input Port 1, then the next byte read would be Input Port 0. There is no limitation on the number of data bytes received in one read transmission but the final byte received, the bus master must not acknowledge the data.

Fig 9. Read from registers

Remark: Transfer of data can be stopped at any moment by a STOP condition. When this occurs, data present at the latest acknowledge phase is valid (output mode). It is assumed that the command byte has previously been set to '00' (read Input Port register).

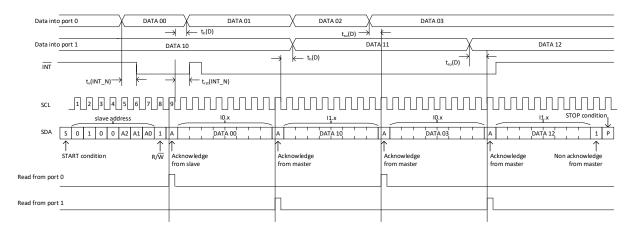

Data into port 0 Data into port 1 INT 1 2 3 4 5 6 7 8 1 0 0 1 0 0 A2 A1 A0 1 0 1 P R/W Acknowledge Acknowledge . Acknowledge Acknowledge Non acknowledge from master from slave from master from master from master Read from port 0 Read from port 1

Fig 10. Read input port registers, scenario 1

Remark: Transfer of data can be stopped at any moment by a STOP condition. When this occurs, data present at the latest acknowledge phase is valid (output mode). It is assumed that the command byte has previously been set to '00' (read Input Port register).

Fig 11. Read input port registers, scenario 2

#### 7.3. interrupt output

The open-drain interrupt output is activated when one of the port pins changes state and the pin is configured as an input. The interrupt is deactivated when the input returns to its previous state or the Input Port register is read (see Figure 10). A pin configured as an output cannot cause an interrupt. Since each 8-bit port is read independently, the interrupt caused by Port 0 will not be cleared by a read of Port 1 or the other way around.

Remark: Changing an I/O from an output to an input may cause a false interrupt to occur if the state of the pin does not match the contents of the Input Port register.

## 8. characteristics of the I<sup>2C</sup>-BUS

The I2C-bus is for 2-way, 2-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial

Copyright © 2020, NOVOSENSE

Page 17

clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

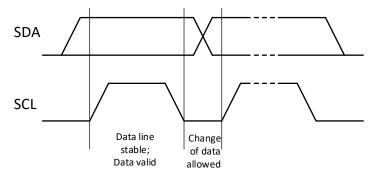

#### 8.1. bit transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as control signals (see Figure 12).

Fig 12. Bit transfer

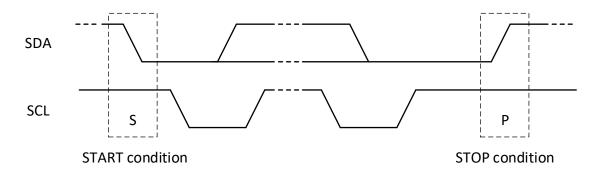

#### 8.2. start and stop conditions

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line while the clock is HIGH is defined as the START condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition (P) (see Figure 13).

Fig 13. Definition of START and STOP conditions

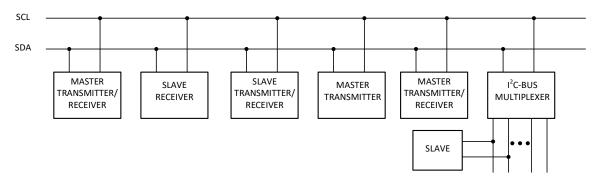

#### 8.3. system configuration

A device generating a message is a 'transmitter'; a device receiving is the 'receiver'. The device that controls the message is the 'master' and the devices which are controlled by the master are the 'slaves' (see Figure 14).

Fig 14. System configuration

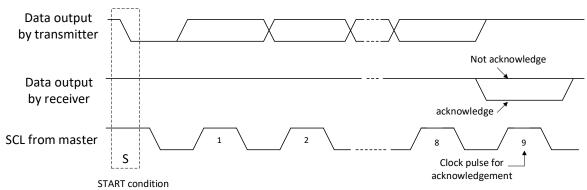

#### 8.4. Acknowledge

The number of data bytes transferred between the START and the STOP conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter, whereas the master generates an extra acknowledge related clock pulse.

A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse; set-up time and hold time must be taken into account.

A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event, the transmitter must leave the data line HIGH to enable the master to generate a STOP condition.

Fig 15. Acknowledgement on I<sup>2</sup>C-bus

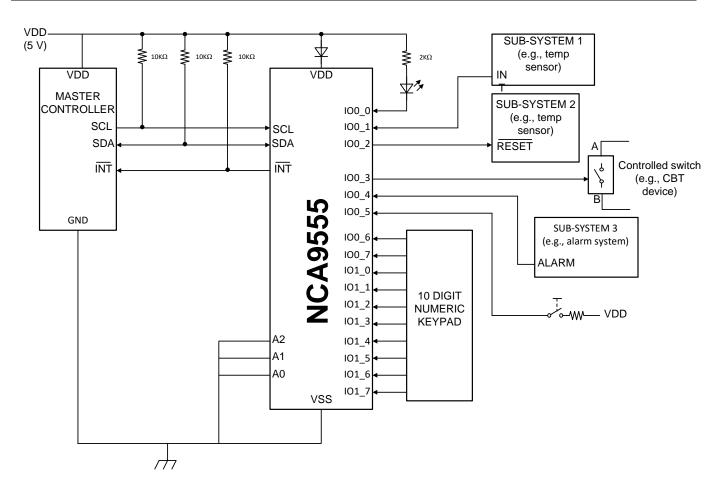

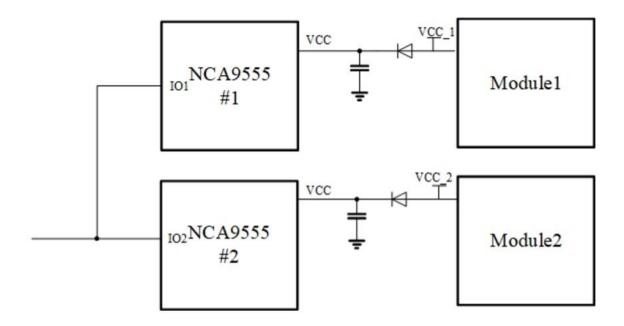

#### 9. APPLICATION DESIGN-IN INFORMATION

Fig 16. Typical application

When the IO level of the NCA9555 is higher than the power supply voltage, the diode inside the chip to prevent backflow will be turned on. In the case of power down and data input, the IO signal will be fed back to the VDD module (eg.master controller), which will cause the data to be pulled low. In order to realize IO still has high resistance characteristics when power down, it is recommended to connect a forward schottky diode to the power supply pin of NCA9555.

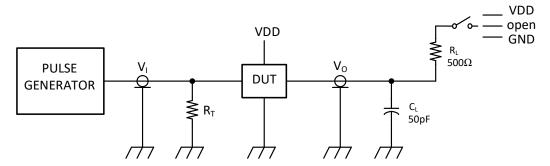

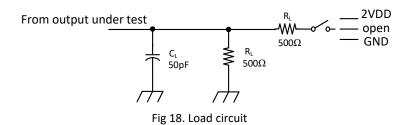

### 10. Test information

$R_L$  = load resistor.

$C_L$  = load capacitance includes jig and probe capacitance.

$R_T$  = termination resistance should be equal to the output impedance of  $Z_o$  of the pulse generators.

Fig 17. Test circuitry for switching times

Fig 19. Parameter Measurement Waveform:  $t_{rst(INT\_N)}$

Fig 20. Parameter Measurement Waveform: tVD; DAT & tVD;ACK

## 11. Package information

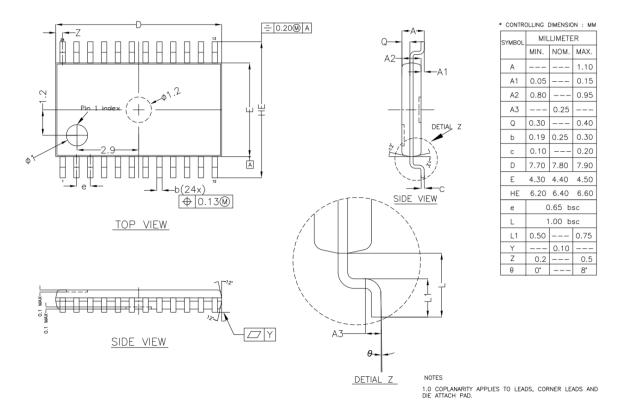

#### 11.1. package outline

Fig 21. Package outline for TSSOP24

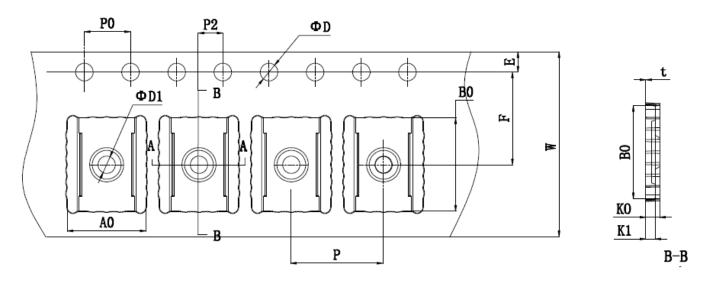

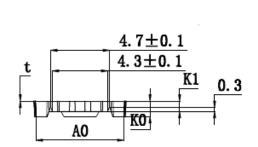

### 12. TAPE AND REEL INFORMATION

|      | -          |

|------|------------|

| E    | 1.75±0.10  |

| F    | 7.5±0.10   |

| P2   | 2.00±0.10  |

| D    | 1.55±0.10  |

| D1   | 1.55±0.10  |

| P0   | 4.00±0.10  |

| 10P0 | 40.00±0.20 |

|    | ı               |

|----|-----------------|

| ₩  | 16.00±0.30      |

| P  | 8.00 $\pm$ 0.10 |

| A0 | $6.80\pm0.10$   |

| В0 | 8.04±0.10       |

| KO | 1.25±0.10       |

| K1 | 1.1±0.10        |

| t  | $0.30 \pm 0.05$ |

| θ  | 5° TYP          |

ALL DIMENSIONSIN MILLIMETERS UNLESS OTHERWISE STATED

Fig 22. tape and reel information for TSSOP24

### 13. Order information

| Part No. | Package Type | Pins | MSL Level | Package Qty | Temperature |

|----------|--------------|------|-----------|-------------|-------------|

| NCA9555  | TSSOP        | 24   | Level 1   | 2500        | -40 to 85 ℃ |

## 14. Documentation Support

| Part Number | Product Folder | Datasheet  | Technical Documents | Isolator selection guide |

|-------------|----------------|------------|---------------------|--------------------------|

| NCA9555     | Click here     | Click here | Click here          | Click here               |

# 15. Revision history

| Revision | Description                                  | Date       |

|----------|----------------------------------------------|------------|

| 1.0      | Initial version                              | 2019/2/27  |

| 1.1      | Added thermal information& order information | 2020/2/10  |

| 1.2      | Changed 3.0 supply current, VPOR and IOL     | 2020/5/31  |

| 1.3      | Added application design-in information      | 2020/10/30 |

## 单击下面可查看定价,库存,交付和生命周期等信息

## >>Novosense