# Operational Amplifier, Railto-Rail Output, 3 MHz BW

The NCx2007x series operational amplifiers provide rail–to–rail output operation, 3 MHz bandwidth, and are available in single, dual, and quad configurations. Rail–to–rail operation enables the user to make optimal use of the entire supply voltage range while taking advantage of 3 MHz bandwidth. The NCx2007x can operate on supply voltages as low as 2.7 V over the temperature range of –40°C to 125°C. At a 2.7 V supply, the high bandwidth provides a slew rate of 2.8 V/µs while only consuming 405 µA of quiescent current per channel. The wide supply range allows the NCx2007x to run on supply voltages as high as 36 V, making it ideal for a broad range of applications. Since this is a CMOS device, high input impedance and low bias currents make it ideal for interfacing to a wide variety of signal sensors. The NCx2007x devices are available in a variety of compact packages. Automotive qualified options are available under the NCV prefix.

#### **Features**

- Rail-To-Rail Output

- Wide Supply Range: 2.7 V to 36 V

- Wide Bandwidth: 3 MHz typical at  $V_S = 2.7 \text{ V}$

- High Slew Rate: 2.8 V/ $\mu$ s typical at V<sub>S</sub> = 2.7 V

- Low Supply Current: 405  $\mu A$  per channel at  $V_S = 2.7 \ V$

- Low Input Bias Current: 5 pA typical

- Wide Temperature Range: -40°C to 125°C

- Available in a variety of packages

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

## **Applications**

- Current Sensing

- Signal Conditioning

- Automotive

#### **End Products**

- Notebook Computers

- Portable Instruments

- Power Supplies

## ON Semiconductor®

www.onsemi.com

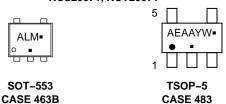

SOT-553 CASE 463B TSOP-5 CASE 483

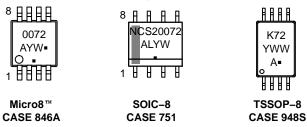

Micro8<sup>™</sup> CASE 846A SOIC-8 CASE 751

TSSOP-8 CASE 948S

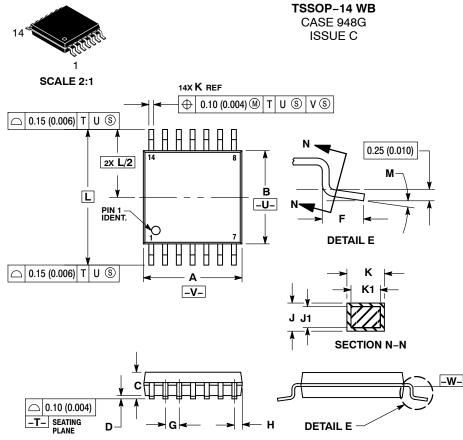

TSSOP-14 CASE 948G

SOIC-14 NB CASE 751A

## **DEVICE MARKING INFORMATION**

See general marking information in the device marking section on page 2 of this data sheet.

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 4 of this data sheet.

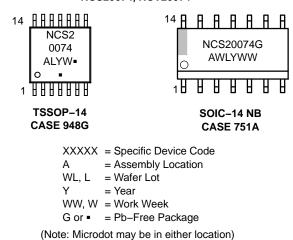

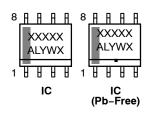

### **MARKING DIAGRAMS**

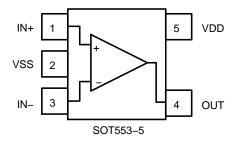

# Single Channel Configuration NCS20071, NCV20071

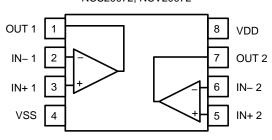

# Dual Channel Configuration NCS20072, NCV20072

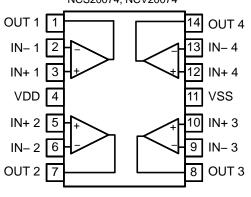

# Quad Channel Configuration NCS20074, NCV20074

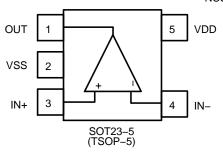

## Single Channel Configuration NCS20071, NCV20071

# **Dual Channel Configuration** NCS20072, NCV20072

#### Quadruple Channel Configuration NCS20074, NCV20074

Figure 1. Pin Connections

## **ORDERING INFORMATION**

| Device           | Configuration | Automotive | Marking      | Package                     | Shipping <sup>†</sup> |

|------------------|---------------|------------|--------------|-----------------------------|-----------------------|

| NCS20071SN2T1G   |               | Na         | AEA          | TSOP-5<br>(Pb-Free)         | 3000 / Tape and Reel  |

| NCS20071XV53T2G  | Cinala        | No         | AL           | SOT553-5<br>(Pb-Free)       | 4000 / Tape and Reel  |

| NCV20071SN2T1G*  | Single        | V          | AEA          | TSOP-5<br>(Pb-Free)         | 3000 / Tape and Reel  |

| NCV20071XV53T2G* |               | Yes        | AL           | SOT553-5<br>(Pb-Free)       | 4000 / Tape and Reel  |

| NCS20072DMR2G    |               |            | 0072         | Micro8 (MSOP8)<br>(Pb-Free) | 4000 / Tape and Reel  |

| NCS20072DR2G     |               | No         | NCS20072     | SOIC-8<br>(Pb-Free)         | 2500 / Tape and Reel  |

| NCS20072DTBR2G   | Dord          |            | K72          | TSSOP-8<br>(Pb-Free)        | 2500 / Tape and Reel  |

| NCV20072DMR2G*   | Dual          |            | 0072         | Micro8 (MSOP8)<br>(Pb-Free) | 4000 / Tape and Reel  |

| NCV20072DR2G*    |               | Yes        | NCS20072     | SOIC-8<br>(Pb-Free)         | 2500 / Tape and Reel  |

| NCV20072DTBR2G*  |               |            | K72          | TSSOP-8<br>(Pb-Free)        | 2500 / Tape and Reel  |

| NCS20074DR2G     |               | N          | NCS20074     | SOIC-14<br>(Pb-Free)        | 2500 / Tape and Reel  |

| NCS20074DTBR2G   | Overl         | No         | NCS2<br>0074 | TSSOP-14<br>(Pb-Free)       | 2500 / Tape and Reel  |

| NCV20074DR2G*    | Quad          | Va a       | NCS20074     | SOIC-14<br>(Pb-Free)        | 2500 / Tape and Reel  |

| NCV20074DTBR2G*  |               | Yes        | NCS2<br>0074 | TSSOP-14<br>(Pb-Free)       | 2500 / Tape and Reel  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC–Q100 Qualified and PPAP

Capable.

### **ABSOLUTE MAXIMUM RATINGS** (Note 1)

|                                                   | Rating                                                                                                                                                             | Symbol                        | Limit                                        | Unit |  |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------|------|--|

| Supply Voltage (V <sub>DD</sub> – V <sub>SS</sub> | ) (Note 4)                                                                                                                                                         | V <sub>S</sub>                | 40                                           | V    |  |

| Input Voltage                                     |                                                                                                                                                                    | V <sub>CM</sub>               | $V_{SS} - 0.2$ to $V_{DD} + 0.2$             | V    |  |

| Differential Input Voltage (N                     | lote 2)                                                                                                                                                            | $V_{ID}$                      | ±V <sub>s</sub>                              | V    |  |

| Maximum Input Current                             |                                                                                                                                                                    | I <sub>IN</sub>               | ±10                                          | mA   |  |

| Maximum Output Current (                          | Note 3)                                                                                                                                                            | I <sub>O</sub>                | ±100                                         | mA   |  |

| Continuous Total Power Dis                        | ssipation (Note 4)                                                                                                                                                 | $P_{D}$                       | P <sub>D</sub> 200                           |      |  |

| Maximum Junction Temper                           | ature                                                                                                                                                              | $T_J$                         | 150                                          | °C   |  |

| Storage Temperature Rang                          | e                                                                                                                                                                  | T <sub>STG</sub>              | -65 to 150                                   | °C   |  |

| Mounting Temperature (Infr                        | rared or Convection – 20 sec)                                                                                                                                      | T <sub>mount</sub>            | 260                                          | °C   |  |

| ESD Capability (Note 5)                           | Human Body Model<br>Machine Model – NCx20071<br>Machine Model – NCx20072, NCx20074<br>Charged Device Model – NCx20071, NCx20072<br>Charged Device Model – NCx20074 | HBM<br>MM<br>MM<br>CDM<br>CDM | 2000<br>200<br>150<br>2000 (C6)<br>1000 (C6) | V    |  |

| Latch-Up Current (Note 6)                         |                                                                                                                                                                    | I <sub>LU</sub>               | 100                                          | mA   |  |

| Moisture Sensitivity Level (                      | Note 7)                                                                                                                                                            | MSL                           | Level 1                                      |      |  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 2. Maximum input current must be limited to ±10 mA. Series connected resistors of at least 500 Ω on both inputs may be used to limit the maximum input current to ±10 mA.

- 3. Total power dissipation must be limited to prevent the junction temperature from exceeding the 150°C limit.

- 4. Continuous short circuit operation to ground at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C. Output currents in excess of the maximum output current rating over the long term may adversely affect reliability. Shorting output to either VDD or VSS will adversely affect reliability.

- 5. This device series incorporates ESD protection and is tested by the following methods:

- ESD Human Body Model tested per JEDEC standard JS-001 (AEC-Q100-002)

- ESD Machine Model tested per JEDEC standard JESD22-A115 (AEC-Q100-003)

- ESD Charged Device Model tested per JEDEC standard JESD22-C101 (AEC-Q100-011)

- 6. Latch-up Current tested per JEDEC standard JESD78 (AEC-Q100-004)

- 7. Moisture Sensitivity Level tested per IPC/JEDEC standard J-STD-020A

### THERMAL INFORMATION

| Parameter           | Symbol            | Package         | Single Layer<br>Board (Note 8) | Multi–Layer<br>Board (Note 9) | Unit |

|---------------------|-------------------|-----------------|--------------------------------|-------------------------------|------|

|                     |                   | SOT23-5 / TSOP5 | 265                            | 195                           |      |

|                     |                   | SOT553-5        | 325                            | 244                           | ]    |

|                     | $\theta_{\sf JA}$ | Micro8 / MSOP8  | 236                            | 167                           | ]    |

| Junction-to-Ambient |                   | SOIC-8          | 190                            | 131                           | °C/W |

|                     |                   | TSSOP-8         | 253                            | 194                           |      |

|                     |                   | SOIC-14         | 142                            | 101                           |      |

|                     |                   | TSSOP-14        | 179                            | 128                           |      |

- 8. Values based on a 1S standard PCB according to JEDEC51-3 with 1.0 oz copper and a 300 mm<sup>2</sup> copper area

- Values based on a 1S2P standard PCB according to JEDEC51-7 with 1.0 oz copper and a 100 mm<sup>2</sup> copper area

#### **OPERATING RANGES**

| Parameter                                | Symbol          | Min             | Max                    | Unit |

|------------------------------------------|-----------------|-----------------|------------------------|------|

| Operating Supply Voltage (Single Supply) | Vs              | 2.7             | 36                     | V    |

| Operating Supply Voltage (Split Supply)  | Vs              | ±1.35           | ±18                    | V    |

| Differential Input Voltage (Note 10)     | $V_{ID}$        |                 | V <sub>S</sub>         | V    |

| Input Common Mode Voltage Range          | V <sub>CM</sub> | V <sub>SS</sub> | V <sub>DD</sub> – 1.35 | V    |

| Ambient Temperature                      | T <sub>A</sub>  | -40             | 125                    | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

10. Maximum input current must be limited to  $\pm 10$  mA. See Absolute Maximum Ratings for more information.

## ELECTRICAL CHARACTERISTICS AT $V_S = 2.7 \text{ V}$

$T_A = 25^{\circ}\text{C}$ ;  $R_L \ge 10 \text{ k}\Omega$ ;  $V_{CM} = V_{OUT} = \text{mid}$ -supply unless otherwise noted. All limits are guaranteed by testing or statistical analysis. **Boldface** limits apply over the specified temperature range,  $T_A = -40^{\circ}\text{C}$  to 125°C. (Notes 11, 12)

| Parameter                           | Symbol                   | Cond                                                          | litions                       | Min | Тур   | Max  | Unit  |

|-------------------------------------|--------------------------|---------------------------------------------------------------|-------------------------------|-----|-------|------|-------|

| INPUT CHARACTERISTICS               |                          |                                                               |                               |     |       | •    |       |

|                                     |                          | NO                                                            | 20074                         |     | 1.3   | ±3.5 |       |

| Innut Officet Valtage               | \ <i>/</i>               | NCX.                                                          | 20071                         |     |       | ±4.5 | \/    |

| Input Offset Voltage                | V <sub>OS</sub>          | NCv20072                                                      | NCv20074                      |     | 1.3   | ±3   | mV    |

|                                     |                          | NCX20072                                                      | , NCx20074                    |     |       | ±4   |       |

| Offset Voltage Drift                | $\Delta V_{OS}/\Delta T$ | T <sub>A</sub> = 25°0                                         | C to 125°C                    |     | 2     |      | μV/°C |

| Input Bias Current (Note 12)        | L.                       |                                                               |                               |     | 5     | 200  | рA    |

| input bias Current (Note 12)        | I <sub>IB</sub>          |                                                               |                               |     |       | 1500 | PΑ    |

|                                     |                          | NCv20071                                                      | NCv20072                      |     | 2     | 75   |       |

| Input Officet Current (Note 12)     | ,                        | NCX20071                                                      | , NCx20072                    |     |       | 500  | - A   |

| Input Offset Current (Note 12)      | los                      | NCv                                                           | 20074                         |     | 2     | 75   | рA    |

|                                     |                          | INCX.                                                         | 20074                         |     |       | 200  | ]     |

| Channel Congretion                  | VTLV                     | DC                                                            | NCx20072                      |     | 100   |      | ٩D    |

| Channel Separation                  | XTLK                     | DC NCx20074                                                   |                               |     | 115   |      | dB    |

| Differential Input Resistance       | R <sub>ID</sub>          |                                                               |                               |     | 5     |      | GΩ    |

| Common Mode Input Resistance        | R <sub>IN</sub>          |                                                               |                               |     | 5     |      | GΩ    |

| Differential Input Capacitance      | C <sub>ID</sub>          |                                                               |                               |     | 1.5   |      | pF    |

| Common Mode Input Capacitance       | C <sub>CM</sub>          |                                                               |                               |     | 3.5   |      | pF    |

| Common Mode Dejection Detic         | CMPP                     | $V_{CM} = V_{SS} + 0.2 \text{ V to } V_{DD} - 1.35 \text{ V}$ |                               | 90  | 110   |      | dB    |

| Common Mode Rejection Ratio         | CMRR                     | $v_{CM} = v_{SS} + 0.2$                                       | V 10 V <sub>DD</sub> – 1.35 V | 69  |       |      | ub    |

| OUTPUT CHARACTERISTICS              |                          |                                                               |                               |     |       |      |       |

| Open Leen Voltage Coin              | ۸                        |                                                               |                               | 96  | 118   |      | ٩D    |

| Open Loop Voltage Gain              | $A_{VOL}$                |                                                               |                               | 86  |       |      | dB    |

| Output Compat Comphility (Nata 42)  | ,                        | Op amp sir                                                    | nking current                 |     | 70    |      | ^     |

| Output Current Capability (Note 13) | Ι <sub>Ο</sub>           | Op amp sou                                                    | rcing current                 |     | 50    |      | mA    |

| Output Valta and High               | M                        | Valta na autout aud                                           |                               |     | 0.006 | 0.15 |       |

| Output Voltage High                 | V <sub>OH</sub>          | voitage output swi                                            | ng from positive rail         |     |       | 0.22 | V     |

| Outrot Valta and Laur               | \ /                      | Valta an autout audi                                          | an financia na matika maji    |     | 0.005 | 0.15 |       |

| Output Voltage Low                  | V <sub>OL</sub>          | voltage output swii                                           | ng from negative rail         |     |       | 0.22 | V     |

| AC CHARACTERISTICS                  |                          |                                                               |                               |     |       |      |       |

| Unity Gain Bandwidth                | UGBW                     | C <sub>L</sub> =                                              | 25 pF                         |     | 3     |      | MHz   |

| Slew Rate at Unity Gain             | SR                       | $C_{L} = 20 \text{ pF}$                                       | $R_L = 2 k\Omega$             |     | 2.8   |      | V/μs  |

| Phase Margin                        | φm                       | C <sub>L</sub> =                                              | 25 pF                         |     | 50    |      | ٥     |

| Gain Margin                         | A <sub>m</sub>           | C <sub>L</sub> =                                              | 25 pF                         |     | 14    |      | dB    |

| Cattling Time                       |                          | V <sub>O</sub> = 1 Vpp,                                       | Settling time to 0.1%         |     | 0.6   |      |       |

| Settling Time                       | ttling Time              |                                                               | Settling time to 0.01%        |     | 1.2   |      | μs    |

<sup>11.</sup> Refer to ABSOLUTE MAXIMUM RATINGS and APPLICATION INFORMATION for Safe Operating Area.

<sup>12.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization.

<sup>13.</sup> Power dissipation must be limited to prevent junction temperature from exceeding 150°C. See Absolute Maximum Ratings for more information.

### **ELECTRICAL CHARACTERISTICS AT V<sub>S</sub> = 2.7 V**

$T_A = 25^{\circ}\text{C}$ ;  $R_L \ge 10 \text{ k}\Omega$ ;  $V_{CM} = V_{OUT} = \text{mid}$ -supply unless otherwise noted. All limits are guaranteed by testing or statistical analysis. **Boldface** limits apply over the specified temperature range,  $T_A = -40^{\circ}\text{C}$  to 125°C. (Notes 11, 12)

| Parameter                            | Symbol          | Cond                                    | itions  | Min  | Тур | Max | Unit                                                |

|--------------------------------------|-----------------|-----------------------------------------|---------|------|-----|-----|-----------------------------------------------------|

| NOISE CHARACTERISTICS                |                 |                                         |         |      |     |     | -                                                   |

| Total Harmonic Distortion plus Noise | THD+N           | V <sub>IN</sub> = 0.5 Vpp, f            |         | 0.05 |     | %   |                                                     |

| Inner Deferred Valters Naise         | _               | f = 1                                   | kHz     |      | 30  |     | \ // <del>                                   </del> |

| Input Referred Voltage Noise         | e <sub>n</sub>  | f = 10 kHz                              |         |      | 20  |     | nV/√ <del>Hz</del>                                  |

| Input Referred Current Noise         | i <sub>n</sub>  | f = 1 kHz                               |         |      | 90  |     | fA/√ <del>Hz</del>                                  |

| SUPPLY CHARACTERISTICS               |                 |                                         |         |      |     |     |                                                     |

| Davisa Comple Daisetica Datis        | 2022            |                                         |         | 114  | 135 |     | ٩D                                                  |

| Power Supply Rejection Ratio         | PSRR            | NO L                                    | ₋oad    | 100  |     |     | dB                                                  |

|                                      |                 | NC-20074                                | Noteed  |      | 420 | 625 |                                                     |

| David Original Original              |                 | NCx20071                                | No load |      |     | 765 | 1                                                   |

| Power Supply Quiescent Current       | I <sub>DD</sub> |                                         |         |      | 405 | 525 | μΑ                                                  |

|                                      |                 | NCx20072, NCx20074 Per channel, no load |         |      |     | 625 | 1                                                   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 11. Refer to ABSOLUTE MAXIMUM RATINGS and APPLICATION INFORMATION for Safe Operating Area.

- 12. Performance guaranteed over the indicated operating temperature range by design and/or characterization.

- 13. Power dissipation must be limited to prevent junction temperature from exceeding 150°C. See Absolute Maximum Ratings for more information.

## **ELECTRICAL CHARACTERISTICS AT V<sub>S</sub> = 5 V**

$T_A = 25$ °C;  $R_L \ge 10 \text{ k}\Omega$ ;  $V_{CM} = V_{OUT} = \text{mid}$ -supply unless otherwise noted. All limits are guaranteed by testing or statistical analysis. **Boldface** limits apply over the specified temperature range,  $T_A = -40$ °C to 125°C. (Notes 14, 15)

| Parameter                      | Symbol                   | Conditions         |                | Min | Тур | Max  | Unit  |

|--------------------------------|--------------------------|--------------------|----------------|-----|-----|------|-------|

| INPUT CHARACTERISTICS          |                          |                    |                |     |     |      |       |

|                                |                          |                    | 1000074        |     | 1.3 | ±3.5 |       |

| Innut Offert Veltage           | V                        | NCx20071           |                |     |     | ±4.5 | \/    |

| Input Offset Voltage           | Vos                      | NCoo               | 1070 NO. 20074 |     | 1.3 | ±3   | mV    |

|                                |                          | NCx20072, NCx20074 |                |     |     | ±4   |       |

| Offset Voltage Drift           | $\Delta V_{OS}/\Delta T$ | $T_A = 2$          | 25°C to 125 °C |     | 2   |      | μV/°C |

| Innut Bigg Current (Note 15)   |                          |                    |                |     | 5   | 200  | n 1   |

| Input Bias Current (Note 15)   | I <sub>IB</sub>          |                    |                |     |     | 1500 | pА    |

|                                |                          | NCx20071, NCx20072 |                |     | 2   | 75   |       |

| Innut Offeet Comment (Note 45) |                          |                    |                |     |     | 500  |       |

| Input Offset Current (Note 15) | los                      |                    | 10-00074       |     | 2   | 75   | - pA  |

|                                |                          | ſ                  | NCx20074       |     |     | 200  |       |

| 0, 10,                         | VTII                     | <b>D</b> 0         | NCx20072       |     | 100 |      | i.    |

| Channel Separation             | XTLK                     | DC                 | NCx20074       |     | 115 |      | dB    |

| Differential Input Resistance  | R <sub>ID</sub>          |                    | •              |     | 5   |      | GΩ    |

| Common Mode Input Resistance   | R <sub>IN</sub>          |                    |                |     | 5   |      | GΩ    |

| Differential Input Capacitance | C <sub>ID</sub>          |                    |                |     | 1.5 |      | pF    |

| Common Mode Input Capacitance  | C <sub>CM</sub>          |                    |                |     | 3.5 |      | pF    |

- 14. Refer to ABSOLUTE MAXIMUM RATINGS and APPLICATION INFORMATION for Safe Operating Area.

- 15. Performance guaranteed over the indicated operating temperature range by design and/or characterization.

- 16. Power dissipation must be limited to prevent junction temperature from exceeding 150°C. See Absolute Maximum Ratings for more information.

**ELECTRICAL CHARACTERISTICS AT V**<sub>S</sub> = 5 V  $T_A = 25^{\circ}C$ ;  $R_L \ge 10$  kΩ;  $V_{CM} = V_{OUT} = \text{mid}$ –supply unless otherwise noted. All limits are guaranteed by testing or statistical analysis. **Boldface** limits apply over the specified temperature range,  $T_A = -40^{\circ}C$  to 125°C. (Notes 14, 15)

| Parameter                            | Symbol                                  | Cond                                                      | itions                        | Min | Тур   | Max  | Unit               |

|--------------------------------------|-----------------------------------------|-----------------------------------------------------------|-------------------------------|-----|-------|------|--------------------|

| INPUT CHARACTERISTICS                | •,                                      | 1                                                         |                               |     | -71   |      |                    |

|                                      |                                         |                                                           |                               | 102 | 125   |      |                    |

| Common Mode Rejection Ratio          | CMRR                                    | $V_{CM} = V_{SS} + 0.2$                                   | V to V <sub>DD</sub> – 1.35 V | 80  | 0     |      | dB                 |

| OUTPUT CHARACTERISTICS               |                                         | l                                                         |                               |     |       |      |                    |

|                                      |                                         |                                                           |                               | 96  | 120   |      |                    |

| Open Loop Voltage Gain               | $A_{VOL}$                               |                                                           |                               | 86  |       |      | dB                 |

|                                      |                                         | Op amp sin                                                | king current                  |     | 50    |      |                    |

| Output Current Capability (Note 16)  | I <sub>O</sub>                          | Op amp sou                                                | rcing current                 |     | 60    |      | mA                 |

| 0                                    | .,,                                     |                                                           |                               |     | 0.013 | 0.20 | .,                 |

| Output Voltage High                  | V <sub>OH</sub>                         | Voltage output swii                                       | ng from positive rail         |     |       | 0.25 | - V                |

| Output Valta as I am                 | V                                       | Valta and acceptant accept                                | a fue as a section well       |     | 0.01  | 0.10 |                    |

| Output Voltage Low                   | $V_{OL}$                                | voltage output swir                                       | ng from negative rail         |     |       | 0.15 | V                  |

| AC CHARACTERISTICS                   |                                         |                                                           |                               |     |       |      |                    |

| Unity Gain Bandwidth                 | UGBW                                    | C <sub>L</sub> = 25 pF                                    |                               |     | 3     |      | MHz                |

| Slew Rate at Unity Gain              | SR                                      | $C_{L} = 20 \text{ pF}$                                   | $R_L = 2 k\Omega$             |     | 2.7   |      | V/μs               |

| Phase Margin                         | $\phi_{m}$                              | C <sub>L</sub> =                                          | 25 pF                         |     | 50    |      | 0                  |

| Gain Margin                          | $A_{m}$                                 | C <sub>L</sub> =                                          | 25 pF                         |     | 14    |      | dB                 |

| Settling Time                        | 4                                       | $V_O = 3 \text{ Vpp},$<br>Gain = 1, $C_L = 20 \text{ pF}$ | Settling time to 0.1%         |     | 1.2   |      | 0                  |

| Settling Time                        | t <sub>S</sub>                          | Gain = 1, $C_L = 20 \text{ pF}$                           | Settling time to 0.01%        |     | 5.6   |      | μS                 |

| NOISE CHARACTERISTICS                |                                         |                                                           |                               |     |       |      |                    |

| Total Harmonic Distortion plus Noise | THD+N                                   | V <sub>IN</sub> = 2.5 Vpp, f                              | = 1 kHz, Av = 1               |     | 0.009 |      | %                  |

| Input Referred Voltage Noice         | 0                                       | f = 1                                                     | kHz                           |     | 30    |      | nV/√ <del>Hz</del> |

| Input Referred Voltage Noise         | e <sub>n</sub>                          | f = 10                                                    | ) kHz                         |     | 20    |      | TIV/ V⊓Z           |

| Input Referred Current Noise         | i <sub>n</sub>                          | f = 1                                                     | kHz                           |     | 90    |      | fA/√Hz             |

| SUPPLY CHARACTERISTICS               |                                         |                                                           |                               |     |       |      |                    |

| Dower Cumply Dejection Datio         | DCDD                                    | No.1                                                      | and                           | 114 | 135   |      | dD                 |

| Power Supply Rejection Ratio         | wer Supply Rejection Ratio PSRR No Load |                                                           | _0au                          | 100 |       |      | dB                 |

|                                      | _                                       | NCv20071                                                  | No load                       |     | 430   | 635  |                    |

| Power Supply Ouiocoopt Current       | I <sub>DD</sub> NO                      | NCx20071                                                  | No load                       |     |       | 775  |                    |

| Power Supply Quiescent Current       |                                         | NCv20072 NCv20074                                         | Per channel, no load          |     | 410   | 530  | μΑ                 |

|                                      |                                         | NCx20072, NCx20074 Per channel, no load                   |                               |     |       | 630  | ]                  |

<sup>14.</sup> Refer to ABSOLUTE MAXIMUM RATINGS and APPLICATION INFORMATION for Safe Operating Area.

<sup>15.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization.

<sup>16.</sup> Power dissipation must be limited to prevent junction temperature from exceeding 150°C. See Absolute Maximum Ratings for more information.

## ELECTRICAL CHARACTERISTICS AT $V_S = 10 \text{ V}$

$T_A = 25^{\circ}\text{C}$ ;  $R_L \ge 10 \text{ k}\Omega$ ;  $V_{CM} = V_{OUT} = \text{mid-supply}$  unless otherwise noted. All limits are guaranteed by testing or statistical analysis. Boldface limits apply over the specified temperature range,  $T_A = -40^{\circ}\text{C}$  to 125°C. (Notes 17, 18)

| Parameter                           | Symbol                   | Cond                            | litions                       | Min | Тур   | Max  | Unit  |

|-------------------------------------|--------------------------|---------------------------------|-------------------------------|-----|-------|------|-------|

| INPUT CHARACTERISTICS               |                          |                                 |                               |     | •     | _    | •     |

| Leaved Office ( Malliane            | .,                       | NO                              | 20074                         |     | 1.3   | ±3.5 | mV    |

| Input Offset Voltage                | V <sub>OS</sub>          | NCX2                            | 20071                         |     |       | ±4.5 | mV    |

| Input Offset Voltage                | V                        | NCv20072                        | , NCx20074                    |     | 1.3   | ±3   | mV    |

| input Onset voltage                 | V <sub>OS</sub>          | NGX20072                        | , NOX20074                    |     |       | ±4   | mV    |

| Offset Voltage Drift                | $\Delta V_{OS}/\Delta T$ | T <sub>A</sub> = 25°C           | C to 125°C                    |     | 2     |      | μV/°C |

| Input Bias Current (Note 18)        | I <sub>IB</sub>          |                                 |                               |     | 5     | 200  | pА    |

| mpat ziao cament (treto re)         | ,ID                      |                                 |                               |     |       | 1500 | μ     |

|                                     |                          | NCx20071                        | , NCx20072                    |     | 2     | 75   |       |

| Input Offset Current (Note 18)      | los                      | 110/20011                       | , 110/20072                   |     |       | 500  | рА    |

| input offset outrefit (Note 10)     | 108                      | NCx:                            | 20074                         |     | 2     | 75   | PΛ    |

|                                     |                          | 140%                            | 2007 4                        |     |       | 200  |       |

| Channel Separation                  | XTLK                     | DC                              | NCx20072                      |     | 100   |      | dB    |

| Grianner Geparation                 | XILK                     | NCx20074                        |                               |     | 115   |      | ub.   |

| Differential Input Resistance       | $R_{ID}$                 |                                 |                               |     | 5     |      | GΩ    |

| Common Mode Input Resistance        | R <sub>IN</sub>          |                                 |                               |     | 5     |      | GΩ    |

| Differential Input Capacitance      | $C_{ID}$                 |                                 |                               |     | 1.5   |      | pF    |

| Common Mode Input Capacitance       | C <sub>CM</sub>          |                                 |                               |     | 3.5   |      | pF    |

| Common Mode Rejection Ratio         | CMRR                     | V                               | V to V <sub>DD</sub> – 1.35 V | 110 | 130   |      | dB    |

| Common wode rejection ratio         | CIVILLIA                 | VCM - VSS + 0.2                 | V 10 VDD - 1.33 V             | 87  |       |      | uB    |

| OUTPUT CHARACTERISTICS              |                          |                                 |                               |     |       |      |       |

| Open Loop Voltage Gain              | Δ                        |                                 |                               | 98  | 120   |      | dB    |

| Open Loop Voltage Gain              | A <sub>VOL</sub>         |                                 |                               | 88  |       |      | uБ    |

| Output Current Capability (Note 19) | I.                       | Op amp sin                      | king current                  |     | 50    |      | mA    |

| Output Current Capability (Note 19) | Io                       | Op amp sou                      | rcing current                 |     | 65    |      | IIIA  |

| Output Voltage High                 | V                        | Voltago output swi              | ng from positive rail         |     | 0.023 | 0.08 | V     |

| Output voltage riigh                | V <sub>OH</sub>          | voltage output swi              | ng nom positive rail          |     |       | 0.10 | V     |

| Output Voltage Low                  | V <sub>a</sub> ,         | Voltago output swir             | ng from negative rail         |     | 0.022 | 0.3  | V     |

| Output Voltage Low                  | V <sub>OL</sub>          | voltage output swii             | ig nom negative rail          |     |       | 0.35 | V     |

| AC CHARACTERISTICS                  |                          |                                 |                               |     |       |      |       |

| Unity Gain Bandwidth                | UGBW                     | C <sub>L</sub> =                | 25 pF                         |     | 3     |      | MHz   |

| Slew Rate at Unity Gain             | SR                       | $C_{L} = 20 \text{ pF}$         | $R_L = 2 k\Omega$             |     | 2.6   |      | V/μs  |

| Phase Margin                        | $\phi_{\text{m}}$        | C <sub>L</sub> =                | C <sub>L</sub> = 25 pF        |     | 50    |      | 0     |

| Gain Margin                         | A <sub>m</sub>           | C <sub>L</sub> =                | 25 pF                         |     | 14    |      | dB    |

| Settling Time                       | t-                       | $V_{O} = 8.5 \text{ Vpp},$      | Settling time to 0.1%         |     | 3.4   |      |       |

| Columny Time                        | t <sub>S</sub>           | Gain = 1, $C_L = 20 \text{ pF}$ | Settling time to 0.01%        |     | 6.8   |      | μS    |

<sup>17.</sup> Refer to ABSOLUTE MAXIMUM RATINGS and APPLICATION INFORMATION for Safe Operating Area.

<sup>18.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization.

<sup>19.</sup> Power dissipation must be limited to prevent junction temperature from exceeding 150°C. See Absolute Maximum Ratings for more information.

### **ELECTRICAL CHARACTERISTICS AT V<sub>S</sub> = 10 V**

$T_A = 25^{\circ}\text{C}$ ;  $R_L \ge 10 \text{ k}\Omega$ ;  $V_{CM} = V_{OUT} = \text{mid}$ -supply unless otherwise noted. All limits are guaranteed by testing or statistical analysis. Boldface limits apply over the specified temperature range,  $T_A = -40^{\circ}\text{C}$  to 125°C. (Notes 17, 18)

| Parameter                            | Symbol          | Cond                                   | itions  | Min   | Тур | Max | Unit                  |

|--------------------------------------|-----------------|----------------------------------------|---------|-------|-----|-----|-----------------------|

| NOISE CHARACTERISTICS                |                 |                                        |         |       |     |     |                       |

| Total Harmonic Distortion plus Noise | THD+N           | V <sub>IN</sub> = 7.5 Vpp, f           |         | 0.004 |     | %   |                       |

| Innuit Defermed Valteria Naisa       | _               | f = 1                                  | kHz     |       | 30  |     | ->/// <del>   -</del> |

| Input Referred Voltage Noise         | e <sub>n</sub>  | f = 10 kHz                             |         |       | 20  |     | nV/√ <del>Hz</del>    |

| Input Referred Current Noise         | i <sub>n</sub>  | f = 1 kHz                              |         |       | 90  |     | fA/√ <del>Hz</del>    |

| SUPPLY CHARACTERISTICS               |                 |                                        |         |       |     |     |                       |

| Davisa Comple Daiastica Datis        | 2022            | No Load                                |         | 114   | 135 |     | ٩D                    |

| Power Supply Rejection Ratio         | PSRR            | NO L                                   | -oad    | 100   |     |     | dB                    |

|                                      |                 | NC-20074                               | No load |       | 430 | 645 |                       |

| Davisa Comple Ordanas Compant        |                 | NCx20071                               | No load |       |     | 785 |                       |

| Power Supply Quiescent Current       | I <sub>DD</sub> |                                        |         |       | 416 | 540 | μΑ                    |

|                                      |                 | NCx20072, NCx20074 Per channel, no loa |         |       |     | 640 | 1                     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 17. Refer to ABSOLUTE MAXIMUM RATINGS and APPLICATION INFORMATION for Safe Operating Area.

- 18. Performance guaranteed over the indicated operating temperature range by design and/or characterization.

- 19. Power dissipation must be limited to prevent junction temperature from exceeding 150°C. See Absolute Maximum Ratings for more information.

## **ELECTRICAL CHARACTERISTICS AT V<sub>S</sub> = 36 V**

$T_A = 25^{\circ}\text{C}$ ;  $R_L \ge 10 \text{ k}\Omega$ ;  $V_{CM} = V_{OUT} = \text{mid-supply}$  unless otherwise noted. All limits are guaranteed by testing or statistical analysis. Boldface limits apply over the specified temperature range,  $T_A = -40^{\circ}\text{C}$  to 125°C. (Notes 20, 21)

| Parameter                      | Symbol                   | Cond               | Conditions         |  | Тур  | Max  | Unit  |

|--------------------------------|--------------------------|--------------------|--------------------|--|------|------|-------|

| INPUT CHARACTERISTICS          |                          |                    |                    |  |      |      |       |

|                                |                          | NCx20071           |                    |  | 1.3  | ±3.5 | mV    |

| Innut Officet Voltage          |                          | NCX                | 20071              |  |      | ±4.5 | mV    |

| Input Offset Voltage           | Vos                      | NCv20073           | 2, NCx20074        |  | 1.3  | ±3   | mV    |

|                                |                          | NCX20072           | z, NCX20074        |  |      | ±4   | mV    |

| Offset Voltage Drift           | $\Delta V_{OS}/\Delta T$ | $T_A = 25^{\circ}$ | C to 125°C         |  | 2    |      | μV/°C |

| Input Bias Current (Note 21)   |                          |                    |                    |  | 5    | 200  |       |

|                                | I <sub>IB</sub>          | NCx20071           | NCx20071, NCx20072 |  |      | 2000 | pА    |

|                                |                          | NCx                |                    |  | 1500 |      |       |

|                                |                          | NCv20074           | NCx20071, NCx20072 |  | 2    | 75   |       |

| lanut Offeet Comment (Nets 24) |                          | NCX20071           |                    |  |      | 1000 |       |

| Input Offset Current (Note 21) | los                      | NO                 | 20074              |  | 2    | 75   | pА    |

|                                |                          | NCX                | 20074              |  |      | 200  | 1     |

| Oh a saad Oan and Car          | VTLIC                    | <b>DO</b>          | NCx20072           |  | 100  |      | -ID   |

| Channel Separation             | XTLK                     | DC                 | NCx20074           |  | 115  |      | dB    |

| Differential Input Resistance  | R <sub>ID</sub>          |                    | •                  |  | 5    |      | GΩ    |

| Common Mode Input Resistance   | R <sub>IN</sub>          |                    |                    |  | 5    |      | GΩ    |

- 20. Refer to ABSOLUTE MAXIMUM RATINGS and APPLICATION INFORMATION for Safe Operating Area.

- 21. Performance guaranteed over the indicated operating temperature range by design and/or characterization.

- 22. Power dissipation must be limited to prevent junction temperature from exceeding 150°C. See Absolute Maximum Ratings for more information.

## **ELECTRICAL CHARACTERISTICS AT V<sub>S</sub> = 36 V**

$T_A = 25^{\circ}\text{C}$ ;  $R_L \ge 10 \text{ k}\Omega$ ;  $V_{CM} = V_{OUT} = \text{mid-supply unless otherwise noted}$ . All limits are guaranteed by testing or statistical analysis. Boldface limits apply over the specified temperature range,  $T_A = -40^{\circ}\text{C}$  to 125°C. (Notes 20, 21)

| Parameter                            | Symbol            | Cond                                                          | litions                                                           | Min | Тур   | Max  | Unit               |

|--------------------------------------|-------------------|---------------------------------------------------------------|-------------------------------------------------------------------|-----|-------|------|--------------------|

| INPUT CHARACTERISTICS                |                   | •                                                             | •                                                                 |     | •     |      |                    |

| Differential Input Capacitance       | C <sub>ID</sub>   |                                                               |                                                                   |     | 1.5   |      | pF                 |

| Common Mode Input Capacitance        | C <sub>CM</sub>   |                                                               |                                                                   |     | 3.5   |      | pF                 |

|                                      |                   |                                                               | Vov. = Voo. + 0.2 V to                                            | 118 | 135   |      |                    |

|                                      |                   | NCx20071                                                      | $V_{CM} = V_{SS} + 0.2 \text{ V to}$<br>$V_{DD} - 1.35 \text{ V}$ | 95  |       |      |                    |

|                                      |                   |                                                               | $V_{CM} = V_{SS} + 0.2 \text{ V to}$                              | 120 | 145   |      |                    |

| Common Mode Rejection Ratio          | CMRR              | NCx20072                                                      | V <sub>DD</sub> – 1.35 V                                          | 95  |       |      | dB                 |

|                                      |                   | NCx20074                                                      | $V_{CM} = V_{SS} + 0.2 \text{ V to}$                              | 120 | 145   |      |                    |

|                                      |                   |                                                               | V <sub>DD</sub> – 1.35 V                                          | 85  |       |      |                    |

| OUTPUT CHARACTERISTICS               |                   |                                                               |                                                                   |     |       |      |                    |

| On and Learn Walter to Online        | Δ.                |                                                               |                                                                   | 98  | 120   |      | ·ID                |

| Open Loop Voltage Gain               | $A_{VOL}$         |                                                               | 88                                                                |     |       | dB   |                    |

| Output Coment Comehility (Nata 20)   |                   | Op amp sinking current                                        |                                                                   |     | 50    |      | A                  |

| Output Current Capability (Note 22)  | I <sub>O</sub>    | Op amp sou                                                    | Op amp sourcing current                                           |     | 65    |      | mA                 |

|                                      |                   |                                                               | NC::00074                                                         |     | 0.074 | 0.15 |                    |

|                                      |                   |                                                               | NCx20071                                                          |     |       | 0.22 |                    |

| Output Voltage High                  | \/                | Voltage output swing                                          | NCv20072                                                          |     | 0.074 | 0.10 | V                  |

|                                      | V <sub>ОН</sub>   | from positive rail                                            | NCx20072                                                          |     |       | 0.15 |                    |

|                                      |                   |                                                               | NC::20074                                                         |     | 0.074 | 0.10 |                    |

|                                      |                   | NCX20074                                                      | NCx20074                                                          |     |       | 0.12 |                    |

| Output Voltage Low                   | V                 | Valtage output out                                            | og from pogotivo roil                                             |     | 0.065 | 0.3  | \/                 |

| Output Voltage Low                   | V <sub>OL</sub>   | voltage output swir                                           | ng from negative rail                                             |     |       | 0.35 | V                  |

| AC CHARACTERISTICS                   |                   |                                                               |                                                                   |     |       |      |                    |

| Unity Gain Bandwidth                 | UGBW              | C <sub>L</sub> =                                              | 25 pF                                                             |     | 3     |      | MHz                |

| Slew Rate at Unity Gain              | SR                | $C_{L} = 20 \text{ pF}$                                       | $R_L = 2 k\Omega$                                                 |     | 2.4   |      | V/μs               |

| Phase Margin                         | $\phi_{\text{m}}$ | C <sub>L</sub> =                                              | 25 pF                                                             |     | 50    |      | 0                  |

| Gain Margin                          | A <sub>m</sub>    | C <sub>L</sub> =                                              | 25 pF                                                             |     | 14    |      | dB                 |

| Cottling Time                        |                   | $V_{O} = 10 \text{ Vpp},$<br>Gain = 1, C <sub>L</sub> = 20 pF | Settling time to 0.1%                                             |     | 3.2   |      | 0                  |

| Settling Time                        | t <sub>S</sub>    | Gain = 1, $C_L = 20 \text{ pF}$                               | Settling time to 0.01%                                            |     | 7     |      | μS                 |

| NOISE CHARACTERISTICS                |                   |                                                               |                                                                   |     |       |      |                    |

| Total Harmonic Distortion plus Noise | THD+N             | V <sub>IN</sub> = 28.5 Vpp,                                   | f = 1 kHz, Av = 1                                                 |     | 0.001 |      | %                  |

| Input Referred Voltage Noise         |                   | f = 1                                                         | kHz                                                               |     | 30    |      | nV/√ <del>Hz</del> |

| input Neieneu voltage Noise          | e <sub>n</sub>    | f = 10 kHz                                                    |                                                                   |     | 20    |      | 110/ 1172          |

| Input Referred Current Noise         | i <sub>n</sub>    | f = 1                                                         | kHz                                                               |     | 90    |      | fA/√ <del>Hz</del> |

<sup>20.</sup> Refer to ABSOLUTE MAXIMUM RATINGS and APPLICATION INFORMATION for Safe Operating Area.

<sup>21.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization.

<sup>22.</sup> Power dissipation must be limited to prevent junction temperature from exceeding 150°C. See Absolute Maximum Ratings for more information.

**ELECTRICAL CHARACTERISTICS AT V**<sub>S</sub> = 36 V  $T_A = 25^{\circ}\text{C}$ ;  $R_L \ge 10 \text{ k}\Omega$ ;  $V_{CM} = V_{OUT} = \text{mid}$ –supply unless otherwise noted. All limits are guaranteed by testing or statistical analysis. Boldface limits apply over the specified temperature range,  $T_A = -40^{\circ}\text{C}$  to 125°C. (Notes 20, 21)

| Parameter                      | Symbol          | Conditions |                      | Min | Тур | Max | Unit |

|--------------------------------|-----------------|------------|----------------------|-----|-----|-----|------|

| SUPPLY CHARACTERISTICS         |                 |            |                      |     |     |     |      |

| Dawar Cumply Dejection Datio   | DODD            | R No Load  |                      | 114 | 135 |     | ٩D   |

| Power Supply Rejection Ratio   | PSRR            |            |                      | 100 |     |     | dB   |

|                                |                 | NCx20071   | No load              |     | 480 | 700 |      |

|                                |                 | NCX20071   | No load              |     |     | 840 |      |

| Bower Supply Ouisesent Current |                 | NCv20072   | Der abannal na laad  |     | 465 | 570 | ^    |

| Power Supply Quiescent Current | I <sub>DD</sub> | NCx20072   | Per channel, no load |     |     | 700 | μΑ   |

|                                |                 | NCv20074   | Der abannal na laad  |     | 465 | 600 |      |

|                                |                 | NCx20074   | Per channel, no load |     |     | 700 |      |

<sup>20.</sup> Refer to ABSOLUTE MAXIMUM RATINGS and APPLICATION INFORMATION for Safe Operating Area.

<sup>21.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization.

<sup>22.</sup> Power dissipation must be limited to prevent junction temperature from exceeding 150°C. See Absolute Maximum Ratings for more information.

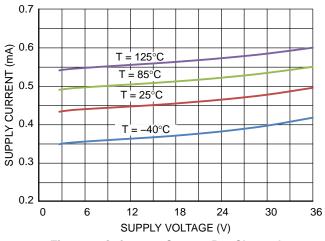

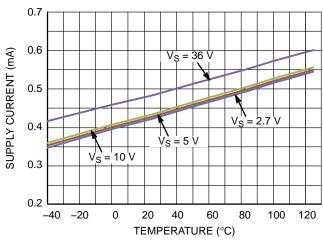

Figure 2. Quiescent Current Per Channel vs. Supply Voltage

Figure 3. Quiescent Current vs. Temperature

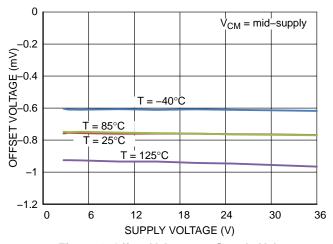

Figure 4. Offset Voltage vs. Supply Voltage

Figure 5. Input Offset Voltage vs. Common Mode Voltage

180

135

90

0 0 -45 DHASE

-90

-135

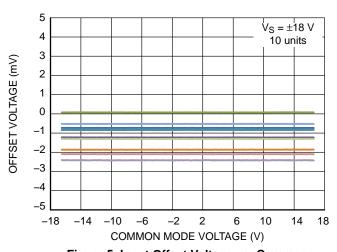

Figure 6. Input Offset Voltage vs. Common Mode Voltage

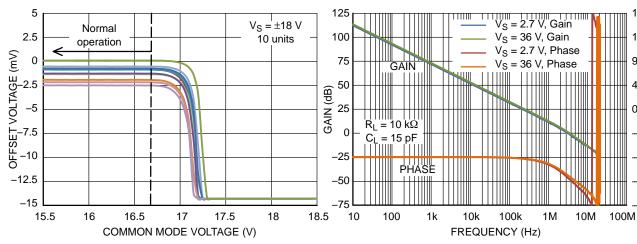

Figure 7. Gain and Phase vs. Frequency

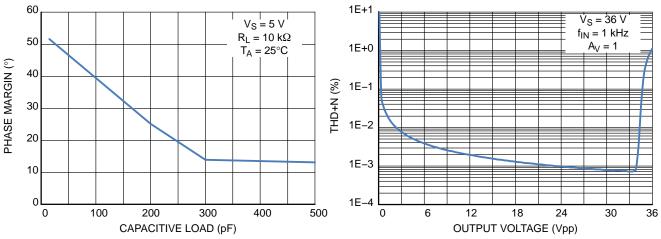

Figure 8. Phase Margin vs. Capacitive Load

Figure 9. THD+N vs. Output Voltage

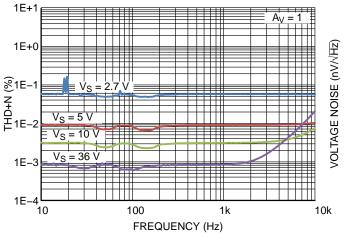

Figure 10. THD+N vs. Frequency

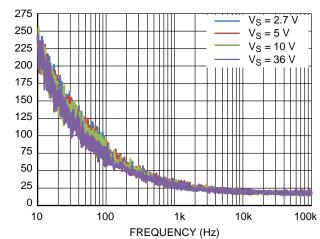

Figure 11. Input Voltage Noise vs. Frequency

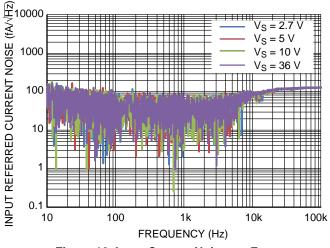

Figure 12. Input Current Noise vs. Frequency

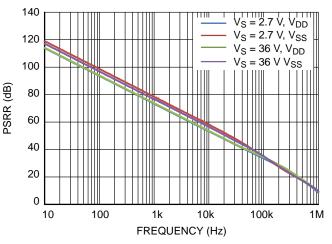

Figure 13. PSRR vs. Frequency

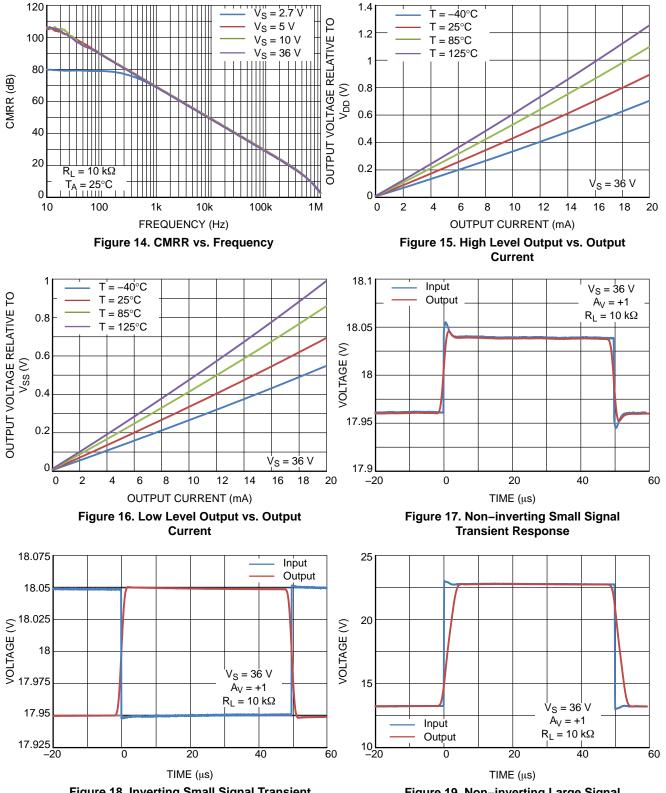

Figure 18. Inverting Small Signal Transient Response

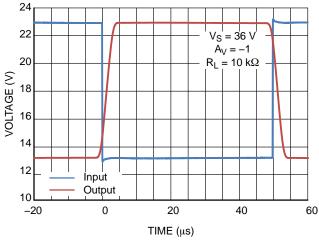

Figure 19. Non-inverting Large Signal Transient Response

Figure 20. Inverting Large Signal Transient Response

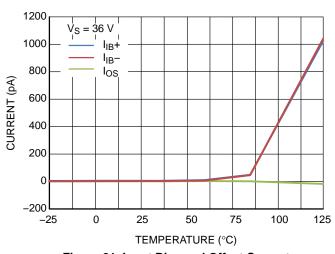

Figure 21. Input Bias and Offset Current vs.

Temperature

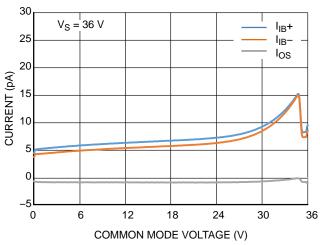

Figure 22. Input Bias Current vs. Common Mode Voltage

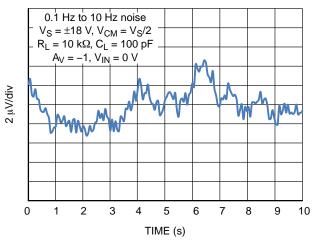

Figure 23. 0.1 Hz to 10 Hz Noise

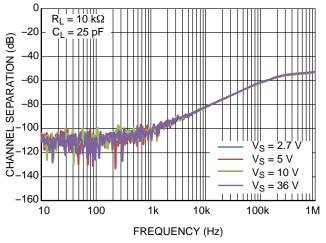

Figure 24. Channel Separation vs. Frequency

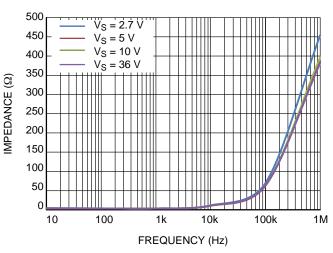

Figure 25. Open Loop Output Impedance

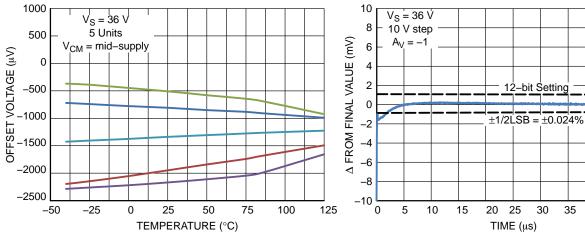

Figure 26. Offset Voltage vs. Temperature

Figure 27. Large Signal Settling Time

40

45

50

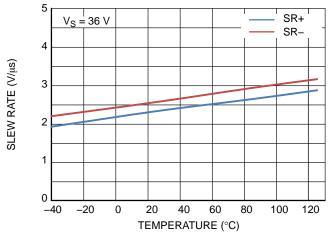

Figure 28. Slew Rate vs. Temperature

#### APPLICATIONS INFORMATION

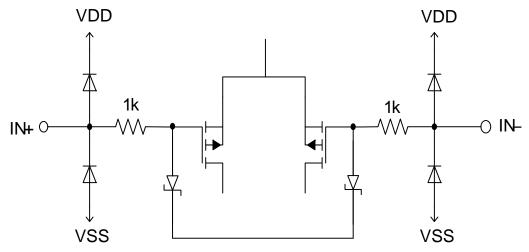

## **Input Circuit**

The NCS2007x input stage has a PMOS input pair and ESD protection diodes. The input pair is internally connected by back–to–back Zener diodes with a reverse voltage of 5.5 V. To protect the internal circuitry, the input current must be limited to 10 mA. When operating the

NCS2007x at differential voltages greater than  $V_{ID}=26~V$ , series resistors can be added externally to limit the input current flowing between the input pins. Adding 500  $\Omega$  resistors in series with the input prevents the current from exceeding 10 mA over the entire operating range up to 36 V.

Figure 29. Differential Input Pair

#### Output

The NCS2007x has a class AB output stage with rail-to-rail output swing.

High output currents can cause the junction temperature to exceed the 150°C absolute maximum rating. In the case of a short circuit where the output is connected to either supply rail, the amount of current the op amp can source and sink is described by the output current capability parameter

listed in the Electrical Characteristics. The junction temperature at a given power dissipation, P, can be calculated using the following formula:

$$T_J = T_A + P \times \theta_{JA}$$

The thermal resistance between junction and ambient,  $\theta_{JA}$ , is provided in the Thermal Information section of this datasheet.

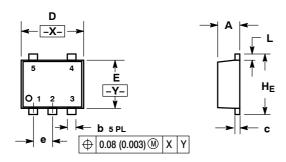

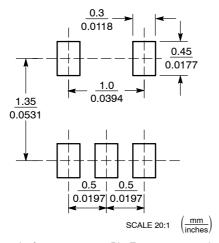

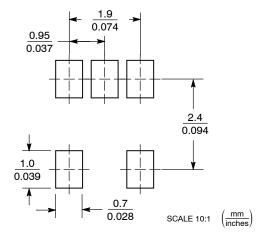

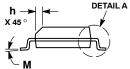

SOT-553, 5 LEAD CASE 463B ISSUE C

**DATE 20 MAR 2013**

### **RECOMMENDED SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETERS

3. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH

THICKNESS: MINIMUM LEAD THICKNESS IS THE MINIMUM

THICKNESS OF BASE MATERIAL.

|     | М    | ILLIMETE | RS   | INCHES |           |       |

|-----|------|----------|------|--------|-----------|-------|

| DIM | MIN  | NOM      | MAX  | MIN    | NOM       | MAX   |

| Α   | 0.50 | 0.55     | 0.60 | 0.020  | 0.022     | 0.024 |

| b   | 0.17 | 0.22     | 0.27 | 0.007  | 0.009     | 0.011 |

| С   | 0.08 | 0.13     | 0.18 | 0.003  | 0.005     | 0.007 |

| D   | 1.55 | 1.60     | 1.65 | 0.061  | 0.063     | 0.065 |

| E   | 1.15 | 1.20     | 1.25 | 0.045  | 0.047     | 0.049 |

| е   |      | 0.50 BSC |      |        | 0.020 BSC | )     |

| L   | 0.10 | 0.20     | 0.30 | 0.004  | 0.008     | 0.012 |

| He  | 1 55 | 1.60     | 1.65 | 0.061  | 0.063     | 0.065 |

### **GENERIC MARKING DIAGRAM\***

XX = Specific Device Code

M = Date Code

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

| STYLE 1:                                                                              | STYLE 2:                                                          | STYLE 3:                                                                      | STYLE 4:                                                                   | STYLE 5:                  |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------|

| PIN 1. BASE                                                                           | PIN 1. CATHODE                                                    | PIN 1. ANODE 1                                                                | PIN 1. SOURCE 1                                                            | PIN 1. ANODE              |

| 2. EMITTER                                                                            | 2. COMMON ANODE                                                   | 2. N/C                                                                        | 2. DRAIN 1/2                                                               | 2. EMITTER                |

| 3. BASE                                                                               | <ol><li>CATHODE 2</li></ol>                                       | 3. ANODE 2                                                                    | <ol><li>SOURCE 1</li></ol>                                                 | 3. BASE                   |

| 4. COLLECTOR                                                                          | <ol><li>CATHODE 3</li></ol>                                       | <ol><li>CATHODE 2</li></ol>                                                   | 4. GATE 1                                                                  | 4. COLLECTOR              |

| <ol><li>COLLECTOR</li></ol>                                                           | <ol><li>CATHODE 4</li></ol>                                       | <ol><li>CATHODE 1</li></ol>                                                   | 5. GATE 2                                                                  | <ol><li>CATHODE</li></ol> |

| STYLE 6: PIN 1. EMITTER 2 2. BASE 2 3. EMITTER 1 4. COLLECTOR 1 5. COLLECTOR 2/BASE 1 | STYLE 7: PIN 1. BASE 2. EMITTER 3. BASE 4. COLLECTOR 5. COLLECTOR | STYLE 8:<br>PIN 1. CATHODE<br>2. COLLECTOR<br>3. N/C<br>4. BASE<br>5. EMITTER | STYLE 9:<br>PIN 1. ANODE<br>2. CATHODE<br>3. ANODE<br>4. ANODE<br>5. ANODE |                           |

| DOCUMENT NUMBER: | 98AON11127D               | Electronic versions are uncontrolle                                  | '           |

|------------------|---------------------------|----------------------------------------------------------------------|-------------|

| STATUS:          | ON SEMICONDUCTOR STANDARD | accessed directly from the Document versions are uncontrolled except |             |

| NEW STANDARD:    |                           | "CONTROLLED COPY" in red.                                            |             |

| DESCRIPTION:     | SOT-553, 5 LEAD           |                                                                      | PAGE 1 OF 2 |

# DOCUMENT NUMBER: 98AON11127D

#### PAGE 2 OF 2

| ED STYLES 3-9. REQ. BY D. BARLOW ED NOMINAL VALUES AND UPDATED GENERIC MARKING DIAGRAM. REQ. ONG XIAO ATED DIMENSIONS D, E, AND HE. REQ. BY J. LETTERMAN. | 11 NOV 2003<br>27 MAY 2005<br>20 MAR 2013 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| ONG XIAO                                                                                                                                                  |                                           |

| ATED DIMENSIONS D, E, AND HE. REQ. BY J. LETTERMAN.                                                                                                       | 20 MAR 2013                               |

|                                                                                                                                                           |                                           |

|                                                                                                                                                           |                                           |

|                                                                                                                                                           |                                           |

|                                                                                                                                                           |                                           |

|                                                                                                                                                           |                                           |

|                                                                                                                                                           |                                           |

|                                                                                                                                                           |                                           |

|                                                                                                                                                           |                                           |

|                                                                                                                                                           |                                           |

|                                                                                                                                                           |                                           |

|                                                                                                                                                           |                                           |

|                                                                                                                                                           |                                           |

|                                                                                                                                                           |                                           |

|                                                                                                                                                           |                                           |

|                                                                                                                                                           |                                           |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

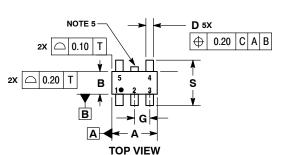

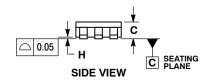

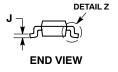

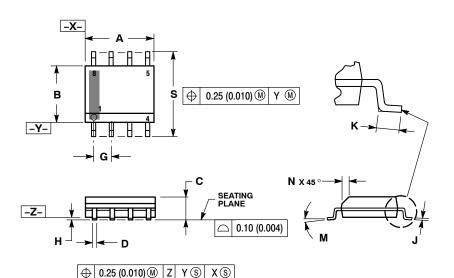

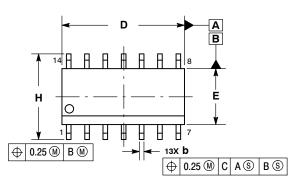

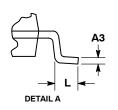

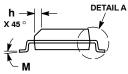

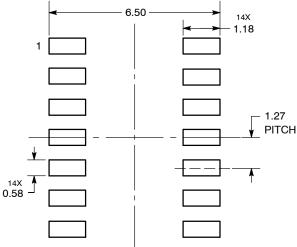

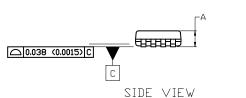

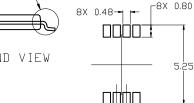

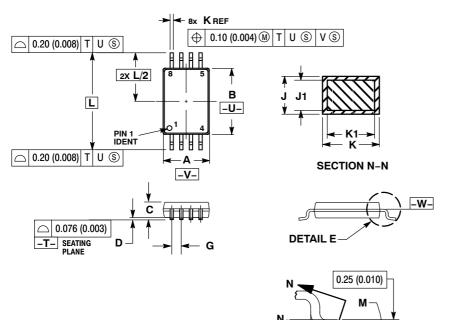

TSOP-5 **CASE 483 ISSUE N**

**DATE 12 AUG 2020**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME

- CONTROLLING DIMENSION: MILLIMETERS.

MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH

THICKNESS. MINIMUM LEAD THICKNESS IS THE

MINIMUM THICKNESS OF BASE MATERIAL.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSION A. OPTIONAL CONSTRUCTION: AN ADDITIONAL

- TRIMMED LEAD IS ALLOWED IN THIS LOCATION. TRIMMED LEAD NOT TO EXTEND MORE THAN 0.2 FROM BODY.

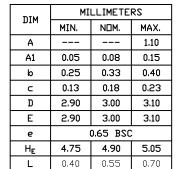

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   | 2.85        | 3.15 |  |  |

| В   | 1.35        | 1.65 |  |  |

| С   | 0.90        | 1.10 |  |  |

| D   | 0.25        | 0.50 |  |  |

| G   | 0.95        | BSC  |  |  |

| Н   | 0.01        | 0.10 |  |  |

| J   | 0.10        | 0.26 |  |  |

| K   | 0.20        | 0.60 |  |  |

| М   | 0 °         | 10 ° |  |  |

| S   | 2.50        | 3.00 |  |  |

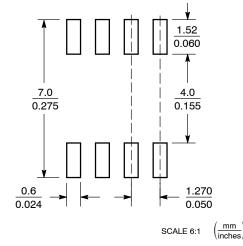

## **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

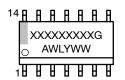

### **GENERIC MARKING DIAGRAM\***

XXX = Specific Device Code XXX = Specific Device Code

= Assembly Location

= Date Code = Year = Pb-Free Package

= Work Week W

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

| DOCUMENT NUMBER: | 98ARB18753C | Electronic versions are uncontrolled except when accessed directly from Printed versions are uncontrolled except when stamped "CONTROLLED" |             |

|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | TSOP-5      |                                                                                                                                            | PAGE 1 OF 1 |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

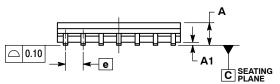

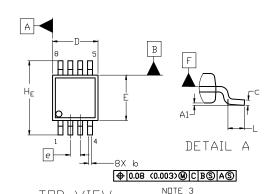

SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |      | INCHES    |       |  |

|-----|-------------|------|-----------|-------|--|

| DIM | MIN         | MAX  | MIN       | MAX   |  |

| Α   | 4.80        | 5.00 | 0.189     | 0.197 |  |