# Notification about the transfer of the semiconductor business

The semiconductor business of Panasonic Corporation was transferred on September 1, 2020 to Nuvoton Technology Corporation (hereinafter referred to as "Nuvoton"). Accordingly, Panasonic Semiconductor Solutions Co., Ltd. became under the umbrella of the Nuvoton Group, with the new name of Nuvoton Technology Corporation Japan (hereinafter referred to as "NTCJ").

In accordance with this transfer, semiconductor products will be handled as NTCJ-made products after September 1, 2020. However, such products will be continuously sold through Panasonic Corporation.

Publisher of this Document is NTCJ.

If you would find description "Panasonic" or "Panasonic semiconductor solutions", please replace it with NTCJ.

\* Except below description page

"Request for your special attention and precautions in using the technical information and semiconductors described in this book"

Nuvoton Technology Corporation Japan

# 3-ch. LED Driver for Illumination

## FEATURES

- I<sup>2</sup>C Interface (Slave address is switchable.)

- Built-in 3-ch. LED Driver Circuit

- ( Max Current Selectable [63.75 mA / 31.875 mA / 25.50 mA / 12.75 mA] )

- 2.4 MHz OSC

- 12 pin Wafer level chip size package (WLCSP)

## DESCRIPTION

AN30259C has 3-ch. LED Driver, suitable for RGB illumination. By synchronous clock function, simultaneous LED turn ON/OFF operation of up to 4 ICs can be achieved.

## APPLICATIONS

- Mobile, Wearable

- Smart Speaker

- PCs

- Game Consoles

- Home Appliances etc.

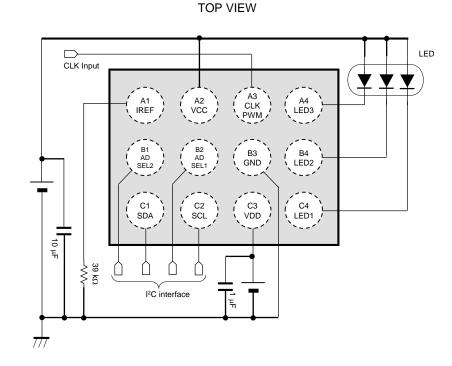

## TYPICAL APPLICATION

Note:

The application circuit is an example. The operation of the mass production set is not guaranteed. Sufficient evaluation and verification is required in the design of the mass production set. The Customer is fully responsible for the incorporation of the above illustrated application circuit in the design of the equipment.

# **ORDERING INFORMATION**

| Order Number | Feature                        | Package      | Packing Form  |

|--------------|--------------------------------|--------------|---------------|

| AN30259C-PR  | LED Driver IC for Illumination | 12 pin WLCSP | Emboss Taping |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      | Symbol                                                                                                   | Rating        | Unit | Note |

|--------------------------------|----------------------------------------------------------------------------------------------------------|---------------|------|------|

| Supplyvoltage                  | VCC <sub>MAX</sub>                                                                                       | 7.0           | V    | *1   |

| Supply voltage                 | VDD <sub>MAX</sub>                                                                                       | 4.6           | V    | *1   |

| Operating ambience temperature | T <sub>opr</sub>                                                                                         | -30 to + 85   | °C   | *2   |

| Operating junction temperature | Τ <sub>j</sub>                                                                                           | - 30 to + 125 | °C   | *2   |

| Storage temperature            | T <sub>stg</sub>                                                                                         | – 55 to + 125 | °C   | *2   |

| Input Voltage Range            | V <sub>ADSEL1</sub> , V <sub>ADSEL2</sub> ,<br>V <sub>SCL</sub> , V <sub>SDA</sub> , V <sub>CLKPWM</sub> | - 0.3 to 4.3  | V    | _    |

| Output Voltage Range           | V <sub>led1</sub> , V <sub>led2</sub> , V <sub>led3</sub>                                                | - 0.3 to 6.5  | V    | _    |

| ESD                            | НВМ                                                                                                      | 2.0           | kV   | _    |

Note: This product may sustain permanent damage if subjected to conditions higher than the above stated absolute maximum rating. This rating is the maximum rating and device operating at this range is not guaranteed as it is higher than our stated recommended operating range. When subjected under the absolute maximum rating for a long time, the reliability of the product may be affected.

\*1: VCC<sub>MAX</sub> = VCC, VDD<sub>MAX</sub> = VDD, the values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

\*2: Except for operating ambient temperature, operating junction temperature and storage temperature, all ratings are for T<sub>a</sub> = 25°C.

## POWER DISSIPATION RATING

| PACKAGE                                      | $\theta_{JA}$ | Р <sub>D</sub> (Та=25 °С) | Р <sub>D</sub> (Та=85 °С) |

|----------------------------------------------|---------------|---------------------------|---------------------------|

| 12 pin Wafer Level Chip Size Package (WLCSP) | 537.1 °C /W   | 0.186 W                   | 0.074 W                   |

Note: For the actual usage, please refer to the P<sub>D</sub>-Ta characteristics diagram in the package specification, follow the power supply voltage, load and ambient temperature conditions to ensure that there is enough margin and the thermal design does not exceed the allowable value.

# CAUTION

Although this IC has built-in ESD protection circuit, it may still sustain permanent damage if not handled properly. Therefore, proper ESD precautions are recommended to avoid electrostatic damage to the MOS gates

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter            | Symbol                                                                                                   | Min.  | Тур. | Max.                  | Unit | Note |

|----------------------|----------------------------------------------------------------------------------------------------------|-------|------|-----------------------|------|------|

|                      | V <sub>CC</sub>                                                                                          | 3.1   | 3.7  | 6.0                   | V    | _    |

| Supply voltage range | V <sub>DD</sub>                                                                                          | 1.7   | 1.85 | 3.2                   | V    |      |

| Input Voltage Range  | V <sub>ADSEL1</sub> , V <sub>ADSEL2</sub> ,<br>V <sub>SCL</sub> , V <sub>SDA</sub> , V <sub>CLKPWM</sub> | - 0.3 | _    | V <sub>DD</sub> + 0.3 | V    | *1   |

| Output Voltage Range | $V_{LED1},V_{LED2},V_{LED3}$                                                                             | - 0.3 |      | V <sub>CC</sub> + 0.3 | V    | *1   |

Note: Voltage values, unless otherwise specified, are with respect to GND. GND is voltage for GND.

$V_{\text{DD}}$  is voltage for VDD.  $V_{\text{CC}}$  is voltage for VCC.

\*1 : (  $V_{\text{DD}}$  + 0.3 ) V must not exceed 4.6 V. (  $V_{\text{CC}}$  + 0.3 ) V must not exceed 7 V.

# **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 3.6 V,  $V_{DD}$  = 1.8 V Note:  $T_a$  = 25 °C ± 2 °C unless otherwise specified.

| Parameter                                             | Symbol Condition   |                                                                                                              |       | Limits |       |      | Note |  |

|-------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------|-------|--------|-------|------|------|--|

|                                                       | Symbol             | Condition                                                                                                    | Min   | Тур    | Max   | Unit | NOte |  |

| Current consumption                                   |                    |                                                                                                              |       |        |       |      |      |  |

| Current consumption 1<br>OFF mode                     | I <sub>CC1</sub>   | $V_{DD} = 0 V$                                                                                               |       | 0      | 2     | μA   | -    |  |

| Current consumption 2<br>OFF mode                     | I <sub>CC2</sub>   | V <sub>DD</sub> = 1.8 V                                                                                      | _     | 1      | 5     | μA   | -    |  |

| Current consumption 3<br>LED lighting mode            | I <sub>CC3</sub>   | $I_{LED1 \text{ to } 3} = 25.50 \text{ mA setting}$<br>All LED = ON                                          |       | 0.6    | 1.0   | mA   | _    |  |

| LED Driver                                            | ł                  |                                                                                                              | i.    |        | :     |      |      |  |

| Off time leak current                                 | I <sub>LEAK</sub>  | Off setting<br>$V_{LED1 \text{ to } 3} = 6.0 \text{ V}$                                                      |       |        | 1.0   | μA   |      |  |

| Minimum setting current value 1                       | I <sub>MIN1</sub>  | IMAX[1:0] = 01,<br>V <sub>LED1 to 3</sub> = 1.0 V                                                            | 0.05  | 0.10   | 0.15  | mA   | _    |  |

| Minimum setting current value 2                       | I <sub>MIN2</sub>  | IMAX[1:0] = 01,<br>V <sub>LED1 to 3</sub> = 1.0 V                                                            | 0.736 | 0.80   | 0.864 | mA   | _    |  |

| Maximum setting current value                         | I <sub>MAX</sub>   | IMAX[1:0] = 01,<br>V <sub>LED1 to 3</sub> = 1.0 V                                                            | 23.46 | 25.50  | 27.54 | mA   | _    |  |

| Current step                                          | I <sub>STEP</sub>  | IMAX[1:0] = 01,<br>V <sub>LED1 to 3</sub> = 1.0 V                                                            | 0.00  | 0.10   | 0.18  | mA   | _    |  |

| Minimum voltage for retainable constant current value | V <sub>SAT</sub>   | IMAX[1:0] = 01,<br>Terminal minimum voltage of<br>LED1 to 3 becoming 85% of the<br>LED current value in 1 V. |       | 0.2    | 0.4   | v    |      |  |

| Error between channels                                | I <sub>MATCH</sub> | 12.80 mA setting,<br>$V_{LED1 to 3} = 1.0 V$                                                                 | -5    | _      | 5     | %    |      |  |

| nternal oscillator                                    | 1                  | 1                                                                                                            |       |        | !     |      | ļ    |  |

| Oscillation frequency                                 | f <sub>OSC</sub>   | _                                                                                                            | 1.92  | 2.40   | 2.88  | MHz  | _    |  |

# **Panasonic**

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_{CC} = 3.6 \text{ V}, \text{ V}_{DD} = 1.8 \text{ V}$

Note:  $T_a = 25 \text{ °C} \pm 2 \text{ °C}$  unless otherwise specified.

| Poromotor                       | Symbol                  | Condition                                                |                          | Limits |                          |      | Note |

|---------------------------------|-------------------------|----------------------------------------------------------|--------------------------|--------|--------------------------|------|------|

| Parameter                       | Symbol                  | Condition                                                | Min                      | Тур    | Max                      | Unit | NOTE |

| SCL, SDA                        |                         |                                                          |                          |        |                          |      |      |

| High-level input voltage range  | V <sub>IH1</sub>        | Voltage which recognized that SDA and SCL are High-level | $V_{DD} \times 0.7$      | _      | V <sub>DD</sub><br>+ 0.5 | V    | *1   |

| Low-level input voltage range   | V <sub>IL1</sub>        | Voltage which recognized that SDA and SCL are Low-level  | - 0.5                    |        | $V_{DD} \times 0.3$      | V    | *1   |

| High-level input current        | I <sub>IH1</sub>        | $V_{SDA}$ , $V_{SCL}$ = 1.8 V                            | _                        | 0      | 1                        | μA   | _    |

| Low-level input current         | $I_{IL1}$               | $V_{SDA}$ , $V_{SCL} = 0$ V                              | —                        | 0      | 1                        | μA   | _    |

| Low-level output voltage1 (SDA) | V <sub>OL1H</sub>       | $I_{SDA} = 3 \text{ mA}, V_{DD} > 2 \text{ V}$           | 0                        | —      | 0.4                      | V    | _    |

| Low-level output voltage2 (SDA) | V <sub>OL1L</sub>       | $I_{SDA}$ = 3 mA, $V_{DD}$ < 2 V                         | 0                        |        | $0.2 \times V_{DD}$      | V    | _    |

| SCL clock frequency             | f <sub>SCL</sub>        | _                                                        | 0                        | _      | 400                      | kHz  | _    |

| CLKPWM                          | I                       | 1                                                        |                          |        |                          |      |      |

| High-level input voltage range  | ange V <sub>IH2</sub> — |                                                          | V <sub>DD</sub><br>× 0.7 |        | V <sub>DD</sub><br>+ 0.2 | V    | _    |

| Low-level input voltage range   | V <sub>IL2</sub>        | _                                                        | - 0.2                    |        | $V_{DD} \times 0.3$      | V    | _    |

| Pin pull down resistance value  | R <sub>PD2</sub>        | _                                                        | 0.5                      | 1.0    | 2.0                      | MΩ   | _    |

| High-level output voltage       | V <sub>OH2</sub>        | $I_{CLKPWM} = -2 \text{ mA}$                             | V <sub>DD</sub><br>× 0.8 |        | V <sub>DD</sub><br>+ 0.2 | V    | _    |

| Low-level output voltage        | V <sub>OL2</sub>        | I <sub>CLKPWM</sub> = 2 mA                               | -0.2                     |        | $V_{DD} \times 0.2$      | V    | _    |

| ADSEL1, ADSEL2                  |                         |                                                          | -                        |        |                          |      |      |

| High-level input voltage range  | V <sub>IH3</sub>        | _                                                        | V <sub>DD</sub><br>× 0.7 | _      | V <sub>DD</sub><br>+ 0.2 | V    | _    |

| Low-level input voltage range   | V <sub>IL3</sub>        | _                                                        | - 0.2                    | _      | $V_{DD} \times 0.3$      | V    | _    |

| High-level input current        | I <sub>IH3</sub>        | V <sub>ADSEL1, 2</sub> = 1.8 V                           | _                        | 0      | 1                        | μA   | —    |

| Low-level input current         | I <sub>IL3</sub>        | $V_{ADSEL1, 2} = 0 V$                                    | _                        | 0      | 1                        | μA   | _    |

Note:\*1: The input threshold voltage of I<sup>2</sup>C bus (Vth) is linked to V<sub>DD</sub> (I<sup>2</sup>C bus I/O stage supply voltage).

In case the pull-up voltage is not  $V_{DD}$ , the threshold voltage (Vth) is fixed to (( $V_{DD}$  / 2) ± (Schmitt width) / 2) and High-level, Low-level of input voltage are not specified.

In this case, pay attention to Low-level (max.) value (V $_{\rm ILmax}).$

It is recommended that the pull-up voltage of  $I^2C$  bus is set to the  $I^2C$  bus I/O stage supply voltage (V<sub>DD</sub>).

## **ELECTRICAL CHARACTERISTICS (continued)**

$V_{CC}$  = 3.6 V,  $V_{DD}$  = 1.8 V Note:  $T_a$  = 25 °C ± 2 °C unless otherwise specified.

|           | Perameter                                                      |                  | Symbol Condition |     | Limits |     |      | Note |

|-----------|----------------------------------------------------------------|------------------|------------------|-----|--------|-----|------|------|

| Parameter |                                                                | Symbol           |                  | Min | Тур    | Max | Unit | Note |

| CL        | KPWM                                                           |                  |                  |     |        |     |      |      |

|           | External PWM operation mode<br>Possible input high pulse width | W <sub>PWM</sub> | _                |     | 2.5    |     | μS   | *2   |

Note: \*2 : Typical design value

# **ELECTRICAL CHARACTERISTICS (continued)**

$\label{eq:V_CC} \begin{array}{l} V_{CC}=3.6~V,~V_{DD}=1.8~V\\ \mbox{Note:} \quad T_a=25~^\circ\mbox{C}\pm2~^\circ\mbox{C}~\mbox{unless otherwise specified.} \end{array}$

| Parameter                                        | Symbol                                     | Condition                                                                                                              |                            | Limits |     | Unit | Note |

|--------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------|--------|-----|------|------|

| Falameter                                        | Symbol                                     | Condition                                                                                                              | Min                        | Тур    | Max | Unit | Note |

| <sup>2</sup> C bus (Internal I/O stage characte  | C bus (Internal I/O stage characteristics) |                                                                                                                        |                            |        |     |      |      |

| Input voltage hysteresis (1)                     | V <sub>hys1</sub>                          | SCL, SDA hysteresis voltage<br>$V_{DD} > 2 V$                                                                          |                            | —      | _   | v    | *3   |

| Input voltage hysteresis (2)                     | V <sub>hys2</sub>                          | SCL, SDA hysteresis voltage<br>V <sub>DD</sub> < 2 V                                                                   | $0.1 \times V_{DD}$        | _      |     | v    | *3   |

| Output fall time from $V_{IHmin}$ to $V_{ILmax}$ | t <sub>of</sub>                            | Bus capacitance : 10 pF to<br>400pF<br>$I_P \le 6 \text{ mA} (V_{OLmax} = 0.6 \text{ V})$<br>$I_P$ : Max. sink current | 20 +<br>0.1×C <sub>b</sub> |        | 250 | ns   | *3   |

| Spike pulse width kept down by input filter      | t <sub>sp</sub>                            | _                                                                                                                      | 0                          | _      | 50  | ns   | *3   |

| I/O pin capacitance                              | C <sub>i</sub>                             |                                                                                                                        | —                          | _      | 10  | pF   | *3   |

Notes: \*3 : These are values checked by design but not production tested.

# Panasonic

## **ELECTRICAL CHARACTERISTICS (continued)**

$V_{CC}$  = 3.6 V,  $V_{DD}$  = 1.8 V Note:  $T_a$  = 25 °C ± 2 °C unless otherwise specified.

|                  | Desembles                                                                   | Symphol             | Condition                                                      |                            | Limits |     | l lmit | Note |

|------------------|-----------------------------------------------------------------------------|---------------------|----------------------------------------------------------------|----------------------------|--------|-----|--------|------|

|                  | Parameter                                                                   | Symbol              | Condition                                                      | Min                        | Тур    | Max | Unit   | Note |

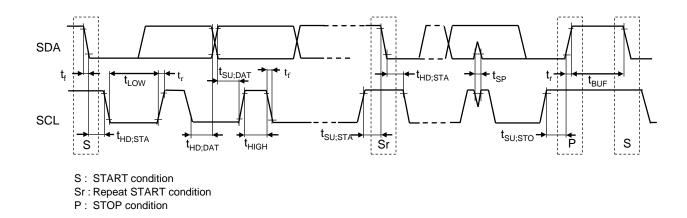

| I <sup>2</sup> C | bus (Bus line specifications)                                               |                     |                                                                |                            |        |     |        |      |

|                  | Hold duration (recursive) t <sub>HD:STA</sub> After t <sub>H</sub> pulse is |                     | After t <sub>HD:STA,</sub> the first clock pulse is generated. | 0.6                        | —      | _   | μS     | *3,4 |

|                  | SCL clock "L" duration                                                      | t <sub>LOW</sub>    | _                                                              | 1.3                        |        | _   | μS     | *3,4 |

|                  | SCL clock "H" duration                                                      | t <sub>HIGH</sub>   | —                                                              | 0.6                        | —      | _   | μS     | *3,4 |

|                  | Recursive "START" condition setting time                                    | t <sub>SU:STA</sub> | _                                                              | 0.6                        | _      | _   | μS     | *3,4 |

|                  | Data hold time                                                              | t <sub>HD:DAT</sub> | _                                                              | 0                          |        | 0.9 | μS     | *3,4 |

|                  | Data setup time                                                             | t <sub>SU:DAT</sub> | _                                                              | 100                        |        | _   | ns     | *3,4 |

|                  | SDA, SCL signal rise up time                                                | t <sub>r</sub>      | _                                                              | 20 +<br>0.1×C <sub>b</sub> | —      | 300 | ns     | *3,4 |

|                  | SDA, SCL signal fall time                                                   | t <sub>f</sub>      | _                                                              | 20 +<br>0.1×C <sub>b</sub> | _      | 300 | ns     | *3,4 |

|                  | Setup time under "STOP" condition                                           | t <sub>SU:STO</sub> |                                                                | 0.6                        | _      |     | μS     | *3,4 |

|                  | Bus free time between under<br>"STOP" condition and "START"<br>condition    | t <sub>BUF</sub>    | _                                                              | 1.3                        | _      |     | μS     | *3,4 |

|                  | Capacitive load for each bus line                                           | $C_{b}$             | _                                                              | _                          | _      | 400 | pF     | *3,4 |

|                  | Noise margin of each connection device at Low-level                         | V <sub>nL</sub>     | _                                                              | $0.1 \times V_{DD}$        |        |     | V      | *3,4 |

|                  | Noise margin of each connection device at High-level                        | $V_{nH}$            |                                                                | $0.2 \times V_{DD}$        |        |     | V      | *3,4 |

Note: \*3: These are values checked by design but not production tested.

\*4: The timing of Fast-mode devices in I<sup>2</sup>C-bus is specified as follows. All values referred to V<sub>IHmin</sub> and V<sub>ILmax</sub> level.

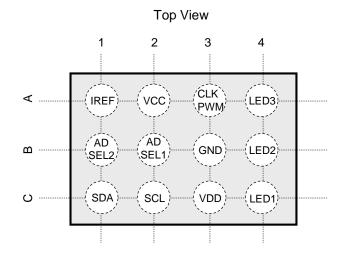

## **PIN CONFIGURATION**

# **PIN FUNCTIONS**

| Pin No. | Pin name | Туре         | Description                                                                                                       |

|---------|----------|--------------|-------------------------------------------------------------------------------------------------------------------|

| A1      | IREF     | Output       | Resistor connection pin for setting constant current value                                                        |

| A2      | VCC      | Power Supply | Power supply pin for LED Circuit                                                                                  |

| A3      | CLKPWM   | Input/Output | Reference clock Input / Output pin<br>PWM signal input pin to control LED brightness by the external pulse signal |

| A4      | LED3     | Output       | LED3 output pin                                                                                                   |

| B1      | ADSEL2   | Input        | I <sup>2</sup> C Interface slave address switch pin 2                                                             |

| B2      | ADSEL1   | Input        | I <sup>2</sup> C Interface slave address switch pin 1                                                             |

| B3      | GND      | Ground       | Ground pin                                                                                                        |

| B4      | LED2     | Output       | LED2 output pin                                                                                                   |

| C1      | SDA      | Input/Output | I <sup>2</sup> C interface data Input / Output pin                                                                |

| C2      | SCL      | Input        | I <sup>2</sup> C interface clock input pin                                                                        |

| C3      | VDD      | Power Supply | Power supply pin for interface                                                                                    |

| C4      | LED1     | Output       | LED1 output pin                                                                                                   |

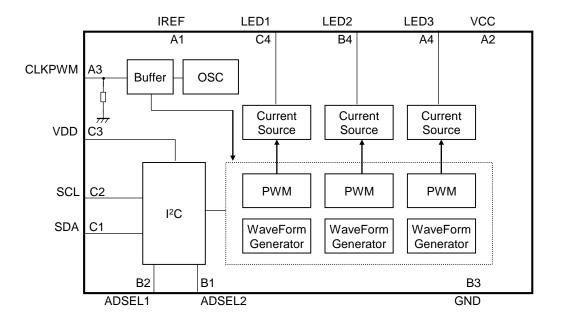

# FUNCTIONAL BLOCK DIAGRAM

Note: This block diagram is for explaining functions. Part of the block diagram may be omitted, or it may be simplified.

## OPERATION

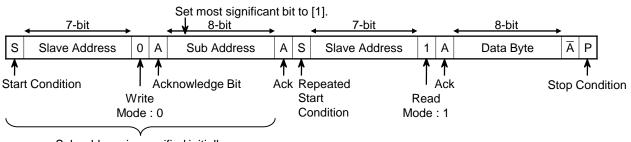

#### 1. I<sup>2</sup>C-bus Interface

- 1) Basic Rules

- This IC, I<sup>2</sup>C-bus, is designed to correspond to the Standard-mode (100 kbps) and Fast-mode(400 kbps) devices in the version 2.1 of NXP's specification. However, it does not correspond to the H<sub>S</sub>-mode (to 3.4 Mbps).

- This IC will be operated as a slave device in the I<sup>2</sup>C-bus system. This IC will not operate as a master device.

- The program operation check of this IC has not been conducted on the multi-master bus system and the mixspeed bus system, yet. The connected confirmation of this IC to the CBUS receiver also has not been checked. Please confirm with our company if it will be used in these mode systems. The I<sup>2</sup>C is the brand of NXP.

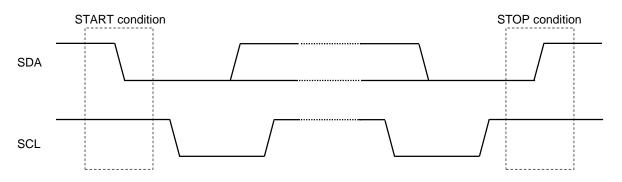

- 2) START and STOP conditions

A High to Low transition on the SDA line while SCL is High is one such unique case. This situation indicates START condition. A Low to High transition on the SDA line while SCL is High defines STOP condition. START and STOP conditions are always generated by the master. After START condition occurs, the bus will be busy. The bus is considered to be free again a certain time after the STOP condition.

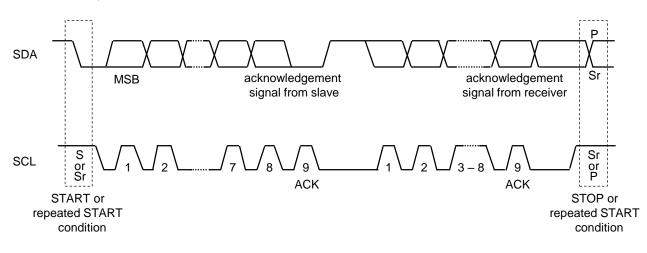

3) Transferring Data

Every byte put on the SDA line must be 8-bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first.

# AN30259C

## **OPERATION** (continued)

#### 1. I<sup>2</sup>C-bus Interface (continued)

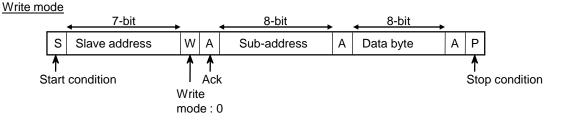

4) Data format

Slave address can be switched by ADSEL1, ADSEL2 pin connections. The chart on the right shows the slave address of this product.

| ADSEL2       | ADSEL1       | Slave address  |  |  |  |

|--------------|--------------|----------------|--|--|--|

| Low (Ground) | Low (Ground) | 30 h (0110000) |  |  |  |

| Low (Ground) | High (VDD)   | 31 h (0110001) |  |  |  |

| High (VDD)   | Low (Ground) | 32 h (0110010) |  |  |  |

| High (VDD)   | High (VDD)   | 33 h (0110011) |  |  |  |

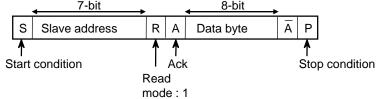

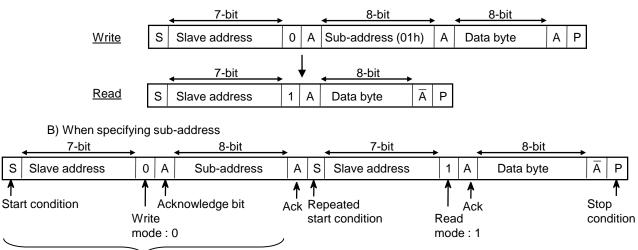

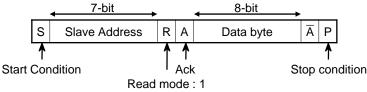

#### Read mode

A) When sub-address is not assigned.

When data is read without assigning sub-address, it is possible to read the value of sub-address specified in Write mode immediately before.

Ex) When writing data into address and reading data from "01 h"

Sub-address should be assigned first.

#### 1. I<sup>2</sup>C-bus Interface (continued)

- 4) Data format (continued)

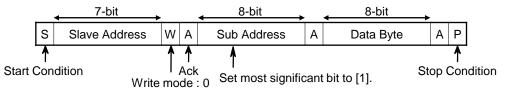

- Continuous Write mode

When using the continuous Write mode, the most significant bit of Sub address should be set to [1].

Ex)  $05h \rightarrow 85h$ ,  $11h \rightarrow 91h$

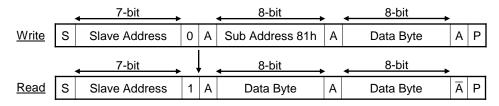

- Continuous Read mode

- A) When Sub address is not specified

When the most significant bit specified in the last Write mode is [1], it is possible to perform the continuous Read mode operation directly after it.

Ex) Case where data is read from Address 01h after data is written to Address 01h

B) When Sub address is specified

Sub address is specified initially

## 2. Register map

| Sub         | -   | Register |                |                             |            |                         | Data           |         |          |         |

|-------------|-----|----------|----------------|-----------------------------|------------|-------------------------|----------------|---------|----------|---------|

| Addr<br>ess | R/W | Name     | D7             | D6                          | D5         | D4                      | D3             | D2      | D1       | D0      |

| 00h         | W   | SRESET   |                | _                           |            |                         | _              |         | _        | SRESET  |

| 01h         | R/W | LEDON    | _              | LED3MD                      | LED2MD     | LED1MD                  | _              | LED3ON  | LED2ON   | LED1ON  |

| 02h         | R/W | SEL      | IMA            | X [1:0]                     | IOEN       | CLKDIR                  | EXTPWM         | DLYSEL3 | DLYSEL2  | DLYSEL1 |

| 03h         | R/W | LED1CC   |                |                             |            | LED                     | 01CC [7:0]     |         |          |         |

| 04h         | R/W | LED2CC   |                |                             |            | LED                     | 02CC [7:0]     |         |          |         |

| 05h         | R/W | LED3CC   |                |                             |            | LED                     | 03CC [7:0]     |         |          |         |

| 06h         | R/W | LED1SLP  |                | SLP1                        | TT2 [3:0]  |                         |                | SLP1T   | Г1 [3:0] |         |

| 07h         | R/W | LED2SLP  |                | SLP2                        | TT2 [3:0]  |                         |                | SLP2T   | Г1 [3:0] |         |

| 08h         | R/W | LED3SLP  |                | SLP3                        | TT2 [3:0]  |                         |                | SLP3T   | Г1 [3:0] |         |

| 09h         | R/W | LED1CNT1 |                | DUTYN                       | /AX1 [3:0] |                         |                | DUTYMI  | D1 [3:0] |         |

| 0Ah         | R/W | LED1CNT2 |                | DELA                        | AY1 [3:0]  |                         |                | DUTYMI  | N1 [3:0] |         |

| 0Bh         | R/W | LED1CNT3 |                | SLP1                        | DT2 [3:0]  |                         |                | SLP1D   | T1 [3:0] |         |

| 0Ch         | R/W | LED1CNT4 |                | SLP1                        | DT4 [3:0]  |                         |                | SLP1D   | T3 [3:0] |         |

| 0Dh         | R/W | LED2CNT1 |                | DUTYN                       | /AX2 [3:0] |                         |                | DUTYMI  | D2 [3:0] |         |

| 0Eh         | R/W | LED2CNT2 |                | DELAY2 [3:0]                |            |                         |                | DUTYMI  | N2 [3:0] |         |

| 0Fh         | R/W | LED2CNT3 |                | SLP2                        | DT2 [3:0]  |                         |                | SLP2D   | T1 [3:0] |         |

| 10h         | R/W | LED2CNT4 |                | SLP2                        | DT4 [3:0]  |                         |                | SLP2D   | T3 [3:0] |         |

| 11h         | R/W | LED3CNT1 | DUTYMAX3 [3:0] |                             |            |                         | DUTYMID3 [3:0] |         |          |         |

| 12h         | R/W | LED3CNT2 |                | DELAY3 [3:0] DUTYMIN3 [3:0] |            |                         |                |         |          |         |

| 13h         | R/W | LED3CNT3 |                | SLP3                        | DT2 [3:0]  | DT2 [3:0] SLP3DT1 [3:0] |                |         |          |         |

| 14h         | R/W | LED3CNT4 |                | SLP3                        | DT4 [3:0]  |                         |                | SLP3D   | T3 [3:0] |         |

Note: Read value in " — " is [0].

## 3. Register map details

| Registe | er Name       |    |    |    | SRE | RESET |    |    |        |  |  |

|---------|---------------|----|----|----|-----|-------|----|----|--------|--|--|

| Address | R / W<br>mode | D7 | D6 | D5 | D4  | D3    | D2 | D1 | D0     |  |  |

| 00 h    | W             | —  |    |    |     |       |    | —  | SRESET |  |  |

| Default | 00 h          | 0  | 0  | 0  | 0   | 0     | 0  | 0  | 0      |  |  |

#### D0 : Software reset pin

[0] : Normal condition ( default )

[1] : Reset (Reset all the other register and returns to Low automatically)

## 3. Register map details (continued)

| Registe | r Name        |    | LEDON  |        |        |    |        |        |        |  |  |  |  |

|---------|---------------|----|--------|--------|--------|----|--------|--------|--------|--|--|--|--|

| Address | R / W<br>mode | D7 | D7 D6  |        | D4     | D3 | D2     | D1     | D0     |  |  |  |  |

| 01 h    | R/W           | —  | LED3MD | LED2MD | LED1MD | —  | LED3ON | LED2ON | LED1ON |  |  |  |  |

| Default | 00 h          | 0  | 0      | 0      | 0      | 0  | 0      | 0      | 0      |  |  |  |  |

#### D6 : LED3MD LED3 lighting mode setting

[0] : LED3 constant current mode ( default )

- [1] : LED3 slope mode

- D5 : LED2MD LED2 lighting mode setting

- [0] : LED2 constant current mode ( default )

- [1] : LED2 slope mode

- D4 : LED1MD LED1 lighting mode setting

- [0] : LED1 constant current mode ( default )

- [1] : LED1 slope mode

- D2 : LED3ON LED3 enable control [0] : LED3 OFF ( default )

- [1] : LED3 ON

- D1 : LED2ON LED2 enable control [0] : LED2 OFF ( default )

- [1] : LED2 ON

- D0 : LED1ON LED1 enable control

- [0] : LED1 OFF ( default )

- [1] : LED1 ON

LED1 operation mode

| D4     | D0     | LED4 energian mode         |

|--------|--------|----------------------------|

| LED1MD | LED10N | LED1 operation mode        |

| 0      | 0      | OFF                        |

| 1      | 0      | OFF                        |

| 0      | 1      | ON (constant current mode) |

| 1      | 1      | ON (slope mode)            |

This mode applies to LED2, LED3 operation modes, too.

#### 3. Register map details (continued)

| Registe | er Name       | SEL   |            |    |        |        |         |         |         |

|---------|---------------|-------|------------|----|--------|--------|---------|---------|---------|

| Address | R / W<br>mode | D7 D6 |            | D5 | D4     | D3     | D2      | D1      | D0      |

| 02 h    | R/W           | IMAX  | IMAX [1:0] |    | CLKDIR | EXTPWM | DLYSEL3 | DLYSEL2 | DLYSEL1 |

| Default | 40 h          | 0 1   |            | 0  | 0      | 0      | 0       | 0       | 0       |

D7-6 : IMAX [1:0] Maximum value, Step value setting for current setting

[00] : Maximum value 12.75 mA, Step value 0.05 mA

[01] : Maximum value 25.50 mA, Step value 0.10 mA ( default )

[10] : Maximum value 31.875 mA, Step value 0.125 mA

- [11] : Maximum value 63.75 mA, Step value 0.25 mA

- D5 : IOEN CLKPWM pin enable control

- [0] : CLKPWM pin invalid ( default )

- [1] : CLKPWM pin valid

D4 : CLKDIR CLKPWM pin I/O mode setting

- [0] : CLKPWM pin input mode ( default )

- [1] : CLKPWM pin output mode

- D4 D3 **D5** CLKPWM operation mode (Clock mode/PWM mode) **IOEN** CLKDIR **EXTPWM** 0 0 or 1 OFF 0 or 1 1 0 or 1 1 External PWM operation mode 1 0 0 External clock input mode 1 1 0 Internal clock output mode

D3 : EXTPWM CLKPWM pin PWM mode setting

[0] : CLKPWM pin PWM mode invalid ( default )

- [1] : CLKPWM pin PWM mode valid

- D2 : DLYSEL3 Lighting delay time mode setting at LED3 Slope mode

- [0] : LED3 delay time Max 7.50 s mode ( default )

[1] : LED3 delay time Max 1.86 s mode

D1 : DLYSEL2 Lighting delay time mode setting at LED2 Slope mode

- [0]: LED2 Delay time Max 7.50 s mode ( default )

- [1]: LED2 Delay time Max 1.86 s mode

- D0 : DLYSEL1 Lighting delay time mode setting at LED1 Slope mode

- [0]: LED1 Delay time Max 7.50 s mode ( default )

- [1]: LED1 Delay time Max 1.86 s mode

Please refer to the detail explanation of following register DELAY1 for DLYSEL\* details.

<External PWM operation mode>

LED lighting turns ON/OFF by High/Low setting of CLKPWM pin at the time of LED lighting setting.

This mode enables LED lighting synchronization with music signal and brightness control by High/Low Duty ratio.

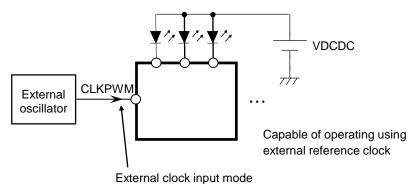

<External clock input mode>

The reference clock for Slope control is CLKPWM pin. Synchronization with external signals is possible.

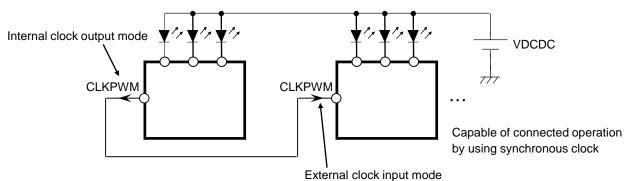

<Internal clock output mode>

Internal reference clock for Slope control is generated via CLKPWM pin.

(The output clock will not be available when LED10N=LED2ON=LED3ON=0.)

Synchronized operation can be possible when more than two pieces of this IC are connected.

## 3. Register map details (continued)

| Registe | Register Name LED1CC |    |                 |    |        |           |    |    |    |  |  |

|---------|----------------------|----|-----------------|----|--------|-----------|----|----|----|--|--|

| Address | R / W<br>mode        | D7 | D6              | D5 | D4     | D3        | D2 | D1 | D0 |  |  |

| 03 h    | R/W                  |    |                 |    | LED1C0 | C [7 : 0] |    |    |    |  |  |

| Default | 00 h                 | 0  | 0 0 0 0 0 0 0 0 |    |        |           |    |    |    |  |  |

D7-0 : LED1CC [7: 0] Current setting for LED1 constant current output

| Registe | r Name        | LED2CC |                 |    |        |           |    |    |    |  |  |

|---------|---------------|--------|-----------------|----|--------|-----------|----|----|----|--|--|

| Address | R / W<br>mode | D7     | D6              | D5 | D4     | D3        | D2 | D1 | D0 |  |  |

| 04 h    | R/W           |        |                 |    | LED2C0 | C [7 : 0] |    |    |    |  |  |

| Default | 00 h          | 0      | 0 0 0 0 0 0 0 0 |    |        |           |    |    |    |  |  |

D7-0 : LED2CC [7: 0] Current setting for LED2 constant current output

| Registe | r Name        |    |               |    | LED3CC |           |    |    |    |  |  |

|---------|---------------|----|---------------|----|--------|-----------|----|----|----|--|--|

| Address | R / W<br>mode | D7 | D6            | D5 | D4     | D3        | D2 | D1 | D0 |  |  |

| 05 h    | R/W           |    |               |    | LED3C0 | C [7 : 0] |    |    |    |  |  |

| Default | 00 h          | 0  | 0 0 0 0 0 0 0 |    |        |           |    |    |    |  |  |

D7-0 : LED3CC [7 : 0] Current setting for LED3 constant current output

Output current value can be changed by IMAX setting as below.

|    |    | L  | ED*C | C [7 : 0 | )] |    |    |           | IMAX      | [1:0]     |           |

|----|----|----|------|----------|----|----|----|-----------|-----------|-----------|-----------|

| D7 | D6 | D5 | D4   | D3       | D2 | D1 | D0 | 00h       | 01h       | 10h       | 11h       |

| 0  | 0  | 0  | 0    | 0        | 0  | 0  | 0  | 0.000 mA  | 0.000 mA  | 0.000 mA  | 0.000 mA  |

| 0  | 0  | 0  | 0    | 0        | 0  | 0  | 1  | 0.050 mA  | 0.100 mA  | 0.125 mA  | 0.250 mA  |

| 0  | 0  | 0  | 0    | 0        | 0  | 1  | 0  | 0.100 mA  | 0.200 mA  | 0.250 mA  | 0.500 mA  |

| :  | :  | :  | :    | :        | :  | :  | :  | :         | :         | :         | :         |

| :  | :  | :  | :    | :        | :  | :  | :  | 0.050 mA  | 0.100 mA  | 0.125 mA  | 0.250 mA  |

| :  | :  | :  | :    | :        | :  | :  | :  | Step      | Step      | Step      | Step      |

| :  | :  | :  | :    | :        | :  | :  | :  | :         | :         | :         | :         |

| 1  | 1  | 1  | 1    | 1        | 1  | 1  | 0  | 12.700 mA | 25.400 mA | 31.750 mA | 63.500 mA |

| 1  | 1  | 1  | 1    | 1        | 1  | 1  | 1  | 12.750 mA | 25.500 mA | 31.875 mA | 63.750 mA |

## 3. Register map details (continued)

| Registe | er Name       | LED1SLP |             |           |   |                 |    |    |    |

|---------|---------------|---------|-------------|-----------|---|-----------------|----|----|----|

| Address | R / W<br>mode | D7      | D7 D6 D5 D4 |           |   |                 | D2 | D1 | D0 |

| 06 h    | R/W           |         | SLP1TT      | 2 [3 : 0] |   | SLP1TT1 [3 : 0] |    |    |    |

| Default | 88 h          | 1       | 0           | 0         | 0 | 1               | 0  | 0  | 0  |

Total time of SLOPE operation for LED1 will be set.

Please refer to following "4. LED control Slope lighting mode" for the details of slope operation.

|   | SLP1TT | 1 [3:0] |   | Total time of SLOPE operation 1, 2                                        |

|---|--------|---------|---|---------------------------------------------------------------------------|

| 0 | 0      | 0       | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 125 $\times$ 0 = 0.0 s  |

| 0 | 0      | 0       | 1 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 125 $\times$ 1 = 0.5 s  |

| 0 | 0      | 1       | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 125 $\times$ 2 = 1.0 s  |

| : | :      | :       | : | :                                                                         |

| : | :      | :       | : | 0.5 s Step                                                                |

| : | :      | :       | : | :                                                                         |

| 1 | 1      | 0       | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 125 $\times$ 12 = 6.0 s |

| 1 | 1      | 0       | 1 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 125 $\times$ 13 = 6.5 s |

| 1 | 1      | 1       | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 125 $\times$ 14 = 7.0 s |

| 1 | 1      | 1       | 1 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 125 $\times$ 15 = 7.5 s |

SLP1TT1 [3:0] is set as the chart below shows.

SLP1TT2 [3: 0] is set as the chart below shows.

|   | SLP1TT | 2 [3:0] |   | Total time of SLOPE operation 3, 4                                        |

|---|--------|---------|---|---------------------------------------------------------------------------|

| 0 | 0      | 0       | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 125 $\times$ 0 = 0.0 s  |

| 0 | 0      | 0       | 1 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 125 $\times$ 1 = 0.5 s  |

| 0 | 0      | 1       | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 125 $\times$ 2 = 1.0 s  |

| : | :      | :       | : | :                                                                         |

| : | :      | :       | : | 0.5 s Step                                                                |

| : | :      | :       | : | :                                                                         |

| 1 | 1      | 0       | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 125 $\times$ 12 = 6.0 s |

| 1 | 1      | 0       | 1 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 125 $\times$ 13 = 6.5 s |

| 1 | 1      | 1       | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 125 $\times$ 14 = 7.0 s |

| 1 | 1      | 1       | 1 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 125 $\times$ 15 = 7.5 s |

Established : 2013-12-26 Revised : 2019-07-23

## 3. Register map details (continued)

| Registe | er Name       | ED2SLP |        |           |    |                 |    |    |    |

|---------|---------------|--------|--------|-----------|----|-----------------|----|----|----|

| Address | R / W<br>mode | D7     | D6     | D5        | D4 | D3              | D2 | D1 | D0 |

| 07 h    | R/W           |        | SLP2TT | 2 [3 : 0] |    | SLP2TT1 [3 : 0] |    |    |    |

| Default | 88 h          | 1      | 0      | 0         | 0  | 1               | 0  | 0  | 0  |

Total time of Slope operation for LED2 will be set.

| Registe | r Name        |    | LED3SLP                    |    |    |    |    |    |    |  |  |

|---------|---------------|----|----------------------------|----|----|----|----|----|----|--|--|

| Address | R / W<br>mode | D7 | D6                         | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

| 08 h    | R/W           |    | SLP3TT2 [3 : 0] SLP3TT1 [3 |    |    |    |    |    |    |  |  |

| Default | 88 h          | 1  | 1 0 0 0 1                  |    |    |    |    |    | 0  |  |  |

Total time of Slope operation for LED3 will be set.

Please refer to following " 4. LED control Slope lighting mode " for the details of slope operation.

The Slope setting charts for LED2 and LED3 are the same as the one for LED1 in the previous page.

#### 3. Register map details (continued)

| Registe | r Name        |    | LED1CNT1             |            |   |                  |   |   |   |  |  |

|---------|---------------|----|----------------------|------------|---|------------------|---|---|---|--|--|

| Address | R / W<br>mode | D7 | D7 D6 D5 D4 D3 D2 D1 |            |   |                  |   |   |   |  |  |

| 09 h    | R/W           |    | DUTYMA               | X1 [3 : 0] |   | DUTYMID1 [3 : 0] |   |   |   |  |  |

| Default | F8 h          | 1  | 1                    | 1          | 1 | 1                | 0 | 0 | 0 |  |  |

D7-4 : DUTYMAX1 [3 : 0] LED1 at Slope lighting maximum PWM Duty setting

D3-0 : DUTYMID1 [3 : 0] LED1 at Slope lighting middle PWM Duty setting

| Registe | r Name        |    | LED1CNT2             |           |   |   |        |            |   |  |  |

|---------|---------------|----|----------------------|-----------|---|---|--------|------------|---|--|--|

| Address | R / W<br>mode | D7 | D7 D6 D5 D4 D3 D2 D1 |           |   |   |        |            |   |  |  |

| 0A h    | R/W           |    | DELAY                | 1 [3 : 0] |   |   | DUTYMI | N1 [3 : 0] |   |  |  |

| Default | 00 h          | 0  | 0                    | 0         | 0 | 0 | 0      | 0          | 0 |  |  |

D7-4 : DELAY1 [3 : 0] LED1 starting delay time setting

D3-0 : DUTYMIN1 [3 : 0] LED1 at Slope lighting minimum PWM Duty setting

| Registe | r Name        |    | LED1CNT3             |            |   |                 |   |   |   |  |  |

|---------|---------------|----|----------------------|------------|---|-----------------|---|---|---|--|--|

| Address | R / W<br>mode | D7 | D7 D6 D5 D4 D3 D2 D1 |            |   |                 |   |   |   |  |  |

| 0B h    | R/W           |    | SLP1D1               | F2 [3 : 0] |   | SLP1DT1 [3 : 0] |   |   |   |  |  |

| Default | 88 h          | 1  | 0                    | 0          | 0 | 1               | 0 | 0 | 0 |  |  |

D7-4 : SLP1DT2 [3 : 0] LED1 slope lighting, the period of SLOPE operation 2 time D3-0 : SLP1DT1 [3 : 0] LED1 slope lighting, the period of SLOPE operation 1 time

| Registe | r Name        |    | LED1CNT4                |   |   |   |   |                 |   |  |  |

|---------|---------------|----|-------------------------|---|---|---|---|-----------------|---|--|--|

| Address | R / W<br>mode | D7 | D7 D6 D5 D4 D3 D2 D1 D0 |   |   |   |   |                 |   |  |  |

| 0C h    | R/W           |    | SLP1DT4 [3 : 0]         |   |   |   |   | SLP1DT3 [3 : 0] |   |  |  |

| Default | 88 h          | 1  | 0                       | 0 | 0 | 1 | 0 | 0               | 0 |  |  |

D7-4 : SLP1DT4 [3 : 0] LED1 slope lighting, the period of SLOPE operation 4 time D3-0 : SLP1DT3 [3 : 0] LED1 slope lighting, the period of SLOPE operation 3 time

Operation parameter of LED1 SLOPE operation will be set.

Please refer to following "4. LED control Slope lighting mode " for the details of slope operation.

### 3. Register map details (continued)

DUTYMAX1 [3:0] correspond to the following PWM Duty setting as the following chart shows.

| I  | OUTYMA | X1 [3 : 0 | ]  |    | Duty s | etting fo | r PWM o | peration | [6 : 0] |    |

|----|--------|-----------|----|----|--------|-----------|---------|----------|---------|----|

| D3 | D2     | D1        | D0 | D6 | D5     | D4        | D3      | D2       | D1      | D0 |

| 0  | 0      | 0         | 0  | 0  | 0      | 0         | 0       | 1        | 1       | 1  |

| 0  | 0      | 0         | 1  | 0  | 0      | 0         | 1       | 1        | 1       | 1  |

| 0  | 0      | 1         | 0  | 0  | 0      | 1         | 0       | 1        | 1       | 1  |

| 0  | 0      | 1         | 1  | 0  | 0      | 1         | 1       | 1        | 1       | 1  |

|    | -      | -         |    |    |        |           | ~       |          |         |    |

| 1  | 1      | 1         | 0  | 1  | 1      | 1         | 0       | 1        | 1       | 1  |

| 1  | 1      | 1         | 1  | 1  | 1      | 1         | 1       | 1        | 1       | 1  |

Duty setting for PWM operation [6:0]

[0000111]: 7 / 128 = 5.47 % [0001111]: 15 / 128 = 11.72 % [0010111]: 23 / 128 = 17.97 % [0011111]: 31 / 128 = 24.22 % : [1110111]: 119 / 128 = 92.97 % [1111111]: 127 / 128 = 99.22 %

DUTYMID1 [3: 0] correspond to the following PWM Duty setting as the following chart shows.

|    | DUTYMI | D1 [3 : 0] |    |    | Duty s | setting fo | or PWM o | operation | n[6 : 0] |    |

|----|--------|------------|----|----|--------|------------|----------|-----------|----------|----|

| D3 | D2     | D1         | D0 | D6 | D5     | D4         | D3       | D2        | D1       | D0 |

| 0  | 0      | 0          | 0  | 0  | 0      | 0          | 0        | 0         | 0        | 0  |

| 0  | 0      | 0          | 1  | 0  | 0      | 0          | 1        | 1         | 1        | 1  |

| 0  | 0      | 1          | 0  | 0  | 0      | 1          | 0        | 1         | 1        | 1  |

| 0  | 0      | 1          | 1  | 0  | 0      | 1          | 1        | 1         | 1        | 1  |

|    | -      | ~          |    |    |        |            | ~        |           |          |    |

| 1  | 1      | 1          | 0  | 1  | 1      | 1          | 0        | 1         | 1        | 1  |

| 1  | 1      | 1          | 1  | 1  | 1      | 1          | 1        | 1         | 1        | 1  |

Duty setting for PWM operation [6:0]

| [0000000] : | 0 / 128 = 0 %       |

|-------------|---------------------|

| [0001111]:  | 15 / 128 = 11.72 %  |

| [0010111]:  | 23 / 128 = 17.97 %  |

| [0011111]:  | 31 / 128 = 24.22 %  |

| :           |                     |

| [1110111]:  | 119 / 128 = 92.97 % |

| [1111111]:  | 127 / 128 = 99.22 % |

|             |                     |

#### 3. Register map details (continued)

DUTYMIN1 [3:0] correspond to the following PWM Duty setting [6:0] as the following chart shows.

|    | DUTYMI | N1 [3 : 0] |    |    | Duty s | etting fo | or PWM o | peration | [6 : 0] |    |

|----|--------|------------|----|----|--------|-----------|----------|----------|---------|----|

| D3 | D2     | D1         | D0 | D6 | D5     | D4        | D3       | D2       | D1      | D0 |

| 0  | 0      | 0          | 0  | 0  | 0      | 0         | 0        | 0        | 0       | 0  |

| 0  | 0      | 0          | 1  | 0  | 0      | 0         | 1        | 0        | 0       | 0  |

| 0  | 0      | 1          | 0  | 0  | 0      | 1         | 0        | 0        | 0       | 0  |

| 0  | 0      | 1          | 1  | 0  | 0      | 1         | 1        | 0        | 0       | 0  |

|    |        | ~          |    |    |        |           | ~        |          |         |    |

| 1  | 1      | 1          | 0  | 1  | 1      | 1         | 0        | 0        | 0       | 0  |

| 1  | 1      | 1          | 1  | 1  | 1      | 1         | 1        | 0        | 0       | 0  |

Duty setting for PWM operation [6: 0] [0000000]: 0 / 128 = 0 % [0001000]: 8 / 128 = 6.25 % [0010000]: 16 / 128 = 12.5 % [0011000]: 24 / 128 = 18.75 % : [1110000]: 112 / 128 = 87.5 % [1111000]: 120 / 128 = 93.75 %

DELAY1 [3 : 0] is set as the following chart shows.

|   | DELAY | [3:0] |   | DLYSEL1 = 0 | DLYSEL1 = 1 |

|---|-------|-------|---|-------------|-------------|

| 0 | 0     | 0     | 0 | 0.00 s      | 0.000 s     |

| 0 | 0     | 0     | 1 | 0.50 s      | 0.124 s     |

| 0 | 0     | 1     | 0 | 1.00 s      | 0.248 s     |

|   | ~     |       |   | ~           | ~           |

| 1 | 1     | 1     | 0 | 7.00 s      | 1.736 s     |

| 1 | 1     | 1     | 1 | 7.50 s      | 1.860 s     |

## 3. Register map details (continued)

SLP1DT1 [3:0] is set as the following chart shows.

|   | SLP1DT | 1 [3 : 0] |   | Detention time at each step                                    |

|---|--------|-----------|---|----------------------------------------------------------------|

| 0 | 0      | 0         | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 1 = 53.3 $\mu$ s         |

| 0 | 0      | 0         | 1 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 1 = 4.0 ms   |

| 0 | 0      | 1         | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 2 = 8.0 ms   |

|   | ~      |           |   | ~                                                              |

| 1 | 1      | 1         | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 14 = 56.0 ms |

| 1 | 1      | 1         | 1 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 15 = 60.0 ms |

SLP1DT2 [3:0] is set as the following chart shows.

|   | SLP1DT | 2 [3: 0] |   | Detention time at each step                                    |

|---|--------|----------|---|----------------------------------------------------------------|

| 0 | 0      | 0        | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 1 = 53.3 $\mu$ s         |

| 0 | 0      | 0        | 1 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 1 = 4.0 ms   |

| 0 | 0      | 1        | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 2 = 8.0 ms   |

|   | ~      |          |   | ~                                                              |

| 1 | 1      | 1        | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 14 = 56.0 ms |

| 1 | 1      | 1        | 1 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 15 = 60.0 ms |

SLP1DT3 [3:0] is set as the following chart shows.

|   | SLP1DT | 3 [3: 0] |   | Detention time at each step                                    |  |  |  |  |  |

|---|--------|----------|---|----------------------------------------------------------------|--|--|--|--|--|

| 0 | 0      | 0        | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 1 = 53.3 $\mu$ s         |  |  |  |  |  |

| 0 | 0      | 0        | 1 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 1 = 4.0 ms   |  |  |  |  |  |

| 0 | 0      | 1        | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 2 = 8.0 ms   |  |  |  |  |  |

|   | ~      |          |   | ~                                                              |  |  |  |  |  |

| 1 | 1      | 1        | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 14 = 56.0 ms |  |  |  |  |  |

| 1 | 1      | 1        | 1 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 15 = 60.0 ms |  |  |  |  |  |

SLP1DT4 [3 : 0] is set as the following chart shows.

|   | SLP1DT | 4 [3: 0] |   | Detention time at each step                                    |  |  |  |  |

|---|--------|----------|---|----------------------------------------------------------------|--|--|--|--|

| 0 | 0      | 0        | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 1 = 53.3 $\mu$ s         |  |  |  |  |

| 0 | 0      | 0        | 1 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 1 = 4.0 ms   |  |  |  |  |

| 0 | 0      | 1        | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 2 = 8.0 ms   |  |  |  |  |

|   | ~      |          |   | ~                                                              |  |  |  |  |

| 1 | 1      | 1        | 0 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 14 = 56.0 ms |  |  |  |  |

| 1 | 1      | 1        | 1 | ( PWM cycle = 53.3 $\mu$ s ) $\times$ 75 $\times$ 15 = 60.0 ms |  |  |  |  |

## 3. Register map details (continued)

| Register Name |               |    |         |            | LED2CNT1 |                  |    |    |    |

|---------------|---------------|----|---------|------------|----------|------------------|----|----|----|

| Address       | R / W<br>mode | D7 | D6      | D5         | D4       | D3               | D2 | D1 | D0 |

| 0D h          | R/W           |    | DUTYMA  | X2 [3 : 0] |          | DUTYMID2 [3 : 0] |    |    |    |

| Default       | F8 h          | 1  | 1 1 1 1 |            |          |                  | 0  | 0  | 0  |

D7-4 : DUTYMAX2 [3 : 0] LED2 at slope lighting, maximum PWM Duty setting

D3-0 : DUTYMID2 [3 : 0] LED2 at slope lighting, middle PWM Duty setting

| Registe | er Name       | LED2CNT2 |         |           |    |                  |    |    |    |  |

|---------|---------------|----------|---------|-----------|----|------------------|----|----|----|--|

| Address | R / W<br>mode | D7       | D6      | D5        | D4 | D3               | D2 | D1 | D0 |  |

| 0E h    | R/W           |          | DELAY   | 2 [3 : 0] |    | DUTYMIN2 [3 : 0] |    |    |    |  |

| Default | 00 h          | 0        | 0 0 0 0 |           |    |                  | 0  | 0  | 0  |  |

D7-4 : DELAY2 [3 : 0] LED2 starting delay time setting

D3-0 : DUTYMIN2 [3 : 0] LED2 at slope lighting, minimum PWM Duty setting

| Registe | er Name       | LED2CNT3 |        |            |    |                 |    |    |    |  |

|---------|---------------|----------|--------|------------|----|-----------------|----|----|----|--|

| Address | R / W<br>mode | D7       | D6     | D5         | D4 | D3              | D2 | D1 | D0 |  |

| 0F h    | R/W           |          | SLP2D1 | F2 [3 : 0] |    | SLP2DT1 [3 : 0] |    |    |    |  |

| Default | 88 h          | 1        | 0      | 0          | 0  | 1               | 0  | 0  | 0  |  |

D7-4 : SLP2DT2 [3 : 0] LED2 slope lighting, the period of SLOPE operation 2 time

D3-0 : SLP2DT1 [3 : 0] LED2 slope lighting, the period of SLOPE operation 1 time

| Registe | er Name       | LED2CNT4 |        |            |    |                 |    |    |    |  |

|---------|---------------|----------|--------|------------|----|-----------------|----|----|----|--|

| Address | R / W<br>mode | D7       | D6     | D5         | D4 | D3              | D2 | D1 | D0 |  |

| 10 h    | R/W           |          | SLP2D1 | [4 [3 : 0] |    | SLP2DT3 [3 : 0] |    |    |    |  |

| Default | 88 h          | 1        | 0      | 0          | 0  | 1               | 0  | 0  | 0  |  |

D7-4 : SLP2DT4 [3 : 0] LED2 slope lighting, the period of SLOPE operation 4 time D3-0 : SLP2DT3 [3 : 0] LED2 slope lighting, the period of SLOPE operation 3 time

Operation parameter of LED2 SLOPE operation will be set.

Each parameter is the same as LED1 Parameter.

Please refer to following "4. LED control Slope lighting mode " for the details of slope operation.

## 3. Register map details (continued)

| Registe | Register Name LED: |    |         |            |    | CNT1             |    |    |    |  |

|---------|--------------------|----|---------|------------|----|------------------|----|----|----|--|

| Address | R / W<br>mode      | D7 | D6      | D5         | D4 | D3               | D2 | D1 | D0 |  |

| 11 h    | R/W                |    | DUTYMA  | X3 [3 : 0] |    | DUTYMID3 [3 : 0] |    |    |    |  |

| Default | F8 h               | 1  | 1 1 1 1 |            |    |                  | 0  | 0  | 0  |  |

D7-4 : DUTYMAX3 [3 : 0] LED3 at slope lighting maximum PWM Duty setting

D3-0 : DUTYMID3 [3 : 0] LED3 at slope lighting middle PWM Duty setting

| Registe | er Name       | LED3CNT2 |       |           |    |                  |    |    |    |  |

|---------|---------------|----------|-------|-----------|----|------------------|----|----|----|--|

| Address | R / W<br>mode | D7       | D6    | D5        | D4 | D3               | D2 | D1 | D0 |  |

| 12 h    | R/W           |          | DELAY | 3 [3 : 0] |    | DUTYMIN3 [3 : 0] |    |    |    |  |

| Default | 00 h          | 0        | 0     | 0         | 0  | 0                | 0  | 0  | 0  |  |

D7-4 : DELAY3 [3 : 0] LED3 starting delay time setting

D3-0 : DUTYMIN3 [3 : 0] LED3 at slope lighting minimum PWM Duty setting

| Registe | er Name       | LED3CNT3 |         |            |    |                 |    |    |    |  |

|---------|---------------|----------|---------|------------|----|-----------------|----|----|----|--|

| Address | R / W<br>mode | D7       | D6      | D5         | D4 | D3              | D2 | D1 | D0 |  |

| 13 h    | R/W           |          | SLP3D1  | [2 [3 : 0] |    | SLP3DT1 [3 : 0] |    |    |    |  |

| Default | 88 h          | 1        | 1 0 0 0 |            |    |                 | 0  | 0  | 0  |  |

$\mathsf{D7-4}: \mathsf{SLP3DT2} \ [3:0] \quad \mathsf{LED3} \ \mathsf{slope} \ \mathsf{lighting}, \ \mathsf{the} \ \mathsf{period} \ \mathsf{of} \ \mathsf{SLOPE} \ \mathsf{operation} \ \mathsf{2} \ \mathsf{time}$

D3-0 : SLP3DT1 [3: 0] LED3 slope lighting, the period of SLOPE operation 1 time

| Registe | r Name        | LED3CNT4 |       |           |    |                |    |    |    |  |

|---------|---------------|----------|-------|-----------|----|----------------|----|----|----|--|

| Address | R / W<br>mode | D7       | D6    | D5        | D4 | D3             | D2 | D1 | D0 |  |

| 14 h    | R/W           |          | SLP3D | T4 [3: 0] |    | SLP3DT3 [3: 0] |    |    |    |  |

| Default | 88 h          | 1        | 0     | 0         | 0  | 1              | 0  | 0  | 0  |  |

D7-4 : SLP3DT4 [3: 0] LED3 slope lighting, the period of SLOPE operation 4 time D3-0 : SLP3DT3 [3: 0] LED3 slope lighting, the period of SLOPE operation 3 time

Operation parameter of LED3 SLOPE operation will be set.

Each parameter is the same as LED1 parameter.

Please refer to following "4. LED control Slope lighting mode " for the details of slope operation.

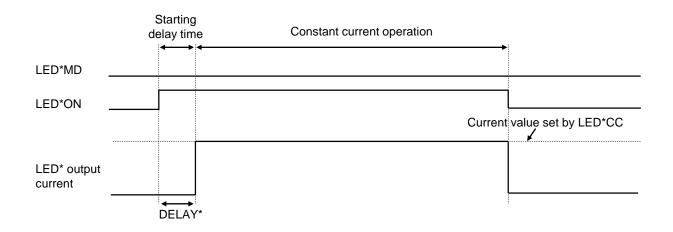

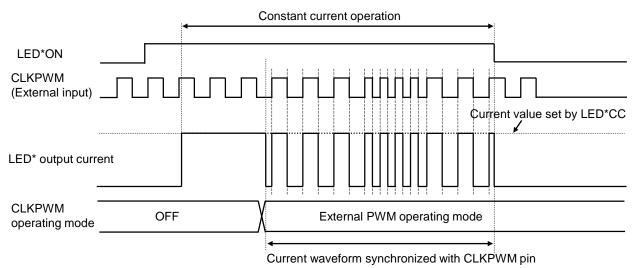

#### 4. LED control

- 4.1 Constant current lighting mode

- It is possible to choose "Constant current lighting mode" and "Slope lighting mode" by setting Register LED\*MD. To operate at "Constant current mode", please set LED\*MD at "0". ("\*" can be 1, 2, or 3.)

- Upon setting LED\*ON to "1", constant current operation will start after the previously set starting delay time, DELAY\*.

- As described in page 30, it is possible to turn on and off at High/Low of CLKPWM pin by making the external PWM

operating mode for CLKPWM pin setting valid.

#### 4. LED control (continued)

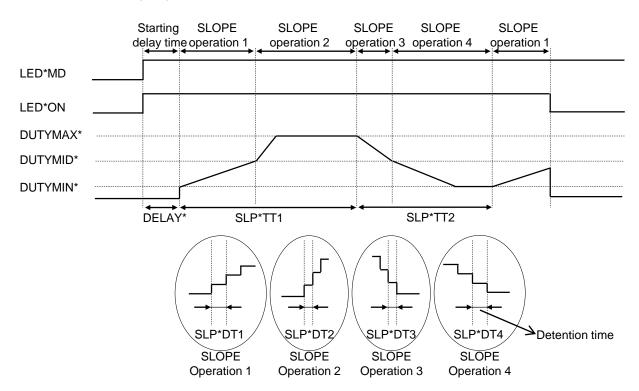

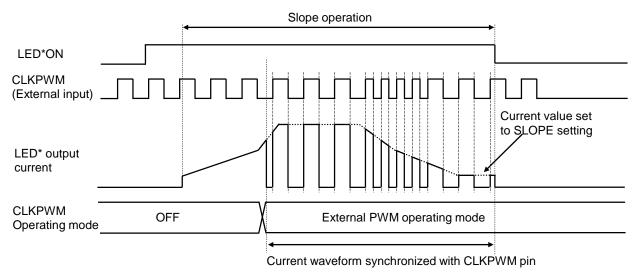

- 4.2 Slope lighting mode

- To operate at "Slope lighting mode", please set LED\*MD at "1". ( "\*" can be 1, 2, or 3.)

- To repeat Slope operation from 1 to 4 after the previously set starting delay time, DELAY\*, please set Register LED\*ON at "1".

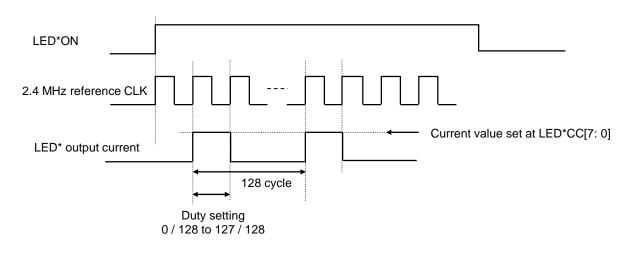

- The minimum resolution of SLOPE sequence control is 2.40 MHz reference clock cycle as below.

#### 4. LED control (continued)

4.3 Total time of Slope operation 1, 2

Total time of Slope operation 1, 2 can be controlled by SLP\*TT1[3 : 0]. SLP\*TT1[3 : 0] is set as described before.

- SLP\*TT1[3 : 0] setting has priority to the case of SLP\*TT1[3 : 0] < "SLOPE operation 1" + "SLOPE operation 2".</li>

- In case of that SLP\*TT1[3 : 0] time is over during SLOPE operation 1 (before SLOPE operation 2), SLOPE operation 2 is omitted and transferred to SLOPE operation 3 from the position of DUTYMAX.

4.4 Total time of Slope operation 3, 4

Total time of Slope operation 3, 4 can be controlled by SLP\*TT2[3: 0]. SLP\* TT2[3: 0] is set as described before.

- SLP\*TT2[3 : 0] setting has priority to the case of SLP\*TT2[3 : 0] < "SLOPE operation 3" + "SLOPE operation 4".

- In case of that SLP\*TT2[3 : 0] time is over during SLOPE operation 3(before SLOPE operation 4), SLOPE operation 4 is omitted and transferred to SLOPE operation 1 from the position of DUTYMIN.

4.5 DUTYMIN, DUTYMID, DUTYMAX setting for SLOPE operation

SLOPE operation 1

PWM step increases step by step from the value set by DUTYMIN\*[3 : 0] to the value set by DUTYMID\*[3 : 0]. Please set the period by SLP\*DT1[3 : 0] for each step.

The value should be DUTYMIN\*[3 : 0] < DUTYMID\*[3 : 0].

SLOPE operation 1 operates at DUTYMIN = DUTYMID in case DUTYMIN\*[3 : 0]  $\geq$  DUTYMID\*[3 : 0] .

SLOPE operation 2

PWM step increases step by step from the value set by DUTYMID\*[3:0] to the value set at DUTYMAX\*[3:0]. Please set the period by SLP\*DT2[3:0] for each step.

The value should be DUTYMID\*[3:0] < DUTYMAX\*[3:0].

SLOPE operation 2 operates at DUTYMID = DUTYMAX in case DUTYMID\*[3 : 0]  $\geq$  DUTYMAX\*[3 : 0] .

Slope operation 3

PWM step decreases step by step from the value set by DUTYMAX\*[3:0] to the value set by DUTYMID\*[3:0]. Please set the period by SLP\*DT3[3:0] for each step.

The value should be DUTYMID\*[3 : 0] < DUTYMAX\*[3 : 0].

SLOPE operation 3 operates at DUTYMID = DUTYMAX in case DUTYMID\*[3 : 0]  $\geq$  DUTYMAX\*[3 : 0] .

SLOPE operation 4

PWM step decreases step by step from the value set by DUTYMID\*[3:0] to the value set by DUTYMIN\*[3:0]. Please set the period by SLP\*DT4[3:0] for each step.

The value should be DUTYMIN\*[3 : 0] < DUTYMID\*[3 : 0].

SLOPE operation 4 operates at DUTYMIN = DUTYMID in case DUTYMIN\*[3 : 0]  $\geq$  DUTYMID\*[3: 0] .

#### 4. LED control (continued)

4.6 External PWM operation mode of CLKPWM pin

The lighting synchronization with CLKPWM signal can be turned on by setting "External PWM operation mode" in register setting.

The maximum frequency which can be input to CLKPWM pin is 20 kHz.

< At Constant current mode >

< At Slope lighting mode>

### 4. LED control (continued)

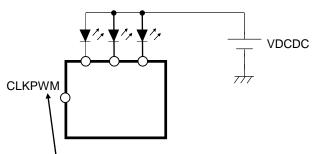

4.7 External clock input mode and internal clock output mode of CLKPWM pin

The following configuration can be made up by choosing "External clock input mode", "Internal clock output mode" in register setting.

< Single application >

Unused state (CLKPWM operation OFF mode)

< Connected application >

(Please refer to the explanation of the operation mode of P.17 for the setting of CLKPWM)

< External reference clock application >

(Please refer to the explanation of the operation mode of P.17 for the setting of CLKPWM)

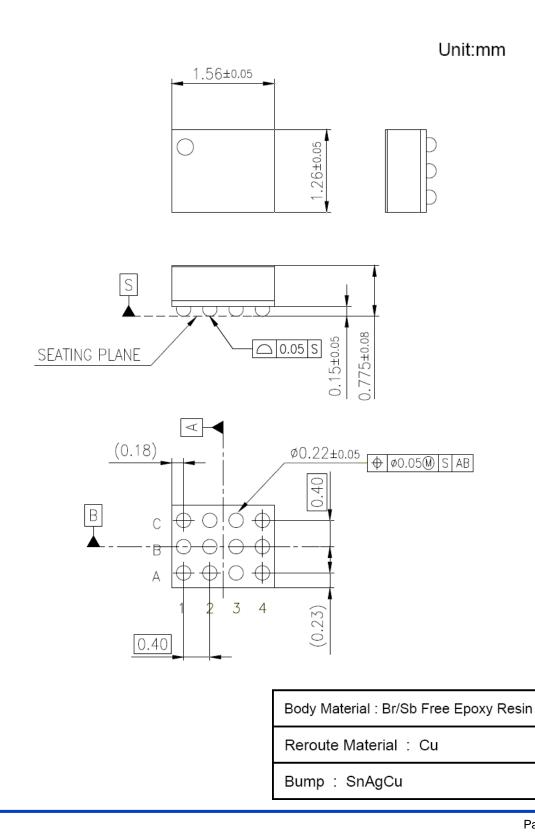

# PACKAGE INFORMATION (Reference Data)

## **IMPORTANT NOTICE**

- 1. When using the IC for new models, verify the safety including the long-term reliability for each product.

- 2. When the application system is designed by using this IC, please confirm the notes in this book. Please read the notes to descriptions and the usage notes in the book.

- 3. This IC is neither designed nor intended for use in automotive applications or environments unless the specific product is designated by our company as compliant with the ISO/TS 16949 requirements. Our company shall not be held responsible for any damage incurred by customers or any third party as a result of or in connection with the IC being used in automotive application, unless our company agrees to such application in this book.

- 4. Please use this product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Our company shall not be held responsible for any damage incurred as a result of our IC being used by our customers, not complying with the applicable laws and regulations.

# **USAGE NOTES**

- 1. Pay attention to the direction of IC. When mounting it in the wrong direction onto the PCB (printed-circuit-board), it might emit smoke or ignite.

- 2. Pay attention in the PCB (printed-circuit-board) pattern layout in order to prevent damage due to short circuit between pins. In addition, refer to the Pin Description for the pin configuration.

- 3. Perform visual inspection on the PCB before applying power, otherwise damage might happen due to problems such as solder-bridge between the pins of the IC. Also, perform full technical verification on the assembly quality, because the same damage possibly can happen due to conductive substances, such as solder ball, that adhere to the IC during transportation.

- 4. Take notice in the use of this IC that it might be damaged or occasionally emit smoke when an abnormal state occurs such as output pin-VCC short (Power supply fault), output pin-GND short (Ground fault), or output-to-output-pin short (load short). Safety measures such as installation of fuses are recommended because the extent of the above-mentioned damage and smoke emission will depend on the current capability of the power supply.

- 5. Due to the unshielded structure of this IC, functions and characteristics of the IC cannot be guaranteed under the exposure of light. During normal operation or even under testing condition, please ensure that the IC is not exposed to light.

- 6. Please ensure that your design does not have metal shield parts touching the chip surface as the surface potential is GND voltage.

- 7. Pay attention to the breakdown voltage of this IC when using.

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products. No license is granted in and to any intellectual property right or other right owned by Panasonic Corporation, Nuvoton Technology Corporation Japan or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information de-scribed in this book.

- (3) The products described in this book are intended to be used for general applications (such as office equipment, communications equipment, measuring instruments and household appliances), or for specific applications as expressly stated in this book.

Please consult with our sales staff in advance for information on the following applications, moreover please exchange documents separately on terms of use etc.: Special applications (such as for in-vehicle equipment, airplanes, aerospace, automotive equipment, traffic signaling equipment, combustion equipment, medical equipment and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

Unless exchanging documents on terms of use etc. in advance, it is to be understood that our company shall not be held responsible for any damage incurred as a result of or in connection with your using the products described in this book for any special application.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most upto-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. We do not guarantee quality for disassembled products or the product re-mounted after removing from the mounting board. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) When reselling products described in this book to other companies without our permission and receiving any claim of request from the resale destination, please understand that customers will bear the burden.

- (8) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of our company.

No.070920

单击下面可查看定价,库存,交付和生命周期等信息

>>Panasonic(松下)