# ICL7660S, ICL7660A

**Super Voltage Converters**

FN3179 Rev 7.01 Feb 10, 2020

The ICL7660S and ICL7660A Super Voltage Converters are monolithic CMOS voltage conversion ICs that ensure significant performance advantages over other similar devices. They are direct replacements for the industry standard ICL7660 offering an **extended** operating supply voltage range up to 12V, with **lower** supply current. A **Frequency Boost pin** has been incorporated to enable the user to achieve lower output impedance despite using smaller capacitors. All improvements are highlighted in the "Electrical Specifications" section on page 3. Critical parameters are ensured over the entire commercial and industrial temperature ranges.

The ICL7660S and ICL7660A perform supply voltage conversions from positive to negative for an input range of 1.5V to 12V, resulting in complementary output voltages of -1.5V to -12V. Only two non-critical external capacitors are needed, for the charge pump and charge reservoir functions. The ICL7660S and ICL7660A can be connected to function as a voltage doubler and will generate up to 22.8V with a 12V input. They can also be used as a voltage multipliers or voltage dividers.

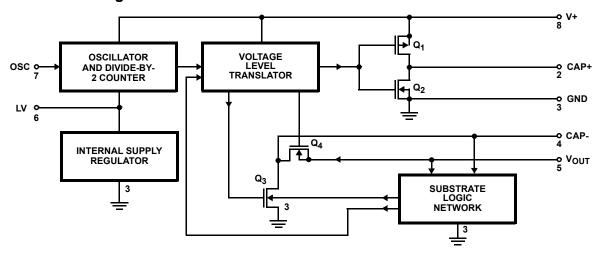

Each chip contains a series DC power supply regulator, RC oscillator, voltage level translator, and four output power MOS switches. The oscillator, when unloaded, oscillates at a nominal frequency of 10kHz for an input supply voltage of 5.0V. This frequency can be lowered by the addition of an external capacitor to the "OSC" terminal, or the oscillator may be over-driven by an external clock.

The "LV" terminal may be tied to GND to bypass the internal series regulator and improve low voltage (LV) operation. At medium to high voltages (3.5V to 12V), the LV pin is left floating to prevent device latchup.

In some applications, an external Schottky diode from  $V_{OUT}$  to CAP- is needed to ensure latchup free operation (see Do's and Dont's section on page 8).

ICL7660S

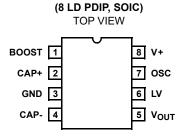

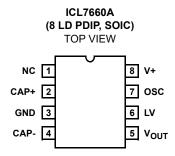

# Pin Configurations

### Features

- Ensured Lower Max Supply Current for All Temperature Ranges

- · Wide Operating Voltage Range: 1.5V to 12V

- 100% Tested at 3V

- · Boost Pin (Pin 1) for Higher Switching Frequency

- · Ensured Minimum Power Efficiency of 96%

- Improved Minimum Open Circuit Voltage Conversion Efficiency of 99%

- Improved SCR Latchup Protection

- Simple Conversion of +5V Logic Supply to ±5V Supplies

- Simple Voltage Multiplication V<sub>OLIT</sub> = (-)nV<sub>IN</sub>

- Easy to Use; Requires Only Two External Non-Critical Passive Components

- Improved Direct Replacement for Industry Standard ICL7660 and Other Second Source Devices

- · Pb-Free Available (RoHS Compliant)

## **Applications**

- Simple Conversion of +5V to ±5V Supplies

- Voltage Multiplication V<sub>OUT</sub> = ±nV<sub>IN</sub>

- Negative Supplies for Data Acquisition Systems and Instrumentation

- RS232 Power Supplies

- Supply Splitter, V<sub>OUT</sub> = ±V<sub>S</sub>

# **Ordering Information**

| PART NUMBER (Note 3)                                                                       | PART<br>MARKING | TEMP. RANGE<br>(°C) | PACKAGE                     | PKG.<br>DWG.# |

|--------------------------------------------------------------------------------------------|-----------------|---------------------|-----------------------------|---------------|

| ICL7660SCBA (No longer available, recommended replacement: ICL7660SCBAZ, ICL7660ACBAZ-T)   | 7660 SCBA       | 0 to +70            | 8 Ld SOIC                   | M8.15         |

| ICL7660SCBAZ (Notes 1, 2)                                                                  | 7660 SCBAZ      | 0 to +70            | 8 Ld SOIC (Pb-free)         | M8.15         |

| ICL7660SCPA (No longer available, recommended replacement: ICL7660SCPAZ)                   | 7660S CPA       | 0 to +70            | 8 Ld PDIP                   | E8.3          |

| ICL7660SCPAZ (Note 2)                                                                      | 7660S CPAZ      | 0 to +70            | 8 Ld PDIP (Pb-free; Note 4) | E8.3          |

| ICL7660SIBA (No longer available, recommended replacement: ICL7660SIBAZ, ICL7660SIBAZ-T)   | 7660 SIBA       | -40 to +85          | 8 Ld SOIC                   | M8.15         |

| ICL7660SIBAZ (Notes 1, 2)                                                                  | 7660 SIBAZ      | -40 to +85          | 8 Ld SOIC (Pb-free)         | M8.15         |

| ICL7660SIPA (No longer available, recommended replacement: ICL7660SIPAZ)                   | 7660 SIPA       | -40 to +85          | 8 Ld PDIP                   | E8.3          |

| ICL7660SIPAZ (Note 2)                                                                      | 7660S IPAZ      | -40 to +85          | 8 Ld PDIP (Pb-free; Note 4) | E8.3          |

| ICL7660ACBA (No longer available, recommended replacement: ICL7660ACBAZA, ICL7660ACBAZA-T) | 7660ACBA        | 0 to 70             | 8 Ld SOIC (N)               | M8.15         |

| ICL7660ACBAZA (Notes 1, 2)                                                                 | 7660ACBAZ       | 0 to 70             | 8 Ld SOIC (N) (Pb-free)     | M8.15         |

| ICL7660ACPA (No longer available, recommended replacement: ICL7660ACPAZ)                   | 7660ACPA        | 0 to 70             | 8 Ld PDIP                   | E8.3          |

| ICL7660ACPAZ (Note 2)                                                                      | 7660ACPAZ       | 0 to 70             | 8 Ld PDIP (Pb-free; Note 4) | E8.3          |

| ICL7660AIBA (No longer available, recommended replacement: ICL7660AIBAZA, ICL7660AIBAZA-T) | 7660AIBA        | -40 to 85           | 8 Ld SOIC (N)               | M8.15         |

| ICL7660AIBAZA ( <u>Notes 1</u> , <u>2</u> )                                                | 7660AIBAZ       | -40 to 85           | 8 Ld SOIC (N) (Pb-free)     | M8.15         |

### NOTES:

- 1. Add "-T\*" suffix for tape and reel. See <u>TB347</u> for details about reel specifications.

- 2. These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

- 3. For Moisture Sensitivity Level (MSL), see <a href="LCL7660S">LCL7660S</a>, <a href="LCL7660S">LC

- 4. Pb-free PDIPs can be used for through-hole wave solder processing only. They are not intended for use in reflow solder processing applications.

## **Absolute Maximum Ratings**

| Supply Voltage                    | +13.0V               |

|-----------------------------------|----------------------|

| LV and OSC Input Voltage (Note 5) |                      |

| V+ < 5.5V                         | 0.3V to V+ + 0.3V    |

| V+ > 5.5V                         | V+ -5.5V to V+ +0.3V |

| Current into LV (Note 5)          |                      |

| V+ > 3.5V                         |                      |

| Output Short Duration             |                      |

| V <sub>SUPPLY</sub> ≤ 5.5V        | Continuous           |

### **Thermal Information**

| Thermal Resistance (Typical, Notes 6, 7) | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|------------------------------------------|------------------------|------------------------|

| 8 Ld PDIP (Note 8)                       | 110                    | 59                     |

| 8 Ld Plastic SOIC                        |                        | 48                     |

| Storage Temperature Range                | <b></b> 65°            | 'C to +150°C           |

| Pb-Free Reflow Profile (Note 8)          |                        | <u>TB493</u>           |

## **Operating Conditions**

| Temperature Range    |               |

|----------------------|---------------|

| ICL7660SI, ICL7660AI | 40°C to +85°C |

| ICL7660SC, ICL7660AC | 0°C to +70°C  |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 5. Connecting any terminal to voltages greater than V+ or less than GND may cause destructive latchup. It is recommended that no inputs from sources operating from external supplies be applied prior to "power up" of ICL7660S and ICL7660A.

- 6. θ<sub>JA</sub> is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief <u>TB379</u> for details.

- 7. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is taken at the package top center.

- 8. Pb-free PDIPs can be used for through-hole wave solder processing only. They are not intended for use in reflow solder processing applications.

# Electrical Specifications

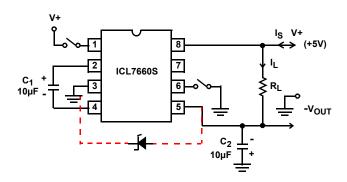

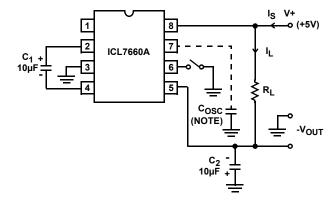

ICL7660S and ICL7660A, V+ = 5V, T<sub>A</sub> = +25°C, OSC = Free running (see <u>Figure 12 on page 7</u>, <u>"ICL7660S Test Circuit"</u> and Figure <u>Figure 13 on page 7</u> <u>"ICL7660A Test Circuit"</u>), unless otherwise specified.

| PARAMETER                             | SYMBOL               | TEST CONDITIONS                                                                     | MIN<br>( <u>Note 9</u> ) | TYP  | MAX<br>( <u>Note 9</u> ) | UNITS |

|---------------------------------------|----------------------|-------------------------------------------------------------------------------------|--------------------------|------|--------------------------|-------|

| Supply Current (Note 11)              | l+                   | R <sub>L</sub> = ∞, +25°C                                                           | -                        | 80   | 160                      | μA    |

|                                       |                      | 0°C < T <sub>A</sub> < +70°C                                                        | -                        | -    | 180                      | μΑ    |

|                                       |                      | -40°C < T <sub>A</sub> < +85°C                                                      | -                        | -    | 180                      | μΑ    |

|                                       |                      | -55°C < T <sub>A</sub> < +125°C                                                     | -                        | -    | 200                      | μΑ    |

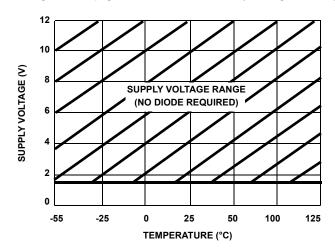

| Supply Voltage Range - High (Note 12) | V+ <sub>H</sub>      | R <sub>L</sub> = 10k, LV Open, T <sub>MIN</sub> < T <sub>A</sub> < T <sub>MAX</sub> | 3.0                      | -    | 12                       | V     |

| Supply Voltage Range - Low            | V+L                  | $R_L$ = 10k, LV to GND, $T_{MIN} < T_A < T_{MAX}$                                   | 1.5                      | -    | 3.5                      | V     |

| Output Source Resistance              | R <sub>OUT</sub>     | I <sub>OUT</sub> = 20mA                                                             | -                        | 60   | 100                      | Ω     |

|                                       |                      | I <sub>OUT</sub> = 20mA, 0°C < T <sub>A</sub> < +70°C                               | -                        | -    | 120                      | Ω     |

|                                       |                      | I <sub>OUT</sub> = 20mA, -25°C < T <sub>A</sub> < +85°C                             | -                        | -    | 120                      | Ω     |

|                                       |                      | I <sub>OUT</sub> = 20mA, -55°C < T <sub>A</sub> < +125°C                            | -                        | -    | 150                      | Ω     |

|                                       |                      | I <sub>OUT</sub> = 3mA, V+ = 2V, LV = GND,<br>0°C < T <sub>A</sub> < +70°C          | -                        | -    | 250                      | Ω     |

|                                       |                      | I <sub>OUT</sub> = 3mA, V+ = 2V, LV = GND,<br>-40°C < T <sub>A</sub> < +85°C        | -                        | -    | 300                      | Ω     |

|                                       |                      | I <sub>OUT</sub> = 3mA, V+ = 2V, LV = GND,<br>-55°C < T <sub>A</sub> < +125°C       | -                        | -    | 400                      | Ω     |

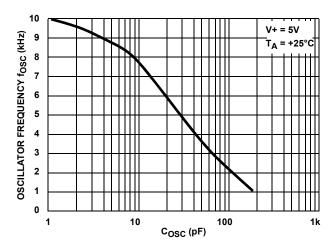

| Oscillator Frequency (Note 10)        | fosc                 | C <sub>OSC</sub> = 0, Pin 1 Open or GND                                             | 5                        | 10   | -                        | kHz   |

|                                       |                      | C <sub>OSC</sub> = 0, Pin 1 = V+                                                    | -                        | 35   | -                        | kHz   |

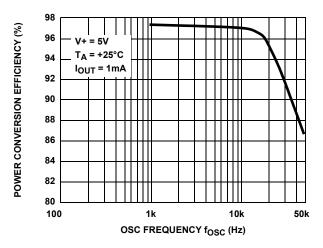

| Power Efficiency                      | P <sub>EFF</sub>     | $R_L = 5k\Omega$                                                                    | 96                       | 98   | -                        | %     |

|                                       |                      | $T_{MIN} < T_A < T_{MAX} R_L = 5k\Omega$                                            | 95                       | 97   | -                        | -     |

| Voltage Conversion Efficiency         | V <sub>OUT</sub> EFF | R <sub>L</sub> = ∞                                                                  | 99                       | 99.9 | -                        | %     |

**Electrical Specifications**ICL7660S and ICL7660A, V+ = 5V, T<sub>A</sub> = +25°C, OSC = Free running (see <u>Figure 12 on page 7</u>, <u>"ICL7660S Test Circuit"</u> and Figure <u>Figure 13 on page 7</u> <u>"ICL7660A Test Circuit"</u>), unless otherwise specified. **(Continued)**

| PARAMETER                                   | SYMBOL           | TEST CONDITIONS                                      | MIN<br>(Note 9) | TYP | MAX<br>(Note 9) | UNITS |

|---------------------------------------------|------------------|------------------------------------------------------|-----------------|-----|-----------------|-------|

| Oscillator Impedance                        | Z <sub>OSC</sub> | V+ = 2V                                              | -               | 1   | -               | ΜΩ    |

|                                             |                  | V+ = 5V                                              | -               | 100 | -               | kΩ    |

| ICL7660A, V+ = 3V, T <sub>A</sub> = 25°C, O | SC = Free rur    | nning, Test Circuit <u>Figure 13</u> , unless otherw | ise specified   | i   |                 |       |

| Supply Current (Note 13)                    | l+               | V+ = 3V, R <sub>L</sub> = ∞, +25°C                   | -               | 26  | 100             | μА    |

|                                             |                  | 0°C < T <sub>A</sub> < +70°C                         | -               | -   | 125             | μА    |

|                                             |                  | -40°C < T <sub>A</sub> < +85°C                       | -               | -   | 125             | μА    |

| Output Source Resistance                    | R <sub>OUT</sub> | V+ = 3V, I <sub>OUT</sub> = 10mA                     | -               | 97  | 150             | Ω     |

|                                             |                  | 0°C < T <sub>A</sub> < +70°C                         | -               | -   | 200             | Ω     |

|                                             |                  | -40°C < T <sub>A</sub> < +85°C                       | -               | -   | 200             | Ω     |

| Oscillator Frequency (Note 13)              | fosc             | V+ = 3V (same as 5V conditions)                      | 5.0             | 8   | -               | kHz   |

|                                             |                  | 0°C < T <sub>A</sub> < +70°C                         | 3.0             | -   | -               | kHz   |

|                                             |                  | -40°C < T <sub>A</sub> < +85°C                       | 3.0             | -   | -               | kHz   |

#### NOTES:

- 9. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 10. In the test circuit, there is no external capacitor applied to pin 7. However, when the device is plugged into a test socket, there is usually a very small but finite stray capacitance present, on the order of 5pF.

- 11. The ICL7660S and ICL7660A can operate without an external diode over the full temperature and voltage range. This device will function in existing designs that incorporate an external diode with no degradation in overall circuit performance.

- 12. All significant improvements over the industry standard ICL7660 are highlighted.

- 13. Derate linearly above  $50^{\circ}\text{C}$  by  $5.5\text{mW}/^{\circ}\text{C}$ .

## Functional Block Diagram

# **Typical Performance Curves**

See Figure 12 on page 7, "ICL7660S Test Circuit") and Figure 13 on page 7 "ICL7660A Test Circuit"

FIGURE 1. OPERATING VOLTAGE AS A FUNCTION OF TEMPERATURE

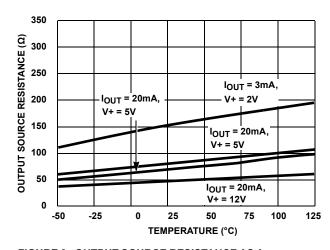

FIGURE 3. OUTPUT SOURCE RESISTANCE AS A FUNCTION OF TEMPERATURE

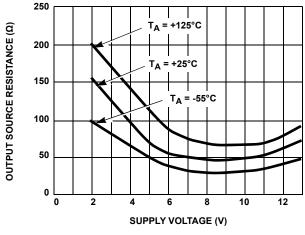

FIGURE 2. OUTPUT SOURCE RESISTANCE AS A FUNCTION OF SUPPLY VOLTAGE

FIGURE 4. POWER CONVERSION EFFICIENCY AS A FUNCTION OF OSCILLATOR FREQUENCY

## **Typical Performance Curves**

See Figure 12 on page 7, "ICL7660S Test Circuit") and Figure 13 on page 7, "ICL7660A Test Circuit" (Continued)

20

FIGURE 5. FREQUENCY OF OSCILLATION AS A FUNCTION OF EXTERNAL OSCILLATOR CAPACITANCE

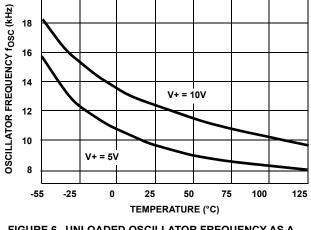

FIGURE 6. UNLOADED OSCILLATOR FREQUENCY AS A FUNCTION OF TEMPERATURE

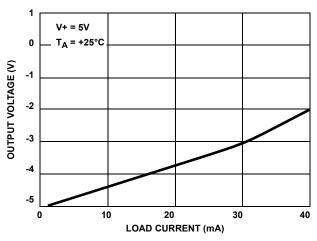

FIGURE 7. OUTPUT VOLTAGE AS A FUNCTION OF OUTPUT CURRENT

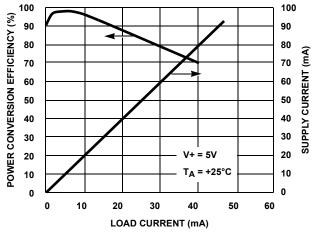

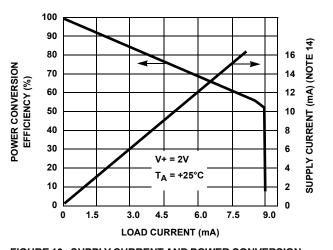

FIGURE 8. SUPPLY CURRENT AND POWER CONVERSION EFFICIENCY AS A FUNCTION OF LOAD CURRENT

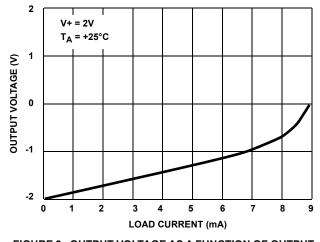

FIGURE 9. OUTPUT VOLTAGE AS A FUNCTION OF OUTPUT CURRENT

FIGURE 10. SUPPLY CURRENT AND POWER CONVERSION EFFICIENCY AS A FUNCTION OF LOAD CURRENT

## **Typical Performance Curves**

See Figure 12 on page 7, "ICL7660S Test Circuit") and Figure 13 on page 7, "ICL7660A Test Circuit" (Continued)

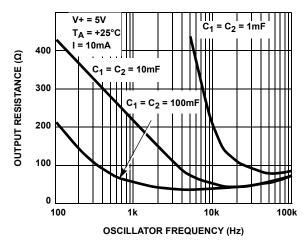

FIGURE 11. OUTPUT SOURCE RESISTANCE AS A FUNCTION OF OSCILLATOR FREQUENCY

#### NOTE:

14. These curves include, in the supply current, that current fed directly into the load R<sub>L</sub> from the V+ (see <u>Figure 12</u>). Thus, approximately half the supply current goes directly to the positive side of the load, and the other half, through the ICL7660S and ICL7660A, goes to the negative side of the load. Ideally, V<sub>OUT</sub>  $\simeq$  2V<sub>IN</sub>, I<sub>S</sub>  $\simeq$  2I<sub>L</sub>, so V<sub>IN</sub> x I<sub>S</sub>  $\simeq$  V<sub>OUT</sub> x I<sub>L</sub>.

NOTE: For large values of  $C_{\mbox{OSC}}$  (>1000pF), the values of  $C_1$  and  $C_2$  should be increased to 100µF.

FIGURE 12. ICL7660S TEST CIRCUIT

NOTE: For large values of C $_{OSC}$  (>1000pF) the values of C $_{1}$  and C $_{2}$  should be increased to 100µF.

FIGURE 13. ICL7660A TEST CIRCUIT

## **Detailed Description**

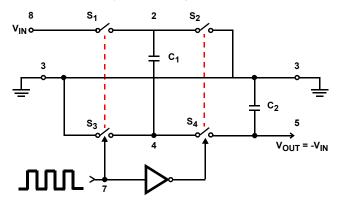

The ICL7660S and ICL7660A contain all the necessary circuitry to complete a negative voltage converter, with the exception of two external capacitors, which may be inexpensive  $10\mu F$  polarized electrolytic types. The mode of operation of the device may best be understood by considering Figure 14, which shows an idealized negative voltage converter. Capacitor  $C_1$  is charged to a voltage, V+, for the half cycle, when switches  $S_1$  and  $S_3$  are closed. (Note: Switches  $S_2$  and  $S_4$  are open during this half cycle). During the second half cycle of operation, switches  $S_2$  and  $S_4$  are closed, with  $S_1$  and  $S_3$  open, thereby shifting capacitor  $C_1$  to  $C_2$  such that the voltage on  $C_2$  is exactly V+, assuming ideal switches and no load on  $C_2$ . The ICL7660S and ICL7660A approach this ideal situation more closely than existing non-mechanical circuits.

FIGURE 14. IDEALIZED NEGATIVE VOLTAGE CONVERTER

In the ICL7660S and ICL7660A, the four switches of Figure 14 are MOS power switches;  $S_1$  is a P-Channel device; and  $S_2$ ,  $S_3$  and  $S_4$  are N-Channel devices. The main difficulty with this approach is that in integrating the switches, the substrates of  $S_3$  and  $S_4$  must always remain reverse biased with respect to their sources, but not so much as to degrade their "ON" resistances. In addition, at circuit start-up, and under output short circuit conditions ( $V_{OUT} = V_{+}$ ), the output voltage must be sensed and the substrate bias adjusted accordingly. Failure to accomplish this would result in high power losses and probable device latch-up.

This problem is eliminated in the ICL7660S and ICL7660A by a logic network that senses the output voltage ( $V_{OUT}$ ) together with the level translators, and switches the substrates of  $S_3$  and  $S_4$  to the correct level to maintain necessary reverse bias.

The voltage regulator portion of the ICL7660S and ICL7660A is an integral part of the anti-latchup circuitry; however, its inherent voltage drop can degrade operation at low voltages. Therefore, to improve low voltage operation, the "LV" pin should be connected to GND, thus disabling the regulator. For supply voltages greater than 3.5V, the LV terminal must be left open to ensure latchup-proof operation and to prevent device damage.

# Theoretical Power Efficiency Considerations

In theory, a voltage converter can approach 100% efficiency if certain conditions are met:

- 1. The drive circuitry consumes minimal power.

- 2. The output switches have extremely low ON resistance and virtually no offset.

- 3. The impedance of the pump and reservoir capacitors are negligible at the pump frequency.

The ICL7660S and ICL7660A approach these conditions for negative voltage conversion if large values of  $C_1$  and  $C_2$  are used. **ENERGY IS LOST ONLY IN THE TRANSFER OF CHARGE BETWEEN CAPACITORS IF A CHANGE IN VOLTAGE OCCURS**. The energy lost is defined as shown in Equation 1:

$$E = \frac{1}{2}C_1(V_1^2 - V_2^2)$$

(EQ. 1)

where  $V_1$  and  $V_2$  are the voltages on  $C_1$  during the pump and transfer cycles. If the impedances of  $C_1$  and  $C_2$  are relatively high at the pump frequency (see Figure 14) compared to the value of  $R_L$ , there will be a substantial difference in the voltages,  $V_1$  and  $V_2$ . Therefore it is not only desirable to make  $C_2$  as large as possible to eliminate output voltage ripple, but also to employ a correspondingly large value for  $C_1$  in order to achieve maximum efficiency of operation.

#### Do's and Don'ts

- 1. Do not exceed maximum supply voltages.

- Do not connect LV terminal to GND for supply voltage greater than 3.5V.

- Do not short circuit the output to V<sup>+</sup> supply for supply voltages above 5.5V for extended periods; however, transient conditions including start-up are okay.

- 4. When using polarized capacitors, the + terminal of  $C_1$  must be connected to pin 2 of the ICL7660S and ICL7660A, and the + terminal of  $C_2$  must be connected to GND.

- 5. If the voltage supply driving the ICL7660S and ICL7660A has a large source impedance ( $25\Omega$  to  $30\Omega$ ), then a  $2.2\mu$ F capacitor from pin 8 to ground may be required to limit the rate of rise of input voltage to less than  $2V/\mu s$ .

- If the input voltage is higher than 5V and it has a rise rate more than 2V/μs, an external Schottky diode from V<sub>OUT</sub> to CAP- is needed to prevent latchup (triggered by forward biasing Q4's body diode) by keeping the output (pin 5) from going more positive than CAP- (pin 4).

- 7. User should ensure that the output (pin 5) does not go more positive than GND (pin 3). Device latch-up will occur under these conditions. To provide additional protection, a 1N914 or similar diode placed in parallel with C<sub>2</sub> will prevent the device from latching up under these conditions, when the load on V<sub>OUT</sub> creates a path to pull up V<sub>OUT</sub> before the IC is active (anode pin 5, cathode pin 3).

## Typical Applications

### Simple Negative Voltage Converter

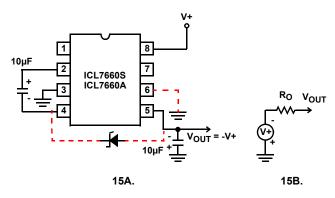

The majority of applications will undoubtedly utilize the ICL7660S and ICL7660A for generation of negative supply voltages. Figure 15 shows typical connections to provide a negative supply where a positive supply of +1.5V to +12V is available. Keep in mind that pin 6 (LV) is tied to the supply negative (GND) for supply voltage below 3.5V.

FIGURE 15. SIMPLE NEGATIVE CONVERTER AND ITS OUTPUT EQUIVALENT

The output characteristics of the circuit in Figure 15 can be approximated by an ideal voltage source in series with a resistance as shown in Figure 15B. The voltage source has a value of -(V+). The output impedance ( $R_O$ ) is a function of the ON resistance of the internal MOS switches (shown in Figure 14), the switching frequency, the value of  $C_1$  and  $C_2$ , and the ESR (equivalent series resistance) of  $C_1$  and  $C_2$ . A good first order approximation for  $R_O$  is shown in Equation 2:

$$R_0 \, \widetilde{=} \, 2((R_{SW1} + R_{SW3} + ESR_{C1}) + 2(R_{SW2} + R_{SW4} + ESR_{C1}))$$

$$\frac{1}{f_{\text{PUMP}} \times C_1} + \text{ESR}_{C2} \tag{EQ. 2}$$

$$f_{PUMP} = \frac{f_{OSC}}{2}$$

(R<sub>SWX</sub> = MOSFET Switch Resistance)

Combining the four  $R_{SWX}$  terms as  $R_{SW}$ , we see in Equation 3 that:

$$R_0 \approx 2xR_{SW} + \frac{1}{f_{PUMP} \times C_1} + 4xESR_{C1} + ESR_{C2}$$

(EQ. 3)

R<sub>SW</sub>, the total switch resistance, is a function of supply voltage and temperature (see the output source resistance graphs, Figures 2, 3, and 11), typically  $23\Omega$  at +25°C and 5V. Careful selection of C<sub>1</sub> and C<sub>2</sub> will reduce the remaining terms, minimizing the output impedance. High value capacitors will reduce the 1/(f<sub>PUMP</sub> x C<sub>1</sub>) component, and low ESR capacitors will lower the ESR term. Increasing the oscillator frequency will reduce the 1/(f<sub>PUMP</sub> x C<sub>1</sub>) term, but may have the side effect of a net increase in output impedance when C<sub>1</sub> > 10µF and is not long enough to fully charge the capacitors every cycle.

Equation 4 shows a typical application where  $f_{OSC}$  = 10kHz and  $C = C_1 = C_2 = 10\mu F$ :

$$R_0 \cong 2x23 + \frac{1}{5 \times 10^3 \times 10 \times 10^{-6}} + 4xESR_{C1} + ESR_{C2}$$

$$(EQ. 4)$$

$$R_0 \cong 46 + 20 + 5 \times ESR_{C}$$

Since the ESRs of the capacitors are reflected in the output impedance multiplied by a factor of 5, a high value could potentially swamp out a low  $1/f_{PUMP} \times C_1$  term, rendering an increase in switching frequency or filter capacitance ineffective. Typical electrolytic capacitors may have ESRs as high as  $10\Omega$ .

## **Output Ripple**

ESR also affects the ripple voltage seen at the output. The peak-to-peak output ripple voltage is given by Equation 5:

$$V_{RIPPLE} \cong \left(\frac{1}{2 \times f_{PUMP} \times C_2} + 2ESR_{C2} \times I_{OUT}\right)$$

(EQ. 5)

A low ESR capacitor will result in a higher performance output.

### Paralleling Devices

Any number of ICL7660S and ICL7660A voltage converters may be paralleled to reduce output resistance. The reservoir capacitor,  $C_2$ , serves all devices, while each device requires its own pump capacitor,  $C_1$ . The resultant output resistance is approximated in Equation 6:

$$R_{OUT} = \frac{R_{OUT(of ICL7660S)}}{n(number of devices)}$$

(EQ. 6)

### Cascading Devices

The ICL7660S and ICL7660A may be cascaded as shown to produce larger negative multiplication of the initial supply voltage. However, due to the finite efficiency of each device, the practical limit is 10 devices for light loads. The output voltage is defined as shown in Equation 7:

$$V_{OUT} = -n(V_{IN})$$

(EQ. 7)

where n is an integer representing the number of devices cascaded. The resulting output resistance would be approximately the weighted sum of the individual ICL7660S and ICL7660A  $R_{OUT}$  values.

# Changing the ICL7660S and ICL7660A Oscillator Frequency

It may be desirable in some applications, due to noise or other considerations, to alter the oscillator frequency. This can be achieved simply by one of several methods.

By connecting the Boost Pin (Pin 1) to V+, the oscillator charge and discharge current is increased and, hence, the oscillator frequency is increased by approximately 3.5 times. The result is a decrease in the output impedance and ripple. This is of major importance for surface mount applications where capacitor size and cost are critical. Smaller capacitors, such as

$0.1\mu F$ , can be used in conjunction with the Boost Pin to achieve similar output currents compared to the device free running with  $C_1 = C_2 = 10\mu F$  or  $100\mu F$ . (see Figure 11).

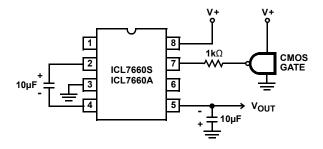

Increasing the oscillator frequency can also be achieved by overdriving the oscillator from an external clock, as shown in Figure 16. In order to prevent device latchup, a  $1 k\Omega$  resistor must be used in series with the clock output. In a situation where the designer has generated the external clock frequency using TTL logic, the addition of a  $10 k\Omega$  pull-up resistor to V+ supply is required. Note that the pump frequency with external clocking, as with internal clocking, will be one-half of the clock frequency. Output transitions occur on the positive going edge of the clock.

FIGURE 16. EXTERNAL CLOCKING

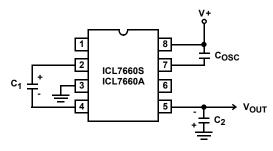

It is also possible to increase the conversion efficiency of the ICL7660S and ICL7660A at low load levels by lowering the oscillator frequency. This reduces the switching losses, and is shown in Figure 17. However, lowering the oscillator frequency will cause an undesirable increase in the impedance of the pump (C<sub>1</sub>) and reservoir (C<sub>2</sub>) capacitors; this is overcome by increasing the values of C<sub>1</sub> and C<sub>2</sub> by the same factor by which the frequency has been reduced. For example, the addition of a 100pF capacitor between pin 7 (OSC and V+) will lower the oscillator frequency to 1kHz from its nominal frequency of 10kHz (a multiple of 10), and thereby necessitate a corresponding increase in the value of C<sub>1</sub> and C<sub>2</sub> (from 10µF to 100µF).

FIGURE 17. LOWERING OSCILLATOR FREQUENCY

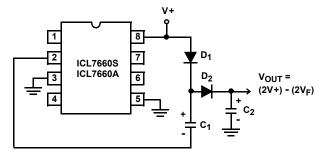

### Positive Voltage Doubling

The ICL7660S and ICL7660A may be employed to achieve positive voltage doubling using the circuit shown in Figure 18. In this application, the pump inverter switches of the ICL7660S and ICL7660A are used to charge  $C_1$  to a voltage level of V+ -

$V_F$ , where V+ is the supply voltage and  $V_F$  is the forward voltage on  $C_1$ , plus the supply voltage (V+) is applied through diode  $D_2$  to capacitor  $C_2$ . The voltage thus created on  $C_2$  becomes (2V+) - (2V<sub>F</sub>) or twice the supply voltage minus the combined forward voltage drops of diodes  $D_1$  and  $D_2$ .

The source impedance of the output ( $V_{OUT}$ ) will depend on the output current, but for V+ = 5V and an output current of 10mA, it will be approximately  $60\Omega$ .

NOTE: D<sub>1</sub> AND D<sub>2</sub> CAN BE ANY SUITABLE DIODE.

FIGURE 18. POSITIVE VOLTAGE DOUBLER

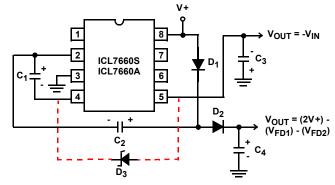

# Combined Negative Voltage Conversion and Positive Supply Doubling

Figure 19 combines the functions shown in Figure 15 and Figure 18 to provide negative voltage conversion and positive voltage doubling simultaneously. This approach would be suitable, for example, for generating +9V and -5V from an existing +5V supply. In this instance, capacitors  $C_1$  and  $C_3$  perform the pump and reservoir functions, respectively, for negative voltage generation, while capacitors  $C_2$  and  $C_4$  are pump and reservoir, respectively, for the doubled positive voltage. There is a penalty in this configuration which combines both functions, however, in that the source impedances of the generated supplies will be somewhat higher, due to the finite impedance of the common charge pump driver at pin 2 of the device.

FIGURE 19. COMBINED NEGATIVE VOLTAGE CONVERTER AND POSITIVE DOUBLER

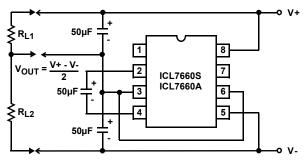

## Voltage Splitting

The bidirectional characteristics can also be used to split a high supply in half, as shown in Figure 20. The combined load will be evenly shared between the two sides, and a high value

resistor to the LV pin ensures start-up. Because the switches share the load in parallel, the output impedance is much lower than in the standard circuits, and higher currents can be drawn from the device. By using this circuit, and then the circuit of Figure 15, +15V can be converted, via +7.5 and -7.5, to a nominal -15V, although with rather high series output resistance ( $\sim\!250\Omega)$ .

FIGURE 20. SPLITTING A SUPPLY IN HALF

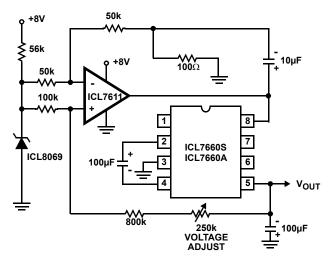

## Regulated Negative Voltage Supply

In some cases, the output impedance of the ICL7660S and ICL7660A can be a problem, particularly if the load current varies substantially. The circuit of Figure 21 can be used to overcome this by controlling the input voltage, via an ICL7611 low-power CMOS op amp, in such a way as to maintain a nearly constant output voltage. Direct feedback is inadvisable, since the ICL7660S's and ICL7660A's output does not respond instantaneously to change in input, but only after the switching delay. The circuit shown supplies enough delay to accommodate the ICL7660S and ICL7660A, while maintaining adequate feedback. An increase in pump and storage capacitors is desirable, and the values shown provide an output impedance of less than  $5\Omega$  to a load of 10mA.

## Other Applications

Further information on the operation and use of the ICL7660S and ICL7660A may be found in application note <u>AN051</u>, <u>"Principles and Applications of the ICL7660 CMOS Voltage Converter"</u>.

FIGURE 21. REGULATING THE OUTPUT VOLTAGE

## **Revision History**

| Rev. | Date | Description                                                                    |  |  |

|------|------|--------------------------------------------------------------------------------|--|--|

| 7.01 |      | Updated Ordering Information table. Added Revision History Updated Disclaimer. |  |  |

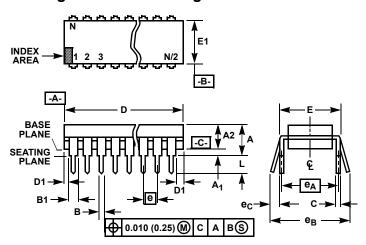

## Package Outline Drawings

### NOTES:

- Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-.

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

For the most recent package outline drawing, see <u>E8.3</u>.

## E8.3 (JEDEC MS-001-BA ISSUE D) 8 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INCHES MILLIMETERS |       |          |       |       |

|----------------|--------------------|-------|----------|-------|-------|

| SYMBOL         | MIN                | MAX   | MIN      | MAX   | NOTES |

| Α              | -                  | 0.210 | -        | 5.33  | 4     |

| A1             | 0.015              | -     | 0.39     | -     | 4     |

| A2             | 0.115              | 0.195 | 2.93     | 4.95  | -     |

| В              | 0.014              | 0.022 | 0.356    | 0.558 | -     |

| B1             | 0.045              | 0.070 | 1.15     | 1.77  | 8, 10 |

| С              | 0.008              | 0.014 | 0.204    | 0.355 | -     |

| D              | 0.355              | 0.400 | 9.01     | 10.16 | 5     |

| D1             | 0.005              | -     | 0.13     | -     | 5     |

| Е              | 0.300              | 0.325 | 7.62     | 8.25  | 6     |

| E1             | 0.240              | 0.280 | 6.10     | 7.11  | 5     |

| е              | 0.100              | BSC   | 2.54     | BSC   | -     |

| e <sub>A</sub> | 0.300              | BSC   | 7.62 BSC |       | 6     |

| e <sub>B</sub> | -                  | 0.430 | -        | 10.92 | 7     |

| L              | 0.115              | 0.150 | 2.93     | 3.81  | 4     |

| N              | 8                  | 3     | 8        |       | 9     |

Rev. 0 12/93

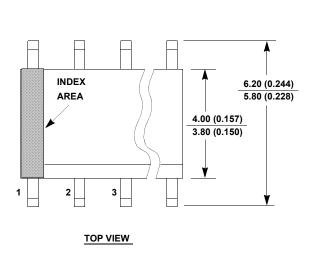

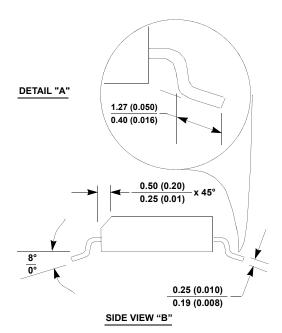

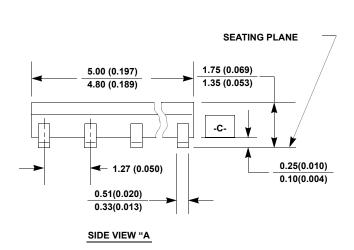

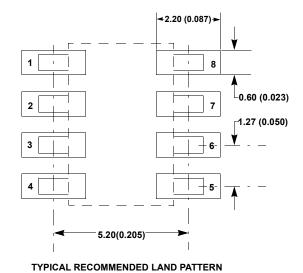

M8.15

8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE Rev 4, 1/12

For the most recent package outline drawing, see M8.15.

### NOTES:

- 1. Dimensioning and tolerancing per ANSI Y14.5M-1994.

- Package length does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Package width does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 4. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 5. Terminal numbers are shown for reference only.

- The lead width as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

- 8. This outline conforms to JEDEC publication MS-012-AA ISSUE C.

### **Notice**

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products

and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your

product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of

these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or

- 4. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 6. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.4.0-1 November 2017)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Renesas(瑞萨)