# **Automotive CIS/CCM PMIC for Ultra Compact Camera and High Image Quality System**

## **General Description**

The RTQ2076 is an integrated PMIC with three step down converters and one high PSRR low-dropout (LDO) regulator for automotive camera applications. The high-voltage step down converter is operated with input voltage range up to 18.5V for Power Over Coax (POC) connection. Two low-voltage step down converters provide constant output voltage. All step down converters operate in a forced fixed-frequency PWM mode. The LDO output voltage is easily set via an external resistor. The RTQ2076 provides 10 power sequences by a resistor for flexibility. The RTQ2076 is available in a WETD-VQFN-16L 3x3 package with dimple lead type wettable flanks.

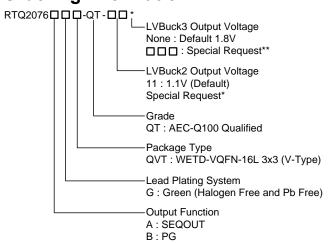

## **Ordering Information**

#### Note:

\*Special Request : Available voltage between 0.6V to 2.1V with 100mV step under specific business agreement.

\*\*Special Request : For example, 095 means 0.95V. Richtek products are :

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ► Suitable for use in SnPb or Pb-free soldering processes.

### **Features**

- AEC-Q100 Grade 1

- FMEA Compliant Pin Placement and Protection Mechanisms

- Three Step-Down Converters (HVBuck1, LVBuck2 and LVBuck3)

- **▶** Peak Current Mode PWM Operation

- ▶ Fixed Switching Frequency at 2.1MHz

- ► EMI Reduction with Spread Spectrum and Phase Shift

- ► HVBuck1 Input Voltage from 4V to 18.5V, Adjustable Output Voltage and Up to 2A Output Current

- ► LVBuck2 Input Voltage from 2.7V to 5V, Fixed Output Voltage and 1.5A Output Current

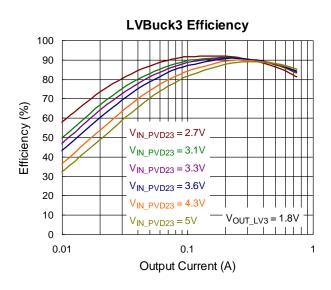

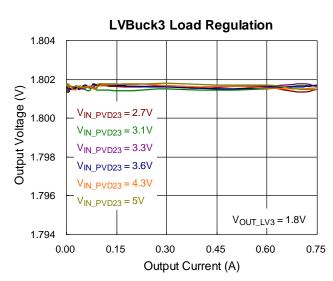

- ▶ LVBuck3 Input Voltage from 2.7V to 5V, Fixed Output Voltage and 750mA Output Current

- ► Pins Related to LVBuck2/LVBuck3 Allowable Floating if Channel Unused

- Low Dropout Regulator (LDO)

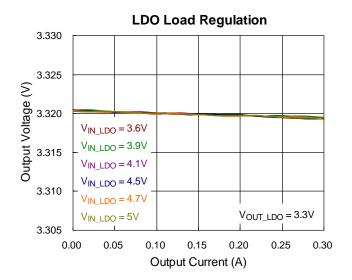

- ► Input Voltage from 2.7V to 5V and 300mA Output Current

- ▶ 10 Adjustable Output Voltage Settings via RSET Pin

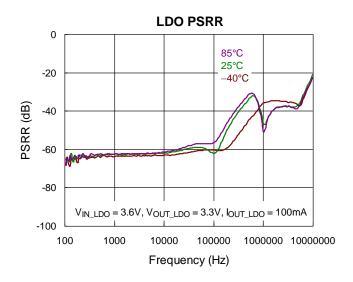

- ▶ High PSRR: 60dB at 100kHz, 40dB at 1MHz

- Output Function

- Sequence Control for External Power IC via SEQOUT (RTQ2076A-QT)

- ► Power Status Indication via PG (RTQ2076B-QT)

- 10 Flexible Power Sequence Settings via SEQ

Pin

- Small Form Factor WETD-VQFN-16L 3x3

Wettable Flanks Package

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

## **Applications**

- Automotive Camera Modules

- ▶ Surround View Camera

- ▶ Front View Camera

- ▶ Rear View Camera

- ▶ Dash Cam DVR

- ▶ Driver Monitoring System

- ► Cabin Monitor

- ▶ eMirror

## **Marking Information**

RTQ2076AGQVT-QT-11

SP=: Product Code YMDNN: Date Code

RTQ2076BGQVT-QT-11

SN=: Product Code YMDNN: Date Code

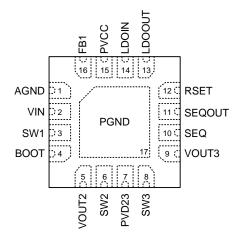

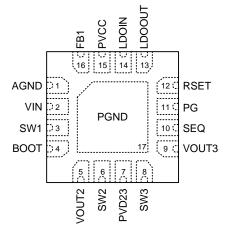

## **Pin Configuration**

(TOP VIEW)

WETD-VQFN-16L 3x3 (RTQ2076A-QT)

WETD-VQFN-16L 3x3 (RTQ2076B-QT)

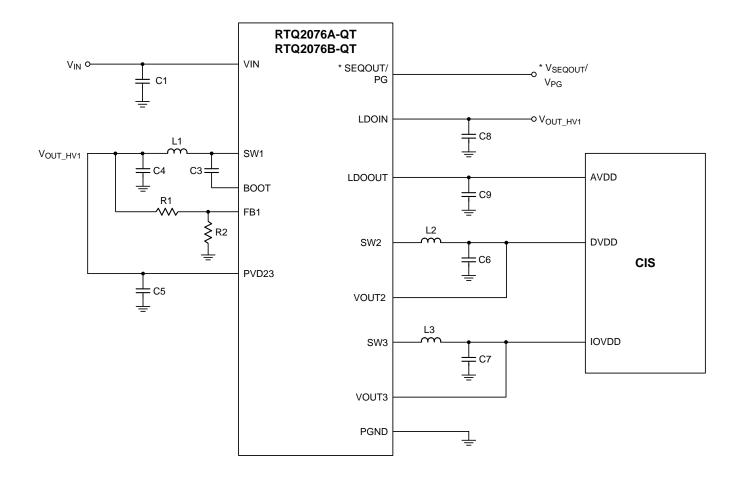

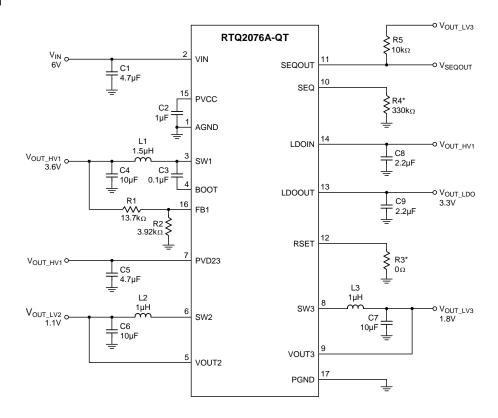

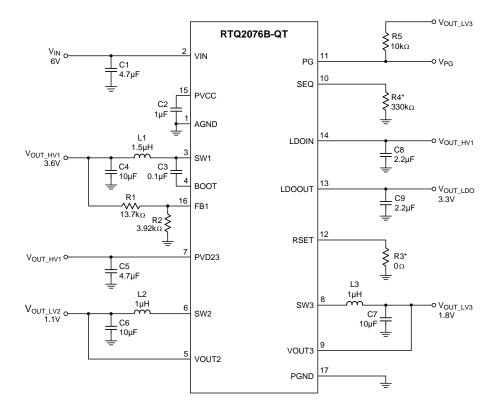

## **Simplified Application Circuit**

<sup>\*</sup> SEQOUT pinout is for RTQ2076A-QT; PG pinout is for RTQ2076B-QT.

## **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                                   |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------|

| 1       | AGND     | Analog ground.                                                                                                                 |

| 2       | VIN      | Supply voltage input of HVBuck1. Connect a 4.7µF or larger decouple ceramic capacitor between this pin and ground.             |

| 3       | SW1      | HVBuck1 switch node.                                                                                                           |

| 4       | воот     | Bootstrap capacitor connection pin for HVBuck1. Connect a 0.1μF ceramic capacitor between this pin and SW1.                    |

| 5       | VOUT2    | Output voltage feedback input of LVBuck2. Directly connect the output capacitor node to this pin for better regulation.        |

| 6       | SW2      | LVBuck2 switch node.                                                                                                           |

| 7       | PVD23    | Supply voltage input of LVBuck2 and LVBuck3. Connect a 4.7µF or larger decouple ceramic capacitor between this pin and ground. |

| 8       | SW3      | LVBuck3 switch node.                                                                                                           |

| Pin No.             | Pin Name | Pin Function                                                                                                                                                   |

|---------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9                   | VOUT3    | Output voltage feedback input of LVBuck3. Directly connect the output capacitor node to this pin for better regulation.                                        |

| 10                  | SEQ      | Power sequence selection.                                                                                                                                      |

|                     | SEQOUT   | Sequence control output with open drain structure for external power IC. (RTQ2076A-QT)                                                                         |

| 11                  | PG       | Power status indication pin with open drain structure for HVBuck1, LVBuck2, LVBuck3 and LDO. PG at high state indicates all outputs work well. (RTQ2076B-QT)   |

| 12                  | RSET     | LDO output voltage selection.                                                                                                                                  |

| 13                  | LDOOUT   | LDO output. Connect a $2.2\mu\text{F}$ ceramic decouple capacitor between this pin and ground.                                                                 |

| 14                  | LDOIN    | Supply voltage input of LDO. Connect a 2.2µF or larger decouple ceramic capacitor between this pin and ground.                                                 |

| 15                  | PVCC     | Internal analog power output. Connect a 1µF ceramic decouple capacitor between this pin and ground. Note additional external loading on this pin is forbidden. |

| 16                  | FB1      | Output voltage feedback input of HVBuck1.                                                                                                                      |

| 17<br>(Exposed Pad) | PGND     | IC thermal pad and power ground. It must connect to main ground plane for proper operation.                                                                    |

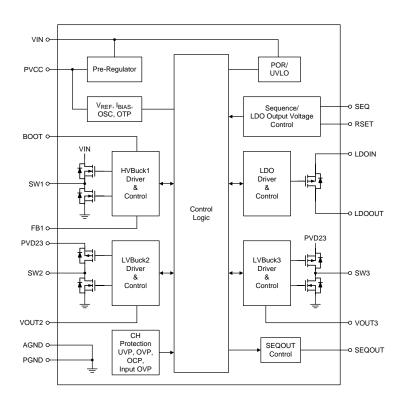

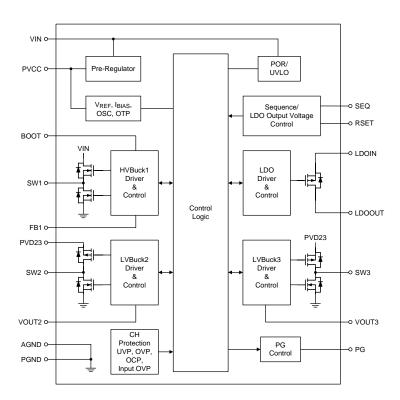

## **Functional Block Diagram**

#### RTQ2076A-QT

#### RTQ2076B-QT

DSQ2076-QT-00 December 2021

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

Downloaded From Oneyac.com

www.richtek.com

## **Operation**

RTQ2076A-QT/RTQ2076B-QT is highly integrated power-management integrated circuit (PMIC) for automotive camera system, which includes three step-down converters (CH1 HVBuck1, CH2 LVBuck2, CH3 LVBuck3) and one generic LDO (CH4 LDO).

## System Under-Voltage Protection and Over-Voltage **Protection**

The RTQ2076A-QT/RTQ2076B-QT stops operating if VIN voltage falls below the Under-Voltage Lock Out level (UVLO\_L). There is a typical 500mV hysteresis implemented to avoid unstable on/off behaviors. The device is initialized in its default state after V<sub>IN</sub> voltage recovering from UVLO\_H. When V<sub>IN</sub> voltage reaches the Over-Voltage Protection level, the step-down converters, LDO and SEQOUT (RTQ2076A-QT) are disabled immediately. Then the IC enters into latch off state and only can re-start with V<sub>IN</sub> ON/OFF. Meanwhile, the PG status will be also set to 0V to indicate IC fault condition.

#### **Thermal Protection**

The RTQ2076A-QT/RTQ2076B-QT features an overtemperature protection (OTP). When the junction temperature is higher than 160°C typical value, OTP is triggered to disable all outputs and the device enters into a latch off state. When the RTQ2076A-QT/ RTQ2076B-QT recovers from OTP, the device only can re-start with V<sub>IN</sub> ON/OFF.

#### **Pre-Regulator**

The device integrates a 4.45V linear regulator (PVCC) supplied by V<sub>IN</sub> to provide power to the internal circuitry. The PVCC can be used as the RSET and SEQ pull-up supply but it is "NOT" allowed to power other device or circuitry. A 1µF decoupling capacitor must be connected between PVCC and AGND to filter the noise and it needs to be placed as close as possible to the PVCC pin.

#### **Peak Current Mode Control**

The three step-down converters utilize the peak current mode control. An internal oscillator initiates turn-on of the high-side MOSFET switch. At the beginning of each

clock cycle, the internal high-side MOSFET switch turns on, allowing current to ramp up in the inductor. With comparisons of the inductor peak current signal during high-side MOSFET switch on interval and the internal compensation signal derived from the sensed feedback voltage with reference voltage, the high-side MOSFET switch is turned off and inductor current continues to flow through the low-side MOSFET switch. This cycle repeats at the next clock cycle. In this way, the regulated inductor current controls duty-cycle and output voltage of the converter.

#### Spread-Spectrum Operation

Due to the periodicity of the switching signal, the energy concentrates in one particular frequency and its harmonics. The energy is radiated and possible to result in a potential EMI issue. The RTQ2076A-QT/ RTQ2076B-QT equips a spread-spectrum function to meet CISPR and automotive EMI compliances. The spread-spectrum function is implemented by a pseudo random sequence and uses +6% spread of the switching frequency. For example, when the switching frequency typical value is 2.1MHz, the frequency range varies from 2.1MHz to 2.226MHz. Therefore, the RTQ2076A-QT/RTQ2076B-QT can guarantee that the 2.1MHz switching frequency does not drop into the 1.8MHz AM band limit.

#### **Phase-Shifted Operation**

The RTQ2076A-QT/RTQ2076B-QT supports phase shift operations among the step-down converters for further easing the simultaneous switching energy radiation quantity. The internal clock is automatically shifted to different respective sub-clocks for step-down converters. For example, when two step-down converters application, the beginning turn-on time between two high-side MOSFETs will have a 180degree phase difference. Likewise, a 120-degree phase difference when three step-down converters.

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

#### **Allowable Channel Floating**

For saving PCB layout space and material cost, the unused low-voltage step-down converter (CH2/CH3) is allowable to pin (SW2/SW3) floating without any inductor and output capacitor placement. The pin PVD23 is required to connect to a fixed voltage for floating detection and it is allowable without capacitor placement. The RTQ2076A-QT/RTQ2076B-QT automatically detects pin status during power-on procedure to determine whether the channel is used or not. In addition, the related failures on unused channels do not affect the device operation.

#### **Power Good Indication**

The RTQ2076B-QT features an open-drain powergood output (PG) to monitor the output voltage status. Connect a pull-up resistor from PG pin to an external voltage. Note it is forbidden to use PVCC as pulled-up voltage of PG pin. When the last channel of power-on sequence reaches 90% of its target output voltage, the PG signal is pulled up to indicate "Power Good" status after 10ms tills to device disabled or any other protection happens.

#### **External Control Output**

The RTQ2076A-QT features an open-drain external control output (SEQ) for external device. Connect a pull-up resistor from SEQ pin to an external voltage. Note it is forbidden to use PVCC as pulled-up voltage of SEQ pin. Referring to Table 3 for further information about power-on sequence.

**Table 1. Unused Channel Pin Connection**

| Unused Channel | Unused Pin Number | Unused Pin Name        | Pin Configuration |

|----------------|-------------------|------------------------|-------------------|

|                | 5                 | VOUT2                  | Floating          |

| LVBuck2        | 6                 | SW2                    | Floating          |

|                | 7                 | PVD23 Connect to volta |                   |

|                | 7                 | 7 PVD23                |                   |

| LVBuck3        | 8                 | SW3                    | Floating          |

|                | 9                 | VOUT3                  | Floating          |

Absolute Maximum Ratings (Note 1)

• Package Thermal Resistance (Note 2)

## • SW1 ------ -0.3V to 24V • BOOT ------ -0.3V to 28V • VOUT2, PVD23, VOUT3, SEQ, SEQOUT (RTQ2076A-QT), PG (RTQ2076B-QT), RSET, LDOOUT, LDOIN, PVCC, FB1 ------ -0.3V to 6.5V

Power Dissipation, PD @ TA = 25°C WETD-VQFN-16L 3x3 ------ 4.16W

WETD-VQFN-16L 3x3, θJA ------ 30°C/W WETD-VQFN-16L 3x3, θJC ------ 4.4°C/W

• Lead Temperature (Soldering, 10 sec.)------ 260°C • Junction Temperature ------ 150°C

ESD Susceptibility (Note 3) HBM (Human Body Model) ------ 2kV

#### **Recommended Operating Conditions** (Note 4)

• Supply Voltage, V<sub>IN</sub>------ 4V to 18.5V

• Supply Voltage, V<sub>PVD23</sub>, V<sub>LDOIN</sub>------ 2.7V to 5V

• Ambient Temperature Range------ -40°C to 125°C

#### **Electrical Characteristics**

(T<sub>A</sub> = T<sub>J</sub> = -40°C to 125°C, V<sub>IN</sub> = 6V, V<sub>OUT HV1</sub> = 3.6V, V<sub>OUT LV2</sub> = 1.1V, V<sub>OUT LV3</sub> = 1.8V, V<sub>OUT LD0</sub> = 3.3V, unless otherwise specified)

| Parameter                     | Symbol             | Test Conditions                                                                                       | Min  | Тур | Max  | Unit |

|-------------------------------|--------------------|-------------------------------------------------------------------------------------------------------|------|-----|------|------|

| System                        |                    |                                                                                                       |      |     |      |      |

| Under-Voltage                 | UVLO_H             | V <sub>IN</sub> rising                                                                                | 3.6  | 3.8 | 4    | V    |

| Lockout Threshold             | UVLO_L             | V <sub>IN</sub> falling                                                                               | 3.15 | 3.3 | 3.45 | V    |

| Input Over-Voltage Protection | V <sub>IN_OV</sub> |                                                                                                       | 18.6 | 20  | 21.5 | V    |

| CH1 HVBuck1                   |                    |                                                                                                       |      |     |      |      |

| Input Voltage<br>Range        | VIN                |                                                                                                       | 4    |     | 18.5 | V    |

| Output Voltage<br>Range       | Vout_HV1           | Buck mode operation. Switching frequency, minimum on time and minimum off time need to be considered. | 2.7  |     | 5    | V    |

| Parameter                                           | Symbol                  | Test Conditions           | Min   | Тур | Max   | Unit     |

|-----------------------------------------------------|-------------------------|---------------------------|-------|-----|-------|----------|

| Output Feedback<br>Voltage Accuracy                 | V <sub>FB1</sub>        |                           | 0.788 | 0.8 | 0.812 | V        |

| Switching<br>Frequency                              | fsw_HV1                 |                           | 1.89  | 2.1 | 2.31  | MHz      |

| Spread-Spectrum<br>Range                            | SS_HV1                  |                           |       | 6   |       | %        |

| Switching Minimum On Time                           | ton_MIN_HV1             |                           |       |     | 55    | ns       |

| Switching Minimum<br>Off Time                       | toff_MIN_HV1            |                           |       |     | 50    | ns       |

| High-Side MOSFET On Resistance                      | Ron_Hs_HV1              | From VIN pin to SW1 pin   | 115   | 210 | 340   | mΩ       |

| Low-Side MOSFET<br>On Resistance                    | RON_LS_HV1              | From SW1 pin to PGND pin  | 40    | 110 | 200   | mΩ       |

| Inductor Peak<br>Current Limit                      | ICL_PK_HV1              |                           | 2.4   | 3   | 3.6   | А        |

| Inductor Valley<br>Current Limit                    | ICL_VL_HV1              |                           |       | 2.7 |       | Α        |

| Negative Inductor<br>Peak Current Limit             | ICL_NPK_HV1             |                           | 1     | 2.5 | 4     | Α        |

| Output Discharge<br>Resistor                        | RDIS_HV1                |                           | 230   | 270 | 360   | Ω        |

| Output<br>Under-Voltage<br>Falling Threshold        | UVP_F_HV1               |                           | 40    | 50  | 60    | %        |

| Output Feedback<br>Over-Voltage Rising<br>Threshold | OVP_R_HV1               |                           |       | 110 |       | %        |

| CH2 LVBuck2 (V <sub>IN_P</sub>                      | <sub>VD23</sub> = 3.6V) |                           |       |     |       |          |

| Input Voltage<br>Range                              | V <sub>IN_PVD23</sub>   |                           | 2.7   |     | 5     | <b>V</b> |

| Output Voltage                                      | Vout_Lv2                |                           |       | 1.1 |       | V        |

| Output Voltage<br>Accuracy                          | Vout_acc_lv2            |                           | -1.5  |     | 1.5   | %        |

| Switching<br>Frequency                              | fsw_Lv2                 |                           | 1.89  | 2.1 | 2.31  | MHz      |

| Spread-Spectrum<br>Range                            | SS_LV2                  |                           |       | 6   |       | %        |

| Switching Minimum<br>On Time                        | ton_min_lv2             |                           |       |     | 44    | ns       |

| High-Side MOSFET On Resistance                      | RON_HS_LV2              | From PVD23 pin to SW2 pin | 110   | 150 | 202   | mΩ       |

| Low-Side MOSFET<br>On Resistance                    | R <sub>ON_LS_LV2</sub>  | From SW2 pin to PGND pin  | 60    | 90  | 133   | mΩ       |

| Inductor Peak<br>Current Limit                      | ICL_PK_LV2              |                           | 1.8   | 2.2 | 2.6   | А        |

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DSQ2076-QT-00 December 2021 www.richtek.com

| Parameter                                    | Symbol                  | Test Conditions               | Min  | Тур  | Max  | Unit |

|----------------------------------------------|-------------------------|-------------------------------|------|------|------|------|

| Inductor Valley<br>Current Limit             | ICL_VL_LV2              |                               |      | 1.8  |      | А    |

| Negative Inductor<br>Peak Current Limit      | ICL_NPK_LV2             |                               | 0.7  | 1.7  | 2.9  | Α    |

| Output Discharge<br>Resistor                 | R <sub>DIS_LV2</sub>    |                               | 6    | 9    | 14   | Ω    |

| Output<br>Under-Voltage<br>Falling Threshold | UVP_F_LV2               |                               | 40   | 50   | 60   | %    |

| Output<br>Over-Voltage Rising<br>Threshold   | OVP_R_LV2               |                               |      | 120  |      | %    |

| Output<br>Over-Voltage<br>Falling Threshold  | OVP_F_LV2               |                               |      | 110  |      | %    |

| Input Over-Voltage<br>Rising Threshold       | OVP_IN_R_LV2            |                               | 5.35 | 5.8  | 6.25 | V    |

| Input Over-Voltage<br>Hysteresis             | OVP_IN_HYS_LV2          | V <sub>IN_PVD23</sub> falling |      | 580  |      | mV   |

| CH3 LVBuck3 (V <sub>IN_P</sub>               | <sub>VD23</sub> = 3.6V) |                               |      |      |      |      |

| Input Voltage<br>Range                       | VIN_PVD23               |                               | 2.7  |      | 5    | V    |

| Output Voltage                               | V <sub>OUT_LV3</sub>    |                               |      | 1.8  |      | V    |

| Output Voltage<br>Accuracy                   | Vout_acc_lv3            |                               | -1.5 |      | 1.5  | %    |

| Switching<br>Frequency                       | f <sub>SW_LV3</sub>     |                               | 1.89 | 2.1  | 2.31 | MHz  |

| Spread-Spectrum<br>Range                     | SS_LV3                  |                               |      | 6    |      | %    |

| Switching Minimum On Time                    | ton_min_lv3             |                               |      |      | 44   | ns   |

| High-Side MOSFET On Resistance               | RON_HS_LV3              | From PVD23 pin to SW3 pin     | 240  | 310  | 423  | mΩ   |

| Low-Side MOSFET<br>On Resistance             | R <sub>ON_LS_LV3</sub>  | From SW3 pin to PGND pin      | 170  | 230  | 344  | mΩ   |

| Inductor Peak<br>Current Limit               | ICL_PK_LV3              |                               | 0.96 | 1.2  | 1.44 | Α    |

| Inductor Valley<br>Current Limit             | ICL_VL_LV3              |                               |      | 1.08 |      | Α    |

| Negative Inductor<br>Peak Current Limit      | ICL_NPK_LV3             |                               | 0.7  | 1.7  | 2.9  | Α    |

| Output Discharge<br>Resistor                 | R <sub>DIS_LV3</sub>    |                               | 7    | 10   | 15   | Ω    |

| Output<br>Under-Voltage<br>Falling Threshold | UVP_F_LV3               |                               | 40   | 50   | 60   | %    |

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

| Parameter                                    | Symbol                    | Test Conditions                                                                           | Min  | Тур  | Max  | Unit |

|----------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| Output<br>Over-Voltage Rising<br>Threshold   | OVP_R_LV3                 |                                                                                           |      | 120  |      | %    |

| Output<br>Over-Voltage<br>Falling Threshold  | OVP_F_LV3                 |                                                                                           |      | 110  |      | %    |

| Input Over-Voltage<br>Rising Threshold       | OVP_IN_R_LV3              |                                                                                           | 5.35 | 5.8  | 6.25 | V    |

| Input Over-Voltage<br>Hysteresis             | OVP_IN_HYS_LV3            | V <sub>IN_PVD23</sub> falling                                                             |      | 580  |      | mV   |

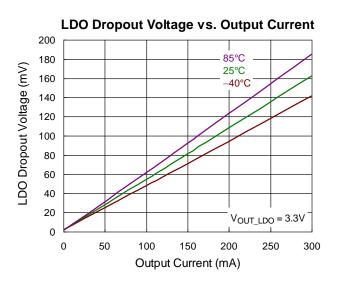

| CH4 LDO (V <sub>IN_LDO</sub> =               | 3.6V)                     |                                                                                           |      |      |      |      |

| Input Voltage<br>Range                       | V <sub>IN_LDO</sub>       |                                                                                           | 2.7  |      | 5    | ٧    |

| Output Voltage<br>Range                      | V <sub>OUT_LDO</sub>      | V <sub>OUT_LDO</sub> setting via RSET                                                     | 1.8  |      | 3.5  | V    |

| Output Voltage<br>Accuracy                   | Vout_acc_ldo              | V <sub>IN_LDO</sub> - V <sub>OUT_LDO</sub> > 0.3V,<br>I <sub>OUT_LDO</sub> = 0mA to 300mA | -1.5 |      | 1.5  | %    |

| Maximum Output<br>Current                    | lout_max_ldo              |                                                                                           | 300  |      |      | mA   |

| Dropout Voltago                              | V <sub>DROP_300_LDO</sub> | I <sub>OUT_LDO</sub> = 300mA (Note 5)                                                     |      |      | 300  | mV   |

| Dropout Voltage                              | VDROP_150_LDO             | I <sub>OUT_LDO</sub> = 150mA (Note 5)                                                     |      |      | 150  | IIIV |

| Output Current<br>Limit                      | ICL_LDO                   |                                                                                           | 345  | 450  | 555  | mA   |

| Output Discharge<br>Resistor                 | Rdis_ldo                  |                                                                                           | 48   | 76   | 104  | Ω    |

| Output<br>Under-Voltage<br>Falling Threshold | UVP_F_LDO                 |                                                                                           | 30   | 40   | 50   | %    |

| Output<br>Over-Voltage Rising<br>Threshold   | OVP_R_LDO                 |                                                                                           |      | 125  |      | %    |

| Output<br>Over-Voltage<br>Falling Threshold  | OVP_F_LDO                 |                                                                                           |      | 110  |      | %    |

| Input Over-Voltage<br>Rising Threshold       | OVP_IN_R_LDO              |                                                                                           | 5.35 | 5.8  | 6.25 | V    |

| Input Over-Voltage<br>Hysteresis             | OVP_IN_HYS_LDO            | V <sub>IN_LDO</sub> falling                                                               |      | 500  |      | mV   |

| PVCC (Note 6)                                |                           |                                                                                           |      |      |      |      |

| Internal Regulator<br>Output Voltage         | Vout_pvcc                 |                                                                                           | 4.33 | 4.58 | 4.83 | V    |

| Over-Current Limit                           | I <sub>CL_PVCC</sub>      |                                                                                           | 150  |      | 300  | mA   |

| SEQOUT (RTQ2076A                             | A-QT)                     |                                                                                           |      |      |      |      |

| Output Low Voltage                           |                           | Current into SEQOUT pin equal to 2mA                                                      |      |      | 200  | mV   |

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DSQ2076-QT-00 December 2021 www.richtek.com

| Parameter                | Symbol                | Test Conditions                                                                                                               | Min | Тур  | Max  | Unit |

|--------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| Input Leakage<br>Current | ILEAK_SEQOUT          | 1.8V applied on SEQOUT pin                                                                                                    |     |      | 1    | μА   |

| Power Good (RTQ2         | 076B-QT)              |                                                                                                                               |     |      |      |      |

| Pull Down Voltage        | V <sub>OUT_L_PG</sub> | Current into PG pin equal to 5mA                                                                                              |     |      | 200  | mV   |

| Input Leakage<br>Current | ILEAK_PG              | 1.8V applied on PG pin                                                                                                        |     |      | 1    | μА   |

| Timing                   |                       |                                                                                                                               |     |      |      |      |

|                          | tss_HV1               | Time from V <sub>OUT_HV1</sub> 0% rise to 90% of target value, no load                                                        | 500 | 1000 | 1500 |      |

|                          | t <sub>SS_LV2</sub>   | Time from V <sub>OUT_LV2</sub> 0% rise to 90% of target value, no load                                                        | 500 | 1000 | 1500 |      |

| Soft-Start Time          | tss_Lv3               | Time from V <sub>OUT_LV3</sub> 0% rise to 90% of target value, no load                                                        | 500 | 1000 | 1500 | μS   |

|                          | tss_ldo               | Time from the previous turn on channel's output voltage reaching 90% of target value to Vout_LDO rise to 90% of target value. | 200 | 700  | 1100 |      |

| PG Delay Time            | t <sub>DLY_PG</sub>   | (RTQ2076B-QT)                                                                                                                 | 9   | 10   | 11   | ms   |

## **System Characteristics**

The following specifications are guaranteed by design and are not performed in production testing. ( $T_A = T_J = -40$ °C to 125°C,  $V_{IN} = 6V, \ V_{OUT\_HV1} = 3.6V, \ V_{OUT\_LV2} = 1.1V, \ V_{OUT\_LV3} = 1.8V, \ V_{OUT\_LDO} = 3.3V, \ unless \ otherwise \ specified.)$

| Parameter                                    | Symbol                  | Test Conditions                                                        | Min  | Тур | Max | Unit |  |  |  |

|----------------------------------------------|-------------------------|------------------------------------------------------------------------|------|-----|-----|------|--|--|--|

| System                                       | System                  |                                                                        |      |     |     |      |  |  |  |

| Over-Temperature Protection                  | ОТР                     |                                                                        |      | 160 |     | °C   |  |  |  |

| Over-Temperature<br>Protection<br>Hysteresis | ОТР_Н                   |                                                                        |      | 20  |     | °C   |  |  |  |

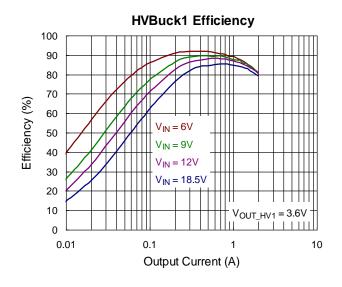

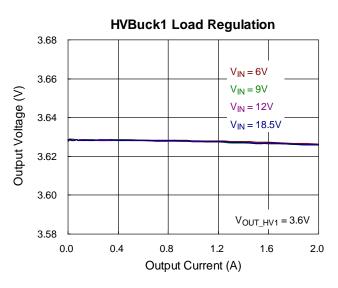

| CH1 HVBuck1                                  |                         |                                                                        |      |     |     |      |  |  |  |

| Maximum Output<br>Current                    | IOUT_MAX_HV1            |                                                                        | 2    |     |     | Α    |  |  |  |

| Load Regulation                              | VLOAD_REG_HV1           | I <sub>OUT_HV1</sub> = 0A to 2A                                        |      |     | 0.1 | %/A  |  |  |  |

| Line Regulation                              | VLINE_REG_HV1           | V <sub>IN</sub> = 5V to 18.5V, I <sub>OUT_HV1</sub> = 2A               |      |     | 1   | %    |  |  |  |

| Load Transient                               | VLOAD_TRAIN_HV1         | I <sub>OUT_HV1</sub> = 10mA to 500mA to 10mA, 1μs                      | -150 |     | 150 | mV   |  |  |  |

| Line Transient                               | VLINE_TRAIN_HV1         | $V_{IN}$ = 5V to 18.5V to 5V, 100 $\mu$ s, $I_{OUT\_HV1}$ = 10mA/500mA | -50  |     | 50  | mV   |  |  |  |

| Output Ripple                                | V <sub>RIPPLE_HV1</sub> | Peak to peak in one switching cycle                                    |      |     | 20  | mVpp |  |  |  |

13

| Parameter                      | Symbol                   | Test Conditions                                                                            | Min | Тур | Max | Unit |

|--------------------------------|--------------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|------|

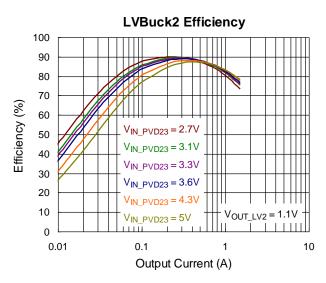

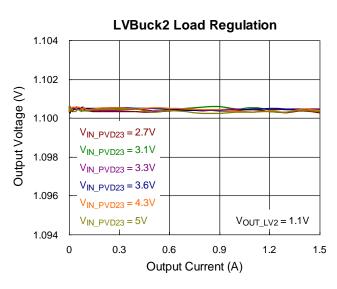

| CH2 LVBuck2 (V <sub>IN_</sub>  | <sub>PVD23</sub> = 3.6V) | 1                                                                                          |     | L   |     |      |

| Maximum Output<br>Current      | IOUT_MAX_LV2             |                                                                                            | 1.5 |     |     | А    |

| Load Regulation                | VLOAD_REG_LV2            | I <sub>OUT_LV2</sub> = 0A to 1.5A                                                          |     |     | 0.1 | %/A  |

| Line Regulation                | VLINE_REG_LV2            | $V_{IN\_PVD23}$ = 2.7V to 5V,<br>$I_{OUT\_LV2}$ = 1.5A                                     |     |     | 1   | %    |

| Load Transient                 | VLOAD_TRAIN_LV2          | $I_{OUT\_LV2}$ = 10mA to 500mA to 10mA, 1µs                                                | -50 |     | 50  | mV   |

| Line Transient                 | VLINE_TRAIN_LV2          | V <sub>IN_PVD23</sub> = 3V to 5V to 3V,<br>50μs, I <sub>OUT_LV2</sub> = 10mA/1A            | -50 |     | 50  | mV   |

| Output Ripple                  | V <sub>RIPPLE_LV2</sub>  | Peak to peak in one switching cycle                                                        |     |     | 10  | mVpp |

| CH3 LVBuck3 (V <sub>IN_</sub>  | <sub>PVD23</sub> = 3.6V) |                                                                                            |     |     |     |      |

| Maximum Output<br>Current      | IOUT_MAX_LV3             |                                                                                            | 750 |     |     | mA   |

| Load Regulation                | VLOAD_REG_LV3            | I <sub>OUT_LV3</sub> = 0A to 750mA                                                         |     |     | 0.1 | %/A  |

| Line Regulation                | VLINE_REG_LV3            | $V_{IN\_PVD23}$ = 2.7V to 5V, $I_{OUT\_LV3}$ = 750mA                                       |     |     | 1   | %    |

| Load Transient                 | VLOAD_TRAIN_LV3          | $I_{OUT\_LV3}$ = 10mA to 300mA to 10mA, 1µs                                                | -50 |     | 50  | mV   |

| Line Transient                 | VLINE_TRAIN_LV3          | V <sub>IN_PVD23</sub> = 3V to 5V to 3V,<br>50μs, I <sub>OUT_LV3</sub> = 10mA/300mA         | -50 |     | 50  | mV   |

| Output Ripple                  | VRIPPLE_LV3              | Peak to peak in one switching cycle                                                        |     |     | 10  | mVpp |

| CH4 LDO (V <sub>IN_LDO</sub> = | = 3.6V)                  |                                                                                            |     |     |     |      |

| Power Supply                   | PSRR_LDO                 | I <sub>OUT_LDO</sub> = 100mA, f = 100kHz                                                   |     | 60  |     | dB   |

| Rejection Ratio                | T SIXIX_LDO              | I <sub>OUT_LDO</sub> = 100mA, f = 1MHz                                                     |     | 40  |     | uБ   |

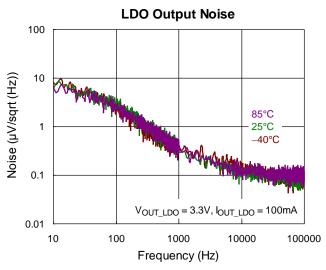

| Output Noise<br>Voltage        | eN_LDO                   | I <sub>OUT_LDO</sub> = 100mA,<br>f = 100Hz to 100kHz                                       |     | 60  |     | μV   |

| Load Transient                 | VLOAD_TRAIN_LDO          | I <sub>OUT_LDO</sub> = 10mA to 200mA to 10mA, 1μs                                          | -25 |     | 25  | mV   |

| Line Transient                 | VLINE_TRAIN_LDO          | All Vout_LDO, VIN_LDO step 600mV, LDO not in dropout condition, 10μs, IOUT_LDO = 1mA/300mA | -25 |     | 25  | mV   |

| Component Requir               | ement (Note 4)           |                                                                                            |     |     |     |      |

| The other leaves               | CIN_HV1                  |                                                                                            | 1.5 | 4.7 | 10  |      |

| Effective Input Capacitance    | C <sub>IN_PVD23</sub>    |                                                                                            | 1.5 | 4.7 | 10  | μF   |

| •                              | C <sub>IN_LDO</sub>      |                                                                                            | 0.7 | 2.2 | 4   |      |

|                                | C <sub>OUT_HV1</sub>     |                                                                                            | 3.3 | 10  | 14  |      |

| Effective Output               | COUT_LV2                 |                                                                                            | 4.5 | 10  | 14  | μF   |

| Capacitance                    | C <sub>OUT_LV3</sub>     |                                                                                            | 4.5 | 10  | 14  | μι   |

|                                | C <sub>OUT_LDO</sub>     |                                                                                            | 0.7 | 2.2 | 4   |      |

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

DSQ2076-QT-00 December 2021 www.richtek.com

## **RTQ2076-QT**

| Parameter                     | Symbol            | Test Conditions | Min  | Тур | Max  | Unit |

|-------------------------------|-------------------|-----------------|------|-----|------|------|

|                               | L <sub>HV1</sub>  |                 | 1    | 1.5 | 2    |      |

| Output Inductance             | L <sub>L</sub> V2 |                 | 0.68 | 1   | 1.2  | μΗ   |

|                               | L <sub>L</sub> V3 |                 | 0.68 | 1   | 1.2  |      |

| Effective Boot<br>Capacitance | Своот             |                 | 0.07 | 0.1 | 0.13 | μF   |

| Effective PVCC Capacitance    | CPVCC             |                 | 0.3  | 1   | 1.4  | μF   |

- Note 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2. θJA is measured under natural convection (still air) at TA = 25°C with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- **Note 4.** The device is not guaranteed to function outside its operating conditions.

- Note 5. Dropout voltage is the voltage difference between the input and the output at which the output voltage drops to 100 mV below its nominal value.

- Note 6. PVCC is the pre-regulator output voltage only for internal circuitry. External loading on PVCC pin is forbidden.

www.richtek.com

## **Typical Application Circuit**

#### RTQ2076A-QT

#### RTQ2076B-QT

DSQ2076-QT-00

December 2021

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

www.richtek.com

**Table 2. Component List of Evaluation Board**

| Reference  | Qty | Part Number          | Description             | Package | Manufacturer |

|------------|-----|----------------------|-------------------------|---------|--------------|

| C1         | 1   | GCJ31CR71E475KA12    | 4.7μF/25V/X7R           | 1206    | MURATA       |

| C2         | 1   | GRT155C81A105KE01    | 1μF/10V/X6S             | 0402    | MURATA       |

| C3         | 1   | GRT155R71C104KE01    | 0.1μF/16V/X7R           | 0402    | MURATA       |

| C4, C6, C7 | 1   | GRT188C81A106ME13    | 10μF/10V/X6S            | 0603    | MURATA       |

| C5         | 1   | GRT188C81C475KE13    | 4.7μF/16V/X6S           | 0603    | MURATA       |

| C8, C9     | 1   | GRT155C81A225KE13    | 2.2μF/10V/X6S           | 0402    | MURATA       |

| L1         | 1   | TFM201610ALMA1R5MTAA | 1.5μH/3.1A/85m $\Omega$ | 0806    | TDK          |

| L2, L3     | 1   | TFM201610ALMA1R0MTAA | 1μH/3.7A/50m $\Omega$   | 0806    | TDK          |

| R1         | 1   | MR02X1372FAL         | 13.7kΩ/1%               | 0201    | WALSIN       |

| R2         | 1   | MR02X3921FAL         | 3.92kΩ/1%               | 0201    | WALSIN       |

| R3*        | 1   | MR02X000 PAL         | 0Ω/Jumper               | 0201    | WALISN       |

| R4*        | 1   | MR02X3303FAL         | 330kΩ/1%                | 0201    | WALSIN       |

| R5         | 1   | MR02X1002FAL         | 10kΩ/1%                 | 0201    | WALSIN       |

R3\*: Resistor is adjustable with different LDO output voltages.

R4\*: Resistor is adjustable with different power on sequences.

## **Typical Operating Characteristics**

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

## **Application Information**

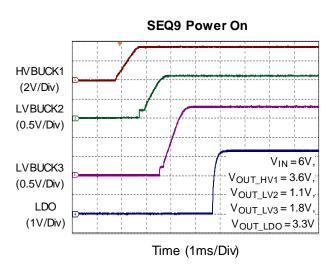

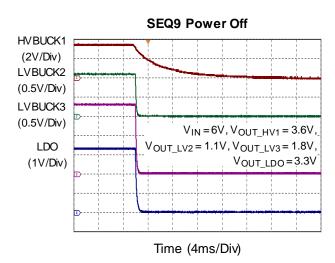

#### **Power Sequence Control**

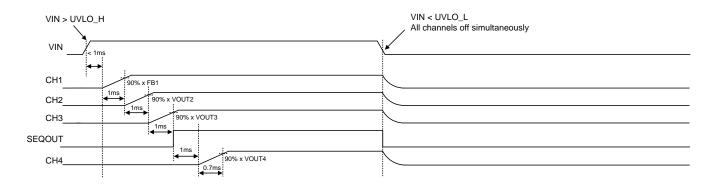

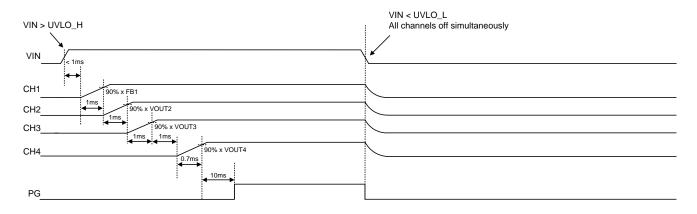

The RTQ2076A-QT/RTQ2076B-QT supports 10 power-on sequences for the step-down converters and LDO via the dedicated resistor on SEQ pin. SEQ pin is not allowable at floating state and resistance selected out of range is not guaranteed to correct power-on sequence. In addition, there is only simultaneous power-off for all outputs. To fix the resistor selection on SEQ pin before enabling the device. Any change during the power on procedure is not guarantee to the correct power-on sequence. Below table shows the power-on sequence with its corresponding resistance.

| SEO No  | Resistance on SEQ (Ω) |             |       | Soguence                   |        |          |        |        |  |  |  |

|---------|-----------------------|-------------|-------|----------------------------|--------|----------|--------|--------|--|--|--|

| SEQ No. | Min                   | Тур         | Max   |                            |        | Sequence |        |        |  |  |  |

| SEQ0    | 1.07M                 | 1.1M        | 1.13M | CH1                        | CH4    | CH3      | CH2    | SEQOUT |  |  |  |

| SEQ1    | 319k                  | 330k        | 341k  | CH1 CH2                    |        | CH3      | SEQOUT | CH4    |  |  |  |

| SEQ2    | 164k                  | 169k        | 174k  | CH1                        | CH2    | SEQOUT   | CH3    | CH4    |  |  |  |

| SEQ3    | 81.6k                 | 84.5k       | 87.4k | CH1                        | SEQOUT | CH2      | CH4    | CH3    |  |  |  |

| SEQ4    | 45.4k                 | 47k         | 48.6k | CH1 CH2, CH3, CH4, SEQOUT  |        |          |        |        |  |  |  |

| SEQ5    | 26.1k                 | 27k         | 27.9k | CH1, CH2, CH3, CH4, SEQOUT |        |          |        |        |  |  |  |

| SEQ6    | 14.5k                 | 15k         | 15.5k | CH1 CH3                    |        | CH2      | CH4    | SEQOUT |  |  |  |

| SEQ7    | 7.78k                 | 8.06k       | 8.34k | CH1                        | CH3    | CH4      | CH2    | SEQOUT |  |  |  |

| SEQ8    | Sh                    | nort to PVC | CC    | CH1                        | SEQOUT | CH2      | CH3    | CH4    |  |  |  |

| SEQ9    | Sh                    | nort to PGI | ND    | CH1                        | CH2    | CH3      | CH4    | SEQOUT |  |  |  |

**Table 3. Power-On Sequence Control**

#### Note:

- (1) The SEQOUT output exists only in RTQ2076A-QT. After SEQOUT output high state 1ms passed, the next channel continues to proceed power on sequence.

- (2) For RTQ2076B-QT, 1ms time interval will substitute the SEQOUT output. Below is the SEQ1 example.

For RTQ2076A-QT, CH1 → CH2 → CH3 → SEQOUT → CH4

For RTQ2076B-QT, CH1 → CH2 → CH3 → 1ms → CH4

Figure 1. Example SEQ1 for RTQ2076A-QT

Figure 2. Example SEQ1 for RTQ2076B-QT

#### **Output Voltage Setting**

#### HVBuck1

The output voltage set by external feedback resistors expressed in the following equation.

$$V_{OUT\_HV1} = \left(1 + \frac{R1}{R2}\right) \times V_{FB1}$$

Where the reference voltage V<sub>FB</sub>1 is 0.8V (typ.)

The placement of the resistive divider should be as close as possible to the FB1 pin. For better output voltage accuracy, the divider resistors with ±1% tolerance or better should be used. The resistance ranges from few  $k\Omega$  to hundreds of  $k\Omega$  is recommended.

#### LVBuck2 and LVBuck3

The output voltage of LVBuck2 is fixed 1.1V. The output voltage of LVBuck3 is fixed 1.8V.

#### • LDO

The LDO output voltage is controlled by setting the dedicated resistor on RSET pin. RSET pin is not allowable at floating state and resistance selected out of range is not guaranteed to correct output voltage. Changing of the output voltage real time is not recommended. To fix the resistor selection on RSET pin before enabling the device.

Table 4. LDO Output Voltage

| <u> </u> |       |         |           |     |  |  |  |  |  |

|----------|-------|---------|-----------|-----|--|--|--|--|--|

| RSET     | Resis | Voltage |           |     |  |  |  |  |  |

| No.      | Min   | Тур     | Max       | (V) |  |  |  |  |  |

| RSET0    | 1.07M | 1.1M    | 1.13M     | 3.5 |  |  |  |  |  |

| RSET1    | 319k  | 330k    | 341k      | 3.4 |  |  |  |  |  |

| RSET2    | 164k  | 169k    | 174k      | 3.2 |  |  |  |  |  |

| RSET3    | 81.6k | 84.5k   | 87.4k     | 3.1 |  |  |  |  |  |

| RSET4    | 45.4k | 47k     | 48.6k     | 3.0 |  |  |  |  |  |

| RSET5    | 26.1k | 27k     | 27.9k     | 2.8 |  |  |  |  |  |

| RSET6    | 14.5k | 15k     | 15k 15.5k |     |  |  |  |  |  |

| RSET7    | 7.78k | 8.06k   | 8.34k     | 1.8 |  |  |  |  |  |

| RSET8    | Sł    | 2.9     |           |     |  |  |  |  |  |

| RSET9    | Sh    | 3.3     |           |     |  |  |  |  |  |

#### **Channel Protection Features**

The RTQ2076A-QT/RTQ2076B-QT equips protections to prevent the device from damages causing by abnormal operations or fault conditions. (Over-load, Short-circuit, Soldering issue...etc.)

#### Under-Voltage Protection (UVP)

#### ► HVBuck1, LVBuck2, LVBuck3 and LDO

The device disables all channels and enters into latch off state if step-down converter or LDO output under voltage fault detected continuously over deglitch time and the device only can re-start with VIN ON/OFF.

#### Over-Voltage Protection (OVP)

#### ▶ HVBuck1

When FB1 pin over-voltage fault detected, the high-side and low-side MOSFETs turn off immediately and auto-recover to switch until FB1 pin's voltage decrease to the reset level.

#### ▶ LVBuck2, LVBuck3 and LDO

The device disables all channels when step-down converter or LDO output over-voltage fault detected continuously over deglitch time. When the fault released, the device auto-restarts all channels in sequence.

#### • Over-Current Protection (OCP)

#### ► HVBuck1, LVBuck2 and LVBuck3

The step-down converter includes a cycle-by-cycle high-side MOSFET peak current-limit protection against the condition that the inductor current increasing abnormally, even over the inductor saturation current rating. If an over-current condition occurs, the controller will immediately turn off the high-side MOSFET and turn on the low-side MOSFET to prevent the inductor current

exceeding the peak current limit level. After inductor current decreasing to below the valley current limit, the high-side MOSFET resume switching on. If over-current fault further detected continuously over than deglitch time, the device disables all channels and enters into latch off state and the device only can re-start with VIN ON/ OFF.

#### ▶ LDO

When the load reaches the current limit threshold. the current sent to the output will kept at current limit level. If over-current fault detected continuously over than the deglitch time, the device disables all channels and enters into latch off state and the device only can re-start with VIN ON/ OFF.

#### • Input Over-Voltage Protection (OVP)

#### ▶ LVBuck2, LVBuck3 and LDO

If the input voltage of step-down converters (LVBuck2, LVBuck3) or LDO reaches over-voltage protection level, the device disables all channels. After fault removed, it auto-restarts all channels in sequence.

www.richtek.com

#### **Table 5. Protection**

| Channel        | Туре         | Threshold<br>(Typ.)                            | Deglitch Time<br>(Typ.) | Protection                                                                                                             | Reset and<br>Threshold<br>(Typ.)                                                                         |  |

|----------------|--------------|------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|

|                | UVLO         | V <sub>IN</sub> ≤ 3.3V<br>(after IC Operation) | 32µs                    | Disable all channels                                                                                                   | V <sub>IN</sub> ≥ 3.8V                                                                                   |  |

| System         | OVP          | V <sub>IN</sub> ≥ 20V                          | 5ms                     | Disable all channels then latch-off protection                                                                         | $V_{IN} \le 3.3V$ , then $V_{IN} \ge 3.8V$                                                               |  |

|                | ОТР          | T <sub>J</sub> ≥ 160°C                         | 5μs                     | Disable all channels then latch-off protection                                                                         | $T_J \le 140^{\circ}\text{C}$ and $V_{\text{IN}} \le 3.3\text{V}$ , then $V_{\text{IN}} \ge 3.8\text{V}$ |  |

|                | UVP          | V <sub>FB1</sub> ≤ 0.8V x 50%                  | 5μs                     | Disable all channels then latch-off protection                                                                         | V <sub>IN</sub> ≤ 3.3V, then V <sub>IN</sub> ≥ 3.8V                                                      |  |

| CH1<br>HVBuck1 | OVP          | V <sub>FB1</sub> ≥ 0.8V x<br>110%              | NA                      | High/Low-side MOSFETs off, low-side MOSFET conditionally ON to charge the BOOT capacitor for driving high-side MOSFET. | V <sub>FB1</sub> < 0.8V x<br>110%                                                                        |  |

|                | OCP          | I <sub>L1_peak</sub> ≥ 3A                      | 10ms                    | Cycle-by-cycle detection If keep 10ms, disable all channels then latch-off protection.                                 | If latch-off protection, $V_{IN} \le 3.3V$ , then $V_{IN} \ge 3.8V$                                      |  |

|                | UVP          | V <sub>OUT_LV2</sub> ≤ 1.1V x<br>50%           | 5μs                     | Disable all channels then latch-off protection                                                                         | V <sub>IN</sub> ≤ 3.3V, then<br>V <sub>IN</sub> ≥ 3.8V                                                   |  |

| CH2            | OVP          | V <sub>OUT_LV2</sub> ≥ 1.1V x<br>120%          | 5ms                     | Disable all channels                                                                                                   | V <sub>OUT2</sub> ≤ 1.1V x<br>110% with deglitch<br>5ms                                                  |  |

| LVBuck2        | OCP          | I <sub>L2_peak</sub> ≥ 2A                      | 10ms                    | Cycle-by-cycle detection If keep 10ms, disable all channels then latch-off protection.                                 | If latch-off protection, $V_{IN} \le 3.3V$ , then $V_{IN} \ge 3.8V$                                      |  |

|                | Input<br>OVP | V <sub>IN_PVD23</sub> ≥ 5.8V                   | 5μs                     | Disable all channels                                                                                                   | V <sub>IN_PVD23</sub> ≤ 5.22V<br>with deglitch 5μs                                                       |  |

|                | UVP          | V <sub>OUT_LV3</sub> ≤1.8V x<br>50%            | 5μs                     | Disable all channels then latch-off protection                                                                         | $V_{IN} \le 3.3V$ , then $V_{IN} \ge 3.8V$                                                               |  |

| CH3<br>LVBuck3 | OVP          | V <sub>OUT_LV3</sub> ≥ 1.8V x<br>120%          | 5ms                     | Disable all channels                                                                                                   | V <sub>OUT3</sub> ≤ 1.8V x<br>110% with deglitch<br>5ms                                                  |  |

|                | OCP          | I <sub>L3_peak</sub> ≥ 1.2A                    | 10ms                    | Cycle-by-cycle detection If keep 10ms, disable all channels then latch-off protection.                                 | If latch-off protection, $V_{IN} \le 3.3V$ , then $V_{IN} \ge 3.8V$                                      |  |

|                | Input<br>OVP | V <sub>IN_PVD23</sub> ≥ 5.8V                   | 5μs                     | Disable all channels                                                                                                   | V <sub>IN_PVD23</sub> ≤ 5.22V<br>with deglitch 5μs                                                       |  |

| Channel | Type         | Threshold<br>(Typ.)                 | Deglitch Time<br>(Typ.) | Reset and<br>Threshold<br>(Typ.)               |                                                                            |  |

|---------|--------------|-------------------------------------|-------------------------|------------------------------------------------|----------------------------------------------------------------------------|--|

|         | UVP          | Vout_LDo≤Vout_L<br>Do setting x 40% | 5μs                     | Disable all channels then latch-off protection | $V_{IN} \le 3.3V$ , then $V_{IN} \ge 3.8V$                                 |  |

| CH4 LDO | OVP          | Vout_ldo ≥<br>Vout_ldo x 125%       | 5ms                     | Disable all channels                           | V <sub>OUT_LDO</sub> ≤<br>V <sub>OUT_LDO</sub> x 110%<br>with deglitch 5ms |  |

|         | OCP          | I <sub>OUT_LDO</sub> ≥ 450mA        | 10ms                    | Disable all channels then latch-off protection | $V_{IN} \le 3.3V$ , then $V_{IN} \ge 3.8V$                                 |  |

|         | Input<br>OVP | V <sub>IN_LDO</sub> ≥ 5.8V          | 5μs                     | Disable all channels                           | V <sub>IN_LDO</sub> ≤ 5.3V<br>with deglitch 5μs                            |  |

#### **Input and Output Capacitor Selection**

#### • HVBuck1, LVBuck2 and LVBuck3

It is recommended at least a  $4.7\mu F$  input capacitor with a  $10\mu F$  output capacitor for step-down converters. The ripple voltage is an important index for choosing output capacitor. This portion consists of two parts. One is the product of ripple current with the ESR of the output capacitor, while the other part is formed by the charging and discharging process of the output capacitor. The output ripple can be calculated as below.

$$\Delta V_{OUTRipple} = \Delta V_{ESR} + \Delta V_{OUT} = \Delta V_{ESR} + \frac{\Delta I_L}{8 \times C_{OUT} \times f_{SW}}$$

where  $\Delta V_{ESR} = I_{Crms} \times R_{CESR}$

#### LDO

Like any low dropout regulator, the external capacitor of the RTQ2076A-QT/RTQ2076B-QT must be carefully selected for regulator stability and performance. Using a  $2.2\mu F$  capacitor for the LDO's input and output is suitable.

Additional capacitor paralleled on the output may get better noise suppression but also lead to higher input inrush current when LDO outputs. It should be taken into consideration carefully.

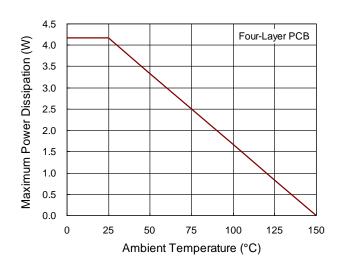

#### **Thermal Considerations**

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature;  $T_A$  is the ambient temperature; and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 150°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a WETD-VQFN-16L 3x3 package, the thermal resistance,  $\theta_{JA}$ , is 30°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at  $T_A$  = 25°C can be calculated as below:

$P_{D(MAX)} = (150^{\circ}C - 25^{\circ}C) / (30^{\circ}C/W) = 4.16W$  for a WETD-VQFN-16L 3x3 package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 3 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Figure 3. Derating Curve of Maximum Power Dissipation

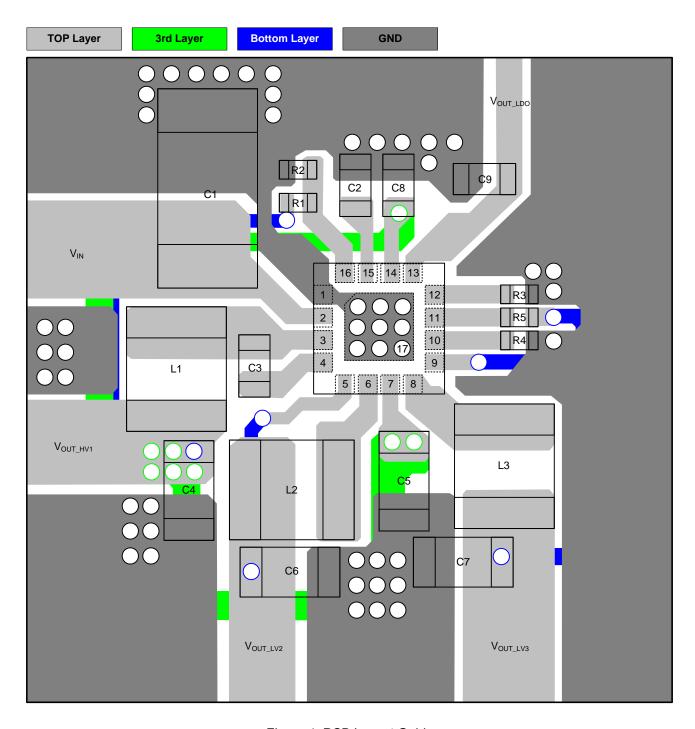

#### **Layout Considerations**

The PCB layout is an important step to maintain the performance of the RTQ2076A-QT/ RTQ2076B-QT. Both the high current and the fast switching nodes demand full attention to the PCB layout to keep the robustness of the RTQ2076A-QT/ RTQ2076B-QT through the PCB layout. Improper layout might lead to the symptoms of poor line or load

regulation, ground and output voltage shifts, stability issues, unsatisfying EMI behavior or worsened efficiency. For the best performance of RTQ2076A-QT/RTQ2076B-QT, the following PCB layout guidelines must be strictly followed.

- ▶ The trace from switching node to inductor should be as short as possible to minimized the switching loop for better EMI.

- ▶ Place the input and output capacitors close to the input and output pins respectively for good filtering.

- ▶ Keep the main power traces as wide and short as possible.

- ► Connect the AGND and PGND to a strong ground plane for maximum thermal dissipation and noise protection.

- ▶ Directly connect the step-down converter's output capacitor to the feedback network to avoid bouncing caused by parasitic resistance and inductance from the PCB trace.

www.richtek.com

Figure 4. PCB Layout Guide

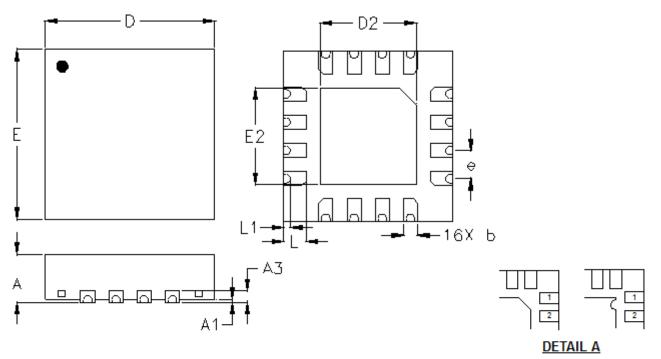

## **Outline Dimension**

Pin #1 ID and Tie Bar Mark Options

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Cumb al | Dimensions | In Millimeters | Dimensions In Inches |       |  |  |

|---------|------------|----------------|----------------------|-------|--|--|

| Symbol  | Min        | Max            | Min                  | Max   |  |  |

| А       | 0.800      | 1.000          | 0.031                | 0.039 |  |  |

| A1      | 0.000      | 0.050          | 0.000                | 0.002 |  |  |

| А3      | 0.175      | 0.250          | 0.007                | 0.010 |  |  |

| b       | 0.180      | 0.300          | 0.007                | 0.012 |  |  |

| D       | 2.950      | 3.050          | 0.116                | 0.120 |  |  |

| D2      | 1.650      | 1.750          | 0.065                | 0.069 |  |  |

| E       | 2.950      | 3.050          | 0.116                | 0.120 |  |  |

| E2      | E2 1.650   |                | 0.065                | 0.069 |  |  |

| е       | 0.5        | 500            | 0.0                  | )20   |  |  |

| L       | 0.350      | 0.450          | 0.014                | 0.018 |  |  |

| L1      | 0.075      | 0.175          | 0.003                | 0.007 |  |  |

WETD V-Type 16L QFN 3x3 Package

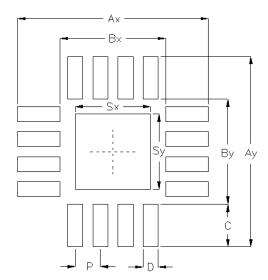

## **Footprint Information**

| Dookogo               | Number of | Footprint Dimension (mm) |      |      |      |      |      |      | Talawanaa |      |           |

|-----------------------|-----------|--------------------------|------|------|------|------|------|------|-----------|------|-----------|

| Package               | Pin       | Р                        | Ax   | Ау   | Вх   | Ву   | С    | D    | Sx        | Sy   | Tolerance |

| WETD-V/W/U/XQFN3x3-16 | 16        | 0.50                     | 3.80 | 3.80 | 2.10 | 2.10 | 0.85 | 0.30 | 1.50      | 1.50 | ±0.05     |

## **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1st Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

DSQ2076-QT-00 December 2021

## 单击下面可查看定价,库存,交付和生命周期等信息

>>Richtek(台湾立锜)