# High Accuracy Current/Voltage Sensing and Protection IC

# **General Description**

The RT9553B is designed for over-current detection and over-/under-voltage protection.

It provides users to set over-current threshold by the ILIM pin to compare that senses dropping voltage between CSP pin and CSN pin. Moreover, users can set over-/under-voltage threshold by the OVSET pin/UVSET pin to compare with the CSP voltage. The RT9553B is available in the WDFN-10L 3x3 package.

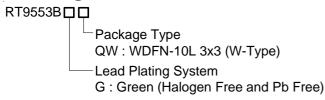

### **Ordering Information**

#### Note:

Richtek products are:

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

### **Features**

- Common Mode Input Range up to 24V

- VCC Operating Current : 200μA

- VCC Shutdown Current: 10µA (under S3/S4/S5)

- Programmable Over-Current Level

- One Shot PROCHOT Signal when OCP

- Pull Low RESET Signal when OVP/UVP

- OVP/UVP with 8% Recover Hysteresis Range

- Programmable OVP/UVP De-glitch Time

## **Applications**

Notebook

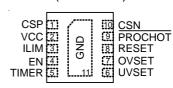

### **Pin Configuration**

(TOP VIEW)

WDFN-10L 3x3

## **Marking Information**

MK=: Product Code YMDNN: Date Code

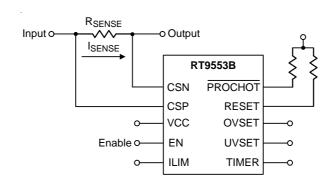

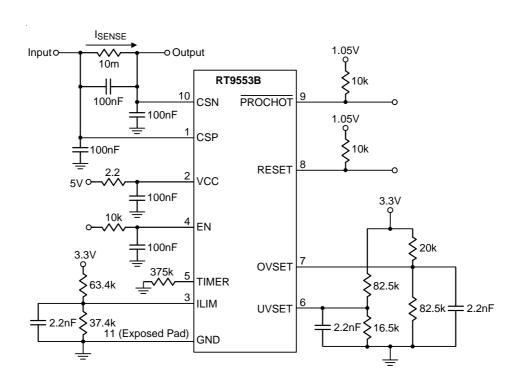

## **Simplified Application Circuit**

# **Functional Pin Description**

| Pin No.          | Pin Name | Pin Function                                                                                                                                                                |  |  |  |  |

|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                | CSP      | Positive current sense input.                                                                                                                                               |  |  |  |  |

| 2                | VCC      | Power supply input. Connect this pin to 5V and place a minimum $0.1\mu F$ decoupling capacitor. The decoupling capacitor should be placed to this pin as close as possible. |  |  |  |  |

| 3                | ILIM     | Over-current trip point setting input. The setting range is from 0.4V to 2V.                                                                                                |  |  |  |  |

| 4                | EN       | Enable control input.                                                                                                                                                       |  |  |  |  |

| 5                | TIMER    | Deglitch time setting of OV/UV protection. Connect a resistor from this pin tied to GND to set deglitch time. Do not parallel any filter capacitor to this pin.             |  |  |  |  |

| 6                | UVSET    | Under-voltage trip point setting input. The setting range is from 0.55V to 3V.                                                                                              |  |  |  |  |

| 7                | OVSET    | Over-voltage trip point setting input. The setting range is from 0.55V to 3V.                                                                                               |  |  |  |  |

| 8                | RESET    | Open-drain output. Connect to an external resistor to pull high. When OV/UV occurs, this pin will be pulled low.                                                            |  |  |  |  |

| 9                | PROCHOT  | Open-drain output. Connect to an external resistor to pull high. When OC occurs, this pin will be pulled low.                                                               |  |  |  |  |

| 10               | CSN      | Negative current sense input.                                                                                                                                               |  |  |  |  |

| 11 (Exposed Pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                 |  |  |  |  |

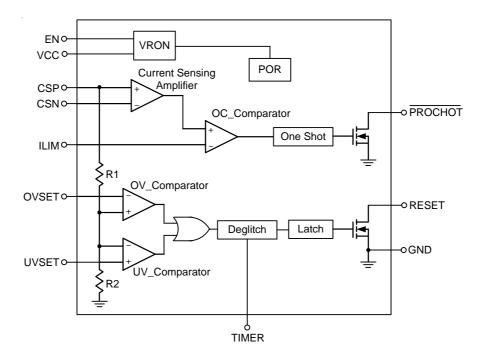

# **Functional Block Diagram**

## **Operation**

The RT9553B consists of a current sensing amplifier, and two comparators, and it provides the following functions: over-current protection, over-voltage protection and undervoltage protection.

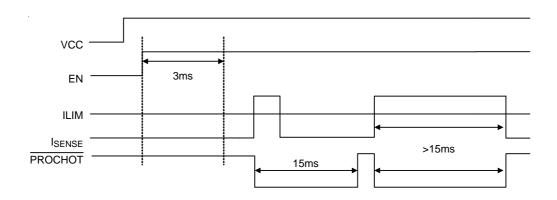

#### **Over-Current Protection**

With m $\Omega$  order of resistor shunts between CSP and CSN, the current sensing amplifier multiplies the voltage between CSP and CSN by 100 and compares the result with the ILIM voltage. If the output voltage of current sensing amplifier is larger than the ILIM voltage, the  $\overline{\text{PROCHOT}}$  voltage is pulled low.

### **OVP/UVP Deglitch Time**

The output signal of OV\_comparator or UV\_comparator is delayed by deglitch timer. The delayed time is decided by the resistor (see spec.) connected to the TIMER pin.

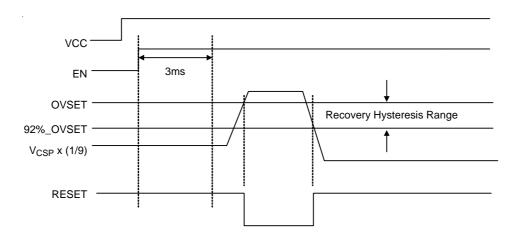

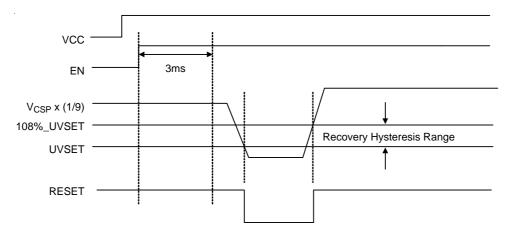

### Over-/Under-Voltage Protection

The OVSET voltage is set by users and it compares with the voltage which is 1/9 of CSP voltage with OV\_comparator. The UVSET voltage is set by users and it also compares with the voltage which is 1/9 of CSP voltage with UV\_comparator. Either the output of OV\_comparator or UV\_comparator is high, the RESET voltage is pulled low.

## Absolute Maximum Ratings (Note 1)

| CSP/CSN to GND                                                              | –0.3V to 28V   |

|-----------------------------------------------------------------------------|----------------|

| • VCC, ILIM, EN, UVSET, OVSET, RESET, PROCHOT to GND                        | -0.3V to 6V    |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                |

| WDFN-10L 3x3                                                                | 3.27W          |

| Package Thermal Resistance (Note 2)                                         |                |

| WDFN-10L 3x3, $\theta_{JA}$                                                 | 30.5°C/W       |

| WDFN-10L 3x3, $\theta_{JC}$                                                 | 7.5°C/W        |

| • Lead Temperature (Soldering, 10 sec.)                                     |                |

| Junction Temperature                                                        |                |

| Storage Temperature Range                                                   | –65°C to 150°C |

| ESD Susceptibility (Note 3)                                                 |                |

| HBM (Human Body Model)                                                      | 2kV            |

|                                                                             |                |

| Recommended Operating Conditions (Note 4)                                   |                |

| High-Side Voltage, VCSP/VCSN                                                | 5V to 24V      |

### **Electrical Characteristics**

( $V_{CC}$  = 5V,  $T_A$  = 25°C, unless otherwise specified)

| Parameter                     |                        | Symbol                              | Test Conditions   | Min | Тур | Max | Unit |

|-------------------------------|------------------------|-------------------------------------|-------------------|-----|-----|-----|------|

| CSN CSP Inpu                  | ut                     | •                                   |                   | •   |     |     |      |

| Input Voltage F               | Range                  | V <sub>CSP</sub> , V <sub>CSN</sub> |                   | 5   |     | 24  | V    |

| ICSN + ICSP                   |                        |                                     | VCC = 5V, EN high |     | 50  |     | - Λ  |

|                               |                        |                                     | VCC = 5V, EN low  |     |     | 5   | μΑ   |

| VCC Input                     |                        |                                     |                   |     |     |     |      |

| VCC Operating                 | g Current              | Ivcc                                |                   |     | 200 |     | μΑ   |

| VCC Shutdown Current          |                        | I <sub>VCC_shd</sub>                |                   |     |     | 10  | μΑ   |

| V00 D0D D: :                  |                        | V <sub>IN_POR</sub>                 | Rising            | 2.8 |     | 3.7 | V    |

| VCC POR RISI                  | VCC POR Rising Voltage |                                     | Hysteresis        |     | 400 |     | mV   |

| Enable                        |                        | •                                   |                   | •   |     |     |      |

| Enable Input Logic-Hi         |                        | ViH                                 |                   | 0.7 |     |     | .,   |

| Voltage                       | Logic-Low              | VIL                                 |                   |     |     | 0.3 | V    |

| Over-Current                  | Protection             | •                                   |                   |     |     |     |      |

| System Response Time          |                        |                                     |                   |     | 50  |     | μS   |

| Open-Drain Output<br>Duration |                        | ТРПОСНОТ                            |                   | 10  |     | 18  | ms   |

| Open-Drain Ou                 | utput Ron              | RON_PROCHOT                         |                   |     |     | 10  | Ω    |

Copyright ©2017 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

DS9553B-00 October 2017

| Parameter                       | Symbol                    | Test Conditions                   | Min | Тур | Max | Unit |

|---------------------------------|---------------------------|-----------------------------------|-----|-----|-----|------|

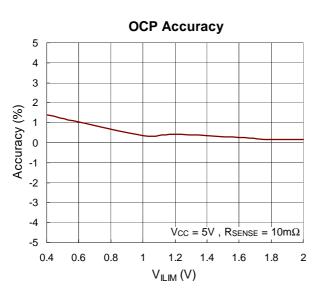

| Input Current Sensing Accuracy  | OCacc                     | V <sub>ILIM</sub> = 0.4V to 2V    |     |     | 6.5 | %    |

| PROCHOT Leakage<br>Current      | I <sub>leak_PROCHOT</sub> | EN Low                            |     |     | 5   | μΑ   |

| ILIM Leakage Current            | I <sub>leak_ILIM</sub>    | EN Low                            |     |     | 5   | μΑ   |

| ILIM Operation Range            | VILIM                     |                                   | 0.4 |     | 2   | V    |

| Over-/Under-Voltage Prot        | ection                    |                                   | •   |     |     |      |

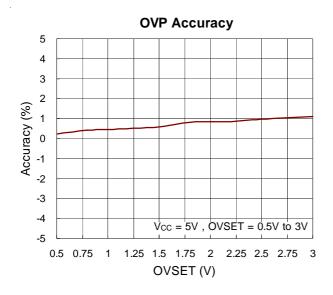

| OVP Accuracy                    | OVPacc                    | Vovset = 0.55V to 3V              |     |     | 5   | %    |

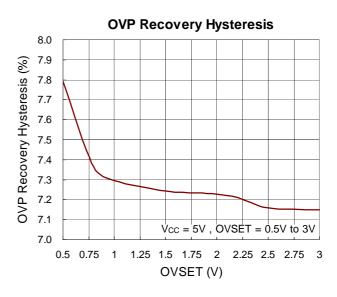

| OVP Recover Hysteresis<br>Range |                           | V <sub>O</sub> VSET = 0.55V to 3V |     | 8   |     | %    |

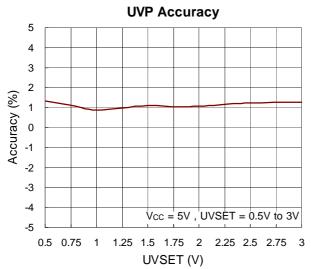

| UVP Accuracy                    | UVP <sub>acc</sub>        | V <sub>UVSET</sub> = 0.55V to 3V  |     |     | 5   | %    |

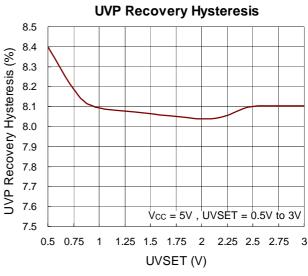

| UVP Recover Hysteresis<br>Range |                           | V <sub>UVSET</sub> = 0.55V to 3V  |     | 8   |     | %    |

| Open Drain Output Ron           | Ron_reset                 | I <sub>Sink</sub> = 10mA          |     |     | 10  | Ω    |

| RESET Leakage Current           | I <sub>leak_RESET</sub>   | EN Low                            |     |     | 5   | μΑ   |

| OVD/UVD Do glitch Time          | <b>t</b>                  | R <sub>Timer</sub> = 375k         |     | 15  |     | 0    |

| OVP/UVP De-glitch Time          | t <sub>Timer</sub>        | R <sub>Timer</sub> = 125k         |     | 5   |     | μS   |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- **Note 2.**  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}\text{C}$  with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

# **Typical Application Circuit**

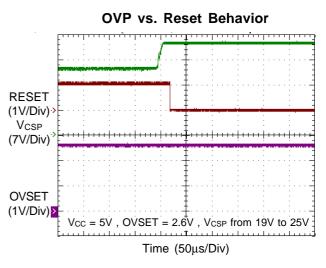

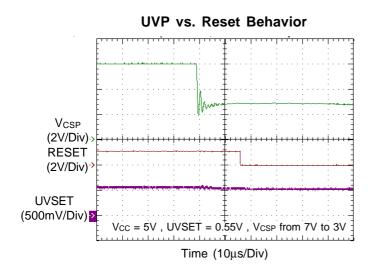

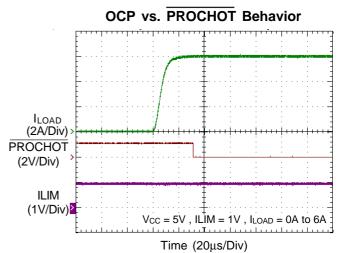

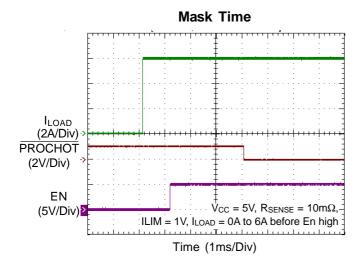

# **Typical Operating Characteristics**

Copyright ©2017 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9553B-00 October 2017

www.richtek.com

### **Application Information**

The RT9553B provides OVP, UVP, OCP protection functions with RESET, PROCHOT indicator to inform system. It can be operated minimize external components of switching power supply systems to achieve protection. For easily using and increasing PCB space utilization, the RT9553B is used in notebook applications.

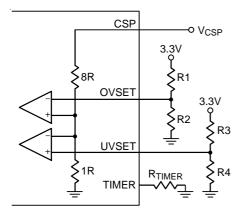

### **Over-Voltage Protection (OVP)**

The CSP pin voltage can be continuously monitored for over-voltage condition.

When the CSP pin voltage exceeds the setting threshold at the OVSET pin, the over-voltage protection will be triggered, and the RESET pin will be pull low after a deglitch time, the RESET is resumed when the CSP pin voltage down to 8% hysteresis.

For more details, please refer to the following information.

The equation of over-voltage setting threshold is shown as below:

$$V_{OVSET} = 3.3V \times \frac{R2}{R1 + R2}$$

$$V_{CSP} = 3.3V \times \frac{R2}{R1 + R2} \times 9$$

We suggest that the total resistance of divider network should be higher than  $100k\Omega$ .

V<sub>CSP</sub> is over-voltage protection trigger point.

Fighre 1. Setting Network of Over-Voltage Protection and Under-Voltage Protection

### **Under-Voltage Protection (UVP)**

The principle of under-voltage protection is the same as over-voltage protection function. The under-voltage protection threshold is set by the UVSET pin.

When the CSP pin voltage is lower the setting threshold at the UVSET pin, the under-voltage protection will be triggered, and the RESET pin will be pull low after a deglitch time, the RESET is resumed when the CSP pin voltage up to 8% hysteresis.

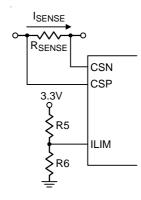

### **Over-Current Protection (OCP)**

As an industry standard, high accuracy current sense amplifier is used to monitor the input current that flows through current sense resistor. The RT9553B detects CSP-CSN differential voltage across the current sense resistor to monitor input current. The equation of overcurrent protection is shown as below:

$$\begin{split} &V_{ILIM} = 3.3V \times \frac{R6}{R5 + R6} \\ &(I_{SENSE} \times R_{SENSE}) \times 100 = V_{ILIM} \\ &I_{SENSE} = \frac{V_{ILIM}}{100 \times R_{SENSE}} \end{split}$$

We suggest that the total resistance of divider network should be higher than  $100k\Omega$ .

I<sub>SENSE</sub> is over-current protection trigger point.

The 100 is amplification of internal error amplifier.

Figure 2. Setting Network of Over-Current Protection

#### **RESET/Timer**

The RESET pin is an open-drain output, and requires to be connected to a pull-up resistor. When over-voltage or under-voltage occurs, the RESET pin will be pulled low and resume to high with a hysteresis.

Users can set the deglitch time of RESET by adjusting the TIMER pin, and there are two choices of deglitch time, 15  $\mu s$  and 5  $\mu s$ . When the  $R_{TIMER}$  is  $375 k\Omega$ , the deglitch time is 15  $\mu s$ ; when the  $R_{TIMER}$  is  $125 k\Omega$ , the deglitch time is 5  $\mu s$ . Users can choose a suitable deglitch time to avoid protection false triggering.

### **PROCHOT**

The PROCHOT pin is an open-drain output, and requires to be connected to a pull-up resistor. When over-current is detected, PROCHOT will be pulled low within 50µs for 15ms. If over-current condition keeps longer than 15ms, PROCHOT maintains low status until over-current protection is released.

Figure 3, Figure 4, Figure5 illustrates RESET and PROCHOT indicator signals.

Figure 3. RESET and PROCHOT Indicator Illustration

Figure 4. OVP and RESET Indicator Illustrator

Figure 5. UVP and RESET Indicator Illustrator

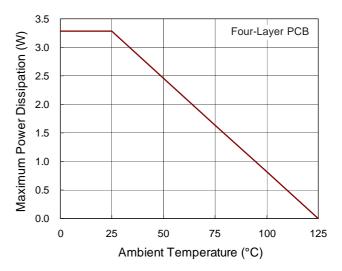

#### **Thermal Considerations**

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula :

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a WDFN-10L 3x3 package, the thermal resistance,  $\theta_{JA}$ , is 30.5°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at  $T_A=25^\circ\text{C}$  can be calculated as below :

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (30.5^{\circ}C/W) = 3.27W$  for a WDFN-10L 3x3 package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 6 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 6. Derating Curve of Maximum Power Dissipation

### **Layout Considerations**

Layout is very important in the RT9553B, if designed improperly, the PCB may radiate excessive noise. Certain points must be considered before starting a layout for the RT9553B.

- ▶ Connect a RC low pass filter to VCC. The recommended BOM of RC filter is  $2.2\Omega$  and  $0.1\mu F$ . Place the filter capacitor close to the IC.

- Current sense connections must always be made using Kelvin connections to ensure an accurate signal with the current limit resistor located at the device.

- All sensitive analog traces and components such as CSP, CSN, VCC, EN, PROCHOT, RESET and ILIM should be placed away form high voltage switching nodes to avoid coupling.

Copyright ©2017 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9553B-00 October 2017 www.richtek.com

11

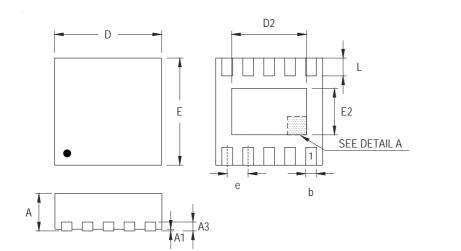

# **Outline Dimension**

**DETAIL A**

Pin #1 ID and Tie Bar Mark Options

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |  |

|--------|--------------|---------------|----------------------|-------|--|--|

|        | Min          | Max           | Min                  | Max   |  |  |

| А      | 0.700        | 0.800         | 0.028                | 0.031 |  |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002 |  |  |

| А3     | 0.175        | 0.250         | 0.007                | 0.010 |  |  |

| b      | 0.180        | 0.300         | 0.007                | 0.012 |  |  |

| D      | 2.950        | 3.050         | 0.116                | 0.120 |  |  |

| D2     | 2.300        | 2.650         | 0.091                | 0.104 |  |  |

| Е      | 2.950        | 3.050         | 0.116                | 0.120 |  |  |

| E2     | 1.500        | 1.750         | 0.059                | 0.069 |  |  |

| е      | 0.5          | 500           | 0.020                |       |  |  |

| L      | 0.350        | 0.450         | 0.014                | 0.018 |  |  |

W-Type 10L DFN 3x3 Package

12

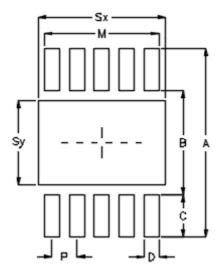

# **Footprint Information**

| Package            | Number of | Footprint Dimension (mm) |      |      |      |      |      | Tolerance |      |           |

|--------------------|-----------|--------------------------|------|------|------|------|------|-----------|------|-----------|

|                    | Pin       | Р                        | Α    | В    | С    | D    | Sx   | Sy        | М    | Tolerance |

| V/W/U/X/ZDFN3*3-10 | 10        | 0.50                     | 3.80 | 2.10 | 0.85 | 0.30 | 2.55 | 1.70      | 2.30 | ±0.05     |

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

DS9553B-00 October 2017

www.richtek.com

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Richtek(台湾立锜)