## 1.5A, 6V, Low $I_{\mbox{\scriptsize Q}}$ ACOT Synchronous Step-Down Converter

### **General Description**

The RTQ2102A-QA is a full featured 6V, 1.5A, Advanced Constant-On-Time (ACOT) synchronous step-down converter with two integrated MOSFETs. The advanced COT operation allows transient responses to be optimized over a wide range of loads, and output capacitors to efficiently reduce external component count. The RTQ2102A-QA provides up to 2.7MHz switching frequency to minimize the size of output inductor and capacitors. The RTQ2102A-QA is available in the WDFN-8L 3x3 package.

### **Ordering Information**

RTQ2102A Grade QA : AEC-Q100 Qualified and Screened by High Temperature Package Type QW : WDFN-8L 3x3 (W-Type) Lead Plating System G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

### **Marking Information**

HX=YM DNN HX= : Product Code YMDNN : Date Code

### Features

- AEC-Q100 Grade 1 Qualified

- 3V to 6V Input Voltage Range

- Advanced COT Control Loop Design

- Fast Transient Response

- Internal 110m  $\Omega$  and 90m  $\Omega$  Synchronous Rectifier

- Highly Accurate V<sub>OUT</sub> Regulation Over Load/Line Range

- Robust Loop Stability with Low-ESR COUT

- Automotive Temperature Range –40°C to 125°C

### **Applications**

- Mobile Phones and Handheld Devices

- STB, Cable Modem, and xDSL Platforms

- WLAN ASIC Power / Storage (SSD and HDD)

- General Purpose for POL LV Buck Converter

- Automotive Infotainment

- Automotive Instrument Clusters & HUD

- Car Connectivity

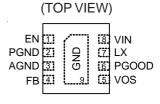

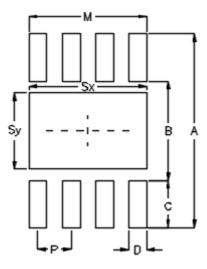

### <sup>Pb Free)</sup> Pin Configuration

WDFN-8L 3x3

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

### **Functional Pin Description**

| Pin No.               | Pin Name | Pin Function                                                                                                                                |

|-----------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1                     | EN       | Enable control input. Pull high to enable.                                                                                                  |

| 2,<br>9 (Exposed Pad) | PGND     | Power ground. The exposed pad must be soldered to a large PCB and connected to PGND for maximum power dissipation.                          |

| 3                     | AGND     | Analog ground. Should be electrically connected to GND close to the device.                                                                 |

| 4                     | FB       | Feedback voltage input.                                                                                                                     |

| 5                     | VOS      | Output voltage sense pin for the internal control loop. Must be connected to output.                                                        |

| 6                     | PGOOD    | Power good open-drain output. This pin is pulled to low if the output voltage is below regulation limits. Can be left floating if not used. |

| 7                     | LX       | Switch node. The Source of the internal high-side power MOSFET, and Drain of the internal low-side (synchronous) rectifier MOSFET.          |

| 8                     | VIN      | Power input supply voltage, 3V to 6V.                                                                                                       |

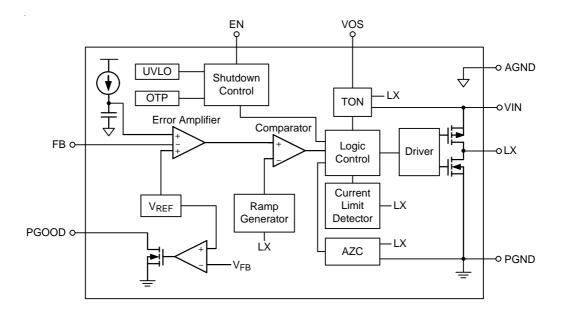

### **Functional Block Diagram**

Copyright ©2019 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation. www.richtek.com DSQ2102A-QA-02 October 2019

### Operation

The RTQ2102A-QA is a low voltage synchronous stepdown converter that can support input voltage ranging from 3V to 6V and the output current can be up to 1.5A. The RTQ2102A-QA uses ACOT<sup>™</sup> mode control. To achieve good stability with low-ESR ceramic capacitors, the ACOT uses a virtual inductor current ramp generated inside the IC. This internal ramp signal replaces the ESR ramp normally provided by the output capacitor's ESR. The ramp signal and other internal compensations are optimized for low-ESR ceramic output capacitors.

In steady-state operation, the feedback voltage, with the virtual inductor current ramp added, is compared to the reference voltage. When the combined signal is less than the reference, the on-time one-shot is triggered, as long as the minimum off-time one-shot is clear and the measured inductor current (through the synchronous rectifier) is below the current limit. The on-time one-shot turns on the high-side switch and the inductor current ramps up linearly. After the on-time, the high-side switch is turned off and the synchronous rectifier is turned on and the inductor current ramps down linearly. At the same time, the minimum off-time one-shot is triggered to prevent another immediate on-time during the noisy switching time and allow the feedback voltage and current sense signals to settle. The minimum off-time is kept short so that rapidly-repeated on-times can raise the inductor current quickly when needed.

#### **PWM Frequency and Adaptive On-Time Control**

The on-time can be roughly estimated by the equation :

$T_{ON} = \frac{V_{OUT}}{V_{IN}} \times \frac{1}{f_{OSC}}$  where for is nominal 2.7MHz

#### Under-Voltage Protection (UVLO)

The UVLO continuously monitors the VCC voltage to make sure the device works properly. When the VCC is high enough to reach the UVLO high threshold voltage, the step-down converter softly starts or pre-bias to its regulated output voltage. When the VCC decreases to its low threshold voltage, the device shuts down.

#### Power Good

When the output voltage is higher than PGOOD rising threshold, the PGOOD flag is high.

#### **Output Under-Voltage Protection (UVP)**

When the output voltage is lower than 66% reference voltage after soft-start, the UVP is triggered.

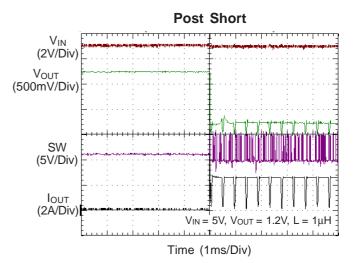

#### **Over-Current Protection (OCP)**

The RTQ2102A-QA senses the current signal when the high-side and low-side MOSFET turns on. As a result, The OCP is a cycle-by-cycle current limit. If an over-current condition occurs, the converter turns off the next on pulse until inductor current drops below the OCP limit. If the OCP is continually activated and the load current is larger than the current provided by the converter, the output voltage drops. Also, when the output voltage triggers the UVP also, the current will drop to ZC and trigger the resoft start sequence.

#### Soft-Start

An internal current source charges an internal capacitor to build the soft-start ramp voltage. The typical soft-start time is  $150\mu s$ .

#### **Over-Temperature Protection (OTP)**

The RTQ2102A-QA has an over-temperature protection. When the device triggers the OTP, the device shuts down until the temperature is back to normal.

## Absolute Maximum Ratings (Note 1)

| Supply Input Voltage, VIN                      | –0.3V to 7V                       |

|------------------------------------------------|-----------------------------------|

| LX Pin Switch Voltage                          | -0.3V to (V <sub>IN</sub> + 0.3V) |

| < 100ns                                        | -5V to 9V                         |

| Other Pins                                     | -0.3V to (V <sub>IN</sub> + 0.3V) |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                                   |

| WDFN-8L 3x3                                    | 3.22W                             |

| Package Thermal Resistance (Note 2)            |                                   |

| WDFN-8L 3x3, $\theta_{JA}$                     | 31°C/W                            |

| WDFN-8L 3x3, $\theta_{JC}$                     | 8°C/W                             |

| Junction Temperature                           | 150°C                             |

| Lead Temperature (Soldering, 10 sec.)          | 260°C                             |

| Storage Temperature Range                      | –65°C to 150°C                    |

| ESD Susceptibility (Note 3)                    |                                   |

| HBM (Human Body Model)                         | 2kV                               |

### Recommended Operating Conditions (Note 4)

| Supply Input Voltage, VIN  | - 3V to 6V                         |

|----------------------------|------------------------------------|

| Junction Temperature Range | <ul> <li>–40°C to 125°C</li> </ul> |

| Ambient Temperature Range  | <ul> <li>–40°C to 125°C</li> </ul> |

### **Electrical Characteristics**

| Parai                         | meter   |                   | Symbol                                                          | Test Conditions                        | Min         | Тур  | Max   | Unit |

|-------------------------------|---------|-------------------|-----------------------------------------------------------------|----------------------------------------|-------------|------|-------|------|

| Under-Voltage L<br>Threshold  | .ockout |                   | Vuvlo                                                           | Vcc rising                             |             | 2.35 | 2.52  | V    |

| Under-Voltage L<br>Hysteresis | .ockout |                   | VUVLOHY                                                         |                                        |             | 400  |       | mV   |

| Shutdown Suppl                | y Curre | ent               | ISHDN                                                           | EN = 0V                                |             |      | 2     | μA   |

| Quiescent Curre               | ent     |                   | lq                                                              | Active, $V_{FB} = 0.5V$ , no switching |             | 30   |       | μA   |

| Voltage Referen               | се      |                   | Vref                                                            |                                        | 0.443       | 0.45 | 0.457 | V    |

|                               | High-S  | Side              |                                                                 | Peak current                           | 2.4         | 3.2  | 4     | ^    |

| Current Limit                 | Low-S   | ide               | ILIM                                                            | Valley current                         | 1.8 2.4 2.9 |      |       | A    |

| Power Good Threshold          |         | V <sub>PGTH</sub> | V <sub>OUT</sub> falling referenced to V <sub>OUT</sub> nominal | -15                                    | -10         | -5   | %     |      |

| Power Good Hysteresis         |         | Vpghy             | Hysteresis referenced to V <sub>OUT</sub> nominal               |                                        | 5           |      | %     |      |

| Power Good Leakage Current    |         | I <sub>PG</sub>   | V <sub>PG</sub> = 5V                                            |                                        | 0.01        | 0.1  | μA    |      |

| Power Good Low Level Voltage  |         | Vpgl              | I <sub>sink</sub> = 500µA                                       |                                        |             | 0.3  | V     |      |

|                               |         | H-Level           | V <sub>ENH</sub>                                                | EN rising                              | 1           |      |       | V    |

| EN Threshold Vo               | onage   | L-Level           | Venl                                                            | EN falling                             |             |      | 0.4   | V    |

(V<sub>IN</sub> = 3.6V, T<sub>A</sub> = T<sub>J =</sub>  $-40^{\circ}$ C to 125°C, unless otherwise specified)

Copyright ©2019 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

www.richtek.com

| Param                          | eter      | Symbol                | Test Conditions | Min Typ Max |     | Unit |     |

|--------------------------------|-----------|-----------------------|-----------------|-------------|-----|------|-----|

| Switch<br>On-Resistance        | High-Side | <b>R</b> P-MOSFET     |                 |             | 110 |      | ~   |

|                                | Low-Side  | R <sub>N-MOSFET</sub> |                 |             | 90  |      | mΩ  |

| Thermal Shutdo<br>Temperature  | wn        |                       |                 | 130         | 150 |      | °C  |

| Thermal Shutdown<br>Hysteresis |           |                       |                 |             | 20  |      | °C  |

| Switching Frequency            |           | fosc                  |                 | 2.2         | 2.7 | 3    | MHz |

| Output Discharge Resistor      |           |                       |                 |             | 1   |      | kΩ  |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}$ C on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package. The copper area is 70mm<sup>2</sup> connected with IC exposed pad.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

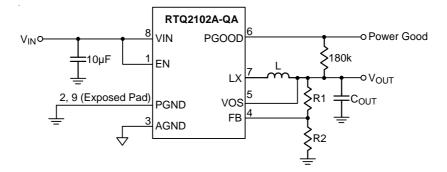

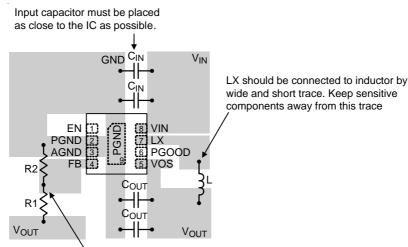

## **Typical Application Circuit**

| V <sub>OUT</sub> (V) | <b>R1 (k</b> Ω) | <b>R2 (k</b> Ω) | <b>L (</b> μ <b>H)</b> | C <sub>OUT</sub> (μF) |

|----------------------|-----------------|-----------------|------------------------|-----------------------|

| 1.2V                 | 65.3            | 39.2            | 0.47                   | 22                    |

| 1.8V                 | 117.6           | 39.2            | 1                      | 22                    |

| 2.5V                 | 178.6           | 39.2            | 1                      | 22                    |

| 3.3V                 | 248.3           | 39.2            | 1                      | 22                    |

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

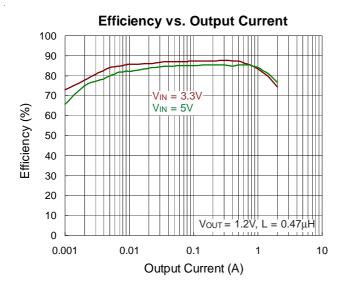

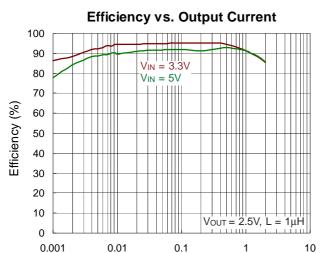

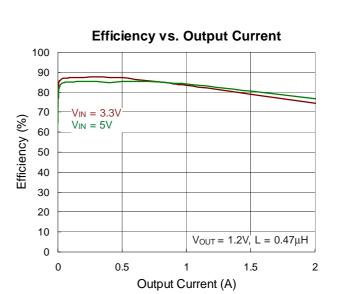

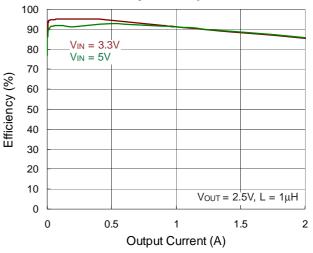

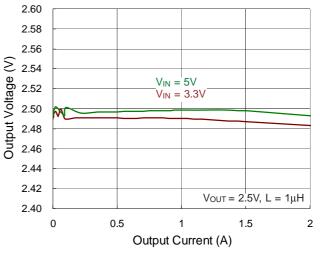

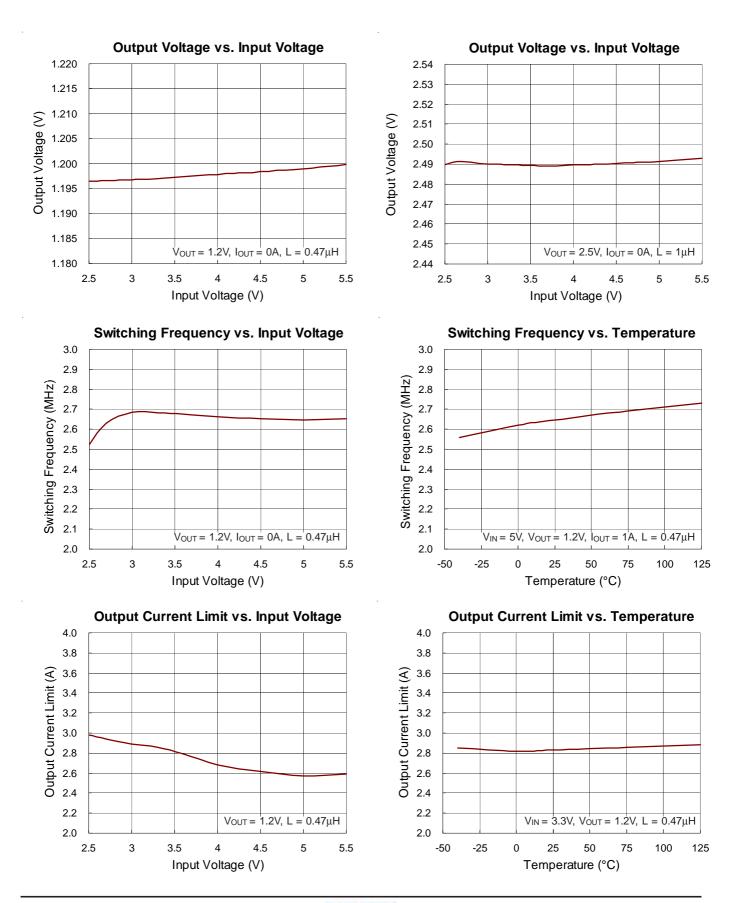

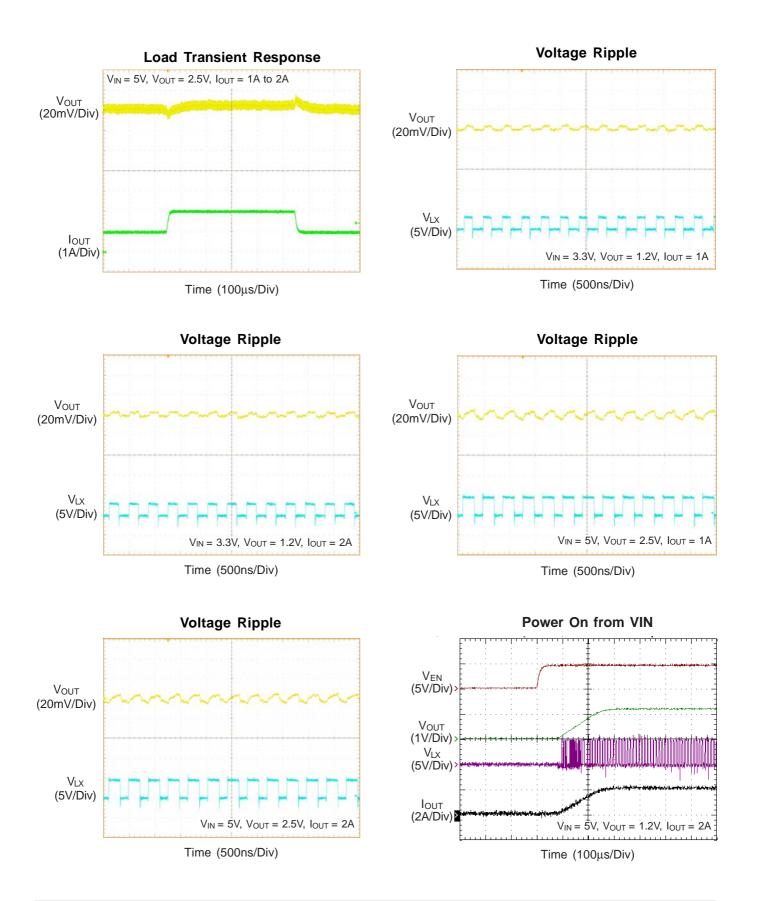

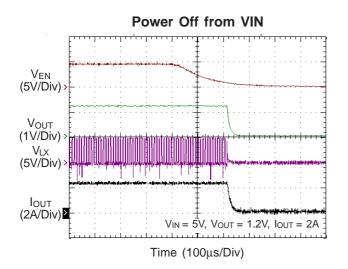

## **Typical Operating Characteristics**

Output Current (A)

1

Output Current (A)

Efficiency vs. Output Current

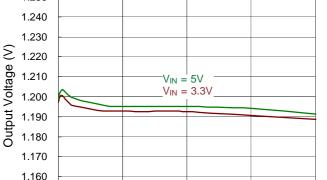

**Output Voltage vs. Output Current**

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

2

$V_{OUT} = 1.2V$ , L = 0.47 $\mu$ H

1.5

DSQ2102A-QA-02 October 2019

0.5

1.150

0

Copyright ©2019 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

8

RICHTEK

Copyright ©2019 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation. DSQ2102A-QA-02 October 2019 www.richtek

Copyright ©2019 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation. www.richtek.com DSQ2102A-QA-02 October 2019 10

Copyright ©2019 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

### **Application Information**

The RTQ2102A-QA is a single-phase step-down converter. Advance Constant-on-Time (ACOT) with fast transient response. An internal 0.45V reference allows the output voltage to be precisely regulated for low output voltage applications. A fixed switching frequency (2.7MHz) oscillator and internal compensation are integrated to minimize external component count. Protection features include over current protection, under voltage protection and over temperature protection.

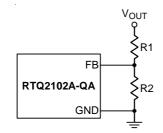

#### **Output Voltage Setting**

The output voltage is set by an external resistive divider according to the following equation :

$$V_{OUT} = V_{REF} \times (1 + \frac{R1}{R2})$$

where VREF equals to 0.45V typical. The resistive divider allows the FB pin to sense a fraction of the output voltage as shown in Figure 1.

Figure 1. Setting the Output Voltage

#### Low Supply Operation

The RTQ2102A-QA is designed to operate down to an input supply voltage of 3V. One important consideration at low input supply voltages is that the  $R_{DS(ON)}$  of the P-Channel and N-Channel power switches increases. The user should calculate the power dissipation when the RTQ2102A-QA is used at 100% duty cycle with low input voltages to ensure that thermal limits are not exceeded.

#### **Under Voltage Protection (UVP)**

#### **Hiccup Mode**

For the RTQ2102A-QA, it provides Hiccup Mode Under Voltage Protection (UVP). When the output voltage is lower than 66% reference voltage after soft-start, the UVP is triggered. If the UVP condition remains for a period, the RTQ2102A-QA will retry automatically. When the UVP condition is removed, the converter will resume operation. The UVP is disabled during soft-start period.

#### CIN and COUT Selection

The input capacitance,  $C_{IN}$ , is needed to filter the trapezoidal current at the source of the top MOSFET. To prevent large ripple voltage, a low ESR input capacitor sized for the maximum RMS current should be used. RMS current is given by :

$$I_{RMS} = I_{OUT(MAX)} \frac{V_{OUT}}{V_{IN}} \sqrt{\frac{V_{IN}}{V_{OUT}}} - 1$$

This formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} = I_{OUT} / 2$ . This simple worst case condition is commonly used for design because even significant deviations do not result in much difference. Choose a capacitor rated at a higher temperature than required.

Several capacitors may also be paralleled to meet size or height requirements in the design.

The selection of  $C_{OUT}$  is determined by the effective series resistance (ESR) that is required to minimize voltage ripple and load step transients, as well as the amount of bulk capacitance that is necessary to ensure that the control loop is stable. Loop stability can be checked by viewing the load transient response. The output ripple,  $\Delta V_{OUT}$ , is determined by :

$$\Delta V_{OUT} \leq \Delta I_{L} \left[ \text{ESR} + \frac{1}{8 f C_{OUT}} \right]$$

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com 12

The output ripple is highest at maximum input voltage since  $\Delta I_L$  increases with input voltage. Multiple capacitors placed in parallel may be needed to meet the ESR and RMS current handling requirements. Dry tantalum, special polymer, aluminum electrolytic and ceramic capacitors are all available in surface mount packages. Special polymer capacitors offer very low ESR, but have lower capacitance density than other types. Tantalum capacitors have the highest capacitance density, but it is important to only use types that have been surge tested for use in switching power supplies. Aluminum electrolytic capacitors have significantly higher ESR, but can be used in cost-sensitive applications provided that consideration is given to ripple current ratings and long term reliability. Ceramic capacitors have excellent low ESR characteristics, but can have a high voltage coefficient and audible piezoelectric effects.

The high Q of ceramic capacitors with trace inductance can also lead to significant ringing.

#### Using Ceramic Input and Output Capacitors

Higher value, lower cost ceramic capacitors are now becoming available in smaller case sizes. Their high ripple current, high voltage rating and low ESR make them ideal

for switching regulator applications. However, care must be taken when these capacitors are used at the input and output. When a ceramic capacitor is used at the input and the power is supplied by a wall adapter through long wires, a load step at the output can induce ringing at the input, VIN. At best, this ringing can couple to the output and be mistaken as loop instability. At worst, a sudden inrush of current through the long wires can potentially cause a voltage spike at V<sub>IN</sub> large enough to damage the part.

| Table 2. ( | Capacitors | for C | in and | COUT |

|------------|------------|-------|--------|------|

|------------|------------|-------|--------|------|

| Component<br>Supplier | Part No.          | Capacitance<br>(μF) | Case<br>Size |  |

|-----------------------|-------------------|---------------------|--------------|--|

| MuRata                | GRM31CR71A106KA01 | 10µF                | 1206         |  |

| MuRata                | GRM31CR71A226KA01 | 22µF                | 1206         |  |

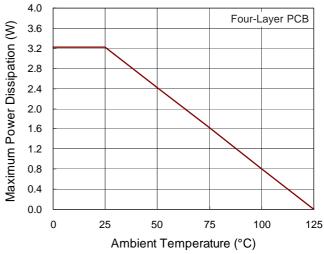

#### **Thermal Considerations**

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula :

#### $P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a WDFN-8L 3x3 package, the thermal resistance,  $\theta_{JA}$ , is 31°C/W on a standard JEDEC 51-7 high effective-thermalconductivity four-layer test board. The maximum power dissipation at  $T_A = 25^{\circ}C$  can be calculated as below :

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (31^{\circ}C/W) = 3.22W$  for a WDFN-8L 3x3 package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 2 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 2. Derating Curve of Maximum Power Dissipation

Copyright @2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

## RICHTEK

#### **Layout Considerations**

Follow the PCB layout guidelines for optimal performance of the RTQ2102A-QA.

- Connect the terminal of the input capacitor(s), C<sub>IN</sub>, as close as possible to the VIN pin. This capacitor provides the AC current into the internal power MOSFETs.

- LX node experiences high frequency voltage swing and should be kept within a small area. Keep all sensitive small-signal nodes away from the LX node to prevent stray capacitive noise pick up.

- Flood all unused areas on all layers with copper. Flooding with copper will reduce the temperature rise of power components. Connect the copper areas to any DC net (V<sub>IN</sub>, V<sub>OUT</sub>, GND, or any other DC rail in the system).

- Connect the FB pin directly to the feedback resistors. The resistive voltage divider must be connected between V<sub>OUT</sub> and GND.

The feedback and must be connected as close to the device as possible. Keep sensitive component away.

Figure 3. PCB Layout Guide

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

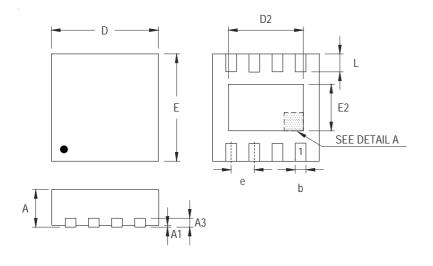

### **Outline Dimension**

DETAIL A Pin #1 ID and Tie Bar Mark Options

Note : The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Complete I | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|------------|------------|----------------|----------------------|-------|--|

| Symbol     | Min        | Max            | Min                  | Max   |  |

| А          | 0.700      | 0.800          | 0.028                | 0.031 |  |

| A1         | 0.000      | 0.050          | 0.000                | 0.002 |  |

| A3         | 0.175      | 0.250          | 0.007                | 0.010 |  |

| b          | 0.200      | 0.300          | 0.008                | 0.012 |  |

| D          | 2.950      | 3.050          | 0.116                | 0.120 |  |

| D2         | 2.100      | 2.350          | 0.083                | 0.093 |  |

| E          | 2.950      | 3.050          | 0.116                | 0.120 |  |

| E2         | 1.350      | 1.600          | 0.053                | 0.063 |  |

| е          | 0.6        | 650            | 0.0                  | )26   |  |

| L          | 0.425      | 0.525          | 0.017                | 0.021 |  |

W-Type 8L DFN 3x3 Package

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

## **Footprint Information**

| Package         | Number of | Footprint Dimension (mm) |      |      |      |      |      |      | Tolerance |           |

|-----------------|-----------|--------------------------|------|------|------|------|------|------|-----------|-----------|

|                 | Pin       | Р                        | А    | В    | С    | D    | Sx   | Sy   | М         | TOIEIANCE |

| V/W/U/XDFN3*3-8 | 8         | 0.65                     | 3.80 | 1.94 | 0.93 | 0.35 | 2.30 | 1.50 | 2.30      | ±0.05     |

#### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

单击下面可查看定价,库存,交付和生命周期等信息

>>Richtek(台湾立锜)