# 12-CH Level Shifter for GOA TFT-LCD Panel

# **General Description**

The RT8935 is a high voltage level shifter. This device is suitable for GOATFT-LCD panel applications.

The level shifter is designed for generating a high voltage signal to drive the TFT-LCD panel. Twelve outputs are provided to switch between VGL and VGH to charge and discharge capacitive loads up to 5nF.

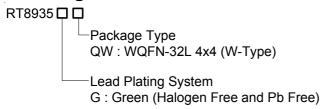

# **Ordering Information**

#### Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

# **Marking Information**

4J=: Product Code

YMDNN: Date Code

# **Features**

- 2.6V to 5.5V Input Logic Level Range

- -15V to 40V Output Voltage Range

- Rise/Fall Time 700ns (Max)

- Protection Functions: UVLO, OTP

- RoHS Compliant and Halogen Free

# **Applications**

GOATFT-LCD Panel

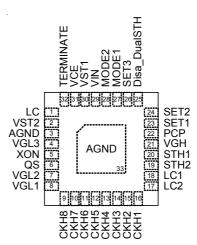

# **Pin Configuration**

(TOP VIEW)

WQFN-32L 4x4

# **Typical Application Circuit**

# **Functional Pin Description**

| Pin No.                | Pin Name     | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                      | LC           | Level shifter input signal (Low frequency clock).                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2                      | VST2         | Level shifter input signal (Start Pulse for GOA Share) The VST2 is the rising edge trigger.                                                                                                                                                                                                                                                                                                                                                                                       |

| 3, 33<br>(Exposed Pad) | AGND         | Analog ground for logic block. The exposed pad must be soldered to a large PCB and connected to AGND for maximum power dissipation.                                                                                                                                                                                                                                                                                                                                               |

| 4                      | VGL3         | Negative power supply for XON.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5                      | XON          | Discharge function for liquid crystal capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6                      | QS           | Charge shaping resistor connection.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7                      | VGL2         | Negative power supply for CKH1 to CKH8.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8                      | VGL1         | Negative power supply for STH1, STH2, LC1 and LC2.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9 to 16                | CKH8 to CKH1 | Level shifter output with charge sharing function.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 17                     | LC2          | Level shifter output signal (Low Frequency Clock 2).                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 18                     | LC1          | Level shifter output signal (Low Frequency Clock 1).                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 19                     | STH2         | Level shifter output signal (Start Pulse for Rotate).                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 20                     | STH1         | Level shifter output signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 21                     | VGH          | Positive power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 22                     | PCP          | Set pin for charge sharing timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 23                     | SET1         | Setting pin for phase selection.  High Level: 8 phase  Low Level: 6 phase  Floating: 4 phase.  The setting will trigger and latch the phase selection function by each VST1 rising edge. (Note: It is suggested that the pin is fixed by VIN or GND or not connect in the application.)  High Level: Connected to VIN  Low Level: Connected to GND  Floating: Not Connect                                                                                                         |

| 24                     | SET2         | Setting pin for clocks interval. High Level : There is no time interval between CKHs. Low Level or floating : There is some time interval between CKHs. The setting will trigger and latch the Clocks Interval function by each VST1 rising edge. (Note : It is suggested that the pin is fixed by VIN or GND or Not Connect in the application.) Connected $400 k\Omega$ to GND inside RT8935. High Level : Connected to VIN Low Level : Connected to GND Floating : Not Connect |

Copyright ©2018 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

3

| Pin No. | Pin Name     | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25      | Disa_DualSTH | Disable control input for dual STH output. High Level : STH1 On (follow VST1), STH2 keeps in VGL1 Low Level : STH1 On (follow VST1), STH2 On (follow VST2) Connected $400k\Omega$ to GND and $400k\Omega$ to VIN inside RT8935. High Level : Connected to VIN Low Level : Connected to GND Floating is not allowed                                                                                                                                           |

| 26      | SET3         | Set pin for charge sharing mode. High level: Enable charge sharing mode1 Low level: Enable charge sharing mode2 Floating: Disable charge sharing mode The setting will trigger and latch the charge sharing mode function by VST1 rising edge. (Note: It is suggested that the pin is fixed by VIN or GND or Not Connect in the application) High level: Connected to VIN Low level: Connected to GND Floating: Not Connect                                  |

| 27      | MODE1        | Receiving signal for pre-charge selection.  High Level: 1-line pre-charge  Low Level: No pre-charge  Middle: 2-line pre-charge  The mode1 will trigger and latch by each VST1 rising edge.  The signal can change real time.  High Level: 1.5V to 5.5V (ex: Connected to VIN)  Low Level: 0 to 0.8V (ex: Connected to GND)  Middle Level: 0.9V to 1.4V (ex: Voltage Divide)                                                                                  |

| 28      | MODE2        | Receiving signal for pre-charge selection High level: Enable 3-line pre-charge function Low level or Middle: Keep MODE1 Setting The setting will trigger and latch the charge sharing mode function by VST1 rising edge. (Note: It is suggested that the pin is fixed by VIN or GND or Not Connect in the application) High level: 1.5V to 5.5V (ex: Connected to VIN) Low level: 0 to 0.8V (ex: Connected to GND) Middle: 0.9V to 1.4V (ex: Voltage Divide) |

| 29      | VIN          | Supply voltage input.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 30      | VST1         | Level shifter input signal (Start Pulse).                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 31      | VCE          | Level shifter input signal (Condensed Clock).                                                                                                                                                                                                                                                                                                                                                                                                                |

| 32      | TERMINATE    | Level shifter input signal (turn off all buffers in blanking time).                                                                                                                                                                                                                                                                                                                                                                                          |

4

DS8935-00 December 2018

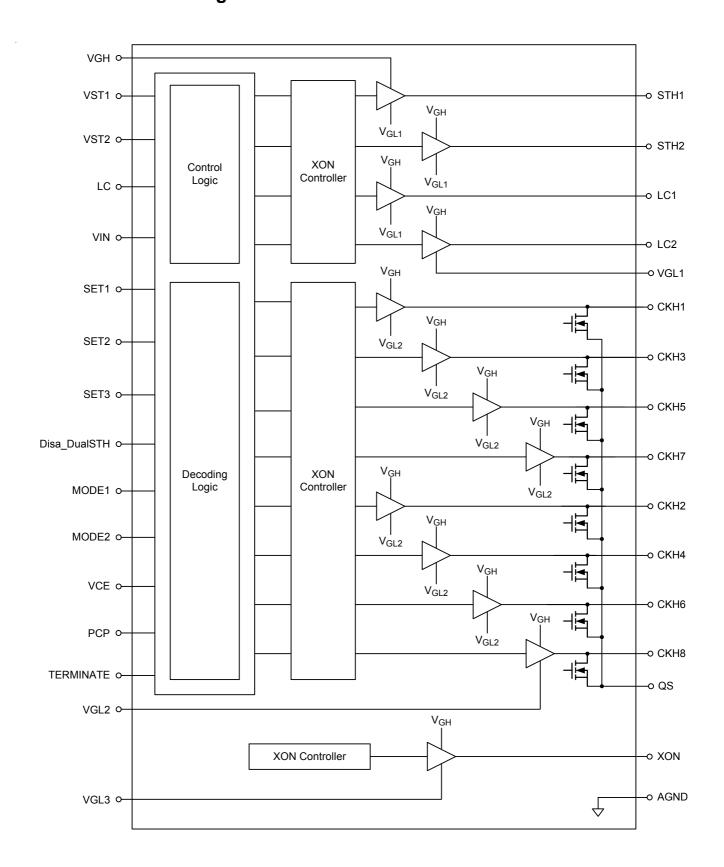

# **Functional Block Diagram**

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

# **Operation**

# **Control Logic and Decoding Logic**

The low voltage input signal will transfer to high voltage output to drive the panel. The output waveform will follow decoding logic command which is based on setting pins results.

Low voltage input pin: VST1, VST2, LC, VCE, PCP, and TERMINAL Setting pin: SET1, SET2, SET3, Disa\_DualSTH, MODE1, and MODE2. High voltage output pin: STH1, STH2, LC1, LC2, CKH1~8, XON, and QS

# Absolute Maximum Ratings (Note 1)

| Supply Input Voltage VIN                                                    | –0.3 to 7V                             |

|-----------------------------------------------------------------------------|----------------------------------------|

| • AGND                                                                      | 0.3 to 0.3V                            |

| <ul> <li>VST1 to VST2, LC, VCE, Disa_DualSTH, PCP</li> </ul>                |                                        |

| SET1 to SET3, TERMINATE, MODE1 to MODE2                                     | 0.3 to 7V                              |

| • VGH                                                                       | 0.3 to 45V                             |

| • VGL1 to VGL3                                                              | –20 to 0.3V                            |

| • VGH – (VGL1 or VGL2 or VGL3)                                              | 0.3 to 60V                             |

| • STH1 and 2, LC1 and 2, CKH1 to CKH8, XON, QS                              | $(V_{GL} + 0.3)V$ to $(V_{GH} - 0.3)V$ |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                                        |

| WQFN 32L 4x4                                                                | 3.59W                                  |

| Package Thermal Resistance (Note 2)                                         |                                        |

| WQFN 32L 4x4, $\theta_{JA}$                                                 | 27.8°C/W                               |

| WQFN 32L 4x4, $\theta_{JC}$                                                 | 7°C/W                                  |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C                                  |

| Junction Temperature                                                        | 150°C                                  |

| Storage Temperature Range                                                   |                                        |

| ESD Susceptibility (Note 3)                                                 |                                        |

| HBM (Human Body Model)                                                      | 2kV                                    |

| Recommended Operating Conditions (Note 4)                                   |                                        |

| Recommended Operating Conditions (Note 4)                                   |                                        |

# **Electrical Characteristics**

$(V_{IN} = 3.3V, V_{GH} = 30V, V_{GL1} = V_{GL2} = -10V, V_{GL3} = -6V, AGND = 0V with typical values T_A = 0°C to 85°C, unless otherwise specified)$

| Parameter                         | Symbol  | Test Conditions              | Min | Тур | Max | Unit  |

|-----------------------------------|---------|------------------------------|-----|-----|-----|-------|

| Supply Current                    |         |                              |     |     |     |       |

| Supply Voltage                    | VIN     |                              | 2.6 |     | 5.5 | V     |

| VIN Quiescent Current             | IQ_VIN  |                              |     | 60  |     | μΑ    |

| VIN Under Voltage NG Lockout      | Mana o  | VIN rising, hysteresis 200mV | 1.9 | 2   | 2.1 | V     |

| Threshold                         | Vuvlo   | VIN falling                  | 1.7 | 1.8 | 1.9 | \ \ \ |

| VGH Under-Voltage Lockout         | Vuvlogh | VIN rising, hysteresis 200mV | 6.2 |     | 6.9 | V     |

| Threshold                         |         | VGH falling                  | 6   |     | 6.7 | v     |

| Thermal Shutdown                  | TsD     | Junction temperature rising  | 150 |     | 160 | °C    |

| Internal Pull Up or Down Resistor |         |                              |     | 400 |     | kΩ    |

| Level Shifter                     |         |                              |     |     |     |       |

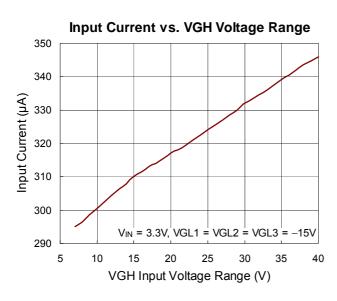

| VGH to GND                        | VgH     |                              | 7   |     | 40  | V     |

| VGL1 Operating Voltage Range      | VGL1    |                              | -15 |     | 0   | V     |

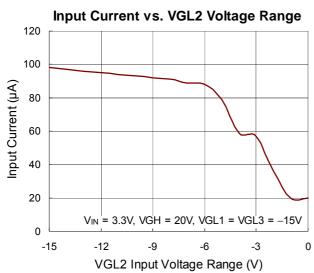

| VGL2 Operating Voltage Range      | VGL2    |                              | -15 |     | 0   | V     |

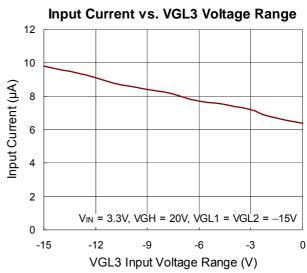

| VGL3 Operating Voltage Range      | VGL3    |                              | -15 |     | 0   | V     |

Copyright ©2018 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

DS8935-00 December 2018 www.richtek.com

| Parameter                                          |               | Symbol          | Test Conditions                                                                                                 | Min                       | Тур                       | Max                       | Unit |  |

|----------------------------------------------------|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|------|--|

| VGH Quiescent Current                              |               | IQ_VGH          |                                                                                                                 |                           | 340                       |                           | μΑ   |  |

| VGL1 Quiescent C                                   | urrent        | IQ_GL1          |                                                                                                                 |                           | 10                        |                           | μΑ   |  |

| VGL2 Quiescent C                                   | urrent        | IQ_GL2          |                                                                                                                 |                           | 70                        |                           | μΑ   |  |

| VGL3 Quiescent C                                   | urrent        | IQ_GL3          |                                                                                                                 |                           | 20                        |                           | μΑ   |  |

| STH1 to STH2, LC                                   | 1 and LC2     | Vout            |                                                                                                                 | 0.3 +<br>V <sub>GL1</sub> | 1                         | V <sub>GH</sub> – 0.3     | ٧    |  |

| CKH1 to CKH8                                       |               | Vout            |                                                                                                                 | 0.3 +<br>VGL2             |                           | V <sub>GH</sub> – 0.3     | ٧    |  |

| VCE, Terminate,<br>Disa_DualSTH,<br>VST1 and VST2, | Logic-High    | ViH             | V <sub>IN</sub> = 2.6V to 5.5V                                                                                  | 1.5                       |                           |                           | V    |  |

| and LC PCP Input<br>Voltage                        | Logic-High    | VIL             | V <sub>IN</sub> = 2.6V to 5.5V                                                                                  |                           |                           | 0.8                       | •    |  |

|                                                    | High-Level    |                 |                                                                                                                 | 1.5                       |                           | 5.5                       | V    |  |

| MODE 1                                             | Middle-Level  |                 |                                                                                                                 | 0.9                       |                           | 1.4                       | V    |  |

|                                                    | Low Level     |                 |                                                                                                                 | 0                         |                           | 0.8                       | V    |  |

| MODE 2                                             | High-Level    |                 |                                                                                                                 | 1.5                       |                           |                           | V    |  |

|                                                    | Low-Level     |                 |                                                                                                                 |                           |                           | 0.8                       | V    |  |

| VGH – (VGL1 or 2                                   | or 3)         |                 |                                                                                                                 |                           |                           | 55                        | V    |  |

| CKH1 to CKH8, ST<br>LC1 and 2, Positive<br>Swing   |               | VCK+            | All inputs high, IOUT = -10mA                                                                                   | VGH -<br>0.5              | VGH -<br>0.2              | Vgн                       | ٧    |  |

| STH1 and 2, LC1 a<br>Negative Output Sv            |               | VCK-            | All inputs low, IOUT = -10mA                                                                                    | V <sub>G</sub> L1         | VGL1<br>+ 0.2             | VGL1<br>+ 0.5             | >    |  |

| CKH1 to CKH8 Neg<br>Swing                          | gative Output | VCK-            | All inputs low, IOUT =10mA                                                                                      | V <sub>GL2</sub>          | V <sub>GL2</sub><br>+ 0.2 | V <sub>GL2</sub><br>+ 0.5 | V    |  |

| QS Switch On-Res                                   | istance       | RLS_On          | I <sub>OUT</sub> = ±10mA                                                                                        |                           | 20                        | 50                        | Ω    |  |

| CKH1 to CKH8,                                      | Rising Time   | t <sub>R</sub>  | V <sub>GH</sub> = 30V, V <sub>GL</sub> 1, 2 = -10V, R <sub>L</sub> = 50J,<br>C <sub>L</sub> = 4.7nF, 10% to 90% |                           | 1                         | 700                       | 2    |  |

| STH1 and 2, LC1 and 2                              | Falling Time  | tF              | V <sub>GH</sub> = 30V, V <sub>GL1</sub> , 2 = -10V, R <sub>L</sub> = 50J,<br>C <sub>L</sub> = 4.7nF, 90% to 10% |                           | 1                         | 700                       | ns   |  |

| CKH1 to CKH8,<br>STH1 and 2, LC1                   | Rising Time   | trd             | VGH = $30V$ , VGOL1, $2 = -10V$<br>50% of input to $10\%$ of output                                             |                           | 150                       | 250                       |      |  |

| and 2, Delay Time                                  | Falling Time  | t <sub>FD</sub> | $V_{GH} = 30V$ , $V_{GL1, 2} = -10V$<br>50% of input to 90% of output                                           |                           | 150                       | 250                       | ns   |  |

| XON Rising Time                                    |               | txon            | V <sub>GH</sub> = 30V, V <sub>GL2</sub> = V <sub>GL3</sub> = -6V,<br>C <sub>L</sub> = 4.7nF, 10% to 90%         |                           | 1                         |                           | μS   |  |

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

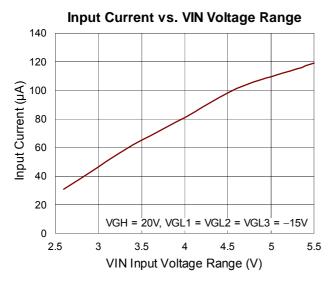

# **Typical Operating Characteristics**

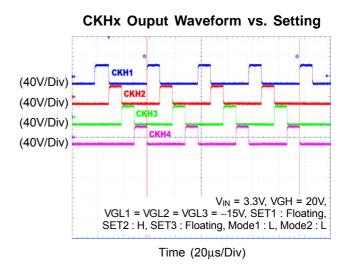

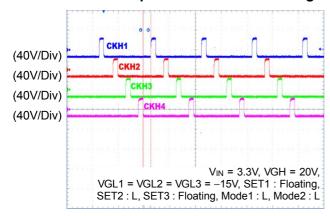

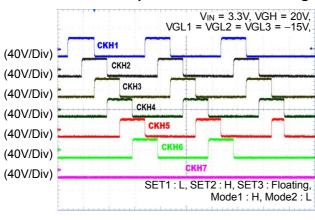

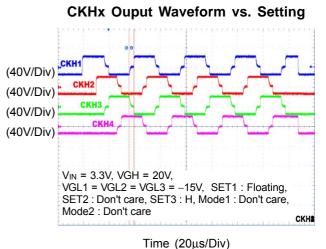

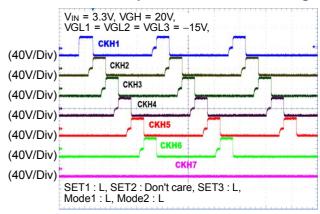

## CKHx Ouput Waveform vs. Setting

Time (20µs/Div)

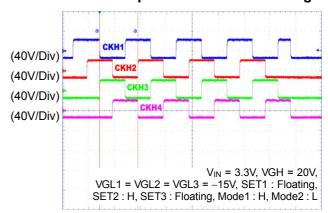

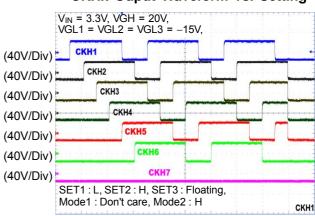

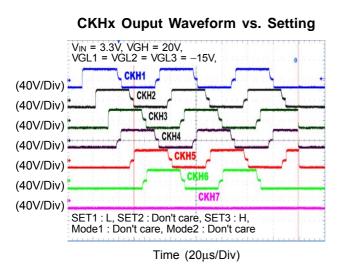

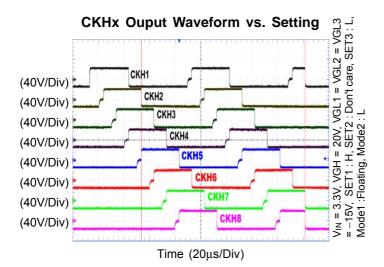

## CKHx Ouput Waveform vs. Setting

Time (20µs/Div)

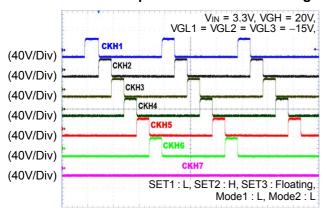

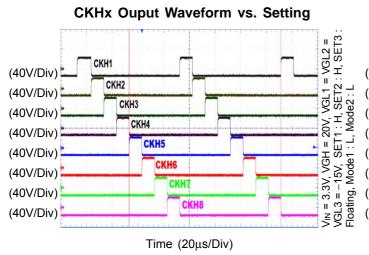

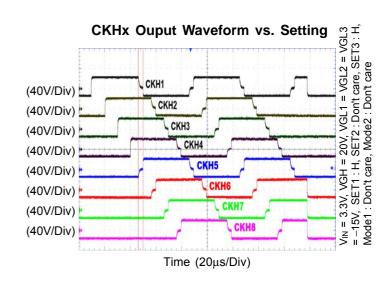

#### CKHx Ouput Waveform vs. Setting

Time (20µs/Div)

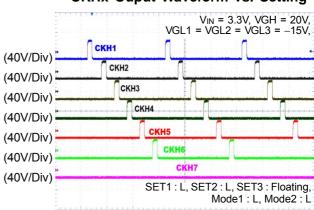

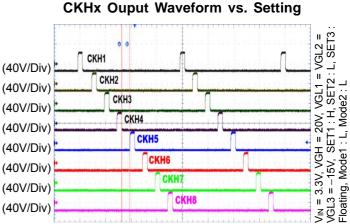

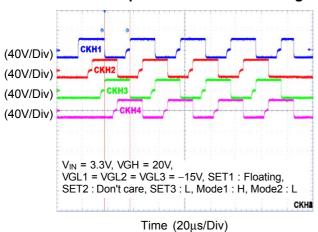

## CKHx Ouput Waveform vs. Setting

Time (20µs/Div)

## **CKHx Ouput Waveform vs. Setting**

Time (20µs/Div)

# CKHx Ouput Waveform vs. Setting

Time (20µs/Div)

Time (20µs/Div)

## CKHx Ouput Waveform vs. Setting V<sub>IN</sub> = 3.3V, VGH = 20V, VGL1 = VGL2 = VGL3 = -15V, SET1: H, SET2: H, SET3 Floating, Mode1: Don't care, Mode2: H CKH1 (40V/Div) CKH<sub>2</sub> (40V/Div) CKH3 (40V/Div) CKH4 (40V/Div) CKH5 (40V/Div) (40V/Div) CKH7 (40V/Div) (40V/Div) Time (20µs/Div)

# CKHx Ouput Waveform vs. Setting

# CKHx Ouput Waveform vs. Setting

Time (20µs/Div)

# **Application Information**

## **General Description**

The RT8935 provides 12-channel level shifter designed to drive the GOA panel. This device converts the logic-level signals generated by the Timing Controller (T-CON) to high-level signals required by GOA panel.

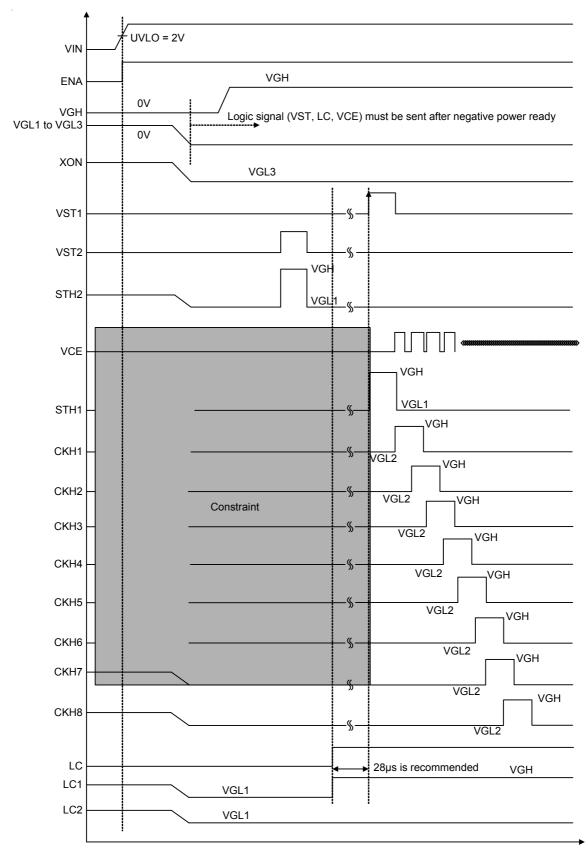

# **Power On Sequence**

When the VIN exceeds UVLO, the internal signal ENA for condensed GOA logic will be high. The outputs of Level Shifter CKH1 to CKH8, and XON should follow  $V_{GL3}$  level since VIN exceeds UVLO. The outputs of Level Shifter LC1, LC2, STH1, and STH2 should follow V<sub>GL1</sub> level since VIN exceeds UVLO. After ENA is high, CKH1 to CKH8 do not output since receiving the first VST1 rising edge. After ENA is high, LC1 will start to follow LC and LC2 will start to be inverting of LC as the 1st LC transition or the 1st VST1 rising.

According to GOA experience, it is recommended that 1. LC1 and LC2 start to work earlier than the 1st STH1 or STH2. Logic signal (VST1 to VST2, LC, VCE) must be sent after negative power ready.

Table 1. Power On (from 0 to VIN) Condition List-1

|      | Analog Power Input |          |                 | Logic Input         |                      |                     | Analog Output       |                     |                     |      |

|------|--------------------|----------|-----------------|---------------------|----------------------|---------------------|---------------------|---------------------|---------------------|------|

| Case | VIN                | VGH      | VGL1 to<br>VGL3 | VST1                | VCE                  | LC                  | STH1                | CKH1 to<br>CKH8     | LC1, LC2            | XON  |

| 1    | > UVLO             | > UVLOGH | Don't Care      | w/<br>Signal        | w/<br>Signal         | w/<br>Signal        | Normal<br>Operation | Normal<br>Operation | Normal<br>Operation | VGL3 |

| 2    | > UVLO             | > UVLOGH | Don't Care      | w/<br>Signal        | w/o<br>Signal        | w/<br>Signal        | Normal<br>Operation | VGL2                | Normal<br>Operation | VGL3 |

| 3    | > UVLO             | > UVLOGH | Don't Care      | w/o<br>Signal       | w /<br>Signal        | w /<br>Signal       | VGL1                | VGL2                | Normal<br>Operation | VGL3 |

| 4    | > UVLO             | > UVLOGH | Don't Care      | w/<br>Signal        | w/<br>Signal         | w/o<br>Signal       | Normal<br>Operation | Normal<br>Operation |                     | VGL3 |

| 5    | > UVLO             | > UVLOGH | Don't Care      | w/o<br>Signal       | w/<br>Signal         | w/o<br>Signal       | VGL1                | VGL2                | VGL1                | VGL3 |

| 6    | > UVLO             | < UVLOGH | Don't Care      | w/ or w/o<br>Signal | w/ or w/o<br>Signal  | w/ or w/o<br>Signal | VGL1                | VGL2                | VGL1                | VGL3 |

| 7    | < UVLO             | < UVLOGH | Don't Care      | w/ or w/o<br>Signal | w/ or w/ o<br>Signal | w/ or w/o<br>Signal | VGL1                | VGL2                | VGL1                | VGL3 |

| 8    | < UVLO             | > UVLOGH | Don't Care      | w/ or w/o<br>Signal | w/ or w/o<br>Signal  | w/ or w/o<br>Signal | VGL1                | VGL2                | VGL1                | VGL3 |

www.richtek.com

DS8935-00 December 2018

Table 2. Power On (from 0 to VIN) Condition List-2

|      | <b>Analog Power Input</b> |          |              | Log              | ic Input                   | Analog Output         |                       |  |

|------|---------------------------|----------|--------------|------------------|----------------------------|-----------------------|-----------------------|--|

| Case | VIN                       | VGH      | VGL1 to VGL3 | VST1             | VST2<br>(Disa_DualSTH = 0) | STH1<br>(follow VST1) | STH2<br>(follow VST2) |  |

| 1    | > UVLO                    | > UVLOGH | Don't Care   | w/Signal         | w/Signal                   | Normal<br>Operation   | Normal<br>Operation   |  |

| 2    | > UVLO                    | > UVLOGH | Don't Care   | w/Signal         | w/o Signal                 | Normal<br>Operation   | VGL1                  |  |

| 3    | > UVLO                    | > UVLOGH | Don't Care   | w/o Signal       | w/Signal                   | VGL1                  | Normal<br>Operation   |  |

| 4    | > UVLO                    | > UVLOGH | Don't Care   | w/o Signal       | w/o Signal                 | VGL1                  | VGL1                  |  |

| 5    | > UVLO                    | < UVLOGH | Don't Care   | w/ or w/o Signal | w/ or w/o Signal           | VGL1                  | VGL1                  |  |

| 6    | < UVLO                    | < UVLOGH | Don't Care   | w/ or w/o Signal | w/ or w/o Signal           | VGL1                  | VGL1                  |  |

| 7    | < UVLO                    | > UVLOGH | Don't Care   | w/ or w/o Signal | w/ or w/o Signal           | VGL1                  | VGL1                  |  |

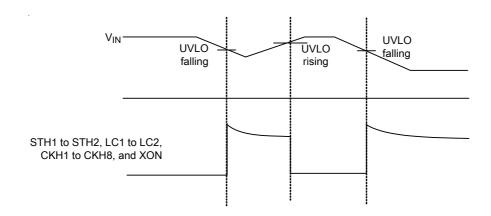

Figure 1. Power On Sequence

17

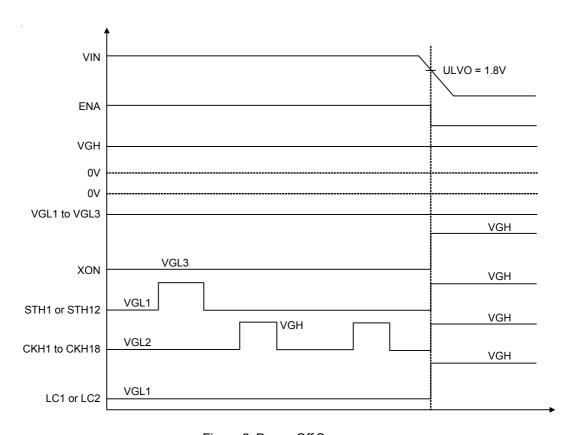

## **Power Off Sequence**

Once the VIN falls below the UVLO threshold, the RT8935 will have the following actions. Pull all level-shift outputs as high level (Note 5) (including XON, STH1 to STH2, LC1 to LC2, and CKH1 to CKH8). (Note 6)

- Note 5. For the tri-state setting pin, it is connected an internal 400k $\Omega$  resistor to VIN and internal 400k $\Omega$  resistor to GND.

- Note 6.  $V_{GH}$  has internal regulator for logic power. We suggest don't repower no at 1V  $V_{GH}$  4V.

| Table 3 | . Power | Off (fro | m vin to | U) Con | aition L | ISt |

|---------|---------|----------|----------|--------|----------|-----|

|         |         |          |          |        |          |     |

|      | An     | Analog Power Input Logic Input |                 |                                          |                     | Analog Output       |               |                 |               |               |

|------|--------|--------------------------------|-----------------|------------------------------------------|---------------------|---------------------|---------------|-----------------|---------------|---------------|

| Case | VIN    | VGH                            | VGL1 to<br>VGL3 | VST1, VST2<br>(Disa_DualSTH = 0<br>or 1) | VCE                 | LC                  | STH1,<br>STH2 | CKH1 to<br>CKH8 | LC1, LC2      | XON           |

| 1    | < UVLO | > UVLOGH                       | Don't Care      | w/ or w/o Signal                         | w/ or w/o<br>Signal | w/ or w/o<br>Signal | Follow<br>VGH | Follow<br>VGH   | Follow<br>VGH | Follow<br>VGH |

| 2    | > UVLO | < UVLOGH                       | Don't Care      | w/ or w/o Signal                         | w/ or w/o<br>Signal | w/ or w/o<br>Signal | VGL1          | VGL2            | VGL1          | VGL3          |

| 3    | < UVLO | < UVLOGH                       | Don't Care      | w/ or w/o Signal                         | w/ or w/o<br>Signal | w/ or w/o<br>Signal | VGL1          | VGL2            | VGL1          | VGL3          |

Figure 2. Power Off Sequence

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS8935-00 December 2018 www.richtek.com

#### **Protection**

The RT8935 provides Over-Temperature Protection (OTP), Under-Voltage Lockout (UVLO). The following table shows the main behavior of each protection.

| Function Protection             | Level<br>Shifter |

|---------------------------------|------------------|

| UVLO (Falling), VIN High to Low | $V_{GON}$        |

| OTP T > 150°C                   | OFF (Hi-Z)       |

# **Over-Temperature Protection (OTP)**

Over-Temperature Protection prevents the RT8935 from overheating due to excessive power dissipation. When the junction temperature exceeds  $T_J$  = 150°C, the OTP will be triggered and latche the device, which also shuts down all outputs. Cycle the VIN (below the UVLO falling threshold) will clear the fault latch and reactivate the device.

| Function Protection | Level<br>Shifter |

|---------------------|------------------|

| OTP, T > 150°C      | OFF (Hi-Z)       |

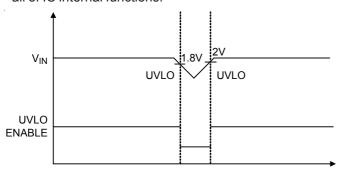

# **Under-Voltage Lockout (UVLO)**

The UVLO circuit compares the input voltage at VIN with the UVLO threshold (2V rising, 1.8V falling, typ.) to ensure the input voltages is high enough for reliable operation. The 200mV (typ.) hysteresis prevents supply transients from causing a shutdown. Once the VIN exceeds the UVLO rising threshold, start-up begins. When VIN falls below the UVLO falling threshold, the controller turns off all of IC internal functions.

| Function Protection                              | Level<br>Shifter |

|--------------------------------------------------|------------------|

| UVLO (Falling), VIN High to Low,<br>VGH > UVLOGH | $V_{GH}$         |

# **Level Shift Function**

The RT8935 contains 12-channels level shifter. It is for GOA (Gate On Array) tech. There are 4 signals to generate STH1 to STH2, LC1 to LC2, and CKH1 to CKH8.  $V_{GL2}$  is the low voltage level for CKH1 to CKH8.  $V_{GL1}$  is the low voltage level for STH1 to STH2 and LC1 to LC2. Settings of level shifter output are listed bellow.

#### **Terminate**

Terminate signal is used to pull low the gate pulses which no more VCE edges can terminate in blanking. Terminate will be high right after the last VCE falling edge. If Terminate is pull to GND, the gate pulses will be pull low as the next VST rising edge. This pin will to GND with an internal  $400k\Omega$  resistor.

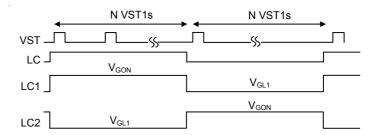

#### LC

For GOA circuit, two low frequency and complementary signals are needed. LC1 will follow LC and have transients between  $V_{GON}$  and  $V_{GL1}$ . LC2 will be the inverting of LC1. LC has transients before VST rising in the blanking.

#### Setting

The SET1/2/3 mode1/mode2 will trigger and latch the function by each VST1 rising edge. The state can not be changed real time except noise interference.

## Mode1, Mode2

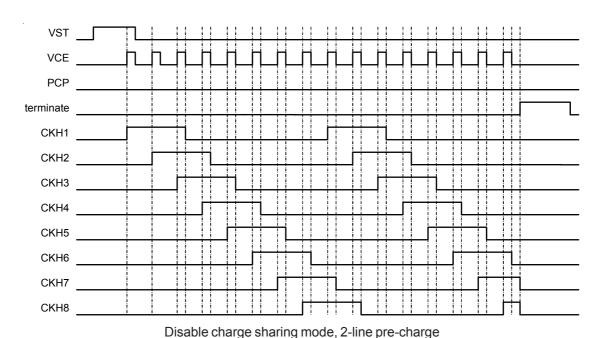

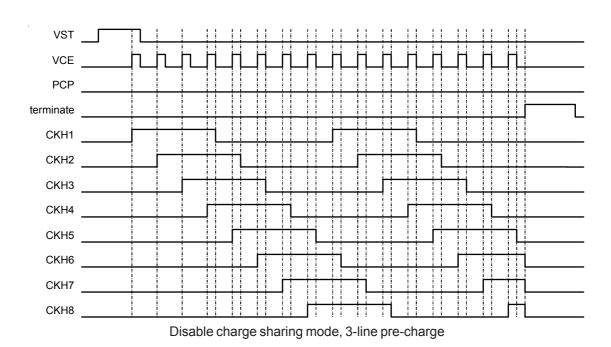

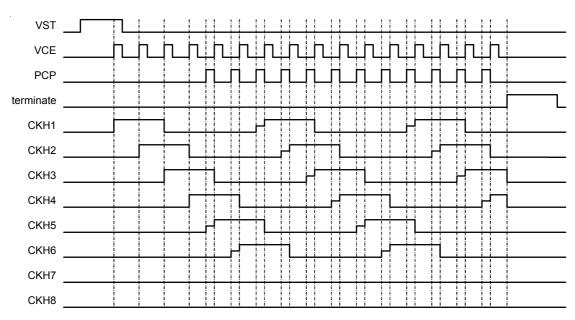

Mode1, Mode2 are the function of pre-charge type. The Mode1 pin will "don't care" at the 3-line pre-charge function. 8 phase for example, the no pre-charge is CKH1 to CKH8 as below.

Disable charge sharing mode, No pre-charge

The 1-line pre-charge is CKH1 to CKH8 as below.

Disable charge sharing mode, 1-line pre-charge

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS8935-00 December 2018 www.richtek.com

The 2-line pre-charge is CKH1 to CKH8 as below.

The 3-line pre-charge is CKH1 to CKH8 as below.

DS8935-00 December 2018

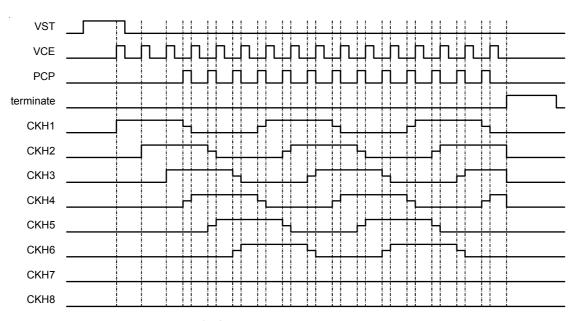

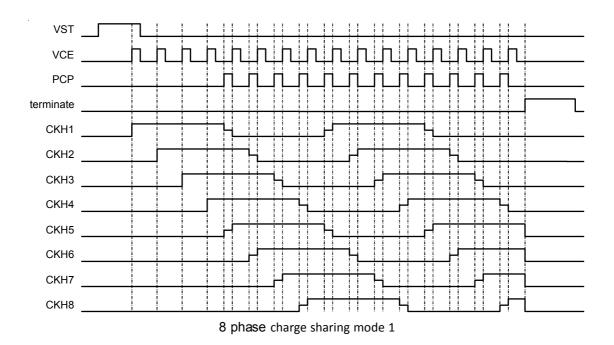

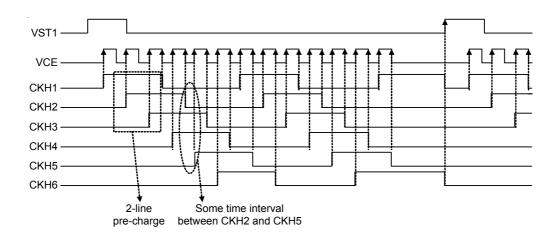

Set3 is the function of charge sharing mode type. The Set2 pin will "don't care" at the charge sharing mode. For example, the waveform [Set1, Set2, Set3, Mode1, Mode2] = [Low, Don't care, High, Don't care, Don't care] is as below.

6 phase charge sharing mode 1

The waveform [Set1, Set2, Set3, Mode1, Mode2] = [High, Don't care, High, Don't care, Don't care] is as below.

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

The waveform [Set1, Set2, Set3, Mode1, Mode2] = [Low, Don't care, Low, High, Low] is as below.

6 phase 1-line pre-charge charge sharing mode 2

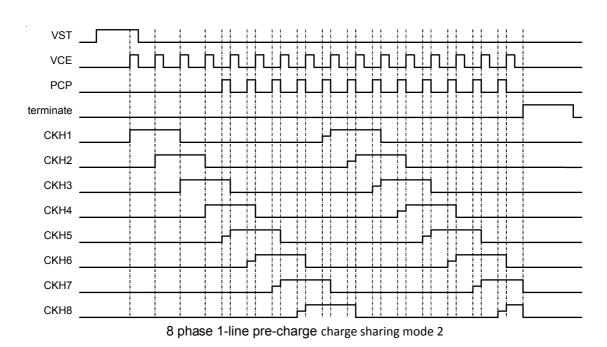

The waveform [Set1, Set2, Set3, Mode1, Mode2] = [High, Don't care, Low, High, Low] is as below.

22

# Table 4. The Setting and Mode Table

| Pin   | Status                    | Level Shifter Output                                                                 |  |  |

|-------|---------------------------|--------------------------------------------------------------------------------------|--|--|

| SET1  | VIN                       | 8 phases. CKH1 to CKH 8 output.                                                      |  |  |

|       | GND                       | 6 phases. CKH1 to CKH 6 output. CkH7 and 8 keep in VGL2.                             |  |  |

|       | Floating                  | 4 phases. CKH1 to CKH 4 output. CkH5 to 8 keep in VGL2.                              |  |  |

| SET2  | VIN                       | There is no time interval between CKHs.                                              |  |  |

|       | GND/Floating              | There is some time interval between CKHs. The time interval can be adjusted by Tcon. |  |  |

| SET3  | VIN                       | Enable charge sharing mode 1.                                                        |  |  |

|       | GND                       | Enable charge sharing mode 2.                                                        |  |  |

|       | Floating                  | Disable charge sharing mode.                                                         |  |  |

| MODE1 | Logic signal high         | 1-line pre-charge.                                                                   |  |  |

|       | Logic signal low          | No pre-charge.                                                                       |  |  |

|       | Floating                  | 2-line pre-charge.                                                                   |  |  |

| MODE2 | Logic signal high         | 3-line pre-charge.                                                                   |  |  |

|       | Logic signal low/Floating | Keep MODE1 Setting.                                                                  |  |  |

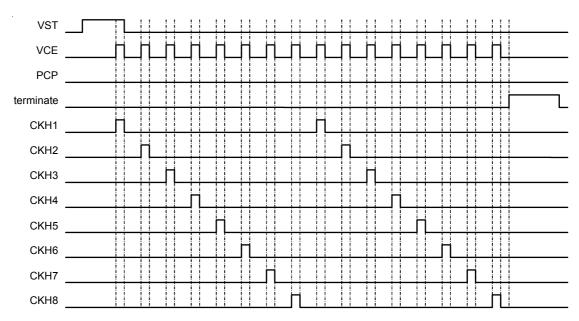

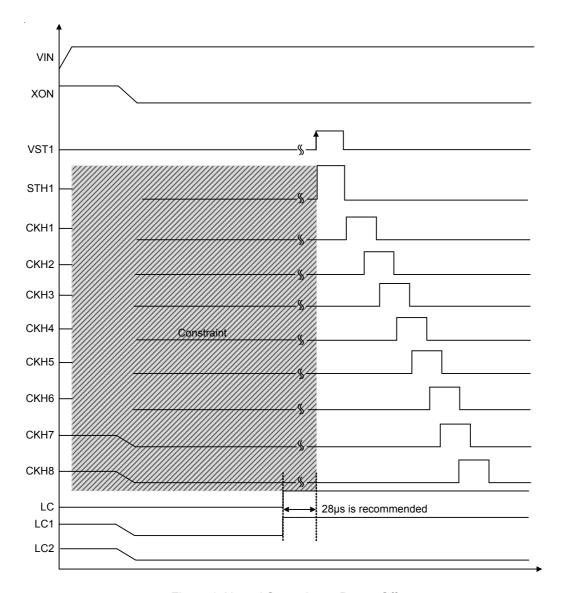

There are two waveforms to show some settings listed above. The settings in the first waveform are in the first waveform is [Set1, Set2, Set3, Mode1, Mode2] = [Low, Low, Floating, Floating, Low].

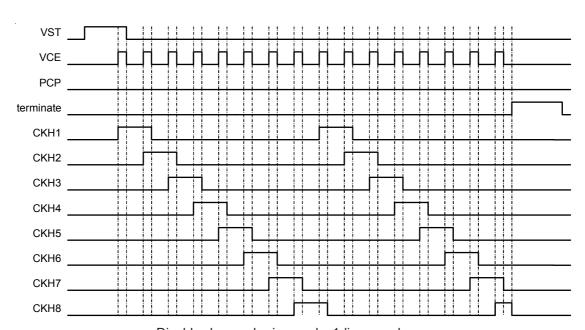

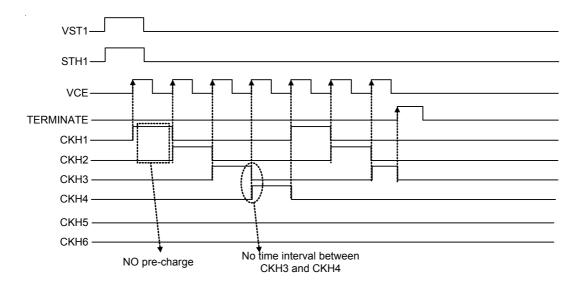

The settings in the second waveform are in the second waveform is [Set1, Set2, Set3, Mode1, Mode2] = [Floating, High, Floating, Floating, Low].

Figure 3. The First Waveform

Figure 4. The Second Waveform

DS8935-00 December 2018

#### **XON Function**

The RT8935 defines a special output timing of the levelshifter output: Once VIN drops below UVLO falling threshold, all the output (include XON, STH1 to STH2, LC1 to LC2, and CKH1 to CKH8) must be pulled high immediately and simultaneously.

When VIN is abnormal as following diagram, XON function will reset (XON is pulled to  $V_{GL3}$ , CKH1 to CKH8 are pulled to V<sub>GL2</sub>, and STH1 to STH2 and LC1 to LC2 are pulled to V<sub>GL1</sub>) no mater what voltage level VIN falls to. If VIN falls below UVLO falling in the constraint region, XON function can still be active. That is, XON, CKH1 to CKH8, STH1 to STH2, and LC1 to LC2 are pulled to VGH.

Figure 5. XON Function at Power Off

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

# **Timing Chart**

Figure 6. Nornal Operation at Power Off

In normal operation, CKH1 to CKH8 would be kept low within constraint till the 1<sup>st</sup> VST rising edge to be received. LC1 to LC2 would be kept low till the 1<sup>st</sup> LC rising edge or 1<sup>st</sup> VST rising edge to be received.

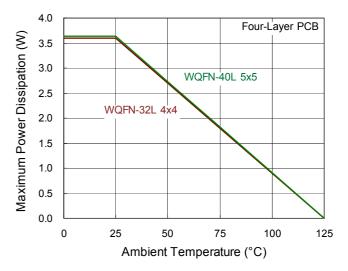

#### **Thermal Considerations**

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula :

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a WQFN 32L 4x4 package, the thermal resistance,  $\theta_{JA}$ , is 27.8°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. For a WQFN-40L 5x5 package, the thermal resistance,  $\theta_{JA}$ , is 27.5°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at  $T_A$  = 25°C can be calculated as below :

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (27.8^{\circ}C/W) = 3.59W$  for a WQFN 32L 4x4 package.

$P_{D(MAX)}$  = (125°C - 25°C) / (27.5°C/W) = 3.64W for a WQFN-40L 5x5 package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 1 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 7. Derating Curve of Maximum Power Dissipation

## **Layout Consideration**

- The VIN input capacitor should be closed the chip.

- The VGH input capacitor should be closed the chip.

- The VGL input capacitor should be closed the chip.

- ▶ The exposed pad of the chip should be connected to ground plane for thermal consideration.

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

27

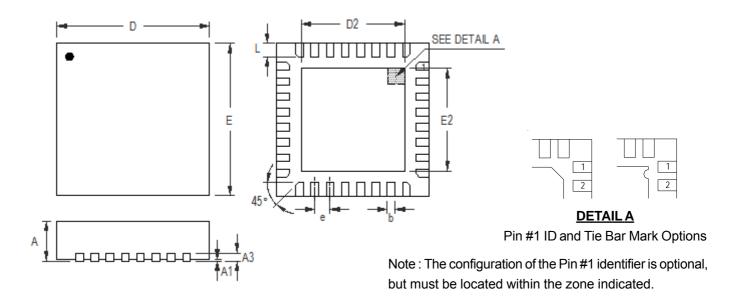

# **Outline Dimension**

| Cumhal | Dimensions In Millimeters |       | Dimensions In Inches |       |

|--------|---------------------------|-------|----------------------|-------|

| Symbol | Min                       | Max   | Min                  | Max   |

| А      | 0.700                     | 0.800 | 0.028                | 0.031 |

| A1     | 0.000                     | 0.050 | 0.000                | 0.002 |

| A3     | 0.175                     | 0.250 | 0.007                | 0.010 |

| b      | 0.150                     | 0.250 | 0.006                | 0.010 |

| D      | 3.900                     | 4.100 | 0.154                | 0.161 |

| D2     | 2.650                     | 2.750 | 0.104                | 0.108 |

| Е      | 3.900                     | 4.100 | 0.154                | 0.161 |

| E2     | 2.650                     | 2.750 | 0.104                | 0.108 |

| е      | 0.400                     |       | 0.016                |       |

| L      | 0.300                     | 0.400 | 0.012                | 0.016 |

W-Type 32L QFN 4x4 Package

# **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

www.richtek.com DS8935-00 December 2018

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Richtek(台湾立锜)