# **Boost Controller with Dimming Control**

## **General Description**

The RT8525 is a wide input operating voltage range step up controller. High voltage output and large output current are feasible by using an external N-MOSFET. The RT8525 input operating range is from 4.5V to 29V.

The RT8525 is an optimized design for wide output voltage range applications. The output voltage of the RT8525 can be adjusted by the FB pin. The PWMI pin can be used as a digital input, allowing WLED brightness control with a logic-level PWM signal.

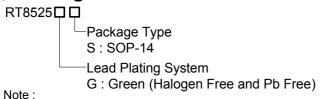

## **Ordering Information**

Richtek products are :

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

## **Marking Information**

DS8525-01 March 2012

#### **Features**

- VIN Range: 4.5V to 29V

- Programmable Soft-Start Time

- Programmable Boost SW Frequency from 50kHz to 600kHz

- Output Over Voltage Protection

- Output Under Voltage Protection

- 14-Lead SOP Package

- RoHS Compliant and Halogen Free

## **Applications**

- LCD TV, Monitor Display Backlight

- LED Driver Application

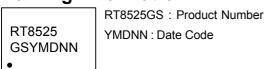

## **Pin Configurations**

(TOP VIEW)

SOP-14

Copyright ©2012 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                                  |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------|

| 1       | VDC      | Output of Internal Pre-Regulator.                                                                                             |

| 2       | VIN      | IC Power Supply.                                                                                                              |

| 3       | COMP     | Compensation for Error Amplifier. Connect a compensation network to ground.                                                   |

| 4       | SS       | External Capacitor to Adjust Soft-Start Time.                                                                                 |

| 5       | FSW      | Frequency Adjust Pin. This pin allows setting the switching frequency with a resistor from 50kHz to 600kHz.                   |

| 6       | AGND     | Analog Ground.                                                                                                                |

| 7       | PWMI     | External Digital Input for Dimming Function.                                                                                  |

| 8       | FAULT    | Open Drain Output for Fault Detection.                                                                                        |

| 9       | FB       | Feedback to Error Amplifier Input.                                                                                            |

| 10      | OOVP     | Sense Output Voltage for Over Voltage Protection and Under Voltage Protection.                                                |

| 11      | ISW      | External MOSFET Switch Current Sense Pin. Connect the current sense resistor between the external N-MOSFET switch and ground. |

| 12      | EN       | Chip Enable (Active High).                                                                                                    |

| 13      | PGND     | Power Ground of Boost Controller.                                                                                             |

| 14      | DRV      | Drive Output for the N-MOSFET.                                                                                                |

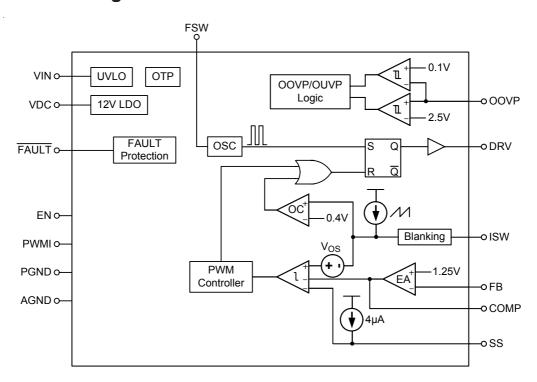

## **Function Block Diagram**

## Absolute Maximum Ratings (Note 1)

| • VIN to GND                                                                | -0.3V to 32V   |

|-----------------------------------------------------------------------------|----------------|

| • VDC, DRV, FAULT to GND                                                    | -0.3V to 13.2V |

| • EN, COMP, SS, FSW, FB, OOVP, ISW, PWMI to GND                             | -0.3V to 6V    |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                |

| SOP-14                                                                      | 1.000W         |

| Package Thermal Resistance (Note 2)                                         |                |

| SOP-14 , θ <sub>JA</sub>                                                    | 100°C/W        |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C          |

| • Junction Temperature                                                      | 150°C          |

| Storage Temperature Range                                                   | -65°C to 150°C |

| ESD Susceptibility (Note 3)                                                 |                |

| HBM                                                                         | 2kV            |

| MM                                                                          | 200V           |

| Recommended Operating Conditions (Note 4)                                   |                |

| Supply Input Voltage, VIN                                                   | 4.5V to 29V    |

• Junction Temperature Range ------ -40°C to 125°C

• Ambient Temperature Range ------ -40°C to 85°C

### **Electrical Characteristics**

$(V_{IN} = 21V, V_{OUT} = 50V, T_A = 25^{\circ}C, unless otherwise specified)$

| Parameter                           |                  | Symbol             | Test Conditions                                                |      | Тур | Max  | Unit |  |

|-------------------------------------|------------------|--------------------|----------------------------------------------------------------|------|-----|------|------|--|

| Input Power Supply                  |                  |                    |                                                                |      |     |      |      |  |

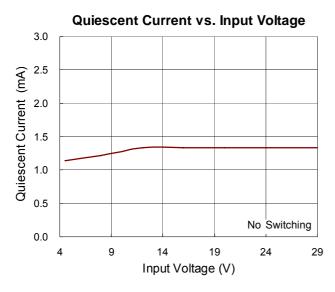

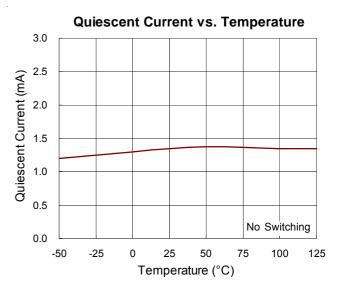

| Quiescent Current                   |                  | ΙQ                 | No Switching, $R_{SW} = 56k\Omega$                             |      | 1.3 | 2    | mA   |  |

| Shutdown Currer                     | nt               | I <sub>SHDN</sub>  | V <sub>EN</sub> = 0V                                           |      | 10  |      | μA   |  |

| Under Voltage Lo<br>Threshold       | ockout           | V <sub>UVLO</sub>  | V <sub>IN</sub> Rising                                         |      | 3.8 | -    | ٧    |  |

| Under Voltage Lockout<br>Hysteresis |                  | $\Delta V_{UVLO}$  |                                                                |      | 500 |      | mV   |  |

| 12V Regulator                       |                  |                    |                                                                |      |     |      |      |  |

|                                     |                  |                    | 13.5V < V <sub>IN</sub> < 16V, 1mA < I <sub>LOAD</sub> < 100mA |      |     |      |      |  |

| Regulator Output Voltage            |                  | $V_{DC}$           | 16V < V <sub>IN</sub> < 20V, 1mA < I <sub>LOAD</sub> < 50mA    | 11.4 | 12  | 12.6 | V    |  |

|                                     |                  |                    | 20V < V <sub>IN</sub> < 29V, 1mA < I <sub>LOAD</sub> < 20mA    |      |     |      |      |  |

| Dropout Voltage                     |                  | $V_{DROP}$         | $V_{IN} - V_{DC}$ , $V_{IN} = 12V$ , $I_{LOAD} = 100mA$        |      | 500 |      | mV   |  |

| Short-Circuit Current Limit         |                  | I <sub>SC</sub>    | V <sub>DC</sub> Short to GND                                   |      | 270 | -    | mΑ   |  |

| Control Input                       | Control Input    |                    |                                                                |      |     |      |      |  |

| EN Threshold                        | Logic-High       | V <sub>IH</sub>    | 2                                                              |      |     |      | V    |  |

| Voltage                             | Logic-Low        | V <sub>IL</sub>    |                                                                |      |     | 8.0  | ヿ ヾ  |  |

| EN Sink Current                     |                  | I <sub>IH</sub>    | V <sub>EN</sub> = 5V                                           |      | 5   |      | μA   |  |

| Shutdown Delay                      | Sleeping<br>Mode | t <sub>SLEEP</sub> | $R_{SW}$ = 56kΩ, EN = L, 12V Regular Shutdown                  |      |     | -    | ms   |  |

| Ondidown Delay                      | Shutdown<br>Mode | t <sub>SHDN</sub>  | $R_{SW}$ = 56k $\Omega$ , EN = L, IC Shutdown                  | 110  |     |      | ms   |  |

Copyright ©2012 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS8525-01 March 2012 www.richtek.com

| Parameter                      |                               | Symbol                  | Test Conditions                        |       | Тур  | Max   | Unit |  |

|--------------------------------|-------------------------------|-------------------------|----------------------------------------|-------|------|-------|------|--|

| Boost Contro                   | oller                         |                         |                                        |       |      |       |      |  |

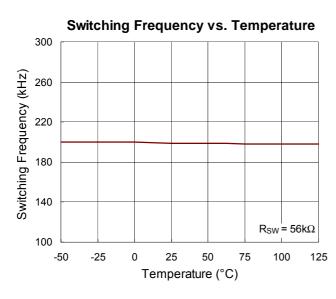

| Switching Frequency            |                               | f <sub>SW</sub>         | $R_{SW} = 56k\Omega$                   |       | 200  |       | kHz  |  |

| Minimum On-                    | imum On-Time t <sub>MON</sub> |                         | 250                                    |       | ns   |       |      |  |

| Maximum Dut                    | :y                            | D <sub>MAX</sub>        | Switching                              | 90    |      |       | %    |  |

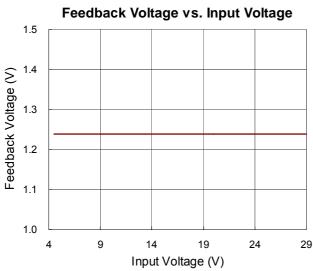

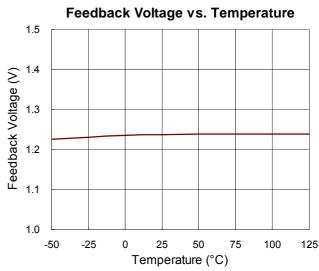

| Feedback Vol                   | tage                          | $V_{FB}$                |                                        |       | 1.25 | 1.275 | V    |  |

| Slope Compe                    | ensation                      |                         |                                        |       |      |       |      |  |

| Peak Magnitu<br>Compensation   |                               | I <sub>SLOPE</sub> , PK |                                        |       | 50   |       | μА   |  |

| Soft-Start                     |                               |                         |                                        |       |      |       |      |  |

| Soft-Start Cur                 | rent                          | I <sub>SS</sub>         |                                        | 3     | 4    | 5     | μΑ   |  |

| Gate Driver                    |                               | 1                       |                                        |       |      |       |      |  |

| DRV On-Resistance              |                               | R <sub>DS(ON)</sub> N   | I <sub>SINK</sub> = 100mA (N-MOSFET)   |       | 1    |       | Ω    |  |

| DITY OIFITESI                  | starice                       | R <sub>DS(ON)</sub> P   | I <sub>SOURCE</sub> = 100mA (P-MOSFET) | 1.5   |      |       | Ω    |  |

| Peak Sink Current              |                               | I <sub>PEAKsk</sub>     | C <sub>LOAD</sub> = 1nF                |       | 2.2  |       | Α    |  |

| Peak Source Current            |                               | I <sub>PEAKsr</sub>     | C <sub>LOAD</sub> = 1nF                |       | 2.55 |       | Α    |  |

| Rise Time                      |                               | t <sub>r</sub>          | C <sub>LOAD</sub> = 1nF                |       | 6    |       | ns   |  |

| Fall Time                      |                               | t <sub>f</sub>          | C <sub>LOAD</sub> = 1nF                |       | 5    |       | ns   |  |

| PWM Dimmir                     | ng Control                    |                         |                                        |       |      |       |      |  |

| PWMI<br>Threshold<br>Voltage   | Logic-High                    | V <sub>PWMI_H</sub>     |                                        | 2     | 1    |       | V    |  |

|                                | Logic-Low                     | V <sub>PWMI_L</sub>     |                                        |       |      | 0.8   | V    |  |

| Protection Fu                  | unction                       |                         |                                        |       |      |       |      |  |

| OCP Threshold                  |                               | V <sub>OCP</sub>        | Including Slope Compensation Magnitude |       | 0.4  |       | V    |  |

| V <sub>OUT</sub> OVP Threshold |                               | V <sub>OVP</sub>        |                                        | 2.375 | 2.5  | 2.625 | V    |  |

| V <sub>OUT</sub> UVP Threshold |                               | V <sub>UVP</sub>        |                                        |       | 0.1  |       | V    |  |

| Thermal Shut<br>Temperature    |                               | T <sub>SD</sub>         |                                        |       | 150  |       | °C   |  |

| Thermal Shutdown<br>Hysteresis |                               | ΔT <sub>SD</sub>        |                                        |       | 50   |       | °C   |  |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25$ °C on a low effective thermal conductivity single-layer test board per JEDEC 51-3.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions..

DS8525-01 March 2012

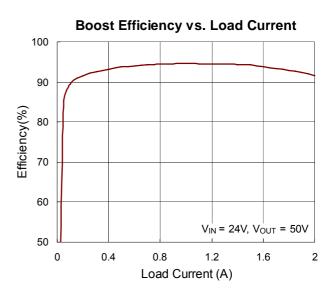

## **Typical Operating Characteristics**

Copyright ©2012 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS8525-01 March 2012 www.richtek.com

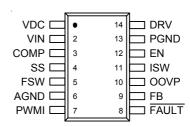

## **Applications Information**

The RT8525 is a wide input operating voltage range step up controller. High voltage output and large output current are feasible by using an external N-MOSFET. The protection functions include output over voltage, output under voltage, over temperature and current limiting protection.

#### **Boost Output Voltage Setting**

The regulated output voltage is set by an external resistor divider according to the following equation:

$$V_{OUT} = V_{FB} \times \left(1 + \frac{R_{FB1}}{R_{FB2}}\right)$$

, where  $V_{FB} = 1.25V$  (typ.)

The recommended value of  $R_{FB2}$  should be at least  $1k\Omega$  for saving sacrificing. Moreover, placing the resistor divider as close as possible to the chip can reduce noise sensitivity.

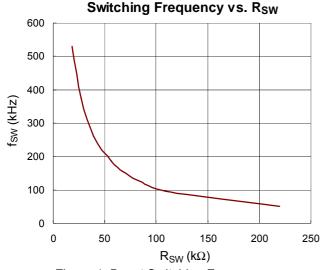

#### **Boost Switching Frequency**

The RT8525 boost driver switching frequency is able to be adjusted by a resistor  $R_{SW}$  ranging from  $18k\Omega$  to  $220k\Omega.$  The following figure illustrates the corresponding switching frequency within the resistor range.

Figure 1. Boost Switching Frequency

#### **Boost Loop Compensation**

The voltage feedback loop can be compensated by an external compensation network consisted of  $R_{\rm C}$ ,  $C_{\rm C1}$  and  $C_{\rm C2}$ . Choose  $R_{\rm C}$  to set high frequency gain for fast transient response. Select  $C_{\rm C1}$  and  $C_{\rm C2}$  to set the zero and pole to maintain loop stability. For typical application,

$V_{IN}$  = 24V,  $V_{OUT}$  = 50V,  $C_{OUT}$  = 100 $\mu$ F x 2, L1 = 33 $\mu$ H, while the recommended value for compensation is as follows :  $R_C$  = 33k $\Omega$ ,  $C_{C1}$  = 27nF.

#### Soft-Start

The soft-start of the RT8525 can be achieved by connecting a capacitor from the SS pin to GND. The built-in soft-start circuit reduces the start-up current spike and output voltage overshoot. The external capacitor charged by an internal  $4\mu A$  constant charging current determines the soft-start time. The SS pin limits the rising rate of the COMP pin voltage and thereby limits the peak switch current. The soft-start interval is set by the soft-start capacitor according to the following equation :

$$t_{SS} \cong C_{SS} \times 5 \times 10^5$$

A typical value for the soft-start capacitor is  $0.33\mu F$ . The soft-start capacitor is discharged when EN voltage falls below its threshold after shutdown delay or UVLO occurs.

#### **Slope Compensation and Current Limiting**

A slope compensation is applied to avoid sub-harmonic oscillation in current-mode control. The slope compensation voltage is generated by the internal ramp current flow through a slope compensation resistor  $R_{\text{SLP}}.$  The inductor current is sensed by the sensing resistor  $R_{\text{S}}.$  Both of them are added and presented on the ISW pin. The internal ramp current is rising linearly form zero at the beginning of each switching cycle to  $50\mu\text{A}$  in maximum on-time of each cycle. The slope compensation resistor  $R_{\text{SLP}}$  can be calculated by the following equation :

$$R_{SLP} > \frac{(V_{OUT} - V_{IN}) \times R_S}{2 \times L \times 50 \mu \times f_{SW}}$$

where  $R_{S}$  is current sensing resistor, L is inductor value, and  $f_{SW}$  is boost switching frequency.

The current flow through inductor during charging period is detected by a sensing resistor  $R_S$ . Besides, the slope compensation voltage also attributes magnitude to ISW. As the voltage at the ISW pin is over 0.4V, the DRV will be pulled low and turn off the external N-MOSFET. So that the inductor will be forced to leave charging stage and enter discharging stage to prevent over current. The current limiting can be calculated by the following equation:

Copyright ©2012 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

$$R_S < \frac{0.4 - D_{MAX} \times R_{SLP} \times 50 \mu}{I_{L.PK}}$$

where  $I_{L, PK}$  is peak inductor current, and  $D_{MAX}$  is maximum duty.

#### **Output Over Voltage Protection**

The output voltage can be clamped at the voltage level determined by the following equation:

$$V_{OUT (OOVP)} = V_{OOVP} \times \left(1 + \frac{R_{OVP1}}{R_{OVP2}}\right),$$

where  $V_{OOVP} = 2.5V$  (typ.)

where  $R_{\text{OVP1}}$  and  $R_{\text{OVP2}}$  are the voltage divider connected to the OOVP pin.

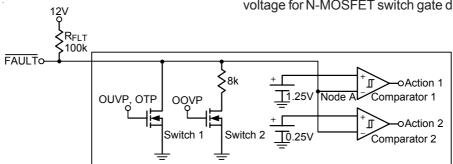

#### **Fault Protection**

The  $\overline{FAULT}$  pin will be pulled low once a protection is triggered, and a suitable pulled-high R<sub>FLT</sub> is required. The suggested R<sub>FLT</sub> is  $100k\Omega$  if the pulled-high voltage was 12V. The following figure illustrates the fault protection function block. If one of the OUVP and OTP occurs, the switch 1 will be turned on, and the voltage at node A will

be under 0.25V. Then the protection function will perform action 2 to turn off the driver. When protection function is released, the RT8525 will re-start.

On the other hand, if the triggered protection is OOVP, the voltage at node A will be decided by voltage divider composed of  $R_{\text{FLT}}$  and the internal  $8k\Omega$  resistor. This voltage must be designed between 0.25V and 1.25V by choosing  $R_{\text{FLT}}$  appropriately. Once the OOVP turns on the Switch 2, the divided  $\overline{\text{FAULT}}$  voltage will activate action 1 to turn off the driver without resetting soft-start. Therefore, when protection function OOVP is released, the RT8525 will be in normal operation.

#### **Power MOSFET Selection**

For the applications operating at high output voltage, switching losses dominate the overall power loss. Therefore, the power N-MOSFET switch is typically chosen for drain voltage, VDS, rating and low gate charge. Consideration of switch on-resistance R<sub>DS(ON)</sub> is usually secondary. The VDC regulator in the RT8525 has a fixed output current limit to protect the IC and provide 12V DRV voltage for N-MOSFET switch gate driver.

Figure 2. Fault Protection Function Block

#### **Inductor Selection**

The boundary value of the inductance L between Discontinuous Conduction Mode (DCM) and Continuous Conduction Mode (CCM) can be approximated by the following equation:

$$L = \frac{D \times (1 - D)^2 \times V_{OUT}}{2 \times f_{SW} \times I_{OUT}}$$

where

V<sub>OUT</sub> is the maximum output voltage,

V<sub>IN</sub> is the minimum input voltage,

fsw is the operating frequency,

$I_{\text{OUT}}$  is the sum of current from all LED strings,

and D is the duty cycle calculated by the following equation:

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}}$$

The boost converter operates in DCM over the entire input voltage range if the inductor value is less than the boundary value L. With an inductance greater than L, the converter operates in CCM at the minimum input voltage and may transit to DCM at higher voltages. The inductor must be

Copyright ©2012 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS8525-01 March 2012 www.richtek.com

selected with a saturated current rating greater than the peak current provided by the following equation :

$$I_{LPK} = \frac{V_{OUT} \times I_{OUT}}{\eta \times V_{IN}} + \frac{VIN \times D \times T}{2 \times L}$$

where  $\eta$  is the efficiency of the power converter.

#### **Diode Selection**

Schottky diodes are recommended for most applications because of their fast recovery time and low forward voltage. The power dissipation, reverse voltage rating and pulsating peak current are the important parameters for Schottky diode selection. Make sure that the diode's peak current rating exceeds  $I_{LPK}$ , and reverse voltage rating exceeds the maximum output voltage.

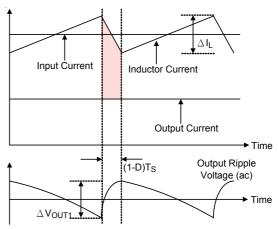

#### **Capacitor Selection**

Output ripple voltage is an important index for estimating the performance. This portion consists of two parts, one is the product of input current and ESR of output capacitor, another part is formed by charging and discharging process of output capacitor. Refer to figure 3, evaluate  $\Delta V_{\text{OUT1}}$  by ideal energy equalization. According to the definition of Q, the Q value can be calculated as following equation :

$$Q = \frac{1}{2} \times \left[ \left( I_{IN} + \frac{1}{2} \Delta I_{L} - I_{OUT} \right) + \left( I_{IN} - \frac{1}{2} \Delta I_{L} - I_{OUT} \right) \right] \times \frac{V_{IN}}{V_{OUT}}$$

$$\times \frac{1}{f_{CW}} = C_{OUT} \times \Delta V_{OUT1}$$

where  $f_{SW}$  is the switching frequency, and  $\Delta I_L$  is the inductor ripple current. Move  $C_{OUT}$  to the left side to estimate the value of  $\Delta V_{OUT1}$  as the following equation :

$$\Delta V_{OUT1} = \frac{D \times I_{OUT}}{\eta \times C_{OUT} \times f_{SW}}$$

Finally, by taking ESR into consideration, the overall output ripple voltage can be determined as the following equation:

$$\Delta V_{OUT} = I_{IN} \times ESR + \frac{D \times I_{OUT}}{\eta \times C_{OUT} \times f_{SW}}$$

Figure 3. The Output Ripple Voltage without the Contribution of ESR

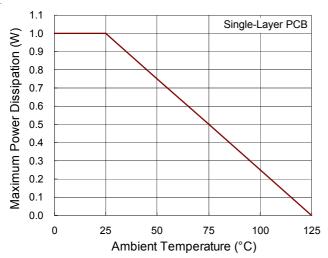

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For SOP-14 packages, the thermal resistance,  $\theta_{JA}$ , is 100°C/W on a standard JEDEC 51-3 single-layer thermal test board. The maximum power dissipation at  $T_A$  = 25°C can be calculated by the following formula :

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (100^{\circ}C/W) = 1.000W$$

for SOP-14 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 4 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Copyright ©2012 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

DS8525-01 March 2012

Figure 4. Derating Curve of Maximum Power Dissipation

#### **Layout Considerations**

PCB layout is very important for designing switching power converter circuits. The following layout guides should be strictly followed for best performance of the RT8525.

- ► The power components L<sub>1</sub>, D<sub>1</sub>, C<sub>IN</sub>, C<sub>OUT</sub> M<sub>1</sub> and R<sub>S</sub> must be placed as close as possible to reduce current loop. The PCB trace between power components must be as short and wide as possible.

- ▶ Place components R<sub>FB1</sub>, R<sub>FB2</sub>, R<sub>OVP1</sub> and R<sub>OVP2</sub> close to IC as possible. The trace should be kept away from the power loops and shielded with a ground trace to prevent any noise coupling.

- The compensation circuit should be kept away from the power loops and should be shielded with a ground trace to prevent any noise coupling. Place the compensation components to the COMP pin as close as possible, no matter the compensation is R<sub>C</sub>, C<sub>C1</sub> or C<sub>C2</sub>.

Place the power components as close as possible. The traces should be wide and short especially for the high-current loop. The compensation circuit should be kept away from Vout 00 0000 the power loops and should be shielded with a ground trace to prevent any noise C<sub>OUT</sub> coupling VDC [ 14 2 ☐ PGND 88 VIN I 13 **PGND** AGND is suggested 3 12 ] EN 0000 that connect to PGND 11 from the sense resistor 5 10 OOVP R<sub>S</sub> for better stability. 6 9 1 FB **AGND**  $\mathsf{R}_{\mathsf{FB2}}$ 7 8 FAULT R<sub>FB1</sub> 00 Vout The feedback voltage divider resistors must near the feedback pin. The divider center trace must be shorter and avoid the trace near any switching nodes.

Figure 5. PCB Layout Guide

Copyright ©2012 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

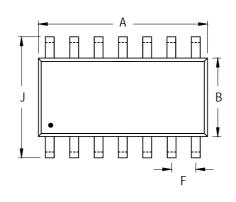

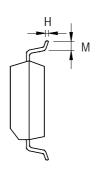

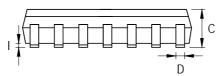

### **Outline Dimension**

| Complete | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|----------|--------------|---------------|----------------------|-------|--|

| Symbol   | Min          | Max           | Min                  | Max   |  |

| А        | 8.534        | 8.738         | 0.336                | 0.344 |  |

| В        | 3.810        | 3.988         | 0.150                | 0.157 |  |

| С        | 1.346        | 1.753         | 0.053                | 0.069 |  |

| D        | 0.330        | 0.508         | 0.013                | 0.020 |  |

| F        | 1.194        | 1.346         | 0.047                | 0.053 |  |

| Н        | 0.178        | 0.254         | 0.007                | 0.010 |  |

| 1        | 0.102        | 0.254         | 0.004                | 0.010 |  |

| J        | 5.791        | 6.198         | 0.228                | 0.244 |  |

| М        | 0.406        | 1.270         | 0.016                | 0.050 |  |

14-Lead SOP Plastic Package

### **Richtek Technology Corporation**

5F, No. 20, Taiyuen Street, Chupei City

Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

DS8525-01 March 2012

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Richtek(台湾立锜)