# Easy to Use Power Bank Solution (EZPBS<sup>™</sup>) Integrated Chip with Switch Charger, ADC, and Load Switch

### **General Description**

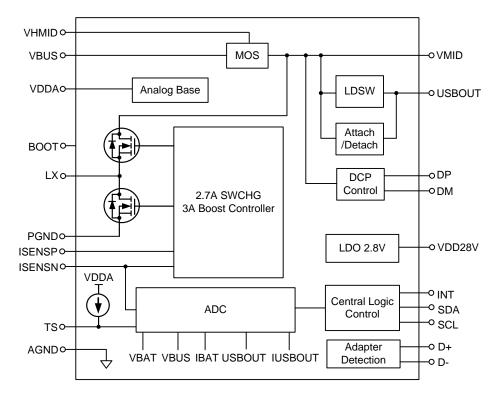

The RT9481 is a high integration and easy to use power solution for Li-ion power bank and other powered handheld applications. We call it EZPBS<sup>TM</sup> (Easy to Use Power Bank Solution). This single chip includes a Switching Charger with Boost function, Analog to Digital Converter (ADC), USBOUT Load Switch, Adapter Detection with BC1.2, DCP controller and LDO.

### Applications

Power Bank

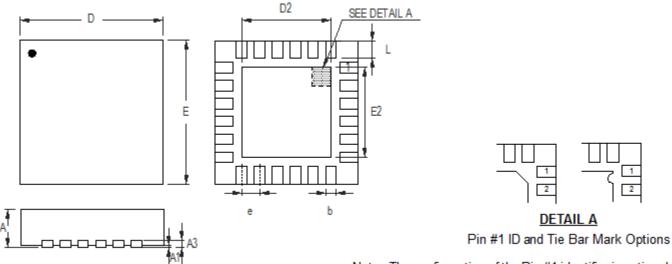

### **Ordering Information**

### RT9481 🖵 📮

Package Type QW : WQFN-24L 4x4 (W-Type) (Exposed Pad-Option 2)

Lead Plating System G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ► Suitable for use in SnPb or Pb-free soldering processes.

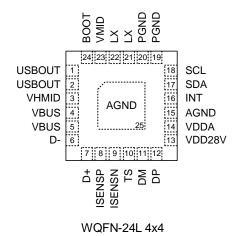

### **Pin Configurations**

### (TOP VIEW)

### Features

### System

- High Accuracy Voltage/Current Regulation

- ▶ ±1% Charge Voltage Regulation

- ▶ ±0.1A Charge Current Regulation

- ▶ ±3% Boost USBOUT Voltage Regulation

- Thermal Shutdown Protection

- Reverse Leakage Protection to Prevent Battery Drainage.

- Built-In USBOUT DCP Controller

- Built-In USBOUT Attach/Detach Detection

- Built-In USBOUT Light Load Detection

- Built-In Load Switch with Current Regulation Thermal Regulation and Output Short Current Protection

- Built-In Adapter Detection with BC1.2

- Built-In Accurate ADC to Measure VBAT, VBUS, TS, IBAT, USBOUT and IUSBOUT

- Built-In LDO

- Interrupt Output for Event Notification

- I<sup>2</sup>C Interface with 400kHz

#### Charge Mode

- Charge Voltage Regulation : 3.65V to 4.6V

- Charge Current Regulation : 0.7A to 2.7A

- Minimum Input Voltage Regulation (MIVR) : 4.2V to 4.8V

- Average Input Current Regulation (AICR) : 0.1A to 2A

- Charge Termination Current : 0.15A to 0.6A

- Pre-charge Threshold : 2.3V to 3.8V

- Pre-charge Current : 0.2A to 0.5A

- Thermal Regulation

- VMID Under Voltage Protection

- VBUS Over Voltage Protection

- Battery Over Voltage Protection

- Bad Adapter Detection

### Boost Mode

- Boost Output Current Up to 3A

- Boost Output Voltage : 3.65V to 5.2V

- Battery Under Voltage Protection : 2.5V to 3.2V

- VMID Over Voltage Protection

### **Marking Information**

|   | 3X=YM |

|---|-------|

|   | DNN   |

| _ |       |

3X= : Product Code YMDNN : Date Code

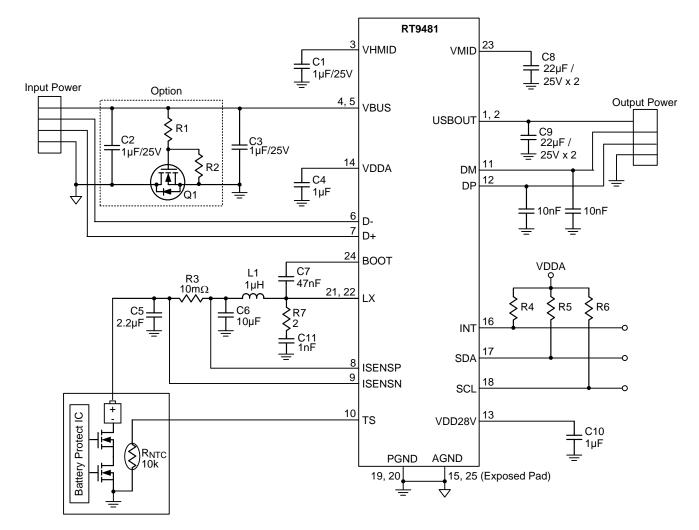

### **Typical Application Circuit**

### **Functional Pin Description**

| Pin No.                 | Pin Name | Pin Function                                                                                                             |

|-------------------------|----------|--------------------------------------------------------------------------------------------------------------------------|

| 1, 2                    | USBOUT   | USB Power Output.                                                                                                        |

| 3                       | VHMID    | Internal Use Only.                                                                                                       |

| 4, 5                    | VBUS     | VBUS Power Supply.                                                                                                       |

| 6                       | D-       | D- Input for Adapter Detection.                                                                                          |

| 7                       | D+       | D+ Input for Adapter Detection.                                                                                          |

| 8                       | ISENSP   | Charging Current Sensing Positive Node.                                                                                  |

| 9                       | ISENSN   | Charging Current Sensing Negative Node and Connect to Battery Plus Terminal.                                             |

| 10                      | TS       | Battery Temperature Detection Pin.                                                                                       |

| 11                      | DM       | DCP Controller DM Output.                                                                                                |

| 12                      | DP       | DCP Controller DP Output.                                                                                                |

| 13                      | VDD28V   | Internal Use LDO Output.                                                                                                 |

| 14                      | VDDA     | Internal Power for Analog Blocks, Put 1µF to GND.                                                                        |

| 15,<br>25 (Exposed Pad) | AGND     | Analog Ground Node. The exposed pad must be soldered to a large PCB and connected to AGND for maximum power dissipation. |

| 16                      | INT      | Interrupter Signal. Connect an external pull-up resistor.                                                                |

| 17                      | SDA      | Data Input and Output for I <sup>2</sup> C Serial Port. Connect an external pull-up resistor.                            |

| 18                      | SCL      | Clock Input for I <sup>2</sup> C Serial Port. Connect an external pull-up resistor.                                      |

| 19, 20                  | PGND     | Power Ground for Switching Charger.                                                                                      |

| 21, 22                  | LX       | Internal Switch Node to Output Inductor Connection.                                                                      |

| 23                      | VMID     | Connection Point Between Reverse Blocking and High-Side.                                                                 |

| 24                      | BOOT     | Bootstrap Power Node for Switching Charger.                                                                              |

### **Functional Blocks Diagram**

### Operation

The RT9481 is a high integrated IC for Li-Ion battery power bank. It includes a Switch charger 2.7A, a synchronous Boost 5V.

### **Charge Current**

Base on thermal regulation function, the charging current can support up to 2.7A.

### **VBUS Over Voltage Protection**

If the input voltage (VBUS) is higher than the threshold voltage VovP, the internal OVP signal will go high and the charger will stop charging until VIN is below Vovp - hysteresis.

### **VMID Over Voltage Protection**

If the internal voltage (VMID) is higher than the threshold voltage VovP, the internal OVP signal will go high and the charger will stop charging until VMID is below VOVP - hysteresis.

### **VMID Under Voltage Protection**

If the internal voltage (VMID) is lower than the threshold voltage VUVP, the internal VMID UVP signal will go high and the system will disable LDSW

function in order to protect system from short-toground current damages.

### USBOUT SCP

The USBOUT short circuit protection (SCP) function will prevent system from burning out by monitoring the voltage drop between LDSW. If the USBOUT is short to ground, the inrush current will make the VDS voltage too large to damage chip. The SCP function also reports this condition to protect chip in time.

### **Boost OCP**

The converter senses the current signal when the high-side P-MOSFET turns on. As a result, The OCP is cycle by-cycle current limitation. If the OCP occurs, the converter holds off the next on pulse until inductor current drops below the OCP limit.

### OTP

The converter has an over-temperature protection.

When the junction temperature is higher than the thermal shutdown rising threshold, the system will be latched and the output voltage will no longer be

Copyright © 2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation. www.richtek.com DS9481-04 August 2016

regulated until the junction temperature drops under the falling threshold.

#### CC/CV/TR Multi Loop Controller

There are constant current loop, constant voltage loop and thermal regulation loop to control the charging current.

#### **Base Circuits**

Base circuits provide the internal power, VDDA and reference voltage and bias current.

## Buck Regulator for Charging and Boost Regulator as BOOST

The multi-loop controller controls the operation of charging process and current supply to the system. It also controls the circuits as a Boost converter for BOOST applications.

#### **USB Charger Detection**

The RT9481 detects USB Charger (Standard Charger Port, Charging Downstream Port and Dedicated Charger Port) via D+ and D- pins.

#### **USBOUT Attach/Detach Detection**

RT9481 includes an auto attach detection for the power bank product. The attach detection has a current threshold which represent an attach condition. When the attach detection is enable, the USBOUT will generate a 1.6V to monitor the load current. Once load current is greater than  $5\mu$ A, the attach flag will be reported until the load current is removed.

### I<sup>2</sup>C Controller

The key parameters of charging and BOOST are programmable through  $I^2C$  commands.

5

### Absolute Maximum Ratings (Note 1)

| VBUS, VHMID Supply Input Voltage                                                                 | –0.3V to 18V   |

|--------------------------------------------------------------------------------------------------|----------------|

| • VMID                                                                                           | –0.3V to 6.7V  |

| • LX, BOOT                                                                                       | –0.3V to 6V    |

| • VMID – VBUS, BOOT– LX                                                                          | –0.3V to 6V    |

| Others                                                                                           | –0.3V to 6V    |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> <li>WQFN-24L 4x4</li></ul> | 3.57W          |

| Package Thermal Resistance (Note 2)                                                              |                |

| WQFN-24L 4x4, $\theta_{JA}$                                                                      | 28°C/W         |

| WQFN-24L 4x4, $\theta_{JC}$                                                                      | 7.1°C/W        |

| Lead Temperature (Soldering, 10 sec.)                                                            | 260°C          |

| Junction Temperature                                                                             | 150°C          |

| Storage Temperature Range                                                                        | –65°C to 150°C |

| ESD Susceptibility (Note 3)                                                                      |                |

| HBM (Human Body Model)                                                                           | 2kV            |

| MM (Machine Model)                                                                               | 200V           |

### Recommended Operating Conditions (Note 4)

| • 5 | Supply Input Voltage       | 4.3V to 5.65V  |

|-----|----------------------------|----------------|

| • . | Junction Temperature Range | –40°C to 125°C |

| • / | Ambient Temperature Range  | –40°C to 85°C  |

### **Electrical Characteristics**

| Parameter                     | Symbol                       | Test Conditions                                                                 | Min | Тур  | Max  | Unit |  |  |

|-------------------------------|------------------------------|---------------------------------------------------------------------------------|-----|------|------|------|--|--|

| Input Power Source            |                              |                                                                                 |     |      |      |      |  |  |

| VBUS Operation Range          |                              |                                                                                 | 4   |      | 5.65 | V    |  |  |

| VBUS Supply Current           |                              | PWM switching,<br>I <sub>CHG</sub> = I <sub>BAT</sub> = 0mA                     |     | 10   |      | mA   |  |  |

|                               | lQ                           | High Impendence Mode                                                            |     |      | 200  | μA   |  |  |

| Leakage Current from Battery  | IBAT_LEAK                    | $V_{BAT} = 4.2V, V_{BUS} = 0V,$<br>Charger off.<br>1/80 ADC execution time duty |     | 40   | 60   | μΑ   |  |  |

| Protection                    |                              |                                                                                 |     |      |      |      |  |  |

| VBUS OVP Threshold<br>Voltage | VBUS_OVP                     | VBUS Rising                                                                     | 5.7 | 6    | 6.3  | V    |  |  |

| VBUS OVP Hysteresis           | V <sub>BUS_OVP_</sub><br>Hys | VBUS Falling                                                                    |     | 200  |      | mV   |  |  |

| VBUS UVLO                     | VBUS_UVLO                    | VBUS Rising                                                                     | 3   | 3.25 | 3.5  | V    |  |  |

|                                                  | 1                             | 1                                                                          |     |         | [    |      |

|--------------------------------------------------|-------------------------------|----------------------------------------------------------------------------|-----|---------|------|------|

| Parameter                                        | Symbol                        | Test Conditions                                                            | Min | Тур     | Max  | Unit |

| VBUS UVLO Hysteresis                             | V <sub>BUS_UVLO_</sub><br>HYS | VBUS Falling                                                               |     | 150     |      | mV   |

| ISENSN OVP                                       | VBAT_OVP                      | VISENSN Rising                                                             | 103 | 107     | 114  | %    |

| ISENSN OVP Hysteresis                            | V <sub>BAT_OVP_</sub><br>HYS  | VISENSN Falling                                                            |     | 5       |      | %    |

| Over Temperature Protection                      | T <sub>OTP</sub>              | (Note 5)                                                                   |     | 160     |      | °C   |

| OTP Hysteresis                                   | T <sub>OTP_HYS</sub>          |                                                                            |     | 20      |      | °C   |

| Thermal Regulation<br>Threshold                  | T <sub>REG</sub>              | Optional 100/120/135°C by I <sup>2</sup> C (Default value is 120°C)        |     | 120     |      | °C   |

| Input Power Source Detection                     | on                            |                                                                            |     |         |      |      |

| Poor Source Detect<br>Threshold                  | VBUS_pr                       | Bad Voltage Source Detection                                               | 3.6 | 3.8     | 4    | V    |

| Poor Source Detect Deglitch                      | t∨BUS_pr_dg                   |                                                                            |     | 30      |      | ms   |

| Poor Source Detect<br>Hysteresis                 | V <sub>BUS_pr_hys</sub>       | VBUS Rising                                                                | 100 |         | 200  | mV   |

| Current Sink to GND                              | I <sub>VBUS_pr</sub>          | During Poor Source Detection                                               |     | 50      |      | mA   |

| Detection Interval Time                          | t∨BUS_pr_int                  |                                                                            | -   | 2       | -    | s    |

| Sleep Mode Comparator                            |                               |                                                                            |     |         |      |      |

| Sleep-Mode Entry Threshold<br>VBUS – ISENSN      | V <sub>SLP</sub>              | 3V < VISENSN < VBATREG,<br>VBUS Falling                                    |     | 40      | 100  | mV   |

| Sleep-Mode Exit Hysteresis<br>VBUS Symbol ISENSN | VSLPEXIT                      | 3V < VISENSN < VBATREG,<br>VBUS Rising                                     | 40  | 120     | 200  | mV   |

| Sleep-Mode Deglitch Time                         | t <sub>SLP</sub>              | VBUS Rising Above V <sub>SLP</sub> +<br>V <sub>SLPEXIT</sub>               |     | 30      |      | ms   |

| Minimum Input Voltage Regu                       | lation (MIVR)                 |                                                                            |     |         |      |      |

| Minimum Input Voltage<br>Regulation              | Vmivr                         | Optional 4.2V to 4.8V by I <sup>2</sup> C per 0.1V (Default value is 4.7V) | 4.2 |         | 4.8  | V    |

| V <sub>MIVR</sub> Accuracy                       |                               |                                                                            | -5  |         | 5    | %    |

|                                                  | IAICR_100mA                   | I <sub>AICR</sub> = 100mA                                                  | 80  | 90      | 100  |      |

| Average Input Current                            | IAICR_500mA                   | IAICR = 500mA                                                              | 400 | 450     | 500  | m۸   |

| Regulation (AICR) Accuracy                       | IAICR_700mA                   | I <sub>AICR</sub> = 700mA                                                  | 560 | 630     | 700  | mA   |

|                                                  | IAICR_1000mA                  | I <sub>AICR</sub> = 1000mA                                                 | 800 | 900     | 1000 |      |

| AICR Range                                       | IAICR                         | Optional 100mA to 2000mA by I <sup>2</sup> C (Default value is 0.5A)       | 100 |         | 2000 | mA   |

| VDDA Regulator                                   |                               |                                                                            |     |         |      |      |

| VDDA Voltage                                     | VDDA                          | $V_{VBUS} > 4.5V$                                                          |     | 4.5     |      | - V  |

|                                                  | VUUA                          | VVBUS < VISENSN                                                            |     | VISENSN |      |      |

| VDDA UVLO                                        | V <sub>DDA_UV</sub>           | VDDA Risling                                                               | 2.4 | 2.5     | 2.6  | V    |

| VDDA UVLO Hysteresis                             | V <sub>DDA_UV_hys</sub>       | VDDA Falling                                                               |     | 150     |      | mV   |

Copyright © 2016 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation. DS9481-04 August 2016 www.richtek.com

RICHTEK

| Parameter                          | Symbol                           | Test Conditions                                                                                                            | Min  | Тур | Max | Unit |

|------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| Battery Voltage Regulation         |                                  |                                                                                                                            |      |     |     |      |

| Battery Voltage Regulation         | VBATREG                          | Optional 3.65V to 4.6V by I <sup>2</sup> C<br>per 25mV (Default value is<br>4.2V)                                          | 3.65 |     | 4.6 | V    |

| VBATREG Accuracy                   |                                  |                                                                                                                            | -1   |     | 1   | %    |

| Re-Charge Threshold                | $\Delta V_{REG}$                 | V <sub>ISENSN</sub> Falling,<br>∆VREG = (VBATREG – VREC)                                                                   | 50   | 125 | 200 | mV   |

| Re-Charge Deglitch Time            | t <sub>REC</sub>                 |                                                                                                                            |      | 128 |     | ms   |

| <b>Charging Current Regulation</b> | า                                |                                                                                                                            |      |     |     |      |

| Output Charging Current            | Існд                             | $R_{SENSE} = 10m\Omega$ ,<br>Optional 0.7A to 2.7A by I <sup>2</sup> C<br>per 0.25A (Default value is<br>0.7A)             | 0.7  |     | 2.7 | A    |

| ICHG Accuracy                      | ICHG_ACC                         | $R_{SENSE} = 10m\Omega$                                                                                                    | -100 |     | 100 | mA   |

| Pre-Charge Threshold               | Vprec                            | Rising,<br>Optional 2.3V to 3.8V by I <sup>2</sup> C<br>per 0.1V (Default value is 3V)                                     | 2.3  |     | 3.8 | V    |

| VPREC Accuracy                     |                                  |                                                                                                                            | -5   |     | 5   | %    |

| Pre-Charge Current                 | IPREC                            | Optional 200mA to 500mA by<br>I <sup>2</sup> C per 100mA (Default value is<br>300mA)                                       | 200  |     | 500 | mA   |

| IPREC Accuracy                     |                                  |                                                                                                                            | -20  |     | 20  | %    |

| Charge Termination Detection       | n                                |                                                                                                                            |      |     |     |      |

| End of Charge Current              | IEOC                             | R <sub>SENSE</sub> = 10mΩ,<br>Optional 150mA to 600mA by<br>$I^{2}C$ (Default value is 200mA)                              | 150  |     | 600 | mA   |

| IEOC Accuracy                      |                                  | $R_{SENSE} = 10m\Omega$                                                                                                    | -100 |     | 100 | mA   |

| Deglitch Time for EOC              | tEOC                             | ICHG < IEOC, VISENSN ><br>(VBATREG – $\Delta$ VREG)<br>Optional 4ms to 32ms by I <sup>2</sup> C<br>(Default value is 32ms) | 4    |     | 32  | ms   |

| Charger Timer Protection           | 1                                |                                                                                                                            |      |     | I   |      |

| Fast-Charge Time-Out               |                                  | Optional 6Hrs to 20Hrs by I <sup>2</sup> C<br>per 2Hrs (Default value is<br>20Hrs)                                         | 6    |     | 20  | Hrs  |

| Pre-Charge Time-Out                |                                  | Optional 30Mins to 60Mins by I <sup>2</sup> C per 15Mins (Default value is 60Mins)                                         | 30   |     | 60  | Mins |

| PWM Switching Charger              |                                  | · ]                                                                                                                        |      |     |     |      |

| VBUS to LX Resistance              | R <sub>DS(ON)</sub> _<br>VBUS_LX | From VBUS to LX, as IAICR disable or $I_{AICR} = 2A$                                                                       |      | 97  |     | mΩ   |

| VBUS to USBOUT<br>Resistance       | R ds(on)_<br>vbus_usbout         | From VBUS to USBOUT                                                                                                        |      | 98  |     | mΩ   |

| Low-Side On-Resistance             | R <sub>DS(ON)</sub> _LS          | From LX to PGND                                                                                                            |      | 35  |     | mΩ   |

9

| Parameter                                          | Symbol               | Test Conditions                                                                                                                   | Min   | Тур  | Max | Unit |

|----------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|------|-----|------|

| Efficiency for Charge                              | EFF_CHG              | $V_{BUS} = 5V$ , $V_{ISENSN} = 4V$ , and $I_{CHG} = 2A$                                                                           |       | 90   |     | %    |

| Oscillator Frequency                               | fosc                 |                                                                                                                                   |       | 0.75 |     | MHz  |

| Frequency Accuracy                                 |                      |                                                                                                                                   | -10   |      | 10  | %    |

| Maximum Duty Cycle                                 | D <sub>MAX</sub>     | At Minimum Voltage Input                                                                                                          |       | 95   |     | %    |

| Minimum Duty Cycle                                 | D(MIN)               |                                                                                                                                   | 0     |      |     | %    |

| Peak OCP as Charger Mode                           |                      |                                                                                                                                   |       | 4.5  |     | А    |

| Boost Mode Operation                               |                      |                                                                                                                                   |       |      |     |      |

| Output Voltage Level                               | VBOOST               | To VMID<br>Optional 3.625V to 5.2V by I <sup>2</sup> C<br>per 25mV (Default value is<br>5.1V)                                     | 3.625 |      | 5.2 | V    |

| Output Voltage Accuracy                            |                      |                                                                                                                                   | -3    |      | 3   | %    |

| Output Current On VMID                             | I <sub>BST</sub>     | V <sub>BAT</sub> > 3V                                                                                                             | 3     |      |     | А    |

| Efficiency for Boost                               | EFF_BST              | $V_{MID} = 5V, V_{ISENSN} = 4V$ , and Loading = 2A                                                                                |       | 92   |     | %    |

| Peak OCP as Boost Mode                             | IOCP_BST             |                                                                                                                                   |       | 6    |     | А    |

| VMID OVP as Reverse Boost                          | VOVP_BST             | VMID Rising                                                                                                                       | -     | 6    |     | V    |

| VMID OVP Hysteresis                                | Vovp_bst_<br>hys     | VMID Falling                                                                                                                      |       | 200  |     | mV   |

| Battery UVP for Boost                              | VBATMIN              | Falling, I <sup>2</sup> C Programmable Per<br>0.1V<br>Optional 2.5V to 3.2V by I <sup>2</sup> C<br>per 0.1V (Default value is 3V) | 2.5   |      | 3.2 | V    |

| NTC Function                                       |                      |                                                                                                                                   |       |      |     |      |

| Current Source for NTC $10k\Omega$                 | ITS_10k              |                                                                                                                                   | 33    | 35   | 37  | μA   |

| Load Switch for USBOUT                             |                      |                                                                                                                                   |       |      |     |      |

| Supply Voltage                                     | V <sub>SW</sub>      |                                                                                                                                   | 2.5   | 5    | 5.5 | V    |

| Load Switch On Resistance of MOSFET                | RDS(ON)_SW           | V <sub>MID</sub> = 5V, I <sub>O</sub> = 1000mA                                                                                    |       | 35   |     | mΩ   |

| Load Switch UVP Delta                              | Vsw_uvp_d            | VMID – VUSBOUT                                                                                                                    |       | 1.4  |     | V    |

| Light Load Detection Current                       | IDET_10mA            | Detection current                                                                                                                 |       | 10   |     | mA   |

| Thermal Regulation<br>Threshold of the Load Switch | T <sub>REG_LSW</sub> | Optional 100°C to 135°C by I <sup>2</sup> C<br>(Default value is 100°C)                                                           |       | 100  |     | °C   |

| Adapter Detection                                  |                      |                                                                                                                                   |       |      |     |      |

| D+ Voltage Source                                  | V <sub>D+_SRC</sub>  |                                                                                                                                   | 0.5   |      | 0.7 | V    |

| VDAT_REF Voltage                                   | Vdat_ref             |                                                                                                                                   | 0.25  |      | 0.4 | V    |

| VLGC Voltage                                       | Vlgc                 |                                                                                                                                   | 0.8   |      | 2   | V    |

| D- Sink Current                                    | I <sub>DN_SINK</sub> |                                                                                                                                   | 50    |      | 150 | μA   |

| RICHTEK |

|---------|

|---------|

| Parame                                                                       | ter         | Symbol                 | Test Conditions                                                    | Min  | Тур | Max  | Unit |

|------------------------------------------------------------------------------|-------------|------------------------|--------------------------------------------------------------------|------|-----|------|------|

| USBOUT Attach/                                                               | Detach Dete | ction                  |                                                                    |      |     |      |      |

| USBOUT Attach                                                                | Voltage     |                        | I <sub>USBOUT</sub> = 1.5μA                                        | 1.4  | 1.6 | 1.8  | V    |

| USBOUT Attach/Detach<br>Threshold                                            |             |                        | C <sub>USBOUT</sub> = 40μF,<br>Note 6                              | 1    | 5   | 10   | μA   |

| Detect Time 1                                                                |             |                        | $V_{BAT} = 3V, C_{OUT} = 30\mu F,$<br>0X24[4:2] = 010              |      | 375 |      | ms   |

| Detect Time 2                                                                |             |                        | V <sub>BAT</sub> = 3V, C <sub>OUT</sub> = 50µF,<br>0X24[4:2] = 100 |      | 600 |      | ms   |

| LDO 2.8V                                                                     |             | ·                      |                                                                    |      |     |      |      |

| Output Voltage                                                               |             | Vout_2.8V              | $C_{OUT} = 1 \mu F$                                                | 2.66 | 2.8 | 2.94 | V    |

| Output Current                                                               |             | IOUT_2.8V              | VDDA > 3V                                                          | 10   |     |      | mA   |

| The Time for VOL                                                             | JT Ready    | trdy_2.8V              | $C_{OUT} = 1 \mu F$                                                | 1    |     |      | ms   |

| ADC Characteris                                                              | tics        |                        |                                                                    |      |     |      |      |

| Resolution                                                                   |             |                        |                                                                    |      | 12  |      | Bit  |

|                                                                              |             |                        | VBAT, TS                                                           | -10  |     | 10   | mV   |

| Measurement Error                                                            |             | Vgerr                  | VBUS, USBOUT                                                       | -50  |     | 50   | mV   |

|                                                                              |             |                        | Ι <sub>ΒΑΤ</sub> < 1Α                                              | -100 |     | 100  | mA   |

|                                                                              |             |                        | I <sub>BAT</sub> > 1A                                              | -10  |     | 20   | %    |

|                                                                              |             |                        | IUSBOUT < 1A                                                       | -100 |     | 100  | mA   |

|                                                                              |             |                        | I <sub>USBOUT</sub> > 1A                                           | -10  |     | 10   | %    |

| Conversion Time                                                              |             | T <sub>CONV</sub>      |                                                                    |      |     | 25   | ms   |

| Logic Inputs (SD                                                             | A SCL)      |                        |                                                                    |      |     |      |      |

| SDA, SCL Input                                                               | High-Level  |                        |                                                                    | 1.5  |     |      | Ň    |

| Threshold<br>Voltage                                                         | Low-Level   |                        |                                                                    |      |     | 0.4  | V    |

| Open Drain Low                                                               | /oltage     | VODL                   | ISINK = 1mA                                                        |      |     | 0.4  | V    |

| I <sup>2</sup> C Timing Chara                                                | acteristics | •                      |                                                                    |      |     |      |      |

| SCL Clock Rate                                                               |             | fscl                   | VDDA = 3.3V                                                        |      |     | 400  | kHz  |

| Hold Time (Repea<br>Condition. After th<br>the first clock puls<br>generated | is period,  | thd;sta                |                                                                    | 0.6  |     |      | ms   |

| Input Power                                                                  |             | ·                      |                                                                    |      |     |      |      |

| DCP Controller Power UVLO<br>Threshold Voltage from VMID                     |             | VUVLO_R_DCP<br>_CTRL   | Rising                                                             | 3.9  | 4.1 | 4.3  | V    |

| UVLO Hysteresis                                                              |             | Vuvlo_f_cp_<br>ctrl    | Falling                                                            | 100  | 200 | 300  | mV   |

| DCP Controller S<br>Current                                                  | upply       | IDCP_CTRL              | 4.5V < V <sub>UID</sub> < 5V                                       |      | 150 | 200  | μA   |

| BC1.2 DCP Mode                                                               | 9           |                        |                                                                    |      |     |      |      |

| DP and DM Short<br>Resistance                                                | ing         | R <sub>DPM_SHORT</sub> | V <sub>DP</sub> = 0.8V, I <sub>DM</sub> = 1mA                      |      | 157 | 200  | Ω    |

Copyright © 2016 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

DS9481-04 August 2016

10

11

| Parameter                                                                       | Symbol                       | Test Conditions       | Min  | Тур | Max  | Unit |  |

|---------------------------------------------------------------------------------|------------------------------|-----------------------|------|-----|------|------|--|

| Resistance Between DP/DM and GND                                                | R <sub>DCHG</sub> _<br>SHORT | DP = 0.8V             | 350  | 656 | 1150 | kΩ   |  |

| Voltage Threshold on DP1<br>under which the Device Goes<br>Back to Divider Mode | Vdpl_th_det                  | Falling               | 310  | 330 | 350  | mV   |  |

| Hysteresis                                                                      | Vdpl_th_det<br>_hys          | Rising                |      | 50  |      | mV   |  |

| DIVIDER Mode                                                                    |                              |                       |      |     |      |      |  |

| DP Output Voltage for<br>DIVIDER Mode                                           | V <sub>DP_2.7V</sub>         | V <sub>UID</sub> = 5V | 2.57 | 2.7 | 2.84 | V    |  |

| DM Output Voltage for<br>DIVIDER Mode                                           | V <sub>DM_2.7V</sub>         | V <sub>UID</sub> = 5V | 2.57 | 2.7 | 2.84 | V    |  |

| DP Output Impedance for<br>DIVIDER Mode                                         | R <sub>DP_PAD1</sub>         | $I_{DP} = -5\mu A$    | 24   | 30  | 36   | kΩ   |  |

| DM Output Impedance for<br>DIVIDER Mode                                         | Rdm_pad1                     | $I_{DM} = -5\mu A$    | 24   | 30  | 36   | kΩ   |  |

| DP and DM Shorting<br>Resistance                                                | R <sub>PM_short</sub>        |                       |      | 150 | 200  | Ω    |  |

| 1.2V / 1.2V Mode                                                                |                              |                       |      |     |      |      |  |

| DP Output Voltage for 1.2V<br>Mode                                              | V <sub>DP_1.2V</sub>         |                       | 1.12 | 1.2 | 1.28 | V    |  |

| DP Output Impedance for<br>1.2V Mode                                            | R <sub>DP_PAD</sub>          |                       | 80   | 102 | 130  | kΩ   |  |

**Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

Note 3. Devices are ESD sensitive. Handling precaution recommended.

Note 4. The device is not guaranteed to function outside its operating conditions.

Note 5. Guarantee by design.

**Note 6.** It will attach when only plug-in APPLE charging line.

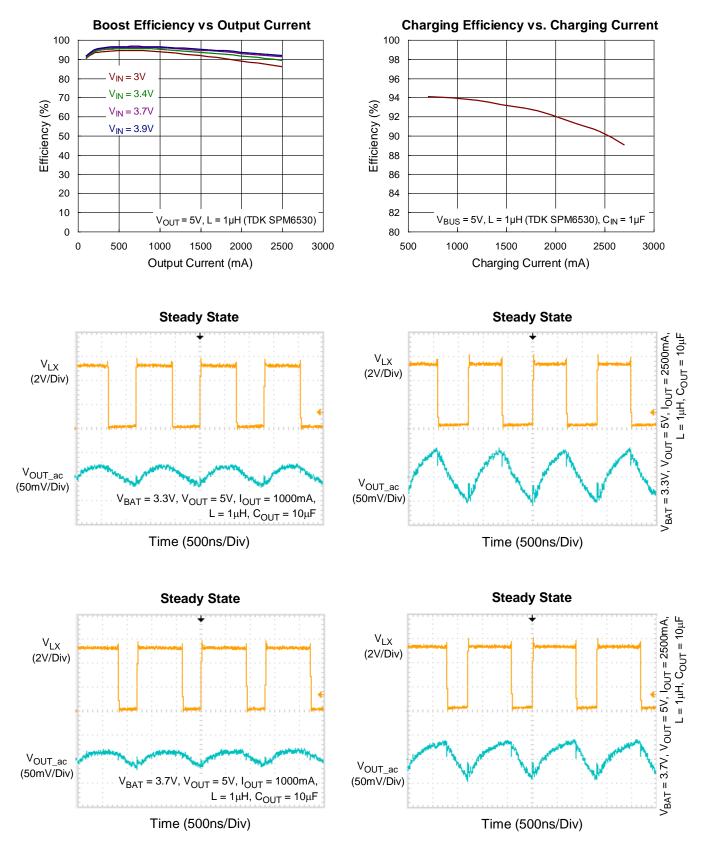

### **Typical Operating Characteristics**

Copyright © 2016 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

DS9481-04 August 2016

### **Application Information**

#### **Switching Charger**

The switching charger integrates a synchronous PWM controller with power MOSFETs to provide Minimum Input Voltage Regulation (MIVR), Average Input Current Regulation (AICR), high accuracy current and voltage regulation, and charge termination.

In charge mode, the switching charger supports a precision charging system for single cell. In boost mode, the switching charger works as the boost converter. And in high impedance mode, the switching charger stops charging or boosting and operates in a mode with low current from battery to reduce the power consumption when the portable device is in standby mode.

Notice that the switching charger does not integrate input power source (AC adapter or USB input) charging detection. Thus, the switching charger does not set the charge current automatically. The charge current needs to be set via I<sup>2</sup>C interface by the host. The switching charger application mechanism and I<sup>2</sup>C compatible interface are introduced in later sections.

#### **Charge Mode Operation**

#### Minimum Input Voltage Regulation (MIVR)

The switching charger features Minimum Input Voltage Regulation function to prevent input voltage drop due to insufficient current provided by the adaptor or USB input. If MIVR function is enabled, the input voltage decreases when the over current of the input power source occurs. VBUS is regulated at a predetermined voltage level which can be set as 4.2V to 4.8V per 0.1V by I<sup>2</sup>C interface. At this time, the current drawn by the switching charger equals to the maximum current value that the input power can provide at the predetermined voltage level, instead of the set value.

| MIVR[2:0] | V <sub>MIVR</sub> |  |

|-----------|-------------------|--|

| 000       | Disable           |  |

| 001       | 4.2V              |  |

| 010       | 4.3V              |  |

| 011       | 4.4V              |  |

| 100       | 4.5V              |  |

| 101       | 4.6V              |  |

| 110       | 4.7V (default)    |  |

| 111       | 4.8V              |  |

| Table 1. | MIVR | Register | Setting | Table |

|----------|------|----------|---------|-------|

|          |      |          |         |       |

#### **Charge Profile**

The switching charger provides a precision Li-ion or Lipolymer charging solution for single-cell applications. Input current limit, charge current, termination current, charge voltage and input voltage MIVR are all programmable via the I<sup>2</sup>C interface. In charge mode, the switching charger has five control loops to regulate input current, charge current, charge voltage, input voltage MIVR and device junction temperature. During the charging process, all five loops (if MIVR is enabled) are enabled and the dominant one will take over the control.

For normal charging process, the Li-ion or Li-polymer battery is charged in three charging modes depending on the battery voltage. At the beginning of the charging process, the switching charger is in pre-charge mode. When the battery voltage rises above pre-charge threshold voltage (VPREC), the switching charger enters fast-charge mode. Once the battery voltage is close to the regulation voltage (VBATREG), the switching charger enters constant voltage mode.

#### **Pre-Charge Mode**

For life-cycle consideration, the battery cannot be charged with large current under low battery condition. When the ISENSN pin voltage is below pre-charge threshold voltage (VPREC), the charger is in pre-charge mode with a weak charge current witch equals to the pre-charge current (IPREC). In pre-charge mode, the charger basically works as a Linear Charger. The precharge current also acts as the current limit when the ISENSN pin is shorted.

The Pre-Charge current levels are 200mA to 500mA programmed by I<sup>2</sup>C per 100mA.

Copyright © 2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9481-04 August 2016

| RICHTEK |  |

|---------|--|

|---------|--|

| Table 2. VPREC Register Setting Table |                      |  |

|---------------------------------------|----------------------|--|

| VPREC[2:0]                            | Pre-Charge Threshold |  |

| 0000                                  | 2.3V                 |  |

| 0001                                  | 2.4V                 |  |

| 0010                                  | 2.5V                 |  |

| 0011                                  | 2.6V                 |  |

| 0100                                  | 2.7V                 |  |

| 0101                                  | 2.8V                 |  |

| 0110                                  | 2.9V                 |  |

| 0111                                  | 3V (default)         |  |

| 1000                                  | 3.1V                 |  |

| 1001                                  | 3.2V                 |  |

| 1010                                  | 3.3V                 |  |

| 1011                                  | 3.4V                 |  |

| 1100                                  | 3.5V                 |  |

| 1101                                  | 3.6V                 |  |

| 1110                                  | 3.7V                 |  |

| 1111                                  | 3.8V                 |  |

#### Table 3. IPREC Register Setting Table

| IPREC[1:0] | Pre-Charge Current |  |

|------------|--------------------|--|

| 00         | 200mA              |  |

| 01         | 300mA (default)    |  |

| 10         | 400mA              |  |

| 11         | 500mA              |  |

#### **Fast-Charge Mode and Settings**

As the ISENSN pin rises above VPREC, the charger enters fast-charge mode and starts switching. Notice that the switching charger does not integrate input power source (AC adapter or USB input) detection. Thus, the switching charger does not set the charge current automatically. Unlike the linear charger (LDO), the switching charger (Buck converter) is a current amplifier. The current drawn by the switching charger is different from the current into the battery. The user can set the Average Input Current Regulation (AICR) and output charge current (I<sub>CHRG</sub>) respectively.

#### Cycle-by-Cycle Current Limit

The charger of the switching charger has an embedded cycle-by-cycle current limit for inductor. Once the inductor current touches the threshold, the charger stops charging immediately to prevent over current from damaging the device. Notice that, the mechanism cannot be disabled by any way.

#### **Adapter Detection**

RT9481 includes the VBUS detection function. When VBUS plugs in, CHGGOODADP STAT will reset to 0 once VBUS not rising exceeds 3.8V after 16ms. Besides, if VBUS falling below 3.8V during the charging interval, CHGBADADP\_ STAT is set as 1 to inform customer the poor adapter situation.

#### Average Input Current Regulation (AICR)

The AICR levels are 100mA to 2A programmed by I<sup>2</sup>C per 50mA.

#### Charge Current (ICHRG)

The charge current into the battery is determined by the sense resistor (R<sub>SENSE</sub>) and ICC setting by  $I^2C$ . The voltage between the ISENSP and ISENSN pins is regulated to the voltage control by ICC setting.

As the R<sub>SENSE</sub> is  $10m\Omega$ , the Fast-Charge currents are 700mA to 2.7A programmed by I<sup>2</sup>C per 250mA.

| ICHG[3:0] | VCC    | ICHG $R_{SENSE}$ is 10m $\Omega$ |  |  |

|-----------|--------|----------------------------------|--|--|

| 0000      | 7mV    | 0.7A (default)                   |  |  |

| 0001      | 9.5mV  | 0.95A                            |  |  |

| 0010      | 12mV   | 1.2A                             |  |  |

| 0011      | 14.5mV | 1.45A                            |  |  |

| 0100      | 17mV   | 1.7A                             |  |  |

| 0101      | 1.95mV | 1.95A                            |  |  |

| 0110      | 2.2mV  | 2.2A                             |  |  |

| 0111      | 2.45mV | 2.45A                            |  |  |

| 1000      | 2.7mV  | 2.7A                             |  |  |

Table 4. ICHG Register Setting Table

#### **Constant Voltage Mode and Settings**

The switching charger enters constant voltage mode when the VBAT voltage is close to the output-charge voltage (VBATREG). Once in this mode, the charge current begins to decrease. For default settings (charge current termination is disabled), the switching charger does not turn off and always regulates the battery voltage at VBATREG. However, once the charge current termination is enabled, the charger terminates if the charge current is below termination current (I<sub>EOC</sub>) in constant-voltage mode. The charge current termination function is controlled by the  $I^2C$  interface.

Copyright © 2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation. www.richtek.com

After termination, a new charge cycle restarts when one of the following conditions is detected :

- ► The ISENSN pin voltage falls below the V<sub>BATREG</sub> as V<sub>REC</sub> threshold.

- ► VBUS Power On Reset (POR).

- ► Enable bit toggle or Charger reset (via I<sup>2</sup>C interface)

### Battery Charge Voltage (VBATREG)

The output-charge voltage is set by the  $I^2C$  interface. Its range is from 3.65V to 4.6V per 25mV.

### Termination Current (IEOC)

If the charger current termination is enabled (TE bit = "1"), the end-of-charge current is determined by both the termination current sense voltage (V<sub>EOC</sub>) and sense resistor (R<sub>SENSE</sub>). As R<sub>SENSE</sub> is 10m $\Omega$ , I<sub>EOC</sub> is set by the I<sup>2</sup>C interface from 150mA to 600mA.

| EOC[2:0] | VEOC    | IEOC $R_{SENSE}$ is 10m $\Omega$ |  |

|----------|---------|----------------------------------|--|

| 000      | Disable | Disable                          |  |

| 001      | 1.5mV   | 150mA                            |  |

| 010      | 2mV     | 200mA (default)                  |  |

| 011      | 2.5mV   | 250mA                            |  |

| 100      | 3mV     | 300mA                            |  |

| 101      | 4mV     | 400mA                            |  |

| 110      | 5mV     | 500mA                            |  |

| 111      | 6mV     | 600mA                            |  |

Table 5. EOC Register Setting Table

### **VBUS Voltage Protection in Charge Mode**

During charge mode, there are two protection mechanisms against if input power source capability is less than the charging current setting. One is AICR and the other is minimum input voltage regulation. A suitable level of AICR can prevent VBUS drop by the insufficient capability. As the AICR setting is not suitable, MIVR will regulate the VBUS in the setting level and sink the maximum current of power source.

### Sleep Mode ( $V_{VBUS} - V_{VBAT} < V_{SLP}$ )

The switching charger enters sleep mode if the voltage drop between the VBUS and ISENSN pins falls below  $V_{SLP}$ . In sleep mode, the reverse blocking switch and PWM are all turned off. This function prevents battery drain during poor or no input power source.

### **VBUS Over Voltage Protection**

When VBUS rises above the input over voltage threshold, the switching charger stops charging and then sets fault status bits. The condition is released when VBUS falls below OVP threshold. The switching charger then resumes charging operation.

## Reverse Boost Mode Operation Trigger and Operation

The switching charger features Boost support. When BOOST function is enabled, the synchronous boost control loop takes over the power MOSFETs. In boost mode, the VMID pin is regulated to 5V (typ.) to support other BOOST devices connected to the USB connector.

### **USBOUT Over-Voltage Protection**

In boost mode, the output over voltage protection is triggered when the VMID voltage is above the output OVP threshold. When OVP occurs, the boost converter stops switching and turns off immediately.

### **Battery Protection**

### Battery Over-Voltage Protection in Charge Mode

The switching charger monitors the VBAT voltage for output over voltage protection. In charge mode, if the VBAT voltage rises above V<sub>OVP\_BAT</sub> x V<sub>BATREG</sub>, such as when the battery is suddenly removed, the switching charger stops charging and then sets fault status bits and sends out fault pulse at the INT pin. The condition is released when the VBAT voltage falls below (V<sub>OVP\_BAT</sub> –  $\Delta$ V<sub>OVP\_BAT</sub>) x V<sub>OVP\_BAT</sub>. The switching charger then resumes charging process with default settings and the fault is cleared.

### Low Battery Voltage Protection (LBP)

When the Battery voltage is lower than a specified value, the converter will stop switching. Until the battery voltage rises above the low battery voltage protection threshold plus hysteresis voltage value, the converter resumes switching. The low battery voltage protection can be programmed with 8 different levels (2.5V to 3.2V).

Copyright © 2016 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Table 6. LBP Register Setting Table |                              |  |  |

|-------------------------------------|------------------------------|--|--|

| LBP[2:0]                            | Low Battery Protection Level |  |  |

| 000                                 | 2.5V                         |  |  |

| 001                                 | 2.6V                         |  |  |

| 010                                 | 2.7V                         |  |  |

| 011                                 | 2.8V                         |  |  |

| 100                                 | 2.9V                         |  |  |

| 101                                 | 3V (default)                 |  |  |

| 110                                 | 3.1V                         |  |  |

| 111                                 | 3.2V                         |  |  |

#### **USB Battery Charging Specification**

The RT9481 supports adapter detection for dedicated charging port, Charging downstream port and Standard downstream port by D- and D+.

#### **USB Dedicated Charging Port Controller**

The RT9481 supports an USB dedicated charging port (DCP) controller. The DCP controller detects USB data line voltage, and automatically provides the correct electrical signatures on the data lines (DM and DP) to charge compliant devices. D+ =2.7V and D- =2.0V. BC1.2 DCP, required to short the D+ Line to the D-Line and 1.2 V on both D+ and D- Lines.

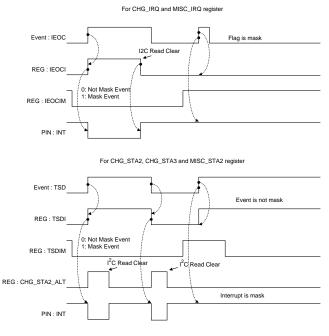

#### **IRQ and STA Operation**

RT9481 summarize all IRQ items in the register table. All IRQ\_status registers are implemented as reset after read. If IRQ\_enable bit is Low, the IRQ\_status bit will not update status. IRQ\_enable will mask IRQ\_status to trigger IRQ Low, so the system can decide which interrupt is necessary.

When STA low to high or high to low IRQ will be trigger but STA will keep situation and cannot be masked only mask IRQ.

Figure 1. IRQ and STA Operation

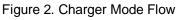

### **Charger Mode Flow**

The Charger mode is start from adapter attached, the flag of VBUS\_STAI (MISC\_STA2[5]) will be set to high and the host can read this bit to check adapter attached or not. Then adapter type detection will auto start to detect the type of adapter with BC1.2 standard. Its detection result is show in the flag ADAPTER\_STAI (MISC\_STA1[6:5]) when ADAPTER\_DONE (MISC\_IRQ[6]) is set.

The host could decide the user Charger setting by adapter type, like AICR or ICHG etc... For example, set IAICR to 0.5A, if the adapter type is SDP. Set IAICR to 1.5A, if the adapter type is CDP or DCP.

If there is no Charger fault event triggered in registers CHG\_STAT1 or CHG\_STAT2, the host can decide to turn on Charger or not. Set user Charger setting from registers CHG\_CTRL1 to CHG\_CTRL6 before turn on Charger. Please refer to I2C register map for detailed functional setting. To enable Charger by setting OPA\_MODE (CHG\_CTRL1[0]) to low and setting SWITCHING\_EN (CHG\_STA1[0]) to high.

When charging is start the host can check CHG\_STAT (CHG\_STA1[5]) to make sure the charging is in progress.

If system want to implement the charge and bypass feature, the host can set EN\_LDSW (USBOUT\_CTL[6]) to high to turn on Load Switch and set EN\_DCP (USBOUT\_CTL[7]) to high to turn on DCP Controller, then the power of adapter could bypass to device when battery is under charging.

### Charger Terminate

There are three conditions to terminate Charger and the host could set SWITCHING\_EN (CHG\_STA1[0]) to low to turn off Charger.

### End of Charge (EOC)

Set TE (CHG\_CTRL1[1]) to high to enable Termination function, then the Charger will terminate automatically and CHTERMI (CHG\_IRQ[7]) is set to high when the charging current is below IEOC (CHG\_CTRL5[2:0]) and charging voltage is above re-charge threshold. The host could turn on Charger again when CHRCHGI (CHG\_IRQ[5]) is set.

### Charger Fault

The Charger automatically terminates when Charger fault event be triggered in Table 7.

Copyright © 2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9481-04 August 2016

| Table 7. Charger Fault Event      |                     |             |  |  |  |

|-----------------------------------|---------------------|-------------|--|--|--|

| Charger Fault Event Flag Register |                     |             |  |  |  |

| Power Status                      | $PWR_Rdy = 0$       | CHG_STA1[2] |  |  |  |

| Thermal Shutdown                  | TSD_STAT = 1        | CHG_STA2[7] |  |  |  |

| VBUS OVP                          | VBUSOVP_STAT = 1    | CHG_STA2[6] |  |  |  |

| Reverse Protection                | CHRVP_STAT = 1      | CHG_STA2[5] |  |  |  |

| Battery OVP                       | CHBATOV_STAT = 1    | CHG_STA2[4] |  |  |  |

| Good Adaptor Detection            | CHGGOODADP_STAT = 0 | CHG_STA2[1] |  |  |  |

| Bad Adaptor Detection             | CHGBADADP_STAT = 1  | CHG_STA2[0] |  |  |  |

#### Adapter Detach

The flag of VBUS\_STAI will be set to low when adapter detached and it will terminate Charger directly.

Copyright © 2016 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

DS9481-04 August 2016

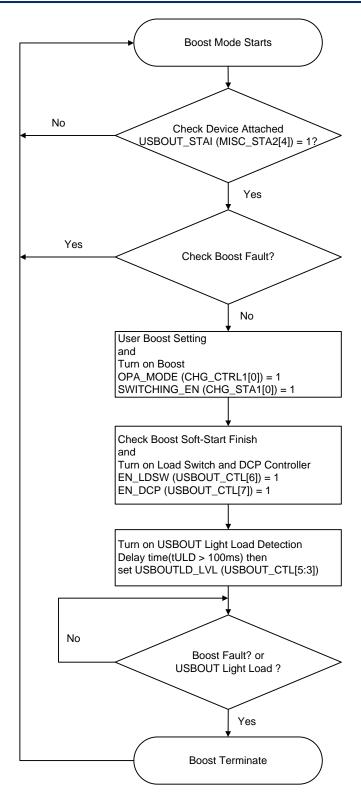

Figure 3. Boost Mode Flow

Copyright © 2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation. DS9481-04 August 2016 www.richtek.co

### **Boost Mode Flow**

The Boost mode could start from device attached, and the flag of USBOUT\_STAI (MISC\_STA2[4]) will be set to high for indicate the device attached. The USBOUT attach detection is control by register ATTACH CTL[5].

If there is no any Boost fault triggered in registers CHG STAT2 or BST IRQ or MISC IRQ, the host can decide to turn on Boost or not. The host can set user Boost setting before turn on the Boost from registers CHG\_CTRL1 to CHG\_CTRL6 and please refer to I2C register map for detailed functional setting.

The Boost could be enable by set OPA\_MODE (CHG CTRL1[0]) to high and setting SWITCHING EN (CHG\_STA1[0]) to high.

Before enable the Load Switch suggest to wait Boost soft start (CHG\_IRQ[3]) finish, it can guarantee the Boost ready for output.

Then the host could set EN LDSW (USBOUT CTL[6]) to high to turn on Load Switch and the Boost would start output current to device. For let device identify the power bank is a powerful adapter, to set EN DCP (USBOUT\_CTL[7]) to high to turn on DCP controller at the same time.

USBOUT light load detection (USBOUTLD\_CTL[5:3]) can help the host to check the device charging full or device detached by the condition of USBOUT current is under the threshold or not. But according to USB standard, the device will start charging after it connect to adapter 100 millisecond. We suggest to add delay time t<sub>ULD</sub> over 100 millisecond before enable USBOUT light load detection after Load Switch turn on. It could avoid USBOUT light load detection trigger early.

The host could read BOOST\_STAT (CHG\_STA1) to make sure the Boost is in progress.

#### **Discharging Terminate**

There are two conditions to terminate discharging.

#### **Boost Fault**

The Boost automatically terminates when Boost fault event be triggered in Table 8.

# Flag

**Boost Fault**

| Event                                   | Tiag       | Register    |  |

|-----------------------------------------|------------|-------------|--|

| Thermal<br>Shutdown                     | TSD_STAT   | CHG_STA2[2] |  |

| Boost Thermal<br>Shutdown               | BSTTSDI    | BST_IRQ[7]  |  |

| VMID Over<br>Voltage Protect            | BSTVMIDVPI | BST_IRQ[6]  |  |

| Battery Voltage<br>is too Low           | BSTLOWVI   | BST_IRQ[5]  |  |

| Load Switch<br>Short Current<br>Protect | LDSW_SCPI  | MISC_IRQ[5] |  |

| VMID Short<br>Current Protect           | VMIDSCPI   | MISC_IRQ[1] |  |

| VMID Under<br>Voltage Protect           | VMIDUVPI   | MISC_IRQ[0] |  |

Table 8. Boost Fault Event

#### USBOUT Light Load

It means device charging full or device detached when USBOUTLD\_STAT (MISC\_STA2) set to high. According to USBOUTLD\_STAT, the host could decide to turn off Boost or not.

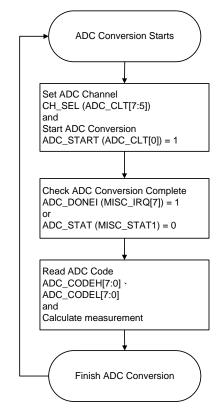

Figure 4. ADC Conversion Operation Flow

Register

#### **ADC Conversion Operation Flow**

Figure 4 shows ADC conversion operation flow. ADC conversion starts from set ADC channel CH\_SEL (ADC\_CLT[7:5]) and set ADC\_START (ADC\_CLT[0]) to high. ADC conversion time is 25ms and ADC\_DONEI (MISC\_IRQ[7]) will set to high and ADC\_STAT (MISC\_STAT1) will set to low also, the host could read them to make sure ADC conversion completes.

The host could read ADC code high byte (ADC\_CODEH[7:0]) and low byte (ADC\_CODEL[7:0]) to calculate the voltage or current measurement relative to ADC channel.

Table 9 shows the every measurement equation of ADC channel. Please pay attention to the calculation of IBAT, it need to consider the setting of ICHG (CHG\_CTRL6[7:4]).

ADC code format is unsigned. If operation is Charger mode, IBAT means battery charging current. If operation is boost mode, IBAT means battery discharging current.

The code of IBAT is invalid if SWITCHING\_EN (CHG\_STA1[0]) is set to low. And the code of IUSBOUT is invalid if EN\_LDSW (USBOUT\_CTL[6]) is set to low.

The TS pin will automatic output 35uA during ADC TS channel under conversion. It will cause the IR drop on NTC thermistor and then ADC measure the voltage on TS pin. The host could get the temperature by mapping the voltage. We suggest to use  $10k\Omega$  NTC which the beta (B25/85) is 3435k, like SEMITEC 103AT.

| Table 5. Calculate Voltage of Current measurement |                                                             |                   |  |

|---------------------------------------------------|-------------------------------------------------------------|-------------------|--|

| ADC Channel Measurement Equation                  |                                                             | Measurement Range |  |

| VBAT                                              | VBAT = ( ( ADC_CODEH x 256 ) + ADC_CODEL ) x 1.25 mV        | 0V to VDDA        |  |

| VBUS                                              | VBUS = ( ( ADC_CODEH x 256 ) + ADC_CODEL ) x 6.25 mV        | 1V to 18V         |  |

| USBOUT                                            | USBOUT = ( ( ADC_CODEH x 256 ) + ADC_CODEL ) x 6.25 mV      | 1V to 6V          |  |

| TS                                                | TS = ( ( ADC_CODEH x 256 ) + ADC_CODEL ) x 1.25 mV          | 0V to VDDA        |  |

| IBAT                                              | IBAT = ( ( ADC_CODEH x 256 ) + ADC_CODEL ) x ICHG x 1.25 mA | 0A to 6A          |  |

| IUSBOUT                                           | IUSBOUT = ( ( ADC_CODEH x 256 ) + ADC_CODEL ) x 2.5 mA      | 0A to 6A          |  |

#### Table 9. Calculate Voltage or Current Measurement

|        | Table 10. Protection Items |                                                     |                                           |                           |                                                                |  |

|--------|----------------------------|-----------------------------------------------------|-------------------------------------------|---------------------------|----------------------------------------------------------------|--|

|        | Protection<br>Type         | Threshold (typical)<br>Refer to Electrical<br>Spec. | Protection Methods                        | IC Shutdown<br>Delay Time | Reset Method                                                   |  |

| _      | LBP                        | VBAT < LPB setting                                  | Exist boost mode                          | None                      | VDDA power reset                                               |  |

| VBAT   | OVP                        | VBAT > 1.07 x<br>CHG_CV                             | Stop charging                             | None                      | VDDA power reset or<br>VBAT falling to 1.02 x<br>CHG_CV        |  |

| VDDA   | UVP                        | VDDA < 2.35V                                        | analog circuit disable                    | None                      | VDDA >2.5V                                                     |  |

|        | OVP                        | VBUS > 6V                                           | Stop charging, UUG disable                | None                      | VDDA power reset or<br>VBUS falling to<br>VBUSOVP-hysteresis   |  |

|        | Bad<br>adapter             | VBUS < 3.8V                                         | None                                      | None                      | VDDA power reset or<br>VBUS rising to<br>VBUS_BAD + hysteresis |  |

|        | Good<br>adapter            | None                                                | None                                      | None                      | None                                                           |  |

| VBUS   | RVP                        | VBUS < VBAT                                         | Stop charging, UUG disable                | None                      | VDDA power reset or<br>VBUS rising above<br>VBAT               |  |

|        | TREG                       | Temp. ≒ Thermal<br>regulation setting               | None                                      | None                      | VDDA power reset or thermal loop release                       |  |

|        | MIVR                       | VBUS ≒ MIVR setting                                 | None                                      | None                      | VDDA power reset or<br>MIVR loop release                       |  |

|        | AICR                       | IBUS ≒ AICR setting                                 | None                                      | None                      | VDDA power reset or<br>AICR loop release                       |  |

|        | OVP                        | N/A                                                 | N/A                                       |                           | N/A                                                            |  |

| VMID   | UVP                        | 3.5V                                                | Absolute voltage below threshold          |                           | sEn_VMIDUVP                                                    |  |

|        | SCP                        | 3.5V                                                | Absolute voltage below threshold          |                           | sEn_VMIDUVP                                                    |  |

|        | LDSWREG                    | 1.5A/2A/2.5A/3A                                     | Load current is above current limit       |                           | sEn_LDSW                                                       |  |

| USBOUT | LDSWSCP                    | VDS~1.4V                                            | VDS voltage is too<br>high                |                           | sEn_LDSW                                                       |  |

|        | Current<br>limit           | 1.5A/2A/2.5A/3A                                     | Load current reach to limit-point         |                           | sEn_LDSW                                                       |  |

| Boost  | Current<br>limit           | Inductor current > 6A                               | cycle by cycle,<br>inductor current limit | None                      | Inductor current < 6A                                          |  |

| OTP    | Thermal<br>Shutdown        | Temp > 160°C                                        | Stop charging, UUG disable                | None                      | Temp < 160°C                                                   |  |

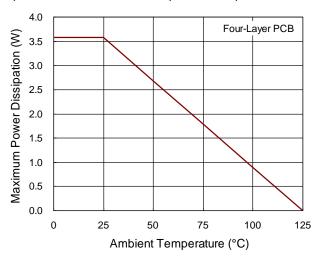

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula :

#### $\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) / \theta_{\mathsf{J}\mathsf{A}}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WQFN-24L 4x4 package, the thermal resistance,  $\theta_{JA}$ , is 28°C /W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at T<sub>A</sub> = 25°C can be calculated by the following formula :

$P_{D(MAX)}$  = (125°C - 25°C) / (28°C /W) = 3.57W for WQFN-24L 4x4 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 5 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 5. Derating Curve of Maximum Power Dissipation

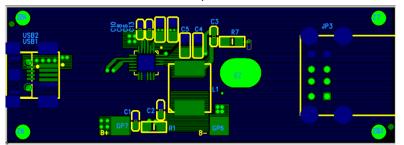

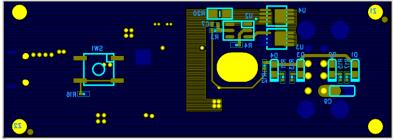

#### Layout Considerations

Some PCB layout guidelines for optimal performance of RT9481 list as following. Following figure shows the real PCB layout considerations and it is based on the real component size whose unit is millimeter (mm).

- Place the input and output capacitors as close to the input and output pins as possible.

- Keep the main power traces as wide and short as possible.

- The output inductor and boot capacitor should be placed close to the chip and LX pins.

- The battery voltage sensing point should be placed after the output capacitor.

- To optimize current sense accuracy, connect the traces to RSENSE with Kelvin sense connection by ISENSN and ISENSP.

- LX node is with high frequency voltage swing and should be kept small area. Keep analog components away from LX node to prevent stray capacitive noise pick-up.

- Add Snubber in LX: 2Ω resister 0805 package and 1nF capacitor.

23

Copyright © 2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation. DS9481-04 August 2016 www.richtek.com

### **RT9481**

Top:

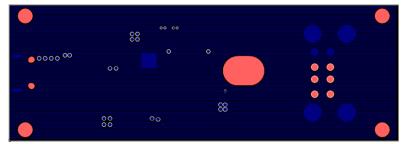

layer2 :

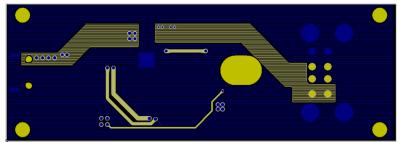

Layer3 :

Bottom :

Figure 6. PCB Layout Guide

25

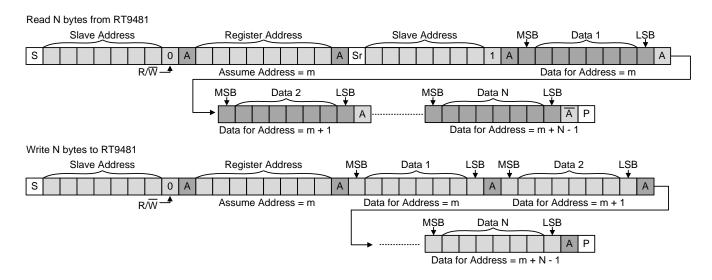

### I<sup>2</sup>C Interface

RT9481  $I^2C$  slave address = 7'b1101100.

$I^2C$  interface support fast mode (bit rate up to 400kb/s). The write or read bit stream (N  $\ge$  1) is shown below :

### I<sup>2</sup>C Register Map

### Register of the SWCHG

| Function        |          | gister<br>dress | b[7]<br>(MSB)                                       | b[6]           | b[5]           | b[4]                         | b[3]          | b[2]            | b[1]     | b[0]<br>(LSB) |

|-----------------|----------|-----------------|-----------------------------------------------------|----------------|----------------|------------------------------|---------------|-----------------|----------|---------------|

|                 |          | Meaning         | Fix_ Freq                                           | Sel_<br>SWFreq | Higher_<br>OCP | HZ                           | LBP<br>Enable |                 | LBP[2:0] |               |

| Low BAT<br>CTRL | 0X00     | Default         | 1                                                   | 1              | 0              | 0                            | 1             | 1               | 0        | 1             |

| CIKL            |          | Read/<br>Write  | R/W                                                 | R/W            | R/W            | R/W                          | R/W           | R/W             | R/W      | R/W           |

| F               | Fix_Freq |                 | Control the sw<br>0 : Auto-chang<br>1 : Fixed frequ | e frequency    |                | ynamic or fix                |               |                 |          |               |