# 4:1 Micro USB Switches with Accessory Detection

## **General Description**

The RT8979 is a USB port accessory detector and switch (USB1, USB2, UART & MHL). The RT8979 adopts I<sup>2</sup>C bus for control and also uses an internal method to determine the connected device.

The RT8979 provides a device detection function by using the USB ID signal pin and the VBUS voltage. The ID pin resistance and VBUS voltage determine the unique detection method for various accessory. The host microprocessor adopts I<sup>2</sup>C to control the switch position and read the results of the accessory detection. The RT8979 also detects USB chargers including dedicated chargers (D+/D- shorted) and high power host/hub chargers.

## **Ordering Information**

RT8979 □

Package Type

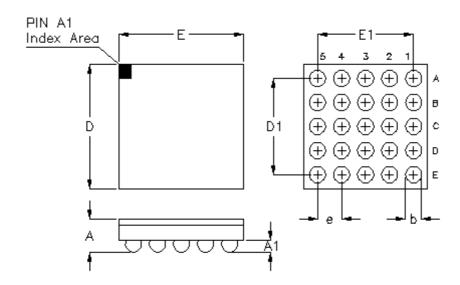

WSC: WL-CSP-25B 2.07x2.07 (BSC)

Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

## **Marking Information**

0V YM DNN

DS8979-00 May 2021

0V : Product Code YMDNN : Date Code

### **Features**

- Hi-Speed USB Operation (USB1 & USB2)

- UART & MHL Switch

- Interrupt for Device Insertion and Removal

- Factory Support

- 28V Maximum Rating for DC Adapter

- I<sup>2</sup>C Controlled Interface

- DP\_CON/DM\_CON TVS Diode Integrated for Surge Protection Up to ±15V

- ID\_CON TVS Diode Integrated for Surge Protection Up to ±20V

- Battery Charger Detection 1.2

## **Applications**

- Mobile Applications

- Smart Handheld device

- Tablets

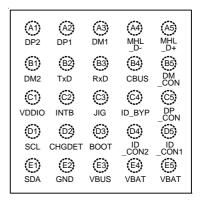

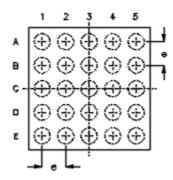

## **Pin Configuration**

(TOP VIEW)

WL-CSP 25B 2.07x2.07 (BSC)

Copyright ©2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Downloaded From Oneyac.com

# **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                                                                                                    |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1      | DP2      | D+ signal switch path; dedicated USB port to be connected to USB_HOST2 on the cellphone.                                                                                                        |

| A2      | DP1      | D+ signal switch path; dedicated USB port to be connected to USB_HOST1 on the cellphone.                                                                                                        |

| А3      | DM1      | D- signal switch path; dedicated USB port to be connected to USB_HOST1 on the cellphone.                                                                                                        |

| A4      | MHL_D-   | D- signal switch path; dedicated MHL port to be connected to MHL TX on the cellphone.                                                                                                           |

| A5      | MHL_D+   | D+ signal switch path; dedicated MHL port to be connected to MHL TX on the cellphone.                                                                                                           |

| B1      | DM2      | D- signal switch path; dedicated USB port to be connected to USB_HOST1 on the cellphone.                                                                                                        |

| B2      | TxD      | Tx switch path from resident UART on the cellphone.                                                                                                                                             |

| В3      | RxD      | Rx switch path from resident UART on the cellphone.                                                                                                                                             |

| B4      | CBUS     | CBUS signal path; connected to the MHL TX on the cellphone.                                                                                                                                     |

| B5      | DM_CON   | Connected to the USB connector D- pin. Depending on the signaling mode, this pin can be switched to DM1, DM2, MHL_D- or TxD.                                                                    |

| C1      | VDDIO    | I <sup>2</sup> C interface power; baseband processor interface I/O supply pin.                                                                                                                  |

| C2      | INTB     | Interrupt; active-low output used to prompt the phone baseband processor to read the I <sup>2</sup> C register bits. Indicates a change in the ID_CON pin status or accessorires attach status. |

| C3      | JIG      | Active-low output control signal driven by the device and used for factory test modes.                                                                                                          |

| C4      | ID_BYP   | ID signal switch path used during USB On-The-Go operation to allow phone transceiver access to the state of the ID pin on the USB connector.                                                    |

| C5      | DP_CON   | Connected to the USB Connector D+ Pin. Depending on the signaling mode, this pin can be switched to DP1, DP2, MHL_D+ or RxD.                                                                    |

| D1      | SCL      | I <sup>2</sup> C interface clock.                                                                                                                                                               |

| D2      | CHGDET   | Open-drain, active-low output; used to signal the charger IC that a charger has been attached.                                                                                                  |

| D3      | воот     | Open-drain, output control signal driven by MUS and used by the processor for Force Download Mode, active-low and need external pull-up.                                                        |

| D4      | ID_CON2  | Connected to USB connector ID pin or SBU and used for external battery testing.                                                                                                                 |

| D5      | ID_CON1  | Connected to USB connector ID pin or SBU and used for detecting accessories or button presses and external battery testing.                                                                     |

| E1      | SDA      | I <sup>2</sup> C interface data.                                                                                                                                                                |

| E2      | GND      | Common ground.                                                                                                                                                                                  |

| E3      | VBUS     | Connected to the connector of VBUS.                                                                                                                                                             |

| E4, E5  | VBAT     | Battery voltage, connected to the positive terminal of the battery pack; VBAT is a power path connection.                                                                                       |

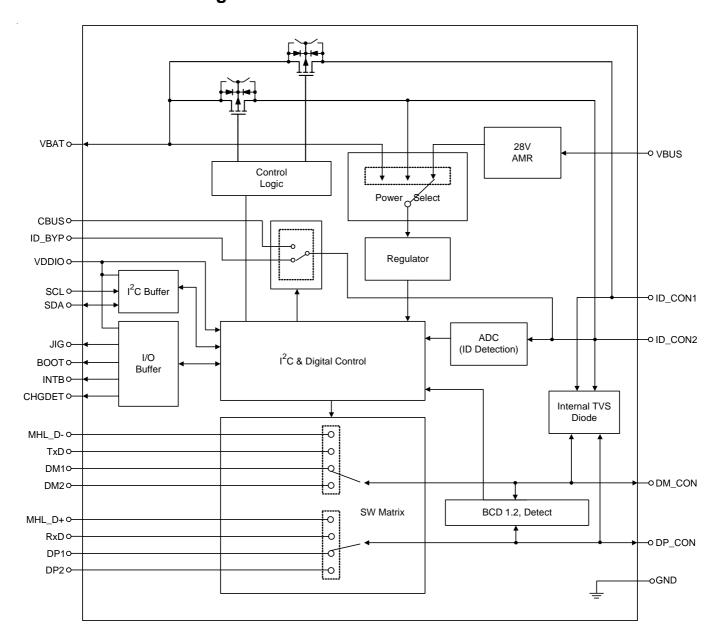

## **Functional Block Diagram**

## **Operation**

The RT8979 is a USB port accessory detector and switch of USB, UART & MHL. The RT8979 supports accessory detection function through the unique characteristics from VBUS voltage, ID resistance and USB data line status.

The RT8979 is programmable by I<sup>2</sup>C interface and it can communicate with microprocessor.

Copyright ©2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# Absolute Maximum Ratings (Note 1)

| • VBUS to GND                                                               | -0.3V to 28V   |

|-----------------------------------------------------------------------------|----------------|

| Other Pins to GND                                                           | -0.3V to 6V    |

| USB & ID_CON to CBUS Switch I/O Current                                     | Max 25mA       |

| UART Switch I/O Current                                                     | Max 12mA       |

| Continuous Current from ID_CON to VBAT (ID_CON1 shorted to ID_CON2)         | Max 2.5A       |

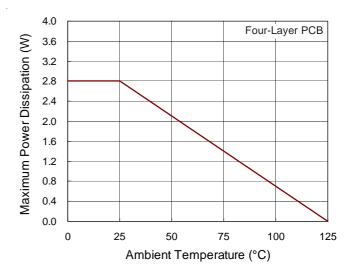

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                |

| WL-CSP 25B 2.07x2.07 (BSC)                                                  | 2.8W           |

| Package Thermal Resistance (Note 2)                                         |                |

| WL-CSP 25B 2.07x2.07 (BSC), $\theta_{JA}$                                   | 35.6°C/W       |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C          |

| • Junction Temperature                                                      | 150°C          |

| Storage Temperature Range                                                   | –65°C to 150°C |

| ESD Susceptibility (Note 3)                                                 |                |

| HBM (Human Body Model)                                                      | 2kV            |

|                                                                             |                |

| Recommended Operating Conditions (Note 4)                                   |                |

| Battery Supply Voltage, VBAT                                                | 3.0V to 4.7V   |

| USB Supply Voltage, VBUS                                                    | 4V to 20V      |

| Processor Supply Voltage, VDDIO                                             | 1.7V to 3.6V   |

| • Junction Temperature Range                                                | –40°C to 125°C |

| Ambient Temperature Range                                                   | –40°C to 85°C  |

## **Electrical Characteristics**

$(T_A = 25^{\circ}C, \text{ unless otherwise specified})$

| Parameter                                                    | Symbol              | Symbol Test Conditions                  |           | Min            | Тур | Max                        | Unit |

|--------------------------------------------------------------|---------------------|-----------------------------------------|-----------|----------------|-----|----------------------------|------|

| Output High Voltage (for push-pull CMOS output pins)         | Vон_рр              | ISOURCE = 2mA                           |           | 0.7 x<br>VDDIO |     |                            | V    |

| Output Low Voltage (for push-pull CMOS output pins)          | V <sub>OL_PP</sub>  | I <sub>SINK</sub> = 10mA                |           |                | 0.4 | V                          |      |

| Output Low Voltage (for open-drain output pins)              | V <sub>OL_OD</sub>  | I <sub>SINK</sub> = 1mA                 |           |                | 0.4 | ٧                          |      |

| Logic High Input Voltage (SDA, SCL)                          | V <sub>IH</sub>     |                                         | 1.4       |                | 1   | ٧                          |      |

| Logic Low Input Voltage (SDA, SCL)                           | VIL                 |                                         |           |                | 0.4 | ٧                          |      |

| Input pin Leakge Current (SDA, SCL)                          | I <sub>INLEAK</sub> | Input Voltage 0.20                      | 6 to 2.3V | -10            |     | 10                         | μΑ   |

| Low-Level Output Voltage at                                  |                     | V <sub>DDIO</sub> > 2V                  |           | 0              |     | 0.4                        |      |

| 3mA Sink Current<br>(Open-Drain)                             | V <sub>OL1</sub>    | V <sub>DDIO</sub> < 2V                  | (Note 5)  |                |     | 0.2 x<br>V <sub>DDIO</sub> | V    |

| Battery Supply Standby<br>Current (No Accessory<br>Attached) | Iccsb               | VBAT = 3 to 4.5V<br>Accessory static of | -         |                | 5   | 10                         | μΑ   |

Copyright ©2021 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Parameter                                                        | Symbol               | Test Conditions                                                                                                  | Min   | Тур | Max   | Unit |

|------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| Battery Supply Standby<br>Current (with Accessory<br>Attached)   | ICCSB_ATT            | VBAT = 3.8V, with Accessory's static current                                                                     | 1     | 35  | 50    | μА   |

| Power Off Leakage Current On Data Ports                          | IOFF_DATA            | VBAT = 0, VSW = 3.6V                                                                                             |       |     | 18    | μΑ   |

| Off-Leakage Current                                              | I <sub>NO_OFF</sub>  | I/O Pins = 0.3V, VBAT = 3.0 to 4.5V                                                                              | -0.5  |     | 0.5   | μΑ   |

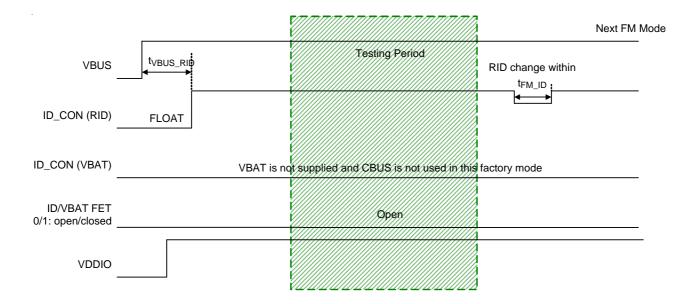

| Current Consumption During FM8 With Only VBAT_ID as Power Supply | ICC_FM8              | VBAT_ID = 3.3 to 4.4V                                                                                            | 1     | 60  |       | μА   |

| ID_CON Short-Circuit Current                                     | IDSHRT               | VBAT = 3.0 to 4.5V,<br>Current Limit if ID_CON =<br>0V                                                           |       | 5   |       | mA   |

| USB 1/2 Switch Path                                              |                      |                                                                                                                  |       |     |       |      |

| USB Analog Signal Range                                          | V <sub>SW_USB</sub>  | VBUS = 5V                                                                                                        | 0     |     | 3.6   | V    |

| USB Switch On Resistance                                         | R <sub>ON_USB</sub>  | VBAT = 3 to 4.5V,<br>VD+/- = 0V, 0.4V with I <sub>ON</sub> =<br>8mA                                              |       | 6   |       | Ω    |

| DP_CON, DM_CON On Capacitance                                    | Con_usb              | VBAT = 3.8V,<br>D+/- = 400mVpp,<br>freq = 240MHz                                                                 |       | 10  |       | pF   |

| OFF Capacitance                                                  | C <sub>OFF_USB</sub> | VBAT = 3.8V,<br>freq = 240MHz                                                                                    |       | 5   |       | pF   |

| Differential –3dB Bandwidth                                      | BW (Insertion loss)  | VBAT = 3.0V to 4.5V, $V_{IN}$ = 400m $V_{pk-pk}$ , $RL$ = 50 $\Omega$ , $CL$ = 0pf, (on USB data paths) (Note 5) | I     | 700 | 1     | MHz  |

| UART Switch Path                                                 |                      |                                                                                                                  |       |     |       |      |

| UART Analog Signal Range                                         | Vsw_uart             |                                                                                                                  | 0     |     | 4.4   | V    |

| UART Switch On Resistance                                        | RON_UART             | VBAT = 3.0 to 4.5V,<br>VD+/- = 0V, 4.4V with I <sub>ON</sub> =<br>2mA                                            |       | 28  |       | Ω    |

| MHL Switch Path                                                  |                      |                                                                                                                  |       |     |       |      |

| MHL Analog Signal Range                                          | Vsw_mhL              |                                                                                                                  | 1.375 |     | 3.465 | V    |

| MHL Switch On Resistance                                         | R <sub>ON_MHL</sub>  | VBAT = 3 to 4.5V,<br>V <sub>SW</sub> = 1.375 to 3.465V with<br>I <sub>ON</sub> = 8mA                             | 1     | 5   |       | Ω    |

| VBAT MOSFET Switch Path                                          |                      |                                                                                                                  |       |     |       |      |

| VBAT MOSFET On<br>Resistance, ID_CON1 shorted<br>to ID_CON2      | R <sub>ON_FET</sub>  | VBAT = 3 to 4.5V, I <sub>ON</sub> = 1A<br>@ Room Temperature                                                     | !     | 50  |       | mΩ   |

| Resistance from ID_CON1 to ID_CON2 when VBAT MOSFET is OFF       | RIDVBAT_OFF          | VBAT = 3 to 4.5V                                                                                                 | 6     |     |       | MΩ   |

Copyright ©2021 Richtek Technology Corporation. All rights reserved.

| Parameter                                                                                                                        | Symbol                | Test Conditions                                                          | Min | Тур                                  | Max | Unit |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------|-----|--------------------------------------|-----|------|

| ID Bypass Switch Path                                                                                                            |                       |                                                                          |     |                                      |     |      |

| ID Analog Signal Range                                                                                                           | Vsw_id                |                                                                          | 0   |                                      | 1.8 | V    |

| ID Bypass Switch On<br>Resistance                                                                                                | RON_IDBP              | VBAT = 3 to 4.5V, V <sub>SW</sub> = 0V, 1.8V with I <sub>ON</sub> = 10mA |     | 23                                   |     | Ω    |

| CBUS Switch Path                                                                                                                 |                       |                                                                          | •   |                                      |     |      |

| CBUS Analog Signal Range                                                                                                         | V <sub>SW_CBUS</sub>  |                                                                          | 0   |                                      | 4.4 | V    |

| CBUS Switch On Resistance                                                                                                        | R <sub>ON_</sub> CBUS | VBAT = 3 to 4.5V, V <sub>SW</sub> = 0V, 4.4V with I <sub>ON</sub> = 10mA |     | 14                                   |     | Ω    |

| Switch AC Eletrical Charateris                                                                                                   | stics                 |                                                                          |     | •                                    |     |      |

| Time after INT Mask clear to 0 until INTB goes Low when INT Mask is set to 1                                                     | t <sub>INT_MASK</sub> |                                                                          |     | 10                                   |     | ms   |

| Time from VBUS Valid to USB<br>Switches Turn On for SDP                                                                          | tsdpdet               |                                                                          |     | 300                                  |     | ms   |

| Time from VBUS Valid to USB<br>Switches Turn On for CDP<br>Only                                                                  | tchgout               |                                                                          |     | 330                                  |     | ms   |

| Time from USB Switched<br>Closed to CHGDET output<br>Low for USB charging port<br>(CDP only)                                     | tCHGDET               |                                                                          |     | 300                                  |     | ms   |

| Time from ID_CON not floating to INTB Low to Signal Accessory attached ID_CON Resistance-based only (VBUS is not valid, No VBUS) | tIDDET                |                                                                          |     | 220                                  | -1  | ms   |

| Timeout Value for Data<br>Contact During DCD Flow                                                                                | tDCD_TIMEOUT          | 300 to 1200ms,<br>300ms/step, with one step<br>to disable                |     | 300<br>600<br>900<br>1200<br>Disable | -   | ms   |

| Time for DCD Check the<br>Contact is Successful (DCD<br>Deglitch)                                                                | tDCD                  |                                                                          |     | 20                                   | 1   | ms   |

| Time for Standard ID Detection to Complete after ID Detects Contact                                                              | t <sub>ID_FLOW</sub>  |                                                                          |     | 200                                  |     | ms   |

| Time for Standard Charger<br>Detection Flow to Complete                                                                          | tchrg_flow            |                                                                          |     | 300                                  | -   | ms   |

| Time from VBAT on ID_CON<br>Valid to VBAT MOSFET<br>Closed ot Time from VBAT on<br>ID_CON Invalid to VBAT<br>MOSFET Open         | tvbat_fet             |                                                                          |     | 5                                    |     | ms   |

| Parameter                                                                                                  | Symbol                               | Test Conditions         | Min | Тур  | Max | Unit |

|------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------|-----|------|-----|------|

| Time from VBUS Invalid to<br>VBAT MOSFET Closed, Only<br>Applied to Factory Mode<br>Phone-Off Leakage Mode | tnovbus_fet                          |                         |     | 50   |     | ms   |

| Time from ID_CON not floating to BOOT LOW to signal that this is forcedownloading mode                     | trid_boot                            |                         |     | 200  |     | ms   |

| JIG BOX Timing                                                                                             |                                      | ·                       |     |      |     |      |

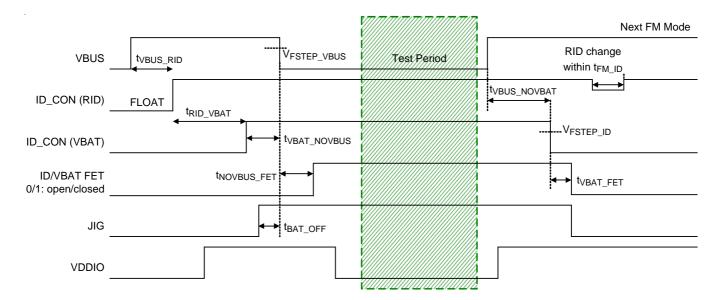

| Time from VBUS Valid to RID on ID_CON Attached                                                             | t <sub>VBUS_RID</sub>                |                         |     | 10   | 200 | ms   |

| Time from RID Attached to VBAT on ID_CON Applied                                                           | t <sub>RID_VBAT</sub>                |                         | 400 |      |     | ms   |

| Time from JIG High to VBUS Removed                                                                         | tBAT_OFF                             |                         | 10  |      |     | ms   |

| Time from VBAT on ID_CON Valid to VBUS Removed                                                             | tvbat_novbus                         |                         | 100 | 200  |     | ms   |

| Time from VBUS Valid to VBAT on ID_CON Removed                                                             | tvbus_novbat                         |                         | 600 | 700  |     | ms   |

| Time VBUS invalid to next<br>VBUS applied, only applied to<br>force download mode without<br>VBAT (FM5)    | t <sub>NOVBUS_VBUS</sub>             |                         | 80  |      |     | ms   |

| Trim from ID_CON not floating to VBUS applied in force download mode with battery (FM3)                    | t <sub>RID_VBUS</sub>                |                         | 250 |      |     | ms   |

| RID Resistance Switching<br>Time for Factory Mode                                                          | t <sub>FM_RID</sub>                  |                         | 30  |      | 70  | ms   |

| Step Voltage for Falling Edge of VBAT on ID_CON                                                            | VFSTEP_ID                            |                         |     | 2.65 |     | >    |

| Step Voltage for Falling Edge of VBUS                                                                      | V <sub>FSTEP_</sub> V <sub>BUS</sub> |                         |     | 3.2  |     | ٧    |

| Rising Time of VBAT on ID_CON                                                                              | t <sub>rVBAT_ID</sub>                | Voltage from 10% to 90% | 10  |      | 50  | ms   |

| I <sup>2</sup> C AC Electrical Characterist                                                                | ics                                  |                         |     |      |     |      |

| SCL Clock Frequency                                                                                        | f <sub>SCL</sub>                     |                         | 0   |      | 400 | kHz  |

| Hold Time (Repeated) START Condition                                                                       | thd;STA                              |                         | 0.6 |      |     | μs   |

| Low Period of SCL Clock                                                                                    | tLOW                                 |                         | 1.3 |      |     | μS   |

| High Period of SCL Clock                                                                                   | thigh                                |                         | 0.8 |      |     | μS   |

| Set-Up Time for Repeated START Condition                                                                   | tsu;sta                              |                         | 0.6 |      |     | μs   |

| Data Hold Time                                                                                             | t <sub>HD;DAT</sub>                  |                         | 0   |      | 0.9 | μS   |

Copyright ©2021 Richtek Technology Corporation. All rights reserved.

DS8979-00 May 2021 www.richtek.com

7

| Parameter                                                     | Symbol           | Test Conditions | Min | Тур | Max | Unit |

|---------------------------------------------------------------|------------------|-----------------|-----|-----|-----|------|

| Data Set-Up Time                                              | tsu;dat          |                 | 150 |     |     | ns   |

| Rise Time of SDA and SCL<br>Signals                           | t <sub>r</sub>   |                 | 20  |     | 300 | ns   |

| Fall Time of SDA and SCL<br>Signals                           | t <sub>f</sub>   |                 | 20  |     | 300 | ns   |

| Set-Up Time for STOP<br>Condition                             | tsu;sto          |                 | 0.6 |     |     | μS   |

| Bus-Free Time between Stop and Start Condition                | t <sub>BUF</sub> |                 | 1.3 |     |     | μS   |

| Pulse width of spikes that must be suppressed by input filter | tsp              | (Note 5)        | 0   |     | 100 | ns   |

- Note 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a high effectivethermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- Note 5. These items are GBD.

DS8979-00 May 2021

www.richtek.com

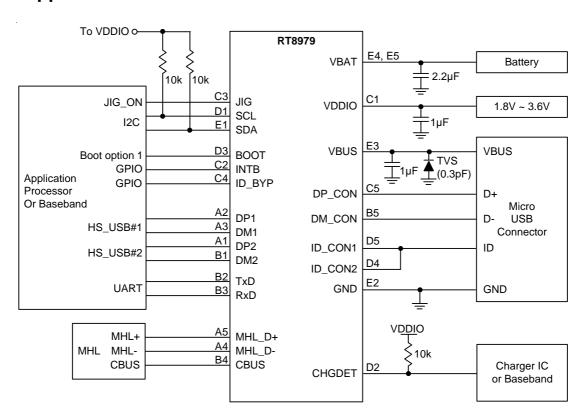

# **Typical Application Circuit**

# **Application Information**

#### **Power States Combinations**

When power is first applied, the device is reset, all the registers are initialized to the default values shown in the register table.

All the combinations of  $V_{BUS},\,V_{BAT},\,power\,on\,ID\_CON\,and\,V_{DDIO}$  are shown in Table 1.

$V_{BAT}$  is used as the primary power supply for normal operation.  $V_{DDIO}$  is the dedicated IO voltage and is only used for I<sup>2</sup>C interface and interrupt processing within the RT8979.

**Table 1. Power States Combinations**

| V <sub>BUS</sub> | V <sub>BAT</sub> | Power on ID_CON | V <sub>DDIO</sub> | Power State          | Processor<br>Communication<br>(I <sup>2</sup> C & Interrupts) | Detection VBUS<br>& ID_CON |  |  |

|------------------|------------------|-----------------|-------------------|----------------------|---------------------------------------------------------------|----------------------------|--|--|

| N                | N                | N               | N                 | Power Down           | NO                                                            | NO                         |  |  |

| N                | N                | N               | Υ                 |                      | ILLEGAL S                                                     | STATE                      |  |  |

| N                | N                | Υ               | N                 | Powered from ID_CON  | NO                                                            | NO                         |  |  |

| N                | N                | Y               | Υ                 | Powered from ID_CON  | YES                                                           | NO                         |  |  |

| N                | Y                | N               | N                 | Powered from<br>VBAT | NO                                                            | YES                        |  |  |

| N                | Y                | N               | Υ                 | Powered from<br>VBAT | YES                                                           | YES                        |  |  |

| N                | Y                | Υ               | N                 |                      | ILLEGAL STATE                                                 |                            |  |  |

| N                | Y                | Y               | Υ                 |                      | ILLEGAL STATE                                                 |                            |  |  |

| Υ                | N                | N               | N                 | Powered from VBUS    | NO                                                            | YES                        |  |  |

| Y                | N                | N               | Υ                 | Powered from VBUS    | YES                                                           | YES                        |  |  |

| Y                | N                | Y               | N                 | Powered from VBUS    | NO                                                            | NO                         |  |  |

| Υ                | N                | Y               | Υ                 | Powered from VBUS    | YES                                                           | NO                         |  |  |

| Υ                | Y                | N               | N                 | Powered from<br>VBAT | NO                                                            | YES                        |  |  |

| Υ                | Y                | N               | Υ                 | Powered from<br>VBAT | YES                                                           | YES                        |  |  |

| Υ                | Y                | Υ               | N                 |                      | ILLEGAL S                                                     | STATE                      |  |  |

| Υ                | Y                | Υ               | Υ                 |                      | ILLEGAL S                                                     | STATE                      |  |  |

Copyright ©2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

11

### **Device Identification**

The RT8979 supports multiple accessories by detecting unique characteristics including VBUS voltage, ID resistance and USB data line status. These characteristics are shown in Table 2 to Table 3.

**Table 2. ADC Selection Table**

| ADC Value | ID_CON R | esistance to | Accessory Detected |                                                         | a.d               |  |

|-----------|----------|--------------|--------------------|---------------------------------------------------------|-------------------|--|

| ADC Value | Min.     | Тур.         | Max.               | Accessory Detector                                      | ea                |  |

| 00000     | 0.00     | 0.00         | 0.01               | USB OTG Mode                                            |                   |  |

| 00001     | 0.80     | 1.00         | 1.20               | MHL Cable                                               |                   |  |

| 00010     | 1.94     | 2.00         | 2.06               | Battery Charge Test (FM1)                               |                   |  |

| 00011     | 2.53     | 2.60         | 2.68               | Factory Mode Boot USB (FM2)                             |                   |  |

| 00100     | 3.12     | 3.21         | 3.30               | Force download with battery (FM3)                       |                   |  |

| 00101     | 3.90     | 4.01         | 4.13               | Factory Mode Boot UART (FM4)                            |                   |  |

| 00110     | 4.68     | 4.82         | 4.96               | For download without battery (FM5)                      |                   |  |

| 00111     | 5.85     | 6.03         | 6.21               | Battery Discharge Test (FM6)                            |                   |  |

| 01000     | 7.79     | 8.03         | 8.27               | RF Calibration (FM7)                                    | Factory Test Mode |  |

| 01001     | 9.73     | 10.03        | 10.33              | Phone-off Current Drain Test (FM8)                      |                   |  |

| 01010     | 11.67    | 12.03        | 12.39              | MHL BIST (FM9)                                          |                   |  |

| 01011     | 14.03    | 14.46        | 14.89              | RF calibration with Communication Processor (CP) (FM10) |                   |  |

| 01100     | 16.75    | 17.26        | 17.77              | Factory Mode Boot USB with CP (FM11)                    |                   |  |

| 01101     | 19.89    | 20.50        | 21.11              | Reserved Accessory 1                                    |                   |  |

| 01110     | 23.35    | 24.07        | 24.79              | Reserved Accessory 2                                    |                   |  |

| 01111     | 27.27    | 28.70        | 30.13              | Reserved Accessory 3                                    |                   |  |

| 10000     | 32.98    | 34.0         | 35.02              | Reserved Accessory 4                                    |                   |  |

| 10001     | 39.00    | 40.20        | 41.40              | Reserved Accessory 5                                    |                   |  |

| 10010     | 48.41    | 49.90        | 51.39              | Reserved Accessory 6                                    |                   |  |

| 10011     | 62.96    | 64.90        | 66.84              | Reserved Accessory 7                                    |                   |  |

| 10100     | 76.10    | 80.70        | 84.10              | Customer Accessory 1                                    |                   |  |

| 10101     | 98.94    | 102.00       | 105.10             | Customer Accessory 2                                    |                   |  |

| 10110     | 115.00   | 121.00       | 127.00             | Customer Accessory 3                                    |                   |  |

| 10111     | 143.00   | 150.00       | 157.00             | UART Cable                                              |                   |  |

| 11000     | 198.00   | 200.00       | 202.00             | Customer Accessory 4                                    |                   |  |

| 11001     | 247.30   | 255.00       | 262.70             | Reserved Accessory 10                                   |                   |  |

| 11010     | 291.90   | 301.00       | 310.10             | Reserved Accessory 11                                   |                   |  |

| 11011     | 347.00   | 365.00       | 383.00             | Customer Accessory 5                                    |                   |  |

| 11100     | 428.70   | 442.00       | 455.30             | ·                                                       |                   |  |

| 11101     | 600.40   | 619.00       | 637.60             | Reserved Accessory 12                                   |                   |  |

| 11110     | 750.00   | 1000.00      | 105.00             | Customer Accessory 7                                    |                   |  |

| 11111     | 6000.00  | Open         |                    | CDP, SDP, CDP                                           |                   |  |

Copyright ©2021 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

**Table 3. Automatic Accessory Configuration**

| Configuration Type | DP_CON | DM_CON | ID_CON | воот | JIG | CHG_DET |

|--------------------|--------|--------|--------|------|-----|---------|

| UART               | RxD    | TxD    | OPEN   | HI-Z | LOW | HI-Z    |

| USB                | DP1    | DM1    | ID BYP | HI-Z | LOW | HI-Z    |

| SDP                | DP1    | DM1    | ID BYP | HI-Z | LOW | LOW     |

| CDP                | DP1    | DM1    | ID BYP | HI-Z | LOW | HI-Z    |

| MHL                | MHL_D+ | MHL_D- | CBUS   | HI-Z | LOW | HI-Z    |

| DCP                | DP1    | DM1    | OPEN   | HI-Z | LOW | LOW     |

| Customer Accessory | OPEN   | OPEN   | OPEN   | HI-Z | LOW | HI-Z    |

| Reserved Accessory | OPEN   | OPEN   | OPEN   | HI-Z | LOW | HI-Z    |

### **Factory-Mode Accessories**

The RT8979 supports up to eleven different Factory Modes (FM). These modes are entered by detecting different R<sub>ID</sub> resistor values. The ID\_CON pin is also used to provide power in several modes by closing the VBAT MOSFET.

- FM1 Battery Charge Test → Tests charger & battery

- FM2 USB Test Boot → Tests the USB using AP

- FM3 Force-Download Mode with Battery → Enter AP force download mode with internal battery

- FM4 UART Test Boot ON → Tests the UART path

- FM5 Force-Download Mode without Battery → Enter AP force download mode without internal battery

- FM6 Battery Discharge Test → Tests the phone battery discharge

- FM7 RF Calibration → Tests the RF section of the phone using AP

- FM8 Phone-Off Current Drain Test → Tests the current drain when the phone is off

- FM9 MHL BIST→ Mobile High Definition Link Built-In Self-Test

- FM10 RF Calibration with CP → Tests the RF section of the phone using Baseband

- FM11 USB Test Boot with CP → Tests the USB path using Baseband

## Table 4. FM1 - Battery Charge Test

|          | JIGBOX          |          |        |          | RT8979   |           |        |        |      |      |        |

|----------|-----------------|----------|--------|----------|----------|-----------|--------|--------|------|------|--------|

| Sequence | ID_JIG          | VBUS_JIG | DM_JIG | DM_JIG   | VBUS     | ID_CON    | DP_CON | DM_CON | JIG  | воот | CHGDET |

| 1        | Floating        | 5V       | Open   | Open     | VBUS_JIG | Detection | Open   | Open   | LOW  | Hi-Z | Hi-Z   |

| 2        | $2k\Omega$      | 5V       | Open   | Open     | VBUS_JIG | OPEN      | DP1    | DM1    | LOW  | Hi-Z | Hi-Z   |

| 3        | VBAT            | 5V       | Open   | Open     | VBUS_JIG | VBAT      | DP1    | DM1    | LOW  | Hi-Z | Hi-Z   |

| 4        | Monitor Current |          |        | VBUS_JIG | VBAT     | DP1       | DM1    | LOW    | Hi-Z | Hi-Z |        |

| 5        | 2kΩ             | 5V       | Open   | Open     | VBUS_JIG | Detection | Open   | Open   | LOW  | Hi-Z | Hi-Z   |

### Table 5. FM2 - USB Test Boot

| Samuanaa | JIGBOX   |           |        |        | RT8979   |           |        |        |     |      |        |

|----------|----------|-----------|--------|--------|----------|-----------|--------|--------|-----|------|--------|

| Sequence | ID_JIG   | VBUS_JIG  | DM_JIG | DM_JIG | VBUS     | ID_CON    | DP_CON | DM_CON | JIG | воот | CHGDET |

| 1        | Floating | 5V        | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |

| 2        | 2.604kΩ  | 5V        | DP1    | DM1    | VBUS_JIG | OPEN      | DP1    | DM1    | LOW | Hi-Z | Hi-Z   |

| 3        | VBAT     | 5V        | DP1    | DM1    | VBUS_JIG | VBAT      | DP1    | DM1    | LOW | Hi-Z | Hi-Z   |

| 4        | Monito   | r Current | Test   | USB    | VBUS_JIG | VBAT      | DP1    | DM1    | LOW | Hi-Z | Hi-Z   |

| 5        | 2.604kΩ  | 5V        | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |

### Table 6. FM4 - UART Test Boot ON

| Commona  |          | JIGBO     | ΟX     |        | RT8979   |           |        |        |     |      |        |  |

|----------|----------|-----------|--------|--------|----------|-----------|--------|--------|-----|------|--------|--|

| Sequence | ID_JIG   | VBUS_JIG  | DM_JIG | DM_JIG | VBUS     | ID_CON    | DP_CON | DM_CON | JIG | воот | CHGDET |  |

| 1        | Floating | 5V        | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |  |

| 2        | 4.014kΩ  | 5V        | DP1    | DM1    | VBUS_JIG | OPEN      | RxD    | TxD    | LOW | Hi-Z | Hi-Z   |  |

| 3        | VBAT     | 5V        | DP1    | DM1    | VBUS_JIG | VBAT      | RxD    | TxD    | LOW | Hi-Z | Hi-Z   |  |

| 4        | Monito   | r Current | Test   | USB    | VBUS_JIG | VBAT      | RxD    | TxD    | LOW | Hi-Z | Hi-Z   |  |

| 5        | 4.014kΩ  | 5V        | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |  |

### Table 7. FM11 - USB Test Boot with CP

| Samuanaa |          | JIGBO     | ΟX     |        | RT8979   |           |        |        |     |      |        |  |

|----------|----------|-----------|--------|--------|----------|-----------|--------|--------|-----|------|--------|--|

| Sequence | ID_JIG   | VBUS_JIG  | DM_JIG | DM_JIG | VBUS     | ID_CON    | DP_CON | DM_CON | JIG | воот | CHGDET |  |

| 1        | Floating | 5V        | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |  |

| 2        | 17.26kΩ  | 5V        | DP2    | DM2    | VBUS_JIG | OPEN      | DP2    | DM2    | LOW | Hi-Z | Hi-Z   |  |

| 3        | VBAT     | 5V        | DP2    | DM2    | VBUS_JIG | VBAT      | DP2    | DM2    | LOW | Hi-Z | Hi-Z   |  |

| 4        | Monito   | r Current | Test   | USB    | VBUS_JIG | VBAT      | DP2    | DM2    | LOW | Hi-Z | Hi-Z   |  |

| 5        | 17.26kΩ  | 5V        | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |  |

Copyright ©2021 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

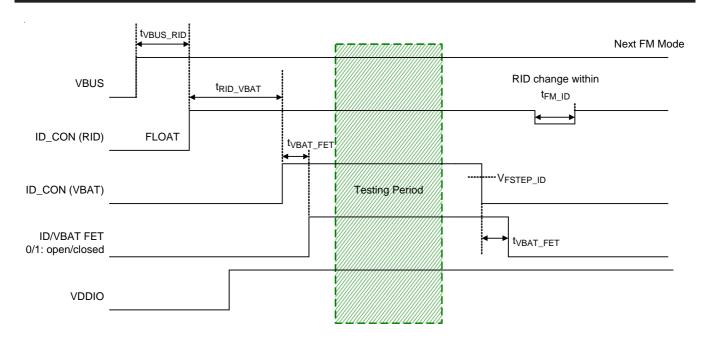

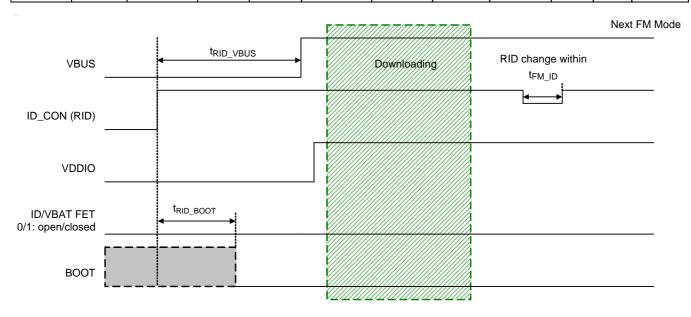

Figure 1. Timing for FM1/2/4/11

Table 8. FM3 - Force-Download Mode with Battery

| C        |                    | JIGBO    | ΟX     |        | RT8979   |           |        |        |     |      |        |  |

|----------|--------------------|----------|--------|--------|----------|-----------|--------|--------|-----|------|--------|--|

| Sequence | ID_JIG             | VBUS_JIG | DM_JIG | DM_JIG | VBUS     | ID_CON    | DP_CON | DM_CON | JIG | воот | CHGDET |  |

| 1        | Floating           | 0V       | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |  |

| 2        | $3.208$ k $\Omega$ | 0V       | DP1    | DM1    | VBUS_JIG | OPEN      | DP1    | DM1    | LOW | LOW  | Hi-Z   |  |

| 3        | $3.208$ k $\Omega$ | 5V       | DP1    | DM1    | VBUS_JIG | VBAT      | DP1    | DM1    | LOW | LOW  | Hi-Z   |  |

| 4        | Force Downloading  |          |        |        | VBUS_JIG | VBAT      | DP1    | DM1    | LOW | LOW  | Hi-Z   |  |

| 5        | $3.208$ k $\Omega$ | 5V       | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |  |

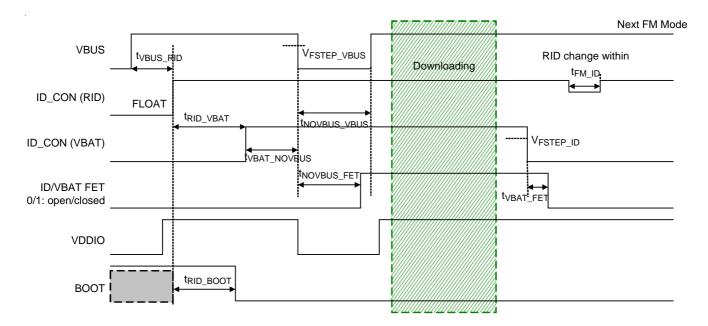

Figure 2. Timing for FM3

DS8979-00 May 2021

| Samuanaa |                   | JIGB     | ох     |        | RT8979   |           |        |        |     |      |        |  |

|----------|-------------------|----------|--------|--------|----------|-----------|--------|--------|-----|------|--------|--|

| Sequence | ID_JIG            | VBUS_JIG | DM_JIG | DM_JIG | VBUS     | ID_CON    | DP_CON | DM_CON | JIG | воот | CHGDET |  |

| 1        | Floating          | 5V       | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |  |

| 2        | $4.82$ k $\Omega$ | 5V       | DP1    | DM1    | VBUS_JIG | OPEN      | DP1    | DM1    | LOW | LOW  | Hi-Z   |  |

| 3        | VBAT              | 0V       | DP1    | DM1    | VBUS_JIG | VBAT      | DP1    | DM1    | LOW | LOW  | Hi-Z   |  |

| 4        | Force Downloading |          |        |        | VBUS_JIG | VBAT      | DP1    | DM1    | LOW | LOW  | Hi-Z   |  |

| 5        | 4.82kΩ            | 5V       | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |  |

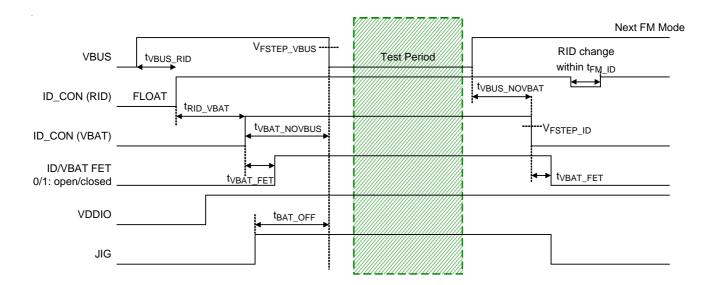

Figure 3. Timing for FM5

Copyright ©2021 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

Table 20. FM6 - Battery Discharge Test

|           | <del></del>     |          |        |        |          |           |        |        |      |      |        |  |

|-----------|-----------------|----------|--------|--------|----------|-----------|--------|--------|------|------|--------|--|

| Samuan aa | JIGBOX          |          |        |        | RT8979   |           |        |        |      |      |        |  |

| Sequence  | ID_JIG          | VBUS_JIG | DM_JIG | DM_JIG | VBUS     | ID_CON    | DP_CON | DM_CON | JIG  | воот | CHGDET |  |

| 1         | Floating        | 5V       | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW  | Hi-Z | Hi-Z   |  |

| 2         | 6.03kΩ          | 5V       | Open   | Open   | VBUS_JIG | OPEN      | Open   | Open   | HIGH | Hi-Z | Hi-Z   |  |

| 3         | VBAT            | 0V       | Open   | Open   | VBUS_JIG | VBAT      | Open   | Open   | HIGH | Hi-Z | Hi-Z   |  |

| 4         | Monitor Current |          |        |        | VBUS_JIG | VBAT      | Open   | Open   | HIGH | Hi-Z | Hi-Z   |  |

| 5         | 6.03kΩ          | 5V       | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW  | Hi-Z | Hi-Z   |  |

Figure 4. Timing for FM6

| Table 21. FM7 | ·RF | Calibration |

|---------------|-----|-------------|

|---------------|-----|-------------|

| Samuenaa |                | JIGB     | ОХ     |        | RT8979   |           |        |        |     |      |        |  |

|----------|----------------|----------|--------|--------|----------|-----------|--------|--------|-----|------|--------|--|

| Sequence | ID_JIG         | VBUS_JIG | DM_JIG | DM_JIG | VBUS     | ID_CON    | DP_CON | DM_CON | JIG | воот | CHGDET |  |

| 1        | Floating       | 5V       | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |  |

| 2        | 8.03kΩ         | 5V       | DP1    | DM1    | VBUS_JIG | OPEN      | DP1    | DM1    | LOW | Hi-Z | Hi-Z   |  |

| 3        | JIG_VBAT       | 0V       | DP1    | DM1    | VBUS_JIG | JIG_VBAT  | DP1    | DM1    | LOW | Hi-Z | Hi-Z   |  |

| 4        | RF Calibration |          |        |        | VBUS_JIG | JIG_VBAT  | DP1    | DM1    | LOW | Hi-Z | Hi-Z   |  |

| 5        | 8.03kΩ         | 5V       | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |  |

Table 22. FM10 - RF Calibration with CP

| Camuanaa |                | JIGB     | ох     |        | RT8979   |           |        |        |     |      |        |  |

|----------|----------------|----------|--------|--------|----------|-----------|--------|--------|-----|------|--------|--|

| Sequence | ID_JIG         | VBUS_JIG | DM_JIG | DM_JIG | VBUS     | ID_CON    | DP_CON | DM_CON | JIG | воот | CHGDET |  |

| 1        | Floating       | 5V       | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |  |

| 2        | 14.46kW        | 5V       | DP2    | DM2    | VBUS_JIG | OPEN      | DP2    | DM2    | LOW | Hi-Z | Hi-Z   |  |

| 3        | JIG_VBAT       | 0V       | DP2    | DM2    | VBUS_JIG | JIG_VBAT  | DP2    | DM2    | LOW | Hi-Z | Hi-Z   |  |

| 4        | RF Calibration |          |        |        | VBUS_JIG | JIG_VBAT  | DP2    | DM2    | LOW | Hi-Z | Hi-Z   |  |

| 5        | 14.46kΩ        | 5V       | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |  |

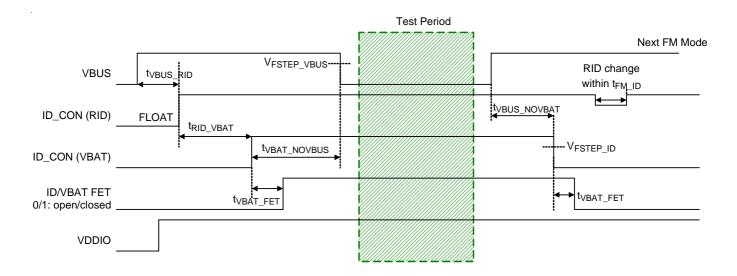

Figure 5. Timing for FM7/10

Table 23. FM8 - Phone-Off Current Drain Test

| Samuanaa |                 | JIGB     | ох     |        | RT8979   |           |        |        |      |      |        |  |

|----------|-----------------|----------|--------|--------|----------|-----------|--------|--------|------|------|--------|--|

| Sequence | ID_JIG          | VBUS_JIG | DM_JIG | DM_JIG | VBUS     | ID_CON    | DP_CON | DM_CON | JIG  | воот | CHGDET |  |

| 1        | Floating        | 5V       | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW  | Hi-Z | Hi-Z   |  |

| 2        | 10.03kΩ         | 5V       | Open   | Open   | VBUS_JIG | OPEN      | Open   | Open   | HIGH | Hi-Z | Hi-Z   |  |

| 3        | VBAT            | 0V       | Open   | Open   | VBUS_JIG | VBAT      | Open   | Open   | HIGH | Hi-Z | Hi-Z   |  |

| 4        | Monitor Current |          |        |        | VBUS_JIG | VBAT      | Open   | Open   | HIGH | Hi-Z | Hi-Z   |  |

| 5        | 10.03kΩ         | 5V       | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW  | Hi-Z | Hi-Z   |  |

Figure 6. Timing for FM8

Table 24. FM9 - MHL BIST

| Samuanaa |                 | JIGB     | ОХ     |        | RT8979   |           |        |        |     |      |        |  |

|----------|-----------------|----------|--------|--------|----------|-----------|--------|--------|-----|------|--------|--|

| Sequence | ID_JIG          | VBUS_JIG | DM_JIG | DM_JIG | VBUS     | ID_CON    | DP_CON | DM_CON | JIG | воот | CHGDET |  |

| 1        | Floating        | 5V       | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |  |

| 2        | 12.03kΩ         | 5V       | MHL_D+ | MHL_D- | VBUS_JIG | Detection | MHL_D+ | MHL_D- | LOW | Hi-Z | Hi-Z   |  |

| 3        | 12.03kΩ         | 5V       | MHL_D+ | MHL_D- | VBUS_JIG | Detection | MHL_D+ | MHL_D- | LOW | Hi-Z | Hi-Z   |  |

| 4        | Monitor Current |          |        |        | VBUS_JIG | Detection | MHL_D+ | MHL_D- | LOW | Hi-Z | Hi-Z   |  |

| 5        | 12.03kΩ         | 5V       | Open   | Open   | VBUS_JIG | Detection | Open   | Open   | LOW | Hi-Z | Hi-Z   |  |

Figure 7. Timing for FM9

## **Register Table**

(Slave address = 0100101x = 0x25)

| Name           | Address | Description                              |

|----------------|---------|------------------------------------------|

| Device ID      | 0x01    | Device ID                                |

| MUIC Control 1 | 0x02    | MUIC control 1                           |

| Interrupt      | 0x03    | MUIC Interrupt                           |

| Interrupt mask | 0x04    | MUIC Interrupt mask                      |

| ADC            | 0x05    | ADC value (real ADC)                     |

| Timing Set 1   | 0x06    | MUIC Timing setting 1                    |

| Detach Control | 0x07    | Detach status                            |

| Device Type 1  | 0x08    | Device type list 1 of ID & BCD detection |

| Device Type 2  | 0x09    | Device type list 2 of ID & BCD detection |

| Device Type 3  | 0x0A    | Device type list 3 of ID & BCD detection |

| Manual S/W 1   | 0x0B    | Manually switching control 1             |

| Manual S/W 2   | 0x0C    | Manually switching control 2             |

| Timing Set 2   | 0x0D    | MUIC Timing setting 2                    |

| MUIC Control 2 | 0x0E    | DCD timeout control                      |

| Device Type 4  | 0x0F    | Device Type 4                            |

| MUIC Control 3 | 0x10    | MUIC control 3                           |

| MUIC Control 4 | 0x11    | MUIC control 4                           |

| MUIC Status 1  | 0x12    | MUIC status 1                            |

| MUIC Status 2  | 0x13    | MUIC status 2                            |

| Stable ADC     | 0x18    | ADC Value (stable ADC)                   |

| Reset          | 0x19    | Reset                                    |

21

| Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Name             | Bit7                      | Bit6                                                              | Bit5                              | Bit4           | Bit3                       | Bit2            | Bit1          | Bit0     |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------|-------------------------------------------------------------------|-----------------------------------|----------------|----------------------------|-----------------|---------------|----------|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Device ID        |                           |                                                                   | REVISION_                         | ID             |                            | VENDOR_ID       |               |          |  |  |

| 0x01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Reset Value      | 0                         | 0                                                                 | 0                                 | 1              | 0                          | 0               | 0             | 1        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Read/Write       | R                         | R                                                                 | R                                 | R              | R                          | R               | R             | R        |  |  |

| REV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ISION_ID         | 00010 for 2               | <sup>nd</sup> revision                                            |                                   |                |                            |                 |               |          |  |  |

| VEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | IDOR_ID          | 001 : RichT               | ek                                                                |                                   |                |                            |                 |               |          |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MUIC<br>Control1 | Reserved                  | Reserved                                                          | Reserved                          | SW OPEN        | RAW Data                   | Manual SW       | Wait          | INT_MASK |  |  |

| 0x02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Reset Value      | 0                         | 0                                                                 | 0                                 | 1              | 1                          | 1               | 1             | 1        |  |  |