# 36V, 2μA I<sub>O</sub>, 100mA Low Dropout Voltage Linear Regulator

## **General Description**

The RT2560Q is a high voltage linear regulator offering the benefits of high input voltage, low dropout voltage, low quiescent current and low external components.

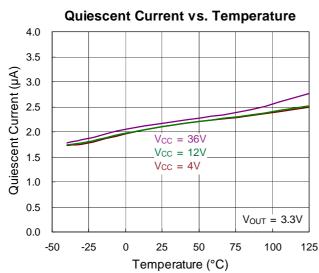

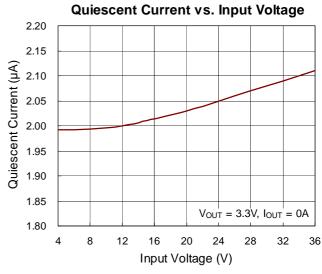

The feature of low quiescent current as low as 2µA is ideal for powering the battery equipment to a longer service life. The RT2560Q is stable with the ceramic output capacitor over its wide input range from 3.5V to 36V and the entire range of output load current (0mA to 100mA).

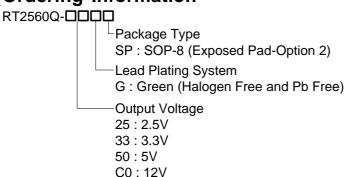

### Ordering Information

Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

## **Marking Information**

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

### **Features**

- AEC-Q100 Grade3 Certification

- 2μA Quiescent Current

- ±2% Output Accuracy

- 100mA Output Current

- 3.5V to 36V Input Voltage Range

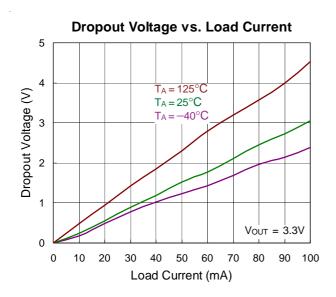

- Dropout Voltage: 0.55V at 10mA

- Fixed Output Voltage: 2.5V, 3.3V, 5V, 12V

- Stable with Ceramic or Tantalum Capacitor

- Current Limit Protection

- Over-Temperature Protection

- SOP-8 (Exposed Pad) Package

- RoHS Compliant and Halogen Free

### **Applications**

- Portable, Battery Powered Equipment

- Ultra Low Power Microcontrollers

- Notebook Computers

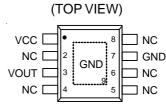

### **Pin Configurations**

SOP-8 (Exposed Pad)

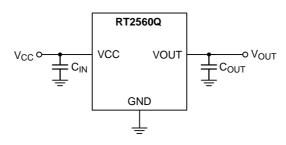

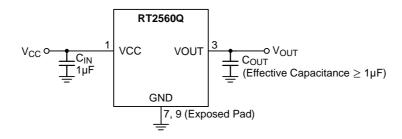

## Simplified Application Circuit

### **Functional Pin Description**

| Pin No.            | Pin Name | Pin Function                                                                                                |  |  |

|--------------------|----------|-------------------------------------------------------------------------------------------------------------|--|--|

| 1                  | VCC      | Supply Voltage Input.                                                                                       |  |  |

| 2, 4, 5, 6, 8      | NC       | No Internal Connection.                                                                                     |  |  |

| 3                  | VOUT     | Regulator Output.                                                                                           |  |  |

| 7, 9 (Exposed Pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation. |  |  |

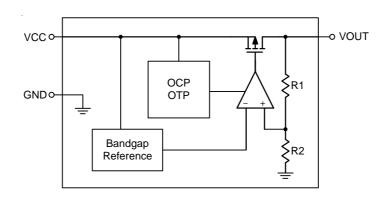

### **Function Block Diagram**

## **Operation**

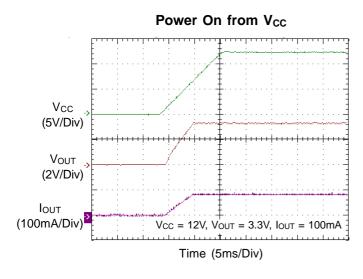

The RT2560Q is a high input voltage linear regulator designed specially for low external components system. The input voltage range is from 3.5V to 36V.

The minimum required output capacitance for stable operation is  $1\mu F$  effective capacitance after consideration of the temperature and voltage coefficient of the capacitor.

#### **Output Transistor**

The RT2560Q builds in a P-MOSFET output transistor which provides a low switch-on resistance for low dropout voltage applications.

### **Error Amplifier**

The Error Amplifier compares the internal reference voltage with the output feedback voltage from the internal divider, and controls the Gate voltage of P-MOSFET to support good line regulation and load regulation at output voltage.

#### **Current Limit**

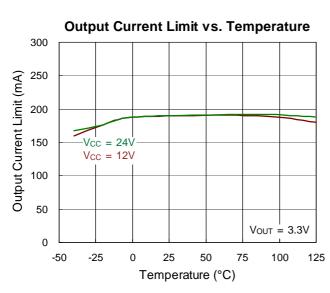

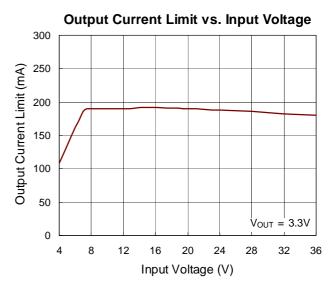

The RT2560Q provides current limit function to prevent the device from damages during over-load or short-circuit condition. This current is detected by an internal sensing transistor.

#### **Over-Temperature Protection**

The over-temperature protection function will turn off the P-MOSFET when the junction temperature exceeds 150°C (typ.). Once the junction temperature cools down by approximately 20°C, the regulator will automatically resume operation.

# Absolute Maximum Ratings (Note 1)

| • VCC to GND                                                                | 0.3V to 40V      |

|-----------------------------------------------------------------------------|------------------|

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                  |

| SOP-8 (Exposed Pad)                                                         | - 2.041W         |

| Package Thermal Resistance (Note 2)                                         |                  |

| SOP-8 (Exposed Pad), $\theta_{JA}$                                          | - 49°C/W         |

| SOP-8 (Exposed Pad), $\theta_{JC}$                                          | - 8°C/W          |

| • Lead Temperature (Soldering, 10 sec.)                                     | - 260°C          |

| • Junction Temperature                                                      | - 150°C          |

| Storage Temperature Range                                                   | - −65°C to 150°C |

| ESD Susceptibility (Note 3)                                                 |                  |

| HBM (Human Body Model)                                                      | - 2kV            |

| Recommended Operating Conditions (Note 4)                                   |                  |

| Supply Input Voltage, VCC                                                   | - 3.5V to 36V    |

Junction Temperature Range ------ -40°C to 125°C

Ambient Temperature Range ----- -40°C to 85°C

### **Electrical Characteristics**

((Vout + 1V) < Vcc < 36V,  $T_A = -40^{\circ}C$  to 85°C, unless otherwise specified.)

| Parameter             | Symbol            | Test Conditions                                           |                         | Min   | Тур  | Max   | Unit |

|-----------------------|-------------------|-----------------------------------------------------------|-------------------------|-------|------|-------|------|

| DC Output Voltage     | Vout              | I <sub>OUT</sub> = 10mA                                   | V <sub>OUT</sub> = 3.3V | 3.234 |      | 3.366 | V    |

|                       |                   |                                                           | V <sub>OUT</sub> = 2.5V | 2.45  |      | 2.55  |      |

|                       |                   |                                                           | V <sub>OUT</sub> = 5V   | 4.9   |      | 5.1   |      |

|                       |                   |                                                           | V <sub>OUT</sub> = 12V  | 11.79 | -    | 12.24 |      |

| Dropout Voltage       | V <sub>DROP</sub> | I <sub>OUT</sub> = 10mA                                   |                         |       | 0.32 | 0.55  | V    |

|                       |                   | I <sub>OUT</sub> = 0mA, V <sub>CC</sub> = 12V             | V <sub>OUT</sub> = 3.3V |       | 2    | 3.5   | μА   |

| VCC Quipagent Current | la                |                                                           | V <sub>OUT</sub> = 2.5V |       |      |       |      |

| VCC Quiescent Current | IQ                |                                                           | V <sub>OUT</sub> = 5V   |       |      |       |      |

|                       |                   | $I_{OUT} = 0$ mA, $V_{CC} = 24$ V                         | V <sub>OUT</sub> = 12V  |       | 3.5  | 5     |      |

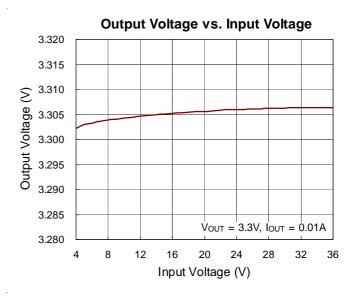

| Line Regulation       | $\Delta V_{LINE}$ | I <sub>OUT</sub> = 10mA                                   |                         | 0.04  | 0.5  | %     |      |

| Load Regulation       | $\Delta V_{LOAD}$ | 0mA < I <sub>OUT</sub> < 50mA,<br>V <sub>CC</sub> = 12V   | $V_{OUT} = 3.3V$        | -0.5  |      | 0.5   | %    |

|                       |                   |                                                           | V <sub>OUT</sub> = 2.5V |       |      |       |      |

|                       |                   |                                                           | V <sub>OUT</sub> = 5V   |       |      |       |      |

|                       |                   | $0mA < I_{OUT} < 50mA,$<br>$V_{CC} = 24V$                 | V <sub>OUT</sub> = 12V  |       |      |       |      |

| Output Current Limit  | I <sub>LIM</sub>  | Vout = 0.5 x Vout(normal),<br>Vcc = 12V                   | V <sub>OUT</sub> = 3.3V | 115   | 175  | 300   | mA   |

|                       |                   |                                                           | V <sub>OUT</sub> = 2.5V |       |      |       |      |

|                       |                   | 100 121                                                   | V <sub>OUT</sub> = 5V   |       |      |       |      |

|                       |                   | $V_{OUT} = 0.5 \times V_{OUT(normal)},$<br>$V_{CC} = 24V$ | V <sub>OUT</sub> = 12V  |       |      |       |      |

| Parameter                                           | Symbol          | Test Conditions         | Min | Тур | Max | Unit |

|-----------------------------------------------------|-----------------|-------------------------|-----|-----|-----|------|

| Thermal Shutdown Temperature (Junction Temperature) | T <sub>SD</sub> | I <sub>OUT</sub> = 30mA |     | 150 |     | °C   |

| Thermal Shutdown<br>Hysteresis                      | $\Delta T_{SD}$ |                         |     | 20  | !   | °C   |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package. The PCB copper area with exposed pad is 70mm<sup>2</sup>.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

## **Typical Application Circuit**

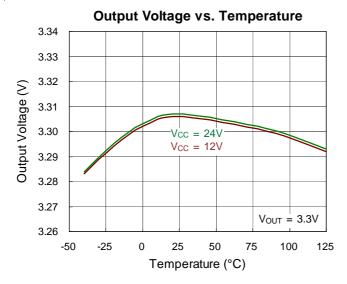

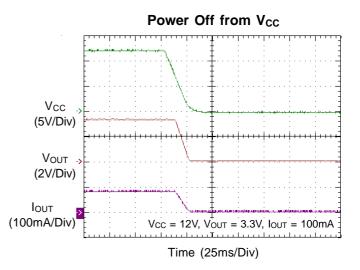

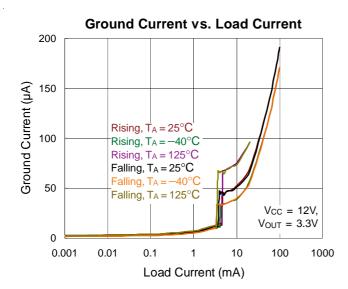

## **Typical Operating Characteristics**

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS2560Q-01 February 2016

### **Application Information**

#### **Capacitor Selection**

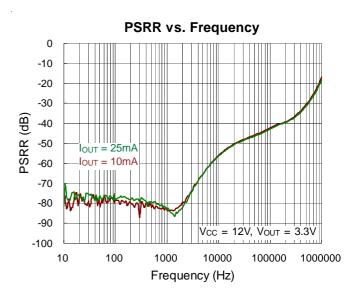

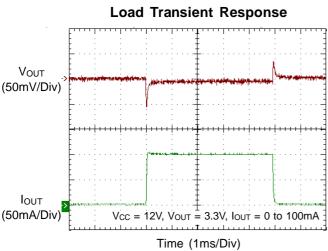

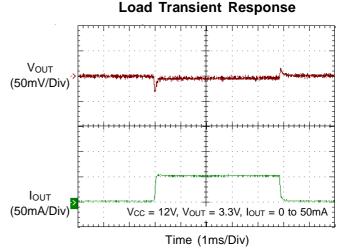

Like any low dropout linear regulator, the RT2560Q's external input and output capacitors must be properly selected for stability and performance. Use a 1µF or larger input capacitor and place it close to the IC's VCC and GND pins. Any output capacitor met the minimum  $1m\Omega$ ESR (Equivalent Series Resistance) and effective capacitance larger than 1µF requirement may be used. Place the output capacitor close to the IC's VOUT and GND pins. Increasing capacitance and decreasing ESR can improve the circuit's PSRR and line transient response.

### **Over-Temperature Protection**

Thermal protection limits power dissipation to prevent IC overheat. When the operation junction temperature exceeds 150°C, the over-temperature protection circuit starts the thermal shutdown function and turns the regulator off. The regulator turns on again after the junction temperature cools down by 20°C.

#### **Power Dissipation**

For continuous operation, do not exceed absolute maximum operation junction temperature 125°C. The power dissipation definition in device is:

$$P_D = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{IN} \times I_Q$$

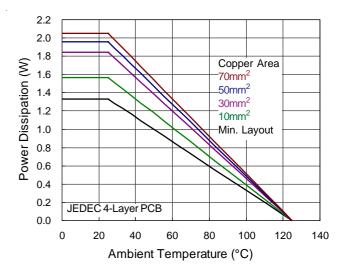

The maximum power dissipation depends on the thermal resistance of IC package, PCB layout, the rate of surroundings airflow and temperature difference between junctions to ambient. The maximum power dissipation can be calculated by following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

Where  $T_{J(MAX)}$  is the maximum operation junction temperature,  $T_A$  is the ambient temperature and the  $\theta_{JA}$  is the junction to ambient thermal resistance.

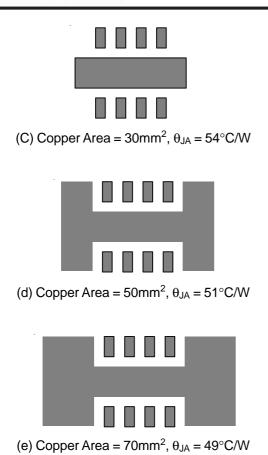

For recommended operating conditions specification, the maximum junction temperature is 125°C. The junction to ambient thermal resistance for SOP-8 (Exposed Pad) package is 75°C/W on the standard JEDEC 51-7 (4 layers, 2S2P) thermal test board. The copper thickness is 2oz. The maximum power dissipation at  $T_A = 25^{\circ}C$  can be calculated by following formula:

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (75^{\circ}C/W) = 1.33W$ (SOP-8 Exposed Pad on the minimum layout)

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (49^{\circ}C/W) = 2.04W$ (SOP-8 Exposed Pad on the 70mm<sup>2</sup> copper area layout)

#### **Layout Considerations**

The thermal resistance  $\theta_{JA}$  of SOP-8 (Exposed Pad) is determined by the package design and the PCB design. However, the package design had been designed. If possible, it's useful to increase thermal performance by the PCB design. The thermal resistance  $\theta_{JA}$  can be decreased by adding a copper under the exposed pad of SOP-8 (Exposed Pad) package.

As shown in Figure 1, the amount of copper area to which the SOP-8 (Exposed Pad) is mounted affects thermal performance. When mounted to the standard SOP-8 (Exposed Pad) pad (Figure 1.a), θ<sub>JA</sub> is 75°C/W. Adding copper area of pad under the SOP-8 (Exposed Pad) (Figure 1.b) reduces the  $\theta_{JA}$  to 64°C/W. Even further, increasing the copper area of pad to 70mm<sup>2</sup> (Figure 1.e) reduces the  $\theta_{JA}$  to 49°C/W.

(a) Copper Area =  $(2.3 \times 2.3) \text{ mm}^2$ ,  $\theta_{JA} = 75^{\circ}\text{C/W}$

(b) Copper Area =  $10\text{mm}^2$ ,  $\theta_{JA} = 64^{\circ}\text{C/W}$

Figure 1. Thermal Resistance vs. Copper Area Layout Thermal Design

The maximum power dissipation depends on operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance  $\theta_{JA}$ . The Figure 2 of derating curves allows the designer to see the effect of rising ambient temperature on the maximum power allowed.

Figure 2. Derating Curve for Package

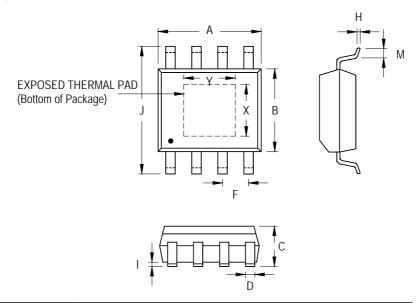

### **Outline Dimension**

| Symbol   |   | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|----------|---|--------------|---------------|----------------------|-------|--|

|          |   | Min          | Max           | Min                  | Max   |  |

| Α        |   | 4.801        | 5.004         | 0.189                | 0.197 |  |

| В        |   | 3.810        | 4.000         | 0.150                | 0.157 |  |

| С        |   | 1.346        | 1.753         | 0.053                | 0.069 |  |

| D        |   | 0.330        | 0.510         | 0.013                | 0.020 |  |

| F        |   | 1.194        | 1.194 1.346   |                      | 0.053 |  |

| Н        |   | 0.170        | 0.254         | 0.007                | 0.010 |  |

| I        |   | 0.000        | 0.152         | 0.000                | 0.006 |  |

| J        |   | 5.791        | 6.200         | 0.228                | 0.244 |  |

| М        |   | 0.406        | 1.270         | 0.016                | 0.050 |  |

| Ontion 1 | Х | 2.000        | 2.300         | 0.079                | 0.091 |  |

| Option 1 | Υ | 2.000        | 2.300         | 0.079                | 0.091 |  |

| Option 2 | Х | 2.100        | 2.500         | 0.083                | 0.098 |  |

| Option 2 | Υ | 3.000        | 3.500         | 0.118                | 0.138 |  |

8-Lead SOP (Exposed Pad) Plastic Package

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

www.richtek.com DS2560Q-01 February 2016

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Richtek(台湾立锜)