# Ideal Diode Controller with Reverse-Current Protection

### **FEATURES**

- Qualified for Automotive Applications

- AEC-Q100 Qualified with the Following Results:

- Device Temperature Grade 1: -40°C to 125°C

Ambient Operating Temperature Range

- Device CDM ESD Classification Level C3B

- 4.8V to 65V Operating Range

- –65V Reverse voltage rating

- Charge pump for external N-Channel MOSFET

- 20mV ANODE to CATHODE forward voltage drop regulation

- 12V Gate Drive Voltage

- With Enable Input

- Drive High Side External N-Channel MOSFET

- 1µA Shutdown current (EN=Low)

- 60µA Operating quiescent current (EN=High)

- 2.3-A Peak gate turnoff current

- Fast reverse current turn-off within 0.75us

- Meets automotive ISO7637 transient requirements with a suitable TVS Diode

- Available in an SOT23-6L Package

### APPLICATIONS

- Automotive Battery Protection

- Redundant Power Supplies

- Industrial Factory Automation

- Enterprise Power Supplies

- Network Telecom Power Systems

- Servers

# **DESCRIPTION**

The SCT53600Q is an ideal diode controller which paired with an external N-channel MOSFET as an ideal diode rectifier for low loss reverse polarity protection to replace a Schottky Diode. The SCT53600Q operates over a wide supply voltage range of 4.8V to 65V. The device can withstand and protect the load against damaging from negative supply voltages down to -65 V and blocks reverse current flow helping to simplify the system designs for automotive ISO7637 protection.

The SCT53600Q controller provides a charge pump gate drive for an external N-channel MOSFET. The device regulates the forward voltage drop across the external MOSFET to 20mV allowing smooth, ring-free operation with providing very fast turn-off(< 0.75  $\mu s$ ) of the MOSFET during a reverse event to minimize reverse current if power source fails or input microshort conditions. The fast response to Reverse Current Blocking makes the device suitable for systems with output voltage holdup requirements during ISO7637 pulse testing.

The SCT53600Q consumes only  $1\mu A$  of current during shutdown mode with the enable pin low to extend battery life. The device is available in an SOT23-6 package.

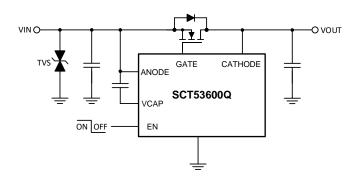

### TYPICAL APPLICATION

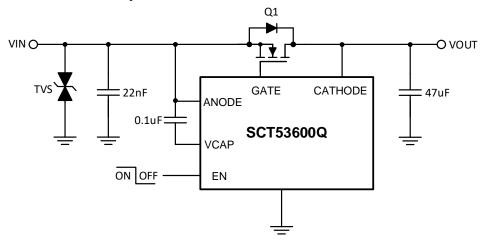

**Typical Application**

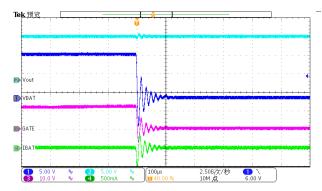

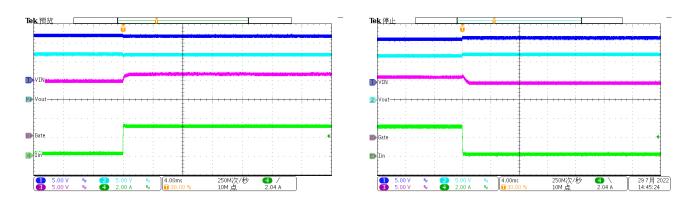

**Reverse Current Blocking**

For more information <a href="www.silicontent.com">www.silicontent.com</a> © 2023 Silicon Content Technology Co., Ltd. All Rights Reserved

### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Revision 1.0: Released to Production.

Revision 1.1: Update IQ\_Charge On MAX and MIN.

Revision 1.2: Modify part number.

Revision 1.3: Update packaging information

Revision 1.4: Update Device Order Information

Revision 1.5: Update Device Order Information

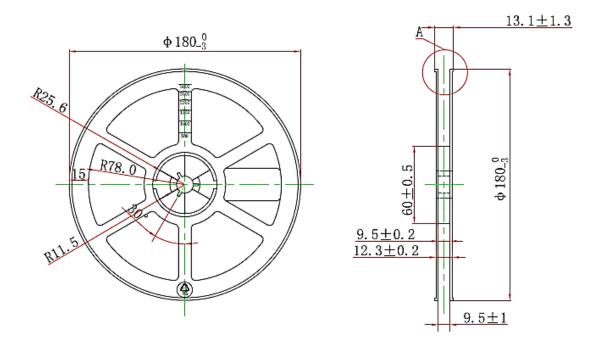

# **DEVICE ORDER INFORMATION**

| ORDERABLE     | PACKAGING   | STANDARD | PACKAGE | PINS | PACKAGE     |

|---------------|-------------|----------|---------|------|-------------|

| DEVICE        | TYPE        | PACK QTY | MARKING |      | DESCRIPTION |

| SCT53600QTVDR | Tape & Reel | 3000     | 3600    | 6    | SOT23-6L    |

### ABSOLUTE MAXIMUM RATINGS

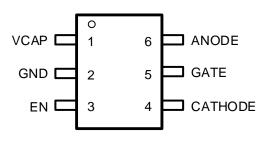

# **PIN CONFIGURATION**

Over operating free-air temperature unless otherwise noted<sup>(1)</sup>

| DESCRIPTION                                      | MIN                  | MAX                      | UNIT |

|--------------------------------------------------|----------------------|--------------------------|------|

| ANODE to GND                                     | -65                  | 65                       | V    |

| EN to GND, $V_{(ANODE)} > 0 V$                   | -0.3                 | 72                       | V    |

| EN to GND, $V_{(ANODE)} \le 0 \text{ V}$         | V <sub>(ANODE)</sub> | 65+ V <sub>(ANODE)</sub> | V    |

| GATE to ANODE                                    | -0.3                 | 15                       | V    |

| VCAP to ANODE                                    | -0.3                 | 15                       | V    |

| CATHODE to ANODE                                 | -5                   | 75                       | V    |

| Operating junction temperature TJ <sup>(2)</sup> | -40                  | 150                      | °C   |

| Storage temperature TSTG                         | -65                  | 150                      | °C   |

Figure 1. 6-Lead Plastic SOT23-6L

# **PIN FUNCTIONS**

| NAME    | NO. | PIN FUNCTION                                                                                                                                               |

|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCAP    | 1   | Charge pump output. Connect a charge pump capacitor typically 0.1uF between VCAP and ANODE.                                                                |

| GND     | 2   | Ground.                                                                                                                                                    |

| EN      | 3   | Enable pin. Drive EN low to make the device in shutdown mode. Can be connected to ANODE for always ON operation.                                           |

| CATHODE | 4   | Cathode of the diode. Connect to the drain of the external N-channel MOSFET.                                                                               |

| GATE    | 5   | Gate drive output. Connect to the gate of the external n-channel MOSFET. GATE shorts to ANODE during reverse-current conditions and when EN is forced low. |

| ANODE   | 6   | Anode of the diode and input power. Connect to the source of the external N-channel MOSFET.                                                                |

For more information www.silicontent.com © 2023 Silicon Content Technology Co., Ltd. All Rights Reserved

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause device permanent damage. The device is not guaranteed to function outside of its Recommended Operation Conditions.

<sup>(2)</sup> The IC includes over temperature protection to protect the device during overload conditions. Junction temperature will exceed 150°C when over temperature protection is active. Continuous operation above the specified maximum operating junction temperature will reduce lifetime.

### RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range unless otherwise noted

| PARAMETER            | DEFINITION                     | MIN | MAX | UNIT |

|----------------------|--------------------------------|-----|-----|------|

| V(ANODE)             | ANODE to GND                   | -60 | 60  | V    |

| V(CATHODE)           | CATHODE to GND                 |     | 60  | V    |

| V <sub>EN</sub>      | EN to GND                      | -60 | 60  | V    |

| V(ANODE) -V(CATHODE) | ANODE to CATHODE               | -70 |     | V    |

| TJ                   | Operating junction temperature | -40 | 150 | °C   |

### **ESD RATINGS**

| PARAMETER        | DEFINITION                                                                                   | MIN | МАХ | UNIT |

|------------------|----------------------------------------------------------------------------------------------|-----|-----|------|

| V                | Human Body Model(HBM), per ANSI-JEDEC-JS-001-2014 specification, all pins <sup>(1)</sup>     | -3  | 3   | kV   |

| V <sub>ESD</sub> | Charged Device Model(CDM), per ANSI-JEDEC-JS-002-2014 specification, all pins <sup>(2)</sup> | -1  | +1  | kV   |

- (1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

### THERMAL INFORMATION

| PARAMETER       | THERMAL METRIC                                          | SOT23-6L | UNIT |

|-----------------|---------------------------------------------------------|----------|------|

| $\theta_{ja}$   | Junction-to-ambient thermal resistance (standard board) | 102      | °C/W |

| $	heta_{jctop}$ | Junction-to-case (top) thermal resistance               | 36.9     | C/VV |

<sup>(1)</sup> SCT provides  $R_{\theta JA}$  and  $R_{\theta JC}$  numbers only as reference to estimate junction temperatures of the devices.  $R_{\theta JA}$  and  $R_{\theta JC}$  are not a characteristic of package itself, but of many other system level characteristics such as the design and layout of the printed circuit board (PCB) on which the SCT2601 is mounted, thermal pad size, and external environmental factors. The PCB board is a heat sink that is soldered to the leads and thermal pad of the SCT2600. Changing the design or configuration of the PCB board changes the efficiency of the heat sink and therefore the actual  $R_{\theta JA}$  and  $R_{\theta JC}$ .

### **ELECTRICAL CHARACTERISTICS**

T<sub>J</sub>=-40°C~125°C, typical value is tested under 25°C.

| SYMBOL                   | PARAMETER                    | TEST CONDITION         | MIN  | TYP | MAX  | UNIT |

|--------------------------|------------------------------|------------------------|------|-----|------|------|

| SUPPLY VOLT              | AGE                          |                        |      |     |      |      |

| V(ANODE)                 | Operating input voltage      |                        | 4.8  |     | 60   | V    |

| V <sub>(ANODE POR)</sub> | VANODE POR Rising threshold  |                        |      | 4.3 | 4.75 | V    |

| (ANODE FOR)              | VANODE POR Falling threshold |                        |      | 3.7 |      | V    |

| I <sub>SHDN</sub>        | Shutdown current             | V <sub>EN</sub> = 0V   |      | 0.3 | 1.5  | μΑ   |

| IQ_Charge Off            | Quiescent current            | Vcap-ANODE=14V         |      | 60  | 130  | uA   |

| Q_Charge On              | Quiescent current            | Vcap-ANODE Floating    | 180  | 285 | 650  | uA   |

| ENABLE                   |                              |                        |      |     |      |      |

| V <sub>EN_</sub> H       | Enable input high threshold  |                        | 2.15 |     |      | V    |

| V <sub>EN_L</sub>        | Enable input low threshold   |                        | 1.48 |     | V    |      |

| V <sub>EN_HYS</sub>      | Enable Hysteresis            |                        | 0.65 |     | V    |      |

| I <sub>EN</sub>          | Enable sink current          | V <sub>EN</sub> = 12 V | 1.5  |     | uA   |      |

| VANODE to VCATHO                | ODE                                                                 |                                                        |      |      |      |      |

|---------------------------------|---------------------------------------------------------------------|--------------------------------------------------------|------|------|------|------|

| V <sub>AC_REG</sub> Regulated F | Pogulated Forward Throshold                                         | TJ=25℃                                                 | 11   | 20   | 29   | mV   |

|                                 | Regulated Forward Threshold                                         | TJ=40~125°C                                            | 7    |      | 36   |      |

| V <sub>AC</sub>                 | threshold for full conduction mode                                  |                                                        |      | 50   |      | mV   |

| Vac_rev                         | threshold for reverse current blocking                              | TJ=40~125℃                                             | -30  | -11  | -1   | mV   |

| Gm                              | Regulation Error AMP Transconductance*                              |                                                        |      | 1800 |      | μΑ/\ |

| GATE DRIVE                      |                                                                     |                                                        |      |      |      |      |

|                                 | Peak source current                                                 | Vanode – Vcathode = 100 mV,<br>VGATE) – Vanode = 5 V   |      | 7    |      | mA   |

| I <sub>GATE</sub>               | Peak sink current*                                                  | Vanode – Vcathode = –20 mV,<br>Vgate – Vanode = 5 V    |      | 2370 |      | mA   |

|                                 | Regulation max sink current                                         | Vanode – Vcathode = 0 V,<br>Vgate – Vanode = 5 V       |      | 12   |      | uA   |

| RDSON                           | discharge switch R <sub>DSON</sub>                                  | Vanode – Vcathode = –20 mV,<br>Vgate – Vanode = 100 mV |      | 0.8  | 1.5  | Ω    |

| CHARGE PUMP                     |                                                                     |                                                        |      |      |      |      |

| I <sub>VCAP</sub>               | Charge Pump source current (Charge pump on)                         | VVCAP - VANODE = 7 V                                   |      | 160  |      | μA   |

| TVCAP                           | Charge Pump sink current (Charge pump off)                          | V <sub>VCAP</sub> - V <sub>ANODE</sub> = 14 V          |      | 20   |      | μΑ   |

| Vvcap–Vanode                    | Charge pump voltage at V <sub>ANODE</sub> = 4.8V                    | I <sub>VCAP</sub> ≤ 30 μA                              | 8    | 11.8 |      | V    |

|                                 | Charge pump turn on voltage                                         |                                                        |      | 11.7 |      | V    |

| V VCAP— V ANODE                 | Charge pump turn off voltage                                        |                                                        |      | 12.8 |      | V    |

|                                 | Charge Pump Enable comparator<br>Hysteresis                         |                                                        |      | 1.1  |      | V    |

| Vvcap_uvlo                      | V <sub>VCAP</sub> – V <sub>ANODE</sub> UV release at rising edge    | Vanode – Vcathode = 100 mV                             | 6.25 | 6.95 | 7.75 | V    |

| VVOAI _UVEO                     | V <sub>VCAP</sub> - V <sub>ANODE</sub> UV threshold at falling edge | V <sub>ANODE</sub> - V <sub>CATHODE</sub> = 100 mV     | 4.75 | 5.86 | 6.45 | V    |

| CATHODE                         |                                                                     |                                                        |      |      |      |      |

| ICATHODE                        | CATHODE sink current                                                | Vanode = 12 V,<br>Vanode - Vcathode = -100 mV          |      | 6    |      | uA   |

|                                 |                                                                     | Vanode =-12 V, Vcathode=12 V                           |      |      | 1    | uA   |

| Timing paramet                  |                                                                     |                                                        |      |      |      |      |

| ENTDLY                          | Enable (low to high) to Gate Turn On delay                          | Vvcap > Vvcap uvlor                                    |      | 350  |      | us   |

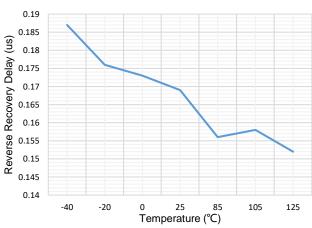

| Reverse delay                   | Reverse voltage detection to Gate<br>Turn Off delay                 | Vanode - Vcathode = 100 mV to -100mV                   |      | 0.2  |      | us   |

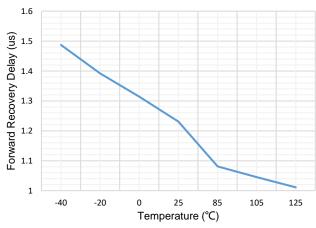

| tForward recovery               | Forward voltage detection to Gate Turn On delay                     | Vanode – Vcathode = –100 mV to 700mV                   |      | 1.23 |      | us   |

<sup>\*</sup>Derived from bench characterization

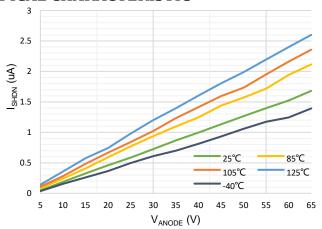

# TYPICAL CHARACTERISTIC

Figure 2. Shutdown Supply Current vs Supply Voltage

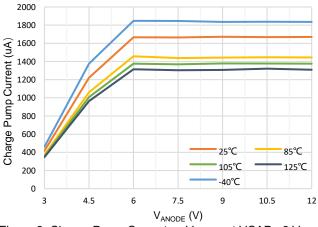

Figure 3. Charge Pump Current vs V<sub>ANODE</sub> at VCAP= 6 V

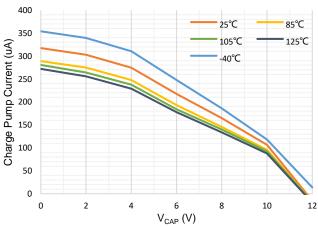

Figure 4. Charge Pump V-I at VANODE >= 12V

Figure 5. Reverse Current Blocking Delay vs Temperature

Figure 6. Forward Recovery Delay vs Temperature

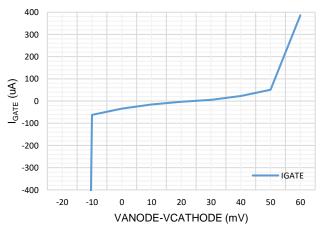

Figure 7. Gate Current vs Forward Voltage Drop

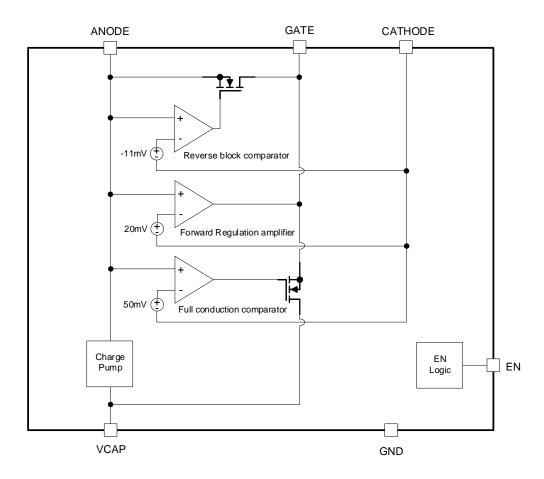

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 8. Functional Block Diagram

### **OPERATION**

#### Overview

The SCT53600Q is a high-voltage, ideal diode controller that provides system protection against reverse voltage, reverse-current flow, and destructive automotive transient voltages to implement an efficient and fast reverse polarity protection circuit or be used in a redundant power system. This easy to use ideal diode controller operates in conjunction with an external N-channel MOSFET to replace other reverse polarity schemes such as a P-channel MOSFET or a Schottky diode.

The SCT53600Q controller provides a charge pump gate drive for an external N-channel MOSFET. The voltage drop across the MOSFET is continuously monitored between the ANODE and CATHODE pins, and the GATE to ANODE voltage is adjusted as needed to regulate the forward voltage drop at 20 mV. This closed loop regulation scheme enables graceful turn off of the MOSFET during a reverse current event and ensures zero DC reverse current flow. A fast reverse current condition is detected when the voltage across ANODE and CATHODE pins reduces below –11 mV, resulting in the GATE pin being internally connected to the ANODE pin turning off the external N-channel MOSFET, and using the body diode to block any of the reverse current. The fast response to Reverse Current Blocking makes the device suitable for systems with output voltage holdup requirements during ISO7637 pulse testing.

The SCT53600Q consumes only 0.3µA of current during shutdown mode with the enable pin low to extend battery life. The device is available in an SOT23-6 package.

### **Input Voltage**

The ANODE pin is the power supply input for internal circuitry, typically drawing 60  $\mu$ A when enabled and 0.3  $\mu$ A when disabled. The SCT53600Q operates if the ANODE pin voltage is greater than the POR Rising threshold with EN pin above the specified input high threshold V<sub>EN\_H</sub>. The voltage from ANODE to GND is designed to vary from 65 V to –65 V, allowing the SCT53600Q to withstand negative voltage transients.

#### **Enable**

A logic input EN pin allows for the gate driver to be either enabled or disabled by an external signal. The EN pin can withstand a voltage as large as 65 V and as low at –65 V. This allows for the EN pin to be connected directly to the ANODE pin if enable functionality is not needed. EN has an internal 2uA sink current which means EN pin cannot be left floating for normal operation.

The SCT53600Q enters shutdown mode when the EN pin voltage is below the specified input low threshold VEN\_L. Both the gate driver and the charge pump are disabled in shutdown mode. During shutdown mode the SCT53600Q enters low IQ operation with the ANODE pin only sinking 0.3µA. When the SCT53600Q is in shutdown mode, forward current flow through the external MOSFET is not interrupted but is conducted through the MOSFET's body diode.

#### **Charge Pump**

The SCT53600Q uses a charge pump to generate the gate drive with respect to ANODE voltage. The charge pump supplies the voltage necessary to drive the external N-channel MOSFET. An external charge pump capacitor is placed between VCAP and ANODE pins to provide energy to turn on the external MOSFET.

The charge pump starts working and sources a charging current of 300  $\mu$ A typical if EN pin voltage exceeds 2V. If EN pins is pulled low, then the charge pump remains disabled. To ensure that the external MOSFET can be driven above its specified threshold voltage, the VCAP to ANODE voltage has the under voltage lockout threshold at typically 5.86 V.

#### **Gate Driver and Conduction Mode**

The gate driver is used to control the external N-Channel MOSFET. There are three defined modes of operation that the gate driver operates under forward regulation, full conduction mode and reverse current protection, according to the ANODE to CATHODE voltage.

The SCT53600Q operate in full conduction mode if the current from source to drain of the external MOSFET be large enough to result in an ANODE to CATHODE voltage drop of greater than 50 mV typical. The GATE pin is internally connected to the VCAP pin resulting in the GATE to ANODE voltage being approximately the same as the VCAP to ANODE voltage. By connecting VCAP to GATE the external MOSFET's RDS(ON) is minimized reducing the power loss of the external MOSFET when forward currents are large.

The SCT53600Q operate in reverse current protection mode if the ANODE to CATHODE voltage is typically less than -11 mv. The GATE pin is internally connected to the ANODE pin. The connection of the GATE to ANODE pin disables the external MOSFET. The body diode of the MOSFET blocks any reverse current from flowing from the drain to source.

The SCT53600Q operate in forward regulation mode if the current from source to drain of the external MOSFET be within the range to result in an ANODE to CATHODE voltage drop of -11 mV to 50 mV. During forward regulation mode the ANODE to CATHODE voltage is regulated to 20 mV by adjusting the GATE to ANODE voltage. This closed loop regulation scheme enables graceful turn off of the MOSFET at very light loads and ensures zero DC reverse current flow.

# APPLICATION INFORMATION

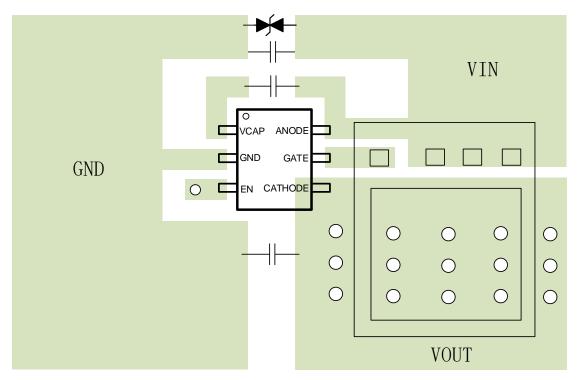

# **Typical Application- Reverse Polarity Protection**

Figure 9. Typical 12V Battery Protection with single bi-directional TVS

**Design Parameters**

| Design Parameters    | Example Value                                   |

|----------------------|-------------------------------------------------|

| Input Voltage        | 12V Battery, 12V Nominal with 35V Load Dump     |

| Output Voltage       | 4.8V during Cold Crank to 35V Load Dump         |

| Output Current Range | 3A Nominal, 5A Maximum                          |

| Output Capacitance   | 1 μF Minimum, 47 μF Typical Hold Up Capacitance |

#### **MOSFET Selection**

MOSFET selection is critical to designing a proper protection circuit. Several factors must be considered: gate capacitance, maximum continuous drain current ID, maximum drain-to-source voltage rating, on-resistance RDS(ON), maximum source current through body diode, peak power dissipation capability and the average power dissipation limit. Gate capacitance is not as critical, but it does determine the length of turn-on and turn-off times. MOSFETs with more gate capacitance tend to respond more slowly.

The maximum continuous drain current, ID, rating must exceed the maximum continuous load current. The maximum drain-to-source voltage, V<sub>DS(MAX)</sub>, must be high enough to withstand the highest differential voltage seen in the application. It is recommended to use MOSFETs with voltage rating up to 60 V maximum with the SCT53600Q because anode-cathode maximum voltage is 65V. The maximum V<sub>GS</sub> SCT53600Q can drive is 13-V, so a MOSFET with 15-V minimum V<sub>GS</sub> should be selected. If a MOSFET with <15-V V<sub>GS</sub> rating is selected, a zener diode can be used to clamp V<sub>GS</sub> to safe level. During startup, inrush current flows through the body diode to charge the bulk holdup capacitors at the output. The maximum source current through the body diode must be higher than the inrush current that can be seen in the application.

To reduce the MOSFET conduction losses, lowest possible R<sub>DS(ON)</sub> is preferred, but selecting a MOSFET based on low R<sub>DS(ON)</sub> may not be beneficial always. Higher R<sub>DS(ON)</sub> will provide increased voltage information to SCT53600Q reverse comparator at a lower reverse current. Reverse current detection is better with increased RDS(ON). It is recommended to operate the MOSFET in regulated conduction mode during nominal load conditions and select R<sub>DS(ON)</sub> such that at nominal operating current, forward voltage drop VDS is close to 20 mV regulation point and not more than 50 mV.

As a guideline, it is suggested to choose (20 mV / ILoad(Nominal)) ≤ R<sub>DS(ON)</sub> ≤ (50 mV / ILoad(Nominal)).

MOSFET manufacturers usually specify R<sub>DS(ON)</sub> at 4.5-V V<sub>GS</sub> and 10-V V<sub>GS</sub>. R<sub>DS(ON)</sub> increases drastically below 4.5-V V<sub>GS</sub> and R<sub>DS(ON)</sub> is highest when VGS is close to MOSFET Vth. For stable regulation at light load conditions, it is recommended to operate the MOSFET close to 4.5V VGS, i.e., much higher than MOSFET gate threshold voltage. It is recommended to choose MOSFET gate threshold voltage Vth of 2-V to 2.5V maximum. Choosing a lower Vth MOSFET also reduces the turn ON time.

Based on the design requirements, preferred MOSFET ratings are:

- 60-V V<sub>DS(MAX)</sub> and ±20-V V<sub>GS(MAX)</sub>

- $R_{DS(ON)}$  at 3A nominal current: (20 mV / 3A )  $\leq R_{DS(ON)} \leq$  (50 mV / 3A) = 6.67 m $\Omega \leq R_{DS(ON)} \leq$  16.67 m $\Omega$ .

- MOSFET gate threshold voltage Vth: 2V maximum

# Selection of TVS Diodes for 12V Battery Protection Applications

In the 12V battery protection application circuit shown in Figure 9, a bi-directional TVS diode is used to protect from positive and negative transient voltages that occur during normal operation of the car and these transient voltage levels and pulses are specified in ISO 7637-2 and ISO 16750-2 standards.

There are two important specifications, breakdown voltage and clamping voltage of the TVS. Breakdown voltage should be higher than worst case steady state voltages seen in the system. The breakdown voltage of the TVS+ should be higher than 24-V jump start voltage and 35-V suppressed load dump voltage and less than the maximum ratings of SCT53600Q (65V). The breakdown voltage of TVS- should be beyond than maximum reverse battery voltage -16-V, so that the TVS- is not damaged due to long time exposure to reverse connected battery.

Clamping voltage is the voltage the TVS diode clamps in high current pulse situations and this voltage is much higher than the breakdown voltage. TVS diodes are meant to clamp transient pulses and should not interfere with steady state operation. In the case of an ISO 7637-2 pulse 1, the input voltage goes up to -150 V with a generator impedance of 10 Ω. This translates to 15 A flowing through the TVS - and the voltage across the TVS would be close to its clamping voltage.

In case of ISO 7637-2 pulse 1, the anode of SCT53600Q is pulled down by the ISO pulse and clamped by TVS-. The MOSFET is turned off quickly to prevent reverse current from discharging the bulk output capacitors. When the MOSFET turns off, the cathode to anode voltage seen is equal to (TVS Clamping voltage + Output capacitor voltage). If the maximum voltage on output capacitor is 16 V (maximum battery voltage), then the clamping voltage of the TVS- should not exceed, (60 V - 16) V = -44 V.

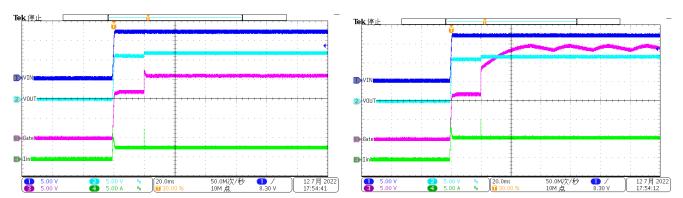

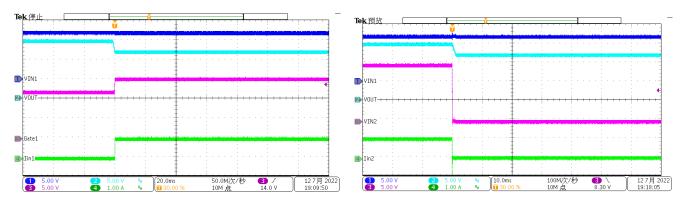

# **Application Waveforms**

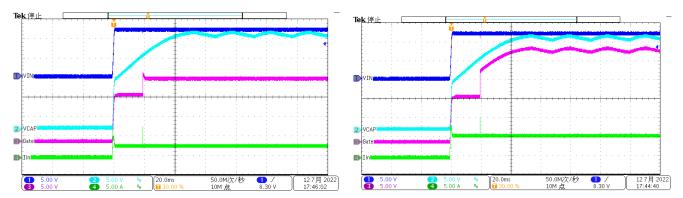

Figure 10. Start up with 3A load

Figure 11. Start up with 5.8A load

Figure 12. VCAP during startup at 3A load

Figure 13. VCAP during startup at 5.8A load

Figure 14. Enable Threshold

Figure 15. Enable turn on delay

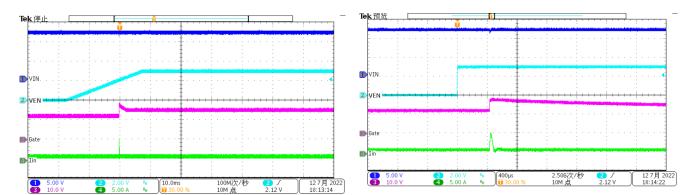

# **Application Waveforms(continued)**

Figure 16. Static Reverse Polarity

Figure 17. Dynamic Reverse Polarity(ISO 7637-2 Pulse 1)

Figure 18. Input Short Response

Figure 19. Input Micro-Short

Figure 21. Load Transient Response, 0.1A->3A

Figure 21. Load Transient Response, 3A->0.1A

# APPLICATION INFORMATION

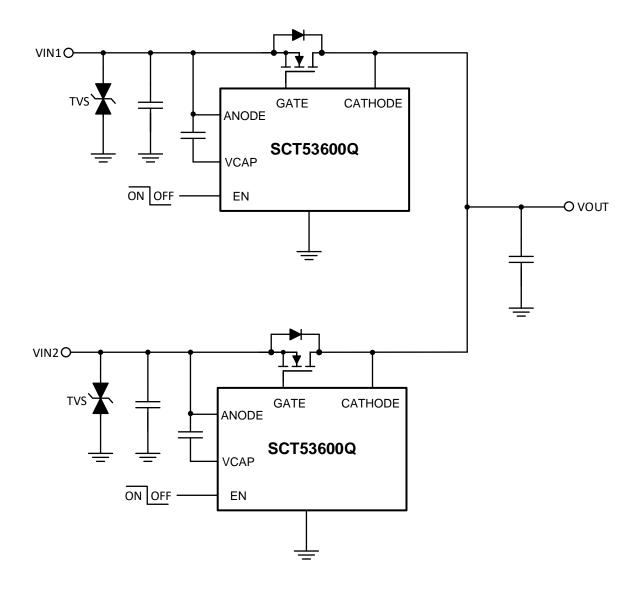

# **Typical Application- Redundant Power**

Figure 22. Redundant Power Supply Application

Downloaded From Oneyac.com

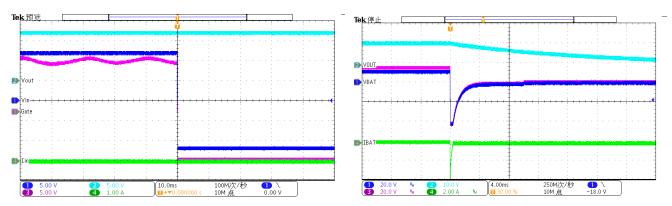

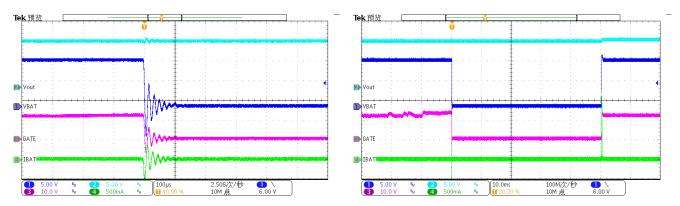

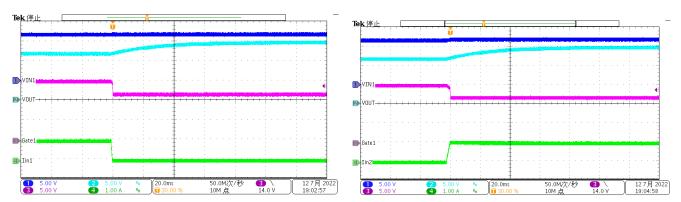

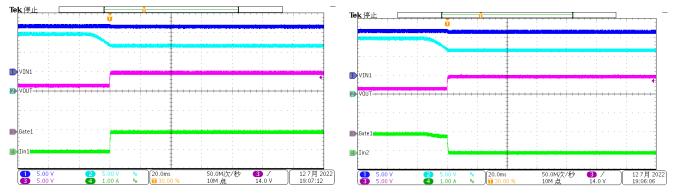

### **Application Waveforms**

Figure 23. V<sub>IN1</sub>(12V) to V<sub>IN2</sub>(15V) Switch Over

Figure 24.  $V_{IN1}(12V)$  to  $V_{IN2}(15V)$  Switch Over

Figure 25. V<sub>IN2</sub>(15V) to V<sub>IN1</sub>(12V) Switch Over

Figure 26. V<sub>IN2</sub>(15V) to V<sub>IN1</sub>(12V) Switch Over

Figure 27. VIN2 Fail and Switch Over to VIN1

Figure 28. V<sub>IN2</sub> Fail and Switch Over to V<sub>IN1</sub>

# **Layout Guideline**

- 1. Connect ANODE, GATE and CATHODE pins of SCT53600Q close to the MOSFET's SOURCE, GATE and DRAIN pins.

- 2. The high current path of for this solution is through the MOSFET, therefore it is important to use thick traces for source and drain of the MOSFET to minimize resistive losses.

- 3. The charge pump capacitor across VCAP and ANODE pins must be kept away from the MOSFET to lower the thermal effects on the capacitance value.

- 4. The Gate pin of the SCT53600Q must be connected to the MOSFET gate without using vias. Avoid excessively thin traces to the Gate Drive.

- 5. Keep the GATE pin close to the MOSFET to avoid increase in MOSFET turn-off delay due to trace resistance.

Figure 29. PCB Layout Example

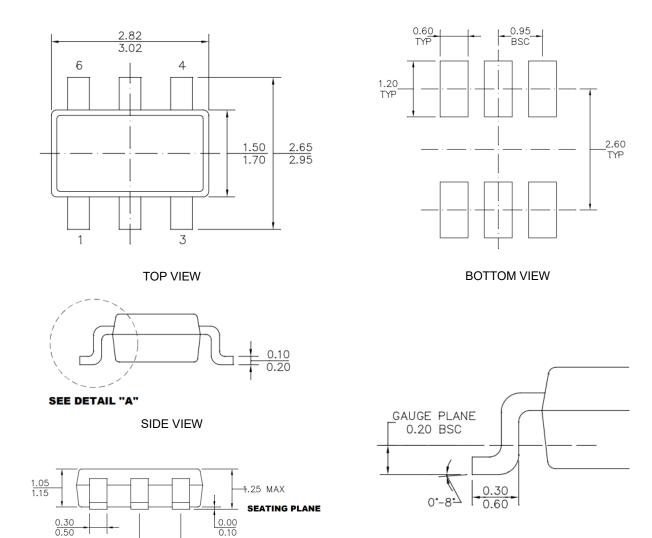

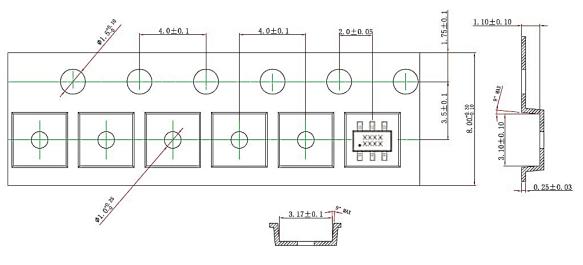

# PACKAGE INFORMATION

SOT23-6L Package Outline Dimensions

Downloaded From Oneyac.com

### NOTE:

- THE LEAD SIDE IS WETTABLE.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS.

- LEAD COPLANARITY SHALL BE 0.08 MILLIMETERS MAX.

-0.95 BSG-

FRONT VIEW

- JEDEC REFERENCE IS MO-220. 4.

- 5. DRAWING IS NOT TO SCALE.

RECOMMENDED LAND PATTERN

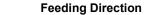

# TAPE AND REEL INFORMATION

# 单击下面可查看定价,库存,交付和生命周期等信息