# **Application Note: SY58873U**

Boost PFC Regulator Preliminary Specification

## **General Description**

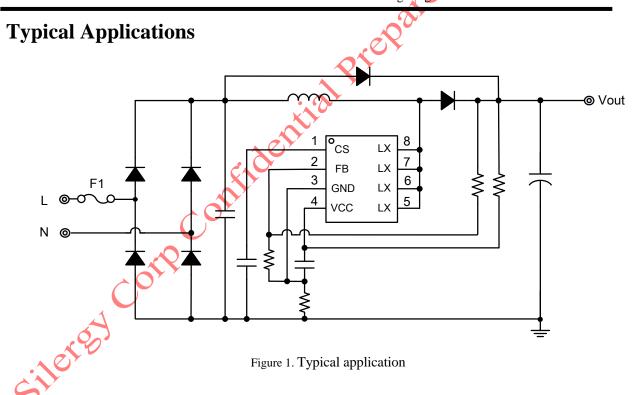

SY58873U is a single-stage Boost PFC Regulator. Constant  $t_{ON}$  operation is applied to achieve high PF and no multiplier is need. Quasi-Resonant switching is applied to achieve high efficiency and better EMI performance.

## **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY58873UFAC     | SO8          |      |

### **Features**

- Integrated 520V MOSFET

- Quasi-Resonant (QR) Mode to Achieve Low Switching Losses

- PF>0.95, THD<10%

- Output Over Voltage Protection

- Low BOM Cost

- Compact Package: SO8

# **Applications**

- Adaptors

- Pre-stage for Two-stage AC/DC Converter

- LED Lighting

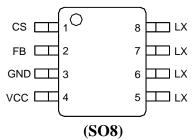

### Pinout (top view)

Top Mark: CAS xyz (device code: CAS, x=year code, y=week code, z= lot number code)

| Pin Name | Pin number | Pin Description                                                              |  |

|----------|------------|------------------------------------------------------------------------------|--|

| CS       | 1          | Peak current limit set pin.                                                  |  |

| FB       | 2          | Voltage feedback pin. Connect to a resistor divider to sense output voltage. |  |

| GND      | 3          | Ground Pin.                                                                  |  |

| VCC      | 4          | Power supply pin.                                                            |  |

| LX       | 5-8        | Internal HV MOSFET drain pin.                                                |  |

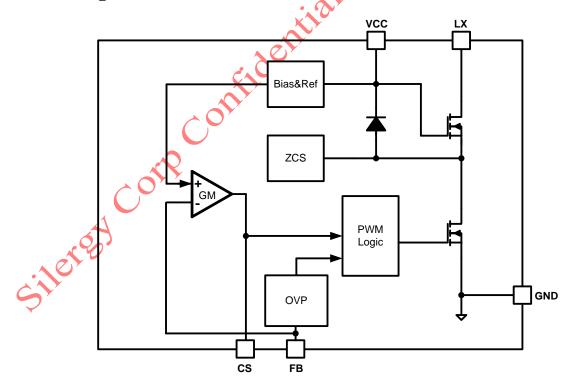

# **Block Diagram**

Fig.2 Simplified block diagram

| Absolute Maximum Ratings (Note 1)              |                 |

|------------------------------------------------|-----------------|

| CS                                             |                 |

| FB                                             |                 |

| VCC                                            |                 |

| LX                                             | 520V            |

| Power Dissipation, @ T <sub>A</sub> = 25°C SO8 | 1.1W            |

| Package Thermal Resistance (Note 2)            |                 |

| SO8, θ <sub>JA</sub>                           | 88° <b>E/</b> W |

| SO8, θ <sub>IC</sub>                           | 45°C/W          |

| SO8, $\theta_{JC}$                             |                 |

| Lead Temperature (Soldering, 10 sec.)          | 260°C           |

| Storage Temperature Range                      |                 |

| ~0t0-                                          |                 |

### **Electrical Characteristics**

$(V_{VCC}= 12V \text{ (Note 3)}, T_A = 25^{\circ}\text{C unless otherwise specified)}$

| Parameter                      | Symbol                 | Test Conditions       | Min      | Тур   | Max | Unit |

|--------------------------------|------------------------|-----------------------|----------|-------|-----|------|

| Power Supply Section           |                        |                       |          |       |     |      |

| VCC Turn-on Threshold          | V <sub>VCC_ON</sub>    |                       |          | 13.9  |     | V    |

| VCC Turn-off Threshold         | V <sub>VCC_OFF</sub>   |                       |          | 7.35  |     | V    |

| VCC Shunt Voltage              | V <sub>VCC_SHUNT</sub> | V <sub>VCC</sub> >2mA |          | 14.7  |     | V    |

| Start up Current               | $I_{ST}$               | V <sub>VCC</sub> =12V |          | 55    |     | μA   |

| Quiescent Current              | $I_Q$                  |                       |          | 260   |     | ΨΑ   |

| CS pin Section                 |                        |                       |          |       |     |      |

| CS Limit                       | V <sub>CS_LIMIT</sub>  |                       |          | 530   |     | mV   |

| FB Pin Section                 |                        |                       |          | co    | 1   |      |

| Reference Voltage for Feedback | $V_{REF}$              |                       | <b>^</b> | 1.228 |     | V    |

| Internal OVP Voltage Threshold | $V_{REF\_OVP}$         |                       |          | 1.396 |     | V    |

| Driver Section .               |                        |                       |          |       |     |      |

| Min ON Time                    | T <sub>ON_MIN</sub>    |                       |          | 755   |     | ns   |

| Max ON Time                    | T <sub>ON_MAX</sub>    |                       |          | 12.9  |     | μs   |

| Min OFF Time                   | T <sub>OFF_MIN</sub>   | •                     |          | 1.7   |     | μs   |

| Max OFF Time                   | T <sub>OFF_MAX</sub>   |                       |          | 75    |     | μs   |

| Integrated MOSFET Section      | ~                      |                       |          |       |     |      |

| BV of HV MOSFET                | V <sub>BV</sub>        |                       | 520      |       |     | V    |

| Rdson of HV MOSFET             | R <sub>DSON</sub>      |                       |          | 4.6   |     | Ω    |

| Thermal Section                | N.                     |                       |          |       |     |      |

| Thermal Shut Down Temperature  | $T_{SD}$               |                       |          | 160   |     | °C   |

**Note 1**: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2:  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25$ °C on a low effective single layer thermal conductivity test board of IEDEC 51-3 thermal measurement standard. Test condition: Device mounted on 2" x 2" FR-4 substrate PCB, 20z copper, with minimum recommended pad on top layer and thermal vias to bottom layer ground plane.

Note 3: Increase VCC pin voltage gradually higher than V<sub>VCC.ON</sub> voltage then turn down to 12V.

### **Operation**

SY58873U is a constant voltage boost PFC regulator targeting at Pre-stage for Two-stage AC/DC Converter.

In order to reduce the switching losses and improve EMI performance, Quasi-Resonant switching mode is applied, which means to turn on the power MOSFET at valley of drain voltage.

SY58873U provides reliable protections such as Over Voltage Protection (OVP), Over Temperature Protection (OTP), etc.

SY58873U is available with SO8 package.

## **Applications Information**

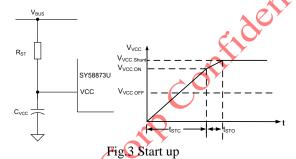

#### Start up

After AC power or DC BUS is powered on, the capacitor C<sub>VCC</sub> across VCC and GND pin is charged up by BUS voltage through a start up resistor R<sub>ST</sub>. Once  $V_{VCC}$  rises up to  $V_{VCC-ON}$ , the internal blocks start to work. Then IC can be supplied at every switching cycle. The supply current is balanced with IC consumption current to maintain V<sub>VCC</sub> above V<sub>VCC OFF</sub>.

The whole start up procedure is divided into two sections shown below. t<sub>STC</sub> is the C<sub>VCC</sub> charged up section, and t<sub>STO</sub> is the time V<sub>VCC</sub> continue rising and clamped at V<sub>VCC\_Shunt</sub>.

The start up resistor R<sub>ST</sub> and C<sub>VCC</sub> are designed by rules below:

(a) Preset start-up resistor R<sub>ST</sub>, make sure that the current through R<sub>ST</sub> is larger than I<sub>ST</sub>.

$$R_{ST} < \frac{V_{BUS}}{I_{ST}}$$

Where  $V_{BUS}$  is the BUS line voltage.

(b) Select  $C_{VCC}$  to obtain an ideal start up time  $t_{ST}$ .

$$C_{VCC} = \frac{\left(\frac{V_{BUS}}{R_{ST}} - I_{ST}\right) \times t_{ST}}{V_{VCC-ON}}$$

Proprietary self-bias technique allows C<sub>VCC</sub> to be charged every switching cycle. There is no need to add auxiliary winding for power supply. C<sub>VCC</sub> can be chosen with small value and small package to save cost.

#### Shut down

After AC power or DC BUS is powered off, the energy stored in the BUS capacitor will be discharged. When power supply for IC is not enough, V<sub>VCC</sub> will drop down. Once V<sub>VCC</sub> is below V<sub>VCC\_OFF</sub>, the IC will stop working.

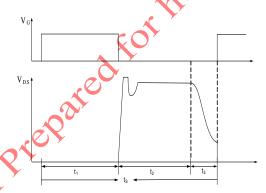

#### **Quasi-resonant Operation**

QR mode operation provides low turn-on switching losses in MOSFET.

Fig.4 QR mode

When the voltage across drain and source of the MOSFET is at voltage valley, the MOSFET would be turned on.

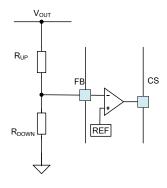

#### **Boost output voltage regulation**

SY58873U regulates the boost output voltage using a internal transconductance error amplifier (GM). The inverting terminal of the GM is pinned out to FB, the non-inverting terminal is connected to an internal 1.225V voltage reference, and the GM output is pinned out to CS.

Fig.5 simplified output voltage feedback circuit

A resistor divider ( $R_{UP}$  and  $R_{DOWN}$ ) scales down the boost output voltage ( $V_{OUT}$ ) and connects to the FB pin. If the output voltage is less than the regulation, then the control voltage ( $V_{CS}$ ) increases the on time of the driver, which increases the power transferring from the input to the output. If  $V_{OUT}$  is higher than the regulation, the  $V_{COMP}$  decreases the on time to limit the power transferring.

$$V_{OUT} = V_{REF} \times \frac{R_{UP} + R_{DOWN}}{R_{DOWN}}$$

#### Over Voltage Protection (OVP)

Because of the extremely low bandwidth of PFC's voltage loop, there is a risk of overshoots at output side during startup, load steps, and line steps. For reliable operation, the over voltage protection (OVP) is necessary to prevent output voltage from exceeding the ratings of the PFC stage components.

SY58873U detects the over voltage condition and disables the driver until Vout decreases to a safe level, which ensures that Vout is within the PFC stage component ratings. An internal comparator connected to the FB pin provides the OVP protection.

$$V_{OUT\_OVP} = V_{REF\_OVP} \times \frac{R_{UP} + R_{DOWN}}{R_{DOWN}}$$

Where V<sub>REF OVP</sub> is the Internal OVP voltage threshold.

#### **Over Temperature Protection (OTP)**

SY58873U has over temperature protection. When the junction temperature rises up over  $T_{SD}$ , the IC stops switching.

## **Power Device Design**

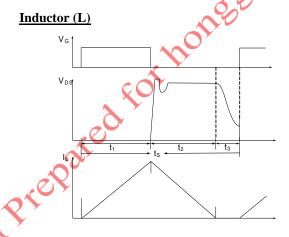

#### **MOSFET and Diode**

When the operation condition is minimum voltage input and full load output, the semiconductor devices suffer the maximum current stress.

$$\begin{split} I_{L\_PK\_MAX} &= \frac{\sqrt{2} \times 2 \times P_{OUT}}{\eta \times V_{AC\_MIN}} \\ I_{MOS\_PK\_MAX} &= I_{D\_PK\_MAX} = I_{L\_PK\_MAX} \\ I_{L\_RMS\_MAX} &= \frac{2 \times P_{OUT}}{\sqrt{3} \times \eta \times V_{AC\_MIN}} \end{split}$$

$$\begin{split} I_{MOS\_RMS\_MAX} &= \frac{2}{\sqrt{3}} \times \frac{P_{OUT}}{\eta \times V_{AC\_MIN}} \times \sqrt{1 - (\frac{\sqrt{2} \times 8 \times V_{AC\_MIN}}{3 \times \pi \times V_{OUT}})} \\ I_{D\_RMS\_MAX} &= \frac{4}{3} \times \frac{P_{OUT}}{\eta \times \sqrt{V_{AC\_MIN} \times V_{OUT}}} \times \sqrt{\frac{2 \times \sqrt{2}}{\pi}} \end{split}$$

$$I_{D\_AVG} = I_{OUT} = \frac{P_{OUT}}{V_{OUT}}$$

Where  $I_{L\text{-PK-MAX}}$  and  $I_{L\text{-RMS-MAX}}$  are maximum inductor peak current and RMS current ,  $P_{OUT}$  is the output power ,  $V_{OUT}$  is the output voltage ,  $V_{AC\_MIN}$  is the minimum input AC voltage ,  $\eta$  is the estimated efficiency

Fig.6 switching waveforms

The design flow is shown as below:

- (a) Preset frequency f<sub>S</sub>

- (b) Compute relative t<sub>S</sub>, t<sub>1</sub>

$$t_{S} = \frac{1}{f_{S}}$$

$$t_{1} = \frac{V_{OUT} - \sqrt{2} \times V_{AC}}{V_{OUT}} \times t_{S}$$

(c) Compute the peak current of inductor

$$I_{L\_PK} = \frac{\sqrt{2} \times 2 \times P_{OUT}}{\eta \times V_{AC}}$$

(d)Design inductance L

$$L_{M} = \frac{\sqrt{2} \times V_{AC\_RMS} \times t_{1}}{I_{L\_PK}}$$

#### Inductor Design (N)

| Necessary parameters: |                       |  |

|-----------------------|-----------------------|--|

| inductance            | L                     |  |

| CS limit              | V <sub>CS_LIMIT</sub> |  |

The design rules are as followed:

- (a) Select the magnetic core style, identify the effective area Ae.

- (b) Preset the maximum magnetic flux  $\Delta B$

$$\Delta B = 0.3 \sim 0.35T$$

$$R_S = \frac{V_{CS\_LIMIT}}{I_{L\_PK\_MAX}}$$

$$N = \frac{L_M \times I_{L\_PK\_MAX}}{\Delta B \times A_a}$$

e demanded in the partial Prepared For Horizon

(f) If the winding area of the core and bobbin is not enough, reselect the core style, go to (a) and redesign the inductor until the ideal inductor is achieved.

#### Output capacitor Cout

Preset the output voltage ripple  $\Delta V_{OUT}$ ,  $C_{OUT}$  is induced

$$C_{OUT} = \frac{P_{OUT}}{2 \times \pi \times f_{AC} \times \Delta V_{OUT} \times V_{OUT}}$$

Where P<sub>OUT</sub> is the rated output power, f<sub>AC</sub> is the AC line frequency,  $\Delta V_{OUT}$  is the demanded voltage ripple.

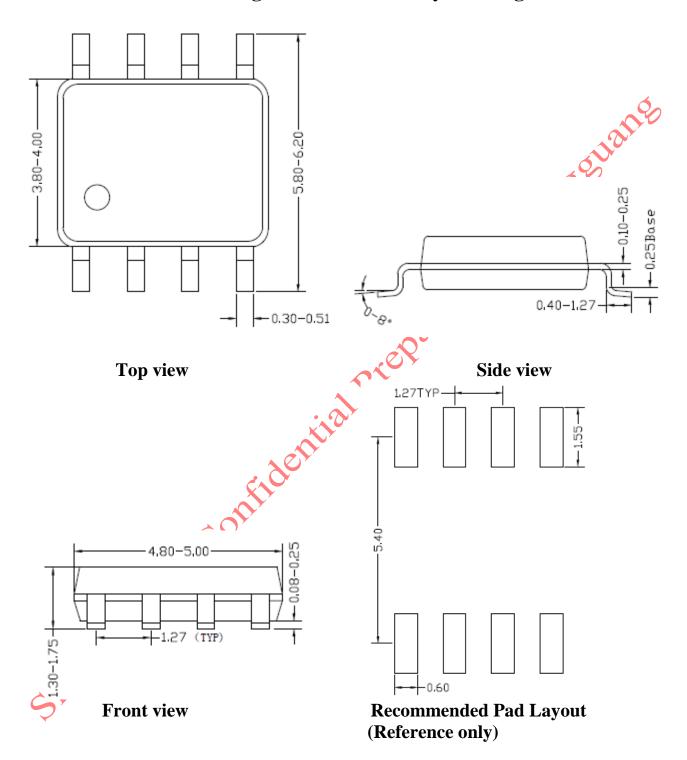

# SO8 Package outline & PCB layout design

Notes: All dimension in millimeter and exclude mold flash & metal burr.

# 单击下面可查看定价,库存,交付和生命周期等信息

>>SILERGY(矽力杰)