### **Description**

The SiT9365 is a differential MEMS XO supporting standard frequencies between 25 MHz and 325 MHz, and engineered for low-jitter applications. Utilizing SiTime's unique DualMEMS™ temperature sensing and TurboCompensation™ technology, the SiT9365 delivers exceptional dynamic performance by providing resistance to airflow, thermal gradients, shock and vibration. This device also integrates multiple on-chip regulators to filter power supply noise, eliminating the need for a dedicated external LDO.

The SiT9365 can be factory programmed for specific combinations of frequency, stability, voltage, and output signaling. Programmability enables designers to optimize clock configurations while eliminating long lead times and customization costs associated with quartz devices where each frequency is custom built.

Standard frequencies and programmability makes this device ideal for telecom, networking, and industrial applications that require a variety of frequencies and operate in noisy environments.

Refer to Manufacturing Notes for proper reflow profile, tape and reel dimension, and other manufacturing related information.

### **Features**

- 32 standard frequencies from 25 MHz to 325 MHz (For additional frequencies, refer to SiT9366 and SiT9367 datasheets)

- LVPECL, Low-swing LVPECL, LVDS and HCSL output signaling

- 0.1 ps RMS phase jitter (random) for Ethernet applications

- Frequency stability as low as ±10 ppm

- Wide temperature ranges from -40°C to 105°C

- Industry-standard packages: 3.2 x 2.5 mm<sup>2</sup>, 7.0 x 5.0 mm<sup>2</sup> and 5.0 x 3.2 mm<sup>2</sup> package

### **Applications**

- 10/40/100 Gbps Ethernet, SONET, SATA, SAS, Fibre Channel

- Telecom, networking, instrumentation, storage, servers

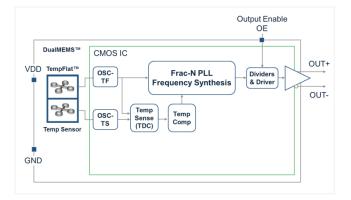

## **Block Diagram**

Figure 1. SiT9365 Block Diagram

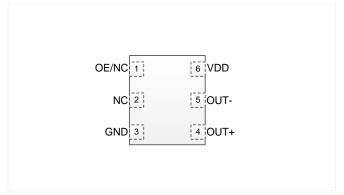

## **Package Pinout**

Figure 2. Pin Assignments (Top view) (Refer to Table 7 for Pin Descriptions)

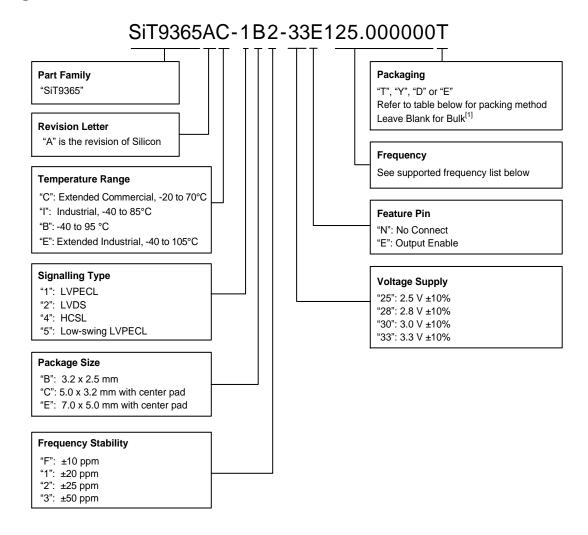

## **Ordering Information**

#### Notes:

1. Bulk is available for sampling only.

#### **Table 1. Supported Frequencies**

| 25.000000 MHz  | 30.720000 MHz  | 50.000000 MHz  | 53.125000 MHz  | 61.440000 MHz  | 62.500000 MHz  | 74.175824 MHz  | 74.250000 MHz  |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 75.000000 MHz  | 77.760000 MHz  | 98.304000 MHz  | 100.000000 MHz | 106.250000 MHz | 122.880000 MHz | 125.000000 MHz | 133.333333 MHz |

| 148.351648 MHz | 150.000000 MHz | 153.600000 MHz | 155.520000 MHz | 156.250000 MHz | 159.375000 MHz | 160.000000 MHz | 161.132813 MHz |

| 166.666666 MHz | 168.040678 MHz | 200.000000 MHz | 212.500000 MHz | 250.000000 MHz | 300.000000 MHz | 322.265625 MHz | 325.000000 MHz |

### Table 2. Ordering Codes for Supported Tape & Reel Packing Method

| Device Size<br>(mm x mm) | 8 mm T&R<br>(3ku) | 8 mm T&R<br>(1ku) | 12 mm T&R<br>(3ku) | 12 mm T&R<br>(1ku) | 16 mm T&R<br>(3ku) | 16 mm T&R<br>(1ku) |

|--------------------------|-------------------|-------------------|--------------------|--------------------|--------------------|--------------------|

| 7.0 x 5.0                | _                 | _                 | _                  | _                  | Т                  | Υ                  |

| 5.0 x 3.2                |                   |                   | Т                  | Υ                  |                    |                    |

| 3.2 x 2.5                | D                 | E                 |                    |                    | _                  |                    |

## **TABLE OF CONTENTS**

| Description                                         |    |

|-----------------------------------------------------|----|

| Features                                            | 1  |

| Applications                                        |    |

| Block Diagram                                       | 1  |

| Block DiagramPackage Pinout                         | 1  |

| Ordering Information                                | 2  |

| Electrical Characteristics                          | 4  |

| Waveform Diagrams                                   | g  |

| Waveform Diagrams                                   | 11 |

| LVPECL and Low-swing LVPECL                         |    |

| LVDS                                                | 13 |

| HCSL                                                | 14 |

| Dimensions and Patterns — 3.2 x 2.5 mm <sup>2</sup> | 15 |

| Dimensions and Patterns — 5.0 x 3.2 mm <sup>2</sup> |    |

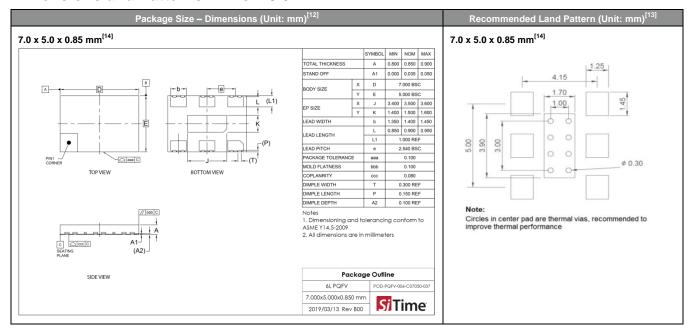

| Dimensions and Patterns — 7.0 x 5.0 mm <sup>2</sup> | 16 |

| Additional Information                              |    |

| Revision History                                    | 18 |

### **Electrical Characteristics**

All Min and Max limits in the Electrical Characteristics tables are specified over temperature and rated operating voltage with standard output termination shown in the termination diagrams. Typical values are at 25°C and nominal supply voltage.

Table 3. Electrical Characteristics – Common to LVPECL, Low-swing LVPECL, LVDS and HCSL (All temperature ranges)

| Parameter                   | Symbol              | Min.                                                      | Тур. | Max.         | Unit     | Condition                                                                                                                                                |  |  |  |  |

|-----------------------------|---------------------|-----------------------------------------------------------|------|--------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                             |                     |                                                           |      | Frequency R  | ange     |                                                                                                                                                          |  |  |  |  |

| Output Frequency Range      | f                   | 32 standard frequencies between 25 MHz and 325.000000 MHz |      | MHz          |          |                                                                                                                                                          |  |  |  |  |

|                             | Frequency Stability |                                                           |      |              |          |                                                                                                                                                          |  |  |  |  |

| Frequency Stability         | F_stab              | -10                                                       | -    | +10          | ppm      | Inclusive of initial tolerance, operating temperature, rated power                                                                                       |  |  |  |  |

|                             |                     | -20                                                       | _    | +20          | ppm      | supply voltage and load variations                                                                                                                       |  |  |  |  |

|                             |                     | -25                                                       | -    | +25          | ppm      |                                                                                                                                                          |  |  |  |  |

|                             |                     | -50                                                       | -    | +50          | ppm      |                                                                                                                                                          |  |  |  |  |

| First Year Aging            | F_1y                | -0.7                                                      | ±0.4 | +0.7         | ppm      | At 85°C                                                                                                                                                  |  |  |  |  |

| 5 Year Aging                | F_5y                | -1.1                                                      | ±0.7 | +1.1         | ppm      | At 85°C                                                                                                                                                  |  |  |  |  |

| 10 Year Aging               | F_10y               | -1.3                                                      | ±0.8 | +1.3         | ppm      | At 85°C                                                                                                                                                  |  |  |  |  |

| 20 Year Aging               | F_20y               | -1.5                                                      | ±1.0 | +1.5         | ppm      | At 85°C                                                                                                                                                  |  |  |  |  |

|                             |                     |                                                           | Te   | emperature F | Range    |                                                                                                                                                          |  |  |  |  |

| Operating Temperature Range | T_use               | -20                                                       | -    | +70          | °C       | Extended Commercial                                                                                                                                      |  |  |  |  |

|                             |                     | -40                                                       | -    | +85          | °C       | Industrial                                                                                                                                               |  |  |  |  |

|                             |                     | -40                                                       | -    | +95          | °C       |                                                                                                                                                          |  |  |  |  |

|                             |                     | -40                                                       | -    | +105         | °C       | Extended Industrial                                                                                                                                      |  |  |  |  |

|                             |                     |                                                           |      | Supply Volt  | age      |                                                                                                                                                          |  |  |  |  |

| Supply Voltage              | Vdd                 | 2.97                                                      | 3.30 | 3.63         | V        |                                                                                                                                                          |  |  |  |  |

|                             |                     | 2.70                                                      | 3.00 | 3.30         | V        |                                                                                                                                                          |  |  |  |  |

|                             |                     | 2.52                                                      | 2.80 | 3.08         | V        |                                                                                                                                                          |  |  |  |  |

|                             |                     | 2.25                                                      | 2.50 | 2.75         | V        |                                                                                                                                                          |  |  |  |  |

|                             |                     |                                                           | Inj  | out Characte | ristics  |                                                                                                                                                          |  |  |  |  |

| Input Voltage High          | VIH                 | 70%                                                       | -    | _            | Vdd      | Pin 1, OE                                                                                                                                                |  |  |  |  |

| Input Voltage Low           | VIL                 | _                                                         | -    | 30%          | Vdd      | Pin 1, OE                                                                                                                                                |  |  |  |  |

| Input Pull-up Impedance     | Z_in                | _                                                         | 100  | _            | kΩ       | Pin 1, OE logic high or logic low                                                                                                                        |  |  |  |  |

|                             |                     |                                                           | Out  | tput Charact | eristics |                                                                                                                                                          |  |  |  |  |

| Duty Cycle                  | DC                  | 45                                                        | _    | 55           | %        |                                                                                                                                                          |  |  |  |  |

|                             |                     |                                                           | Sta  | rtup and OE  | Timing   | <del>-</del>                                                                                                                                             |  |  |  |  |

| Startup Time                | T_start             | -                                                         | -    | 3.0          | ms       | Measured from the time Vdd reaches its rated minimum value.                                                                                              |  |  |  |  |

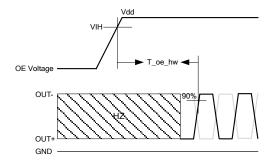

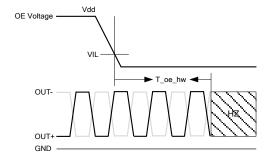

| OE Enable/Disable Time      | T_oe                | -                                                         | -    | 3.8          | μs       | f = 156.25 MHz. Measured from the time OE pin reaches rated VIH and VIL to the time clock pins reach 90% of swing and high-Z. See Figure 8 and Figure 9. |  |  |  |  |

Table 4. Electrical Characteristics – LVPECL, Low-swing LVPECL

| Parameter                         | Symbol   | Min.     | Тур.          | Max.          | Unit      | Condition                                                                                                                                   |

|-----------------------------------|----------|----------|---------------|---------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | •        |          | Cur           | rent Consu    | mption    |                                                                                                                                             |

| Current Consumption               | ldd      | _        | _             | 89            | mA        | Excluding Load Termination Current, Vdd = 3.3V or 2.5V                                                                                      |

| OE Disable Supply Current         | I_OE     | -        | -             | 58            | mA        | OE = Low                                                                                                                                    |

| Output Disable Leakage Current    | I_leak   | -        | 0.15          | -             | μΑ        | OE = Low                                                                                                                                    |

| Maximum Output Current            | I_driver | _        | ı             | 30            | mA        | Maximum average current drawn from OUT+ or OUT-                                                                                             |

|                                   |          |          | Output Ch     | aracteristic  | s for LVP | PECL                                                                                                                                        |

| Output High Voltage               | VOH      | Vdd-1.1  | -             | Vdd-0.7       | V         | See Figure 4                                                                                                                                |

| Output Low Voltage                | VOL      | Vdd-1.9  | _             | Vdd-1.5       | V         | See Figure 4                                                                                                                                |

| Output Differential Voltage Swing | V_Swing  | 1.2      | 1.6           | 2.0           | V         | See Figure 5                                                                                                                                |

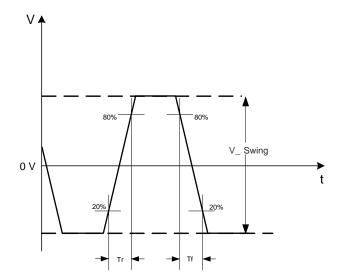

| Rise/Fall Time                    | Tr, Tf   | -        | 225           | 290           | ps        | 20% to 80%. See Figure 5                                                                                                                    |

|                                   |          | Outpu    | ıt Characte   | ristics for L | ow-swin   | g LVPECL                                                                                                                                    |

| Output High Voltage               | VOH      | Vdd-1.2  | -             | Vdd-0.75      | V         | See Figure 4                                                                                                                                |

| Output Low Voltage                | VOL      | Vdd-1.8  | -             | Vdd-1.25      | V         | See Figure 4                                                                                                                                |

| Output Differential Voltage Swing | V_Swing  | 0.4      | 1             | 1.2           | V         | Output frequency less than or equal to 220 MHz, See Figure 5                                                                                |

|                                   |          | 0.4      | 1             | 1.6           | V         | Output frequency greater than 220 MHz, See Figure 5                                                                                         |

| Rise/Fall Time                    | Tr, Tf   | -        | 225           | 290           | ps        | 20% to 80%. See Figure 5                                                                                                                    |

|                                   | •        | ı        | Jitter -      | 7.0 x 5.0 mr  | n Packag  | ge                                                                                                                                          |

| RMS Period Jitter <sup>[2]</sup>  | T_jitt   | -        | 1.0           | 1.6           | ps        | f = 100, 156.25 or 212.5 MHz, Vdd = 3.3V or 2.5V                                                                                            |

| RMS Phase Jitter (random)         | T_phj    | _        | 0.225         | 0.270         | ps        | f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -20 to 70°C and -40 to 85°C    |

|                                   |          | -        | 0.225         | 0.300         | ps        | f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -40 to 95°C and -40 to 105°C   |

|                                   |          | _        | 0.1           | -             | ps        | f = 156.25 or 322.265625 MHz, IEEE802.3-2005 10GbE jitter mask integration bandwidth = 1.875 MHz to 20 MHz, includes spurs, all Vdd levels. |

|                                   |          | Jitter - | - 5.0 x 3.2 r | nm and 3.2    | x 2.5 mm  | n Packages                                                                                                                                  |

| RMS Period Jitter <sup>[2]</sup>  | T_jitt   | _        | 1.0           | 1.6           | ps        | f = 100, 156.25 or 212.5 MHz, Vdd = 3.3V or 2.5V                                                                                            |

| RMS Phase Jitter (random)         |          | ı        | 0.225         | 0.275         | ps        | f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -20 to 70°C and -40 to 85°C    |

|                                   |          | _        | 0.225         | 0.340         | ps        | f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -40 to 95°C and -40 to 105°C   |

|                                   |          | -        | 0.1           | -             | ps        | f = 156.25 or 322.265625 MHz, IEEE802.3-2005 10GbE jitter mask integration bandwidth = 1.875 MHz to 20 MHz, includes spurs, all Vdd levels. |

Notes:

2. Measured according to JESD65B

## Table 5. Electrical Characteristics - LVDS

| Parameter                        | Symbol                 | Min.  | Тур.          | Max.        | Unit     | Condition                                                                                                                                   |  |  |

|----------------------------------|------------------------|-------|---------------|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                  |                        |       | Cur           | rent Consu  | mption   |                                                                                                                                             |  |  |

| Current Consumption              | ldd                    | -     | -             | 79          | mA       | Excluding Load Termination Current, Vdd = 3.3V or 2.5V                                                                                      |  |  |

| OE Disable Supply Current        | I_OE                   | -     | _             | 58          | mA       | OE = Low                                                                                                                                    |  |  |

| Output Disable Leakage Current   | I_leak                 | ı     | 0.15          | -           | μΑ       | OE = Low                                                                                                                                    |  |  |

|                                  | Output Characteristics |       |               |             |          |                                                                                                                                             |  |  |

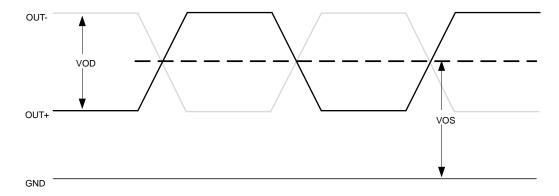

| Differential Output Voltage      | VOD                    | 300   | _             | 450         | mV       | See Figure 6                                                                                                                                |  |  |

| Delta VOD                        | ΔVOD                   | -     | _             | 50          | mV       | See Figure 6                                                                                                                                |  |  |

| Offset Voltage                   | VOS                    | 1.125 | _             | 1.375       | V        | See Figure 6                                                                                                                                |  |  |

| Delta VOS                        | ΔVOS                   | _     | _             | 50          | mV       | See Figure 6                                                                                                                                |  |  |

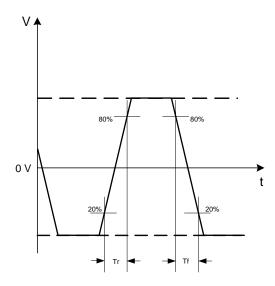

| Rise/Fall Time                   | Tr, Tf                 | I     | 400           | 470         | ps       | Measured with 2 pF capacitive loading to GND, 20% to 80%. See Figure 7                                                                      |  |  |

|                                  |                        |       | Jitter –      | 7.0 x 5.0 m | m Packag | je                                                                                                                                          |  |  |

| RMS Period Jitter <sup>[3]</sup> | T_jitt                 | ı     | 1.0           | 1.6         | ps       | f = 100, 156.25 or 212.5 MHz, Vdd = 3.3V or 2.5V                                                                                            |  |  |

| RMS Phase Jitter (random)        | T_phj                  | -     | 0.215         | 0.265       | ps       | f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -20 to 70°C and -40 to 85°C    |  |  |

|                                  |                        | -     | 0.215         | 0.300       | ps       | f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -40 to 95°C and -40 to 105°C   |  |  |

|                                  |                        | -     | 0.1           | -           | ps       | f = 156.25 or 322.265625 MHz, IEEE802.3-2005 10GbE jitter mask integration bandwidth = 1.875 MHz to 20 MHz, includes spurs, all Vdd levels. |  |  |

|                                  |                        | Jitte | er – 5.0 x 3. | 2 and 3.2 x | 2.5 mm F | Packages                                                                                                                                    |  |  |

| RMS Period Jitter <sup>[1]</sup> | T_jitt                 | -     | 1.0           | 1.6         | ps       | f = 100, 156.25 or 212.5 MHz, Vdd = 3.3V or 2.5V                                                                                            |  |  |

| RMS Phase Jitter (random)        | T_phj                  | I     | 0.235         | 0.275       | ps       | f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -20 to 70°C and -40 to 85°C    |  |  |

|                                  |                        | I     | 0.235         | 0.320       | ps       | f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -40 to 95°C and -40 to 105°C   |  |  |

|                                  |                        | -     | 0.1           | -           | ps       | f = 156.25 or 322.265625 MHz, IEEE802.3-2005 10GbE jitter mask integration bandwidth = 1.875 MHz to 20 MHz, includes spurs, all Vdd levels. |  |  |

#### Notes:

3. Measured according to JESD65B

Table 6. Electrical Characteristics - HCSL

| Parameter                         | Symbol   | Min.  | Тур.          | Max.        | Unit     | Condition                                                                                                                                   |

|-----------------------------------|----------|-------|---------------|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                                   |          |       | Curi          | rent Consu  | mption   |                                                                                                                                             |

| Current Consumption               | ldd      | -     | -             | 89          | mA       | Excluding Load Termination Current, Vdd = 3.3V or 2.5V                                                                                      |

| OE Disable Supply Current         | I_OE     | I     | _             | 58          | mA       | OE = Low                                                                                                                                    |

| Output Disable Leakage Current    | I_leak   | ı     | 0.15          | -           | μА       | OE = Low                                                                                                                                    |

| Maximum Output Current            | I_driver | ı     | -             | 35          | mA       | Maximum average current drawn from OUT+ or OUT-                                                                                             |

|                                   |          |       | Outp          | out Charact | eristics |                                                                                                                                             |

| Output High Voltage               | VOH      | 0.60  | -             | 0.90        | V        | See Figure 4                                                                                                                                |

| Output Low Voltage                | VOL      | -0.05 | _             | 0.08        | V        | See Figure 4                                                                                                                                |

| Output Differential Voltage Swing | V_Swing  | 1.2   | 1.4           | 1.80        | V        | See Figure 5                                                                                                                                |

| Rise/Fall Time                    | Tr, Tf   | ı     | 360           | 465         | ps       | Measured with 2 pF capacitive loading to GND, 20% to 80%. See Figure 5                                                                      |

|                                   |          |       | Jitter -      | 7.0 x 5.0 m | m Packag | ge                                                                                                                                          |

| RMS Period Jitter <sup>[4]</sup>  | T_jitt   | -     | 1.0           | 1.6         | ps       | f = 100, 156.25 or 212.5 MHz, Vdd = 3.3V or 2.5V                                                                                            |

| RMS Phase Jitter (random)         | T_phj    | П     | 0.220         | 0.270       | ps       | f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -20 to 70°C and -40 to 85°C    |

|                                   |          | -     | 0.220         | 0.300       | ps       | f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -40 to 95°C and -40 to 105°C   |

|                                   |          | -     | 0.1           | -           | ps       | f = 156.25 or 322.265625 MHz, IEEE802.3-2005 10GbE jitter mask integration bandwidth = 1.875 MHz to 20 MHz, includes spurs, all Vdd levels. |

|                                   |          | Jitte | er – 5.0 x 3. | 2 and 3.2 x | 2.5 mm F | Packages                                                                                                                                    |

| RMS Period Jitter <sup>[4]</sup>  | T_jitt   | -     | 1.0           | 1.6         | ps       | f = 100, 156.25 or 212.5 MHz, Vdd = 3.3V or 2.5V                                                                                            |

| RMS Phase Jitter (random)         | T_phj    | 1     | 0.230         | 0.275       | ps       | f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -20 to 70°C and -40 to 85°C    |

|                                   |          | 1     | 0.230         | 0.340       | ps       | f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -40 to 95°C and -40 to 105°C   |

|                                   |          | _     | 0.1           | _           | ps       | f = 156.25 or 322.265625 MHz, IEEE802.3-2005 10GbE jitter mask integration bandwidth = 1.875 MHz to 20 MHz, includes spurs, all Vdd levels. |

#### Notes:

4. Measured according to JESD65B

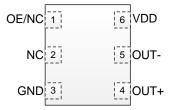

## **Table 7. Pin Description**

| Pin                | Мар              | Functionality                                                           |                                                                              |  |  |  |

|--------------------|------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|

| Output Enable (OE) |                  |                                                                         | H <sup>[5]</sup> : specified frequency output<br>L: output is high impedance |  |  |  |

| '                  | Non Connect (NC) | H or L or Open: No effect on output frequency or other device functions |                                                                              |  |  |  |

| 2                  | NC               | NA                                                                      | No Connect; Leave it floating or connect to GND for better heat dissipation  |  |  |  |

| 3                  | GND              | Power                                                                   | VDD Power Supply Ground                                                      |  |  |  |

| 4                  | OUT+             | Output                                                                  | Oscillator output                                                            |  |  |  |

| 5                  | OUT-             | Output                                                                  | Complementary oscillator output                                              |  |  |  |

| 6                  | VDD              | Power                                                                   | Power supply voltage <sup>[6]</sup>                                          |  |  |  |

### **Top View**

Figure 3. Pin Assignments

- 5. In OE mode, a pull-up resistor of 10 kΩ or less is recommended if pin 1 is not externally driven.

6. A capacitor of value 0.1 μF or higher between VDD and GND is required. An additional 10 μF capacitor between VDD and GND is required for the best phase jitter performance

### **Table 8. Absolute Maximum Ratings**

Attempted operation outside the absolute maximum ratings may cause permanent damage to the part. Actual performance of the IC is only guaranteed within the operational specifications, not at absolute maximum ratings.

| Parameter                                                            | Min. | Max.       | Unit |

|----------------------------------------------------------------------|------|------------|------|

| Vdd                                                                  | -0.5 | 4.0        | V    |

| VIH                                                                  |      | Vdd + 0.3V | V    |

| VIL                                                                  | -0.3 |            | V    |

| Storage Temperature                                                  | -65  | 150        | °C   |

| Maximum Junction Temperature                                         |      | 130        | °C   |

| Soldering Temperature (follow standard Pb-free soldering guidelines) |      | 260        | °C   |

## Table 9. Thermal Considerations<sup>[7]</sup>

| Package     | θ <sub>JA</sub> , 4 Layer Board (°C/W) | θ <sub>JC</sub> , Bottom (°C/W) |

|-------------|----------------------------------------|---------------------------------|

| 3225, 6-pin | 80                                     | 30                              |

| 5032, 6-pin | 53                                     | 20                              |

| 7050, 6-pin | 52                                     | 19                              |

#### Notes

7. Refer to JESD51 for  $\theta_{JA}$  and  $\theta_{JC}$  definitions, and reference layout used to determine the  $\theta_{JA}$  and  $\theta_{JC}$  values in the above table.

## Table 10. Maximum Operating Junction Temperature<sup>[8]</sup>

| Max Operating Temperature (ambient) | Maximum Operating Junction Temperature |

|-------------------------------------|----------------------------------------|

| 70°C                                | 95°C                                   |

| 85°C                                | 110°C                                  |

| 95°C                                | 120°C                                  |

| 105°C                               | 130°C                                  |

#### Notes:

8. Datasheet specifications are not guaranteed if junction temperature exceeds the maximum operating junction temperature.

### **Table 11. Environmental Compliance**

| Parameter                                                            | Test Conditions           | Value       | Unit |

|----------------------------------------------------------------------|---------------------------|-------------|------|

| Mechanical Shock Resistance                                          | MIL-STD-883F, Method 2002 | 10,000      | g    |

| Mechanical Vibration Resistance                                      | MIL-STD-883F, Method 2007 | 70          | g    |

| Soldering Temperature (follow standard Pb free soldering guidelines) | MIL-STD-883F, Method 2003 | 260         | °C   |

| Moisture Sensitivity Level                                           | MSL1 @ 260°C              |             |      |

| Electrostatic Discharge (HBM)                                        | HBM, JESD22-A114          | 2,000       | V    |

| Charge-Device Model ESD Protection                                   | JESD220C101               | 750         | V    |

| Latch-up Tolerance                                                   | JESD7                     | 8 Compliant |      |

# **Waveform Diagrams**

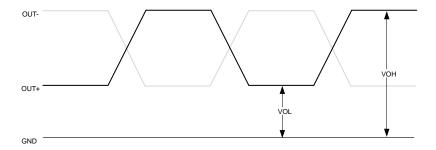

Figure 4. LVPECL, Low-swing LVPECL, and HCSL Voltage Levels per Differential Pin (i.e. OUT+, or OUT-)

Figure 5. LVPECL, Low-swing LVPECL, and HCSL Voltage Levels Across Differential Pair (i.e. OUT+ minus OUT-)

## **Waveform Diagrams (continued)**

Figure 6. LVDS Voltage Levels per Differential Pin (i.e. OUT+, or OUT-)

Figure 7. LVDS Differential Waveform (i.e. OUT+ minus OUT-)

Figure 8. Hardware OE Enable Timing

Figure 9. Hardware OE Disable Timing

## **Termination Diagrams**

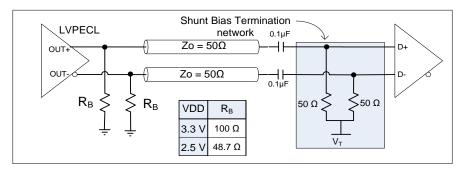

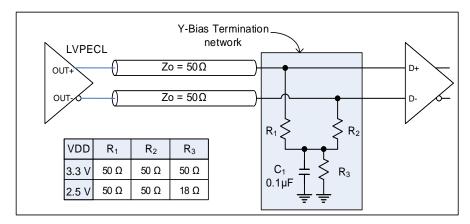

## LVPECL and Low-swing LVPECL

Figure 10. LVPECL and Low-swing LVPECL with AC-coupled Termination

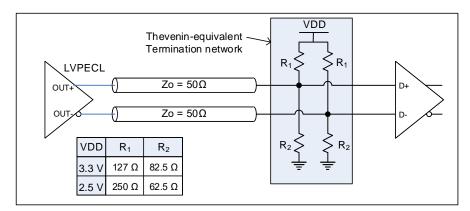

Figure 11. LVPECL and Low-swing LVPECL DC-coupled Load Termination with Thevenin Equivalent Network

Figure 12. LVPECL and Low-swing LVPECL with Y-Bias Termination

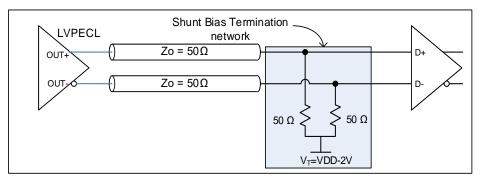

## **Termination Diagrams (continued)**

## LVPECL and Low-swing LVPECL (continued)

Figure 13. LVPECL and Low-swing LVPECL with DC-coupled Parallel Shunt Load Termination

## **Termination Diagrams (continued)**

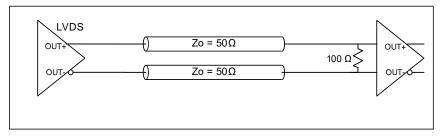

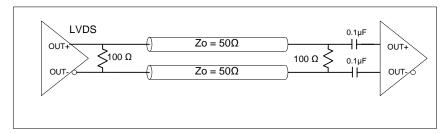

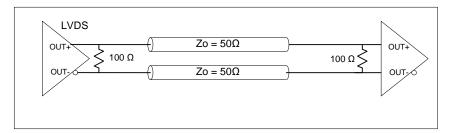

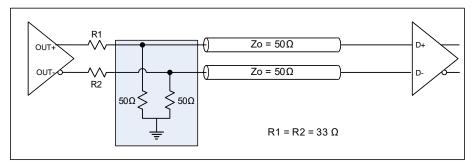

### **LVDS**

Figure 14. LVDS Single DC Termination at the Load

Figure 15. LVDS double AC Termination with Capacitor Close to the Load

Figure 16. LVDS Double DC Termination

# **Termination Diagrams (continued)**

## **HCSL**

Figure 17. HCSL Interface Termination

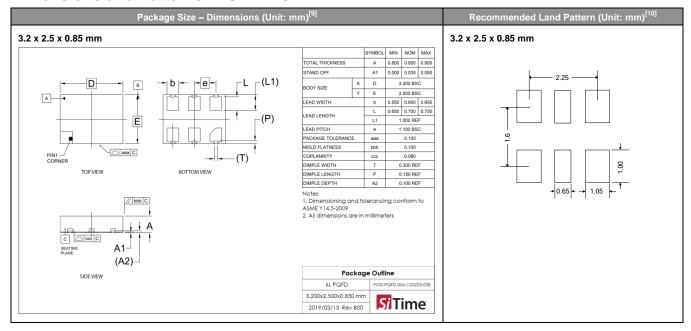

## Dimensions and Patterns — 3.2 x 2.5 mm<sup>2</sup>

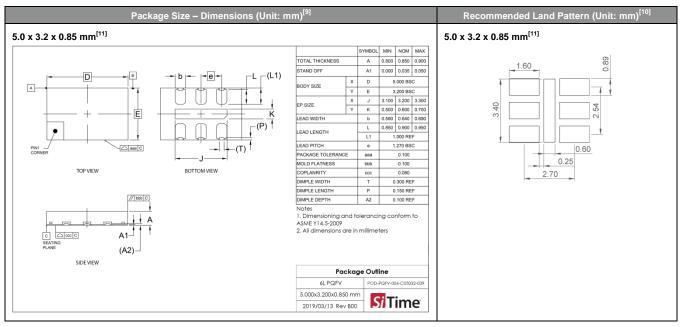

## Dimensions and Patterns — 5.0 x 3.2 mm<sup>2</sup>

#### Notes:

- 9. Top Marking: Y denotes manufacturing origin and XXXX denotes manufacturing lot number. The value of "Y" will depend on the assembly location of the device.

- 10. A capacitor of value 0.1 μF or higher between VDD and GND is required. An additional 10 μF capacitor between VDD and GND is required for the best phase jitter performance.

- 11. The center pad has no electrical function. Soldering down the center pad to the GND is recommended for best thermal dissipation, but is optional.

## Dimensions and Patterns — 7.0 x 5.0 mm<sup>2</sup>

#### Notes

- 12. Top Marking: Y denotes manufacturing origin and XXXX denotes manufacturing lot number. The value of "Y" will depend on the assembly location of the device.

- 13. A capacitor of value 0.1 µF or higher between VDD and GND is required. An additional 10 µF capacitor between VDD and GND is required for the best phase jitter performance.

- 14. The center pad has no electrical function. Soldering down the center pad to the GND is recommended for best thermal dissipation, but is optional.

## **Additional Information**

## **Table 12. Additional Information**

| Document                              | Description                                                                                                                                                           | Download Link                                         |  |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

| ECCN #: EAR99                         | Five character designation used on the commerce Control List (CCL) to identify dual use items for export control purposes.                                            | entify dual                                           |  |

| HTS Classification Code: 8542.39.0000 | A Harmonized Tariff Schedule (HTS) code developed by the World Customs Organization to classify/define internationally traded goods.                                  |                                                       |  |

| Part number Generator                 | Tool used to create the part number based on desired features.                                                                                                        |                                                       |  |

| Manufacturing Notes                   | Tape & Reel dimension, reflow profile and other manufacturing related info                                                                                            | http://www.sitime.com/manufacturing-notes             |  |

| Qualification Reports                 | RoHS report, reliability reports, composition reports                                                                                                                 | http://www.sitime.com/support/quality-and-reliability |  |

| Performance Reports                   | Additional performance data such as phase noise, current consumption and jitter for selected frequencies http://www.sitime.com/support/performance-measurement-report |                                                       |  |

| Termination Techniques                | Termination design recommendations                                                                                                                                    | http://www.sitime.com/support/application-notes       |  |

| Layout Techniques                     | Layout recommendations                                                                                                                                                | http://www.sitime.com/support/application-notes       |  |

| Evaluation Boards                     | SiT6085/6EB rev. 3.0, SiT6085EB rev.3.1 and<br>SiT6097EB rev. 2.0 Evaluation Boards for<br>Differential Oscillators User Manual                                       | https://www.sitime.com/support/user-guides            |  |

## **Revision History**

### **Table 13. Revision History**

| Revision | Release Date | Change Summary                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 09/06/2017   | Final release                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.04     | 04/17/2018   | Added 5032 package Added -40 to 95C and -40 to 105C temperature ranges Corrected minor errors  Added Additional Information Table                                                                                                                                                                                                                                                                                      |

| 1.05     | 07/03/2018   | Performed minor edits and updated Ordering Information.                                                                                                                                                                                                                                                                                                                                                                |

| 1.06     | 10/25/2018   | Removed "Contact SiTime" for ±10 ppm                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.07     | 07/30/2019   | Updated package Dimensions Drawings Updated Table 9 Thermal Considerations for 5032 package Updated Table 3 specification for First Year Aging Added 5, 10, and 20 year aging specs Added Evaluation Boards SiT6085EB reference in Table 12 Rearranged layout, added Description, Block Diagram and TOC Tightened LVDS minimum VOD specification Added HTS code Added low-swing LVPECL package code and specifications |

| 1.08     | 8/17/2019    | Formatting changes                                                                                                                                                                                                                                                                                                                                                                                                     |

SiTime Corporation, 5451 Patrick Henry Drive, Santa Clara, CA 95054, USA | Phone: +1-408-328-4400 | Fax: +1-408-328-4439

© SiTime Corporation 2017-2019. The information contained herein is subject to change at any time without notice. SiTime assumes no responsibility or liability for any loss, damage or defect of a Product which is caused in whole or in part by (i) use of any circuitry other than circuitry embodied in a SiTime product, (ii) misuse or abuse including static discharge, neglect or accident, (iii) unauthorized modification or repairs which have been soldered or altered during assembly and are not capable of being tested by SiTime under its normal test conditions, or (iv) improper installation, storage, handling, warehousing or transportation, or (v) being subjected to unusual physical, thermal, or electrical stress.

Disclaimer: SiTime makes no warranty of any kind, express or implied, with regard to this material, and specifically disclaims any and all express or implied warranties, either in fact or by operation of law, statutory or otherwise, including the implied warranties of merchantability and fitness for use or a particular purpose, and any implied warranty arising from course of dealing or usage of trade, as well as any common-law duties relating to accuracy or lack of negligence, with respect to this material, any SiTime product and any product documentation. Products sold by SiTime are not suitable or intended to be used in a life support application or component, to operate nuclear facilities, or in other mission critical applications where human life may be involved or at stake. All sales are made conditioned upon compliance with the critical uses policy set forth below.

#### CRITICAL USE EXCLUSION POLICY

BUYER AGREES NOT TO USE SITIME'S PRODUCTS FOR ANY APPLICATION OR IN ANY COMPONENTS USED IN LIFE SUPPORT DEVICES OR TO OPERATE NUCLEAR FACILITIES OR FOR USE IN OTHER MISSION-CRITICAL APPLICATIONS OR COMPONENTS WHERE HUMAN LIFE OR PROPERTY MAY BE AT STAKE.

SiTime owns all rights, title and interest to the intellectual property related to SiTime's products, including any software, firmware, copyright, patent, or trademark. The sale of SiTime products does not convey or imply any license under patent or other rights. SiTime retains the copyright and trademark rights in all documents, catalogs and plans supplied pursuant to or ancillary to the sale of products or services by SiTime. Unless otherwise agreed to in writing by SiTime, any reproduction, modification, translation, compilation, or representation of this material shall be strictly prohibited.

单击下面可查看定价,库存,交付和生命周期等信息

>>SiTime