# Si823x Data Sheet

# 0.5 and 4.0 Amp ISOdrivers (2.5 and 5 kV<sub>RMS</sub>)

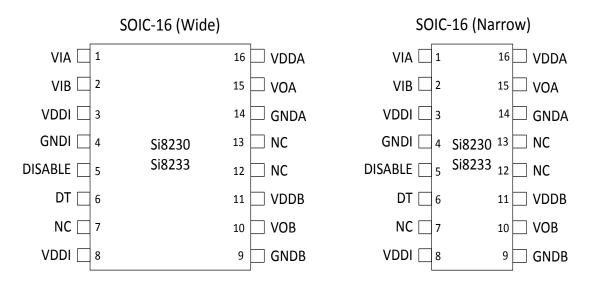

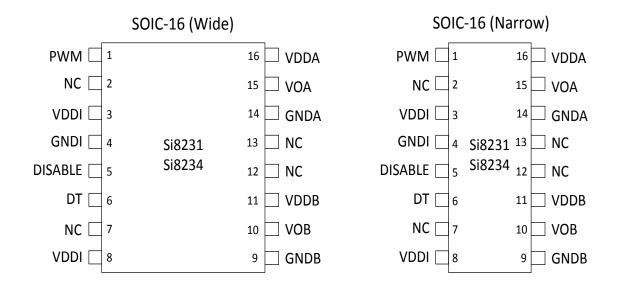

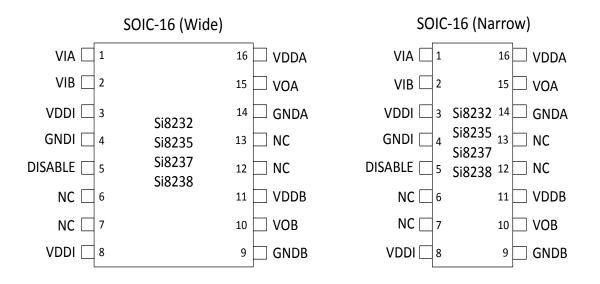

The Si823x isolated driver family combines two independent, isolated drivers into a single package. The Si8230/1/3/4 are high-side/low-side drivers, while the Si8232/5/7/8 are dual drivers. Versions with peak output currents of 0.5 A (Si8230/1/2/7) and 4.0 A (Si8233/4/5/8) are available. All drivers operate with a maximum supply voltage of 24 V.

The Si823x drivers utilize Skyworks' proprietary silicon isolation technology, which provides up to 5 kV<sub>RMS</sub> withstand voltage per UL1577 and fast 45 ns propagation times. Driver outputs can be grounded to the same or separate grounds or connected to a positive or negative voltage. The TTL level compatible inputs with >400 mV hysteresis are available in individual control input (Si8230/2/3/5/7/8) or PWM input (Si8231/4) configurations. High integration, low propagation delay, small installed size, flexibility, and cost-effectiveness make the Si823x family ideal for a wide range of isolated MOS-FET/IGBT gate drive applications.

Automotive Grade is available for certain part numbers. These products are built using automotive-specific flows at all steps in the manufacturing process to ensure the robust-ness and low defectivity required for automotive applications.

## Industrial Applications

- · Power delivery systems

- Motor control systems

- Isolated dc-dc power supplies

- · Lighting control systems

- · Plasma displays

- · Solar and industrial inverters

# Safety Regulatory Approvals

- UL 1577 recognized

- Up to 5000 V<sub>RMS</sub> for 1 minute

- CSA component notice 5A approval

- IEC 60950-1, 62368-1, 60601-1 (reinforced insulation)

- VDE certification conformity

- VDE 0884-10

- EN60950-1 (reinforced insulation)

- · CQC certification approval

- GB4943.1

# **Automotive Applications**

- On-board chargers

- · Battery management systems

- Charging stations

- · Traction inverters

- Hybrid Electric Vehicles

- Battery Electric Vehicles

#### KEY FEATURES

- Two completely isolated drivers in one package

- Up to 5 kV<sub>RMS</sub> input-to-output isolation

- Up to 1500 V<sub>DC</sub> peak driver-to-driver differential voltage

- · HS/LS and dual driver versions

- Up to 8 MHz switching frequency

- 0.5 A peak output (Si8230/1/2/7)

- 4.0 A peak output (Si8233/4/5/8)

- · High electromagnetic immunity

- RoHS-compliant packages:

- SOIC-14/16 wide body

- · SOIC-16 narrow body

- LGA-14

- QFN-14 (pin to pin compatible with LGA-14 packages)

- AEC-Q100 qualification

- Automotive-grade OPNs available

- AIAG compliant PPAP documentation support

- · IMDS and CAMDS listing support

# 1. Ordering Guide

## Industrial and Automotive Grade OPNs

Industrial-grade devices (part numbers having an "-I" in their suffix) are built using well-controlled, high-quality manufacturing flows to ensure robustness and reliability. Qualifications are compliant with JEDEC, and defect reduction methodologies are used throughout definition, design, evaluation, qualification, and mass production steps.

Automotive-grade devices (part numbers having an "-A" in their suffix) are built using automotive-specific flows at all steps in the manufacturing process to ensure robustness and low defectivity. These devices are supported with AIAG-compliant Production Part Approval Process (PPAP) documentation, and feature International Material Data System (IMDS) and China Automotive Material Data System (CAMDS) listing. Qualifications are compliant with AEC-Q100, and a zero-defect methodology is maintained throughout definition, design, evaluation, qualification, and mass production steps.

| Ordering Part Number<br>(OPN) |              |          | Configuration          | Peak<br>Current | UVLO<br>Voltage | Isolation<br>Rating | Package Type           |

|-------------------------------|--------------|----------|------------------------|-----------------|-----------------|---------------------|------------------------|

| Wide Body (WB) Packag         | ge Options   |          |                        |                 |                 |                     |                        |

| Si8230BB-D-IS                 | Si8230BB-AS  | VIA, VIB | High Side/<br>Low Side |                 |                 |                     |                        |

| Si8231BB-D-IS                 | Si8231BB-AS  | PWM      | High Side/<br>Low Side | 0.5 A           | 8 V             |                     |                        |

| Si8232BB-D-IS                 | Si8232BB-AS  | VIA,VIB  | Dual Driver            |                 |                 |                     |                        |

| Si8234CB-D-IS                 | Si8234CB-AS  | PWM      | High Side/<br>Low Side |                 | 10 V            | 2.5 kVrms           | SOIC-16<br>Wide Body   |

| Si8233BB-D-IS                 | Si8233BB-AS  | VIA,VIB  | High Side/<br>Low Side | 4.0 A           |                 |                     |                        |

| Si8234BB-D-IS                 | Si8234BB-AS  | PWM      | High Side/<br>Low Side | _               | 8 V             |                     |                        |

| Si8235BB-D-IS                 | Si8235BB-AS  | VIA,VIB  | Dual Driver            |                 |                 |                     |                        |

| Si8230AB-D-IS                 | Si8230AB-AS  | VIA, VIB | High Side/             |                 |                 |                     |                        |

| Si8231AB-D-IS                 | Si8231AB-AS  | PWM      | Low Side               | 0.5 A           | 5 V             |                     |                        |

| Si8232AB-D-IS                 | Si8232AB-AS  | VIA,VIB  | Dual Driver            |                 |                 | 2.5 kVrms           | SOIC-16                |

| Si8233AB-D-IS                 | Si8233AB-AS  | VIA,VIB  | High Side/             |                 |                 | 2.5 KVIIIIS         | Wide Body              |

| Si8234AB-D-IS                 | Si8234AB-AS  | PWM      | Low Side               | 4.0 A           | 5 V             |                     |                        |

| Si8235AB-D-IS                 | Si8235AB-AS  | VIA,VIB  | Dual Driver            |                 |                 |                     |                        |

| Narrow Body (NB) Pack         | age Options  |          |                        |                 |                 |                     |                        |

| Si8230BB-D-IS1                | Si8230BB-AS1 | VIA,VIB  | High Side/<br>Low Side |                 |                 |                     |                        |

| Si8231BB-D-IS1                | Si8231BB-AS1 | PWM      | High Side/<br>Low Side | 0.5 A           | 8 V             | 2.5 kVrms           | SOIC-16<br>Narrow Body |

| Si8232BB-D-IS1                | Si8232BB-AS1 | VIA,VIB  | Dual Driver            |                 |                 |                     |                        |

# Table 1.1. Si823x Ordering Guide <sup>1, 2, 4</sup>

| Ordering Part Number<br>(OPN) | Automotive OPN <sup>5,6</sup> | Inputs    | Configuration          | Peak<br>Current | UVLO<br>Voltage | Isolation<br>Rating | Package Type           |  |

|-------------------------------|-------------------------------|-----------|------------------------|-----------------|-----------------|---------------------|------------------------|--|

| Si8233BB-D-IS1                | Si8233BB-AS1                  | VIA,VIB   | High Side/<br>Low Side |                 |                 |                     |                        |  |

| Si8234BB-D-IS1                | Si8234BB-AS1                  | PWM       | High Side/<br>Low Side | 4.0 A           | 8 V             | 2.5 kVrms           | SOIC-16<br>Narrow Body |  |

| Si8235BB-D-IS1                | Si8235BB-AS1                  | VIA,VIB   | Dual Driver            | -               |                 |                     |                        |  |

| Si8235BA-D-IS1                | Si8235BA-AS1                  | VIA,VIB   | Dual Driver            | _               |                 | 1.0 kVrms           |                        |  |

| Si8230AB-D-IS1                | Si8230AB-AS1                  | VIA,VIB   | High Side/             |                 |                 |                     |                        |  |

| Si8231AB-D-IS1                | Si8231AB-AS1                  | PWM       | Low Side               | 0.5 A           | 5 V             |                     |                        |  |

| Si8232AB-D-IS1                | Si8232AB-AS1                  | VIA,VIB   | Dual Driver            | _               |                 | 0.5 1) (111         | SOIC-16                |  |

| Si8233AB-D-IS1                | Si8233AB-AS1                  | VIA,VIB   | High Side/             |                 |                 | 2.5 kVrms           | Narrow Body            |  |

| Si8234AB-D-IS1                | Si8234AB-AS1                  | PWM       | Low Side               | 4.0 A           | 5 V             |                     |                        |  |

| Si8235AB-D-IS1                | Si8235AB-AS1                  | VIA,VIB   | Dual Driver            | _               |                 |                     |                        |  |

| Si8230BC-D-IS1                | Si8230BC-AS1                  | VIA,VIB   | High Side/<br>Low Side |                 |                 |                     |                        |  |

| Si8231BC-D-IS1                | Si8231BC-AS1                  | PWM       | High Side/<br>Low Side | 0.5 A           | 8 V             | 3.75 kVrms          | SOIC-16<br>Narrow Body |  |

| Si8232BC-D-IS1                | Si8232BC-AS1                  | VIA,VIB   | Dual Driver            | _               |                 |                     |                        |  |

| Si8233BC-D-IS1                | Si8233BC-AS1                  | VIA,VIB   | High Side/<br>Low Side |                 |                 |                     | SOIC-16<br>Narrow Body |  |

| Si8234BC-D-IS1                | Si8234BC-AS1                  | PWM       | High Side/<br>Low Side | 4.0 A           | 8 V             | 3.75 kVrms          |                        |  |

| Si8235BC-D-IS1                | Si8235BC-AS1                  | VIA,VIB   | Dual Driver            | _               |                 |                     |                        |  |

| Si8235BA-D-IS1                | Si8235BA-AS1                  | VIA,VIB   | Dual Driver            | _               |                 | 1.0 kVrms           |                        |  |

| Si8230AC-D-IS1                | Si8230AC-AS1                  | VIA,VIB   | High Side/             |                 |                 |                     |                        |  |

| Si8231AC-D-IS1                | Si8231AC-AS1                  | PWM       | Low Side               | 0.5 A           | 5 V             |                     |                        |  |

| Si8232AC-D-IS1                | Si8232AC-AS1                  | VIA,VIB   | Dual Driver            | _               |                 | 0.75 ()////         | SOIC-16                |  |

| Si8233AC-D-IS1                | Si8233AC-AS1                  | VIA,VIB   | High Side/             |                 |                 | - 3.75 kVrms        | Narrow Body            |  |

| Si8234AC-D-IS1                | Si8234AC-AS1                  | PWM       | Low Side               | 4.0 A           | 5 V             |                     |                        |  |

| Si8235AC-D-IS1                | Si8235AC-AS1                  | VIA,VIB   | Dual Driver            | -               |                 |                     |                        |  |

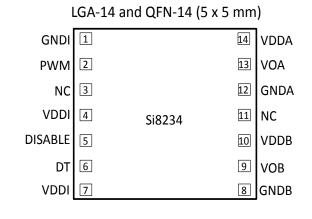

| LGA Package Options           |                               | 1         |                        |                 | I               | 1                   |                        |  |

| Si8233CB-D-IM                 | Si8233CB-AM                   |           |                        |                 | 10 V            |                     |                        |  |

| Si8233BB-D-IM                 | Si8233BB-AM                   | VIA,VIB   |                        |                 | 8 V             | -                   |                        |  |

| Si8233AB-D-IM                 | Si8233AB-AM                   |           | High Side/<br>Low Side |                 | 5 V             | 1                   |                        |  |

| Si8234BB-D-IM                 | Si8234BB-AM                   |           |                        | 4.0 A           | 8 V             | 2.5 kVrms           | LGA-14 5x5 mm          |  |

| Si8234AB-D-IM                 | Si8234AB-AM                   | - PWM     |                        |                 | 5 V             | -                   |                        |  |

| Si8235BB-D-IM                 | Si8235BB-AM                   |           |                        | 1               | 8 V             | 1                   |                        |  |

| Si8235AB-D-IM                 | Si8235AB-AM                   | - VIA,VIB | Dual Driver            |                 | 5 V             | 1                   |                        |  |

| QFN Package Options           |                               | 1         | I                      |                 | I               | 1                   | 1                      |  |

# Si823x Data Sheet • Ordering Guide

| Ordering Part Number<br>(OPN) | Automotive OPN <sup>5,6</sup> | Inputs    | Configuration          | Peak<br>Current | UVLO<br>Voltage | lsolation<br>Rating | Package Type               |

|-------------------------------|-------------------------------|-----------|------------------------|-----------------|-----------------|---------------------|----------------------------|

| Si8233AB-D-IM1                | Si8233AB-AM1                  |           |                        |                 | 5 V             |                     |                            |

| Si8233BB-D-IM1                | Si8233BB-AM1                  | - VIA,VIB | High Side/             |                 | 8 V             |                     |                            |

| Si8234AB-D-IM1                | Si8234AB-AM1                  | - PWM     | Low Side               | 4.0 A           | 5 V             | 2.5 kVrms           | QFN-14                     |

| Si8234BB-D-IM1                | Si8234BB-AM1                  |           |                        | 4.0 A           | 8 V             | - 2.5 KVIIIIS       | QFN-14                     |

| Si8235AB-D-IM1                | Si8235AB-AM1                  |           | Dual Driver            |                 | 5 V             |                     |                            |

| Si8235BB-D-IM1                | Si8235BB-AM1                  | - VIA,VIB | Dual Driver            |                 | 8 V             |                     |                            |

| 5 kV Ordering Options         |                               |           |                        |                 |                 |                     |                            |

| Si8230BD-D-IS                 | Si8230BD-AS                   | VIA, VIB  | High Side/<br>Low Side |                 |                 |                     |                            |

| Si8231BD-D-IS                 | Si8231BD-AS                   | PWM       | High Side/<br>Low Side | 0.5 A           |                 |                     |                            |

| Si8232BD-D-IS                 | Si8232BD-AS                   | VIA, VIB  | Dual Driver            |                 | 0.1/            | 5.0 kVrms           | SOIC-16                    |

| Si8233BD-D-IS                 | Si8233BD-AS                   | VIA, VIB  | High Side/<br>Low Side |                 | 8 V             | 5.0 KVIIIIS         | Wide Body                  |

| Si8234BD-D-IS                 | Si8234BD-AS                   | PWM       | High Side/<br>Low Side | 4.0 A           |                 |                     |                            |

| Si8235BD-D-IS                 | Si8235BD-AS                   | VIA, VIB  | Dual Driver            | _               |                 |                     |                            |

| Si8230AD-D-IS                 | Si8230AD-AS                   | VIA, VIB  | High Side/             |                 |                 |                     |                            |

| Si8231AD-D-IS                 | Si8231AD-AS                   | PWM       | Low Side               | 0.5 A           | 5 V             |                     | SOIC-16<br>Wide Body       |

| Si8232AD-D-IS                 | Si8232AD-AS                   | VIA, VIB  | Dual Driver            | _               |                 | 5.0 kVrms           |                            |

| Si8233AD-D-IS                 | Si8233AD-AS                   | VIA, VIB  | High Side/             |                 |                 |                     |                            |

| Si8234AD-D-IS                 | Si8234AD-AS                   | PWM       | Low Side               | 4.0 A           | 5 V             |                     |                            |

| Si8235AD-D-IS                 | Si8235AD-AS                   | VIA, VIB  | Dual Driver            |                 | 5 V             |                     |                            |

| Si8230AD-D-IS3                | Si8230AD-AS3                  | VIA, VIB  |                        | 0.5 A           |                 |                     |                            |

| Si8230BD-D-IS3                | Si8230BD-AS3                  | VIA, VIB  | High Side/             | 0.5 A           | 8 V             |                     |                            |

| Si8233AD-D-IS3                | Si8233AD-AS3                  | VIA, VIB  | Low Side               |                 | 5 V             |                     | SOIC-14<br>Wide Body       |

| Si8233BD-D-IS3                | Si8233BD-AS3                  | VIA, VIB  |                        | - 4.0 A         | 8 V             |                     | with increased<br>creepage |

| Si8235AD-D-IS3                | Si8235AD-AS3                  | VIA, VIB  | Dual Driver            | 4.0 A           | 5 V             |                     | e.copugo                   |

| Si8235BD-D-IS3                | Si8235BD-AS3                  | VIA, VIB  | Dual Driver            |                 | 8 V             |                     |                            |

| 3 V VDDI Ordering Optic       | ons                           |           |                        |                 |                 |                     |                            |

| Si8237AB-D-IS1                | Si8237AB-AS1                  | VIA, VIB  | Dual Driver            | - 0.5 A         | 5 V             |                     |                            |

| Si8237BB-D-IS1                | Si8237BB-AS1                  | VIA, VIB  | Dual Driver            | - 0.5 A         | 8 V             | 2.5 kVrms           | SOIC-16                    |

| Si8238AB-D-IS1                | Si8238AB-AS1                  | VIA, VIB  | Dual Driver            | - 4.0 A         | 5 V             | 2.5 KVIIIIS         | Narrow Body                |

| Si8238BB-D-IS1                | Si8238BB-AS1                  | VIA, VIB  | Dual Driver            | 4.0 A           | 8 V             |                     |                            |

| Si8237AC-D-IS1                | Si8237AC-AS1                  | VIA, VIB  | Dual Driver            | - 0.5 A         | 5 V             |                     |                            |

| Si8237BC-D-IS1                | Si8237BC-AS1                  | VIA, VIB  | Dual Driver            | 0.5 A           | 8 V             | –<br>– 3.75 kVrms   | SOIC-16                    |

| Si8238AC-D-IS1                | Si8238AC-AS1                  | VIA, VIB  | Dual Driver            | - 4.0 A         | 5 V             |                     | Narrow Body                |

| Si8238BC-D-IS1                | Si8238BC-AS1                  | VIA, VIB  | Dual Driver            | 4.0 A           | 8 V             |                     |                            |

| Ordering Part Number<br>(OPN) | Automotive OPN <sup>5,6</sup> | Inputs   | Configuration | Peak<br>Current | UVLO<br>Voltage | lsolation<br>Rating | Package Type                            |  |

|-------------------------------|-------------------------------|----------|---------------|-----------------|-----------------|---------------------|-----------------------------------------|--|

| Si8237AD-D-IS                 | Si8237AD-AS                   | VIA, VIB | Dual Driver   | 0.5 A           | 5 V             |                     |                                         |  |

| Si8237BD-D-IS                 | Si8237BD-AS                   | VIA, VIB | Dual Driver   | 0.5 A           | 8 V             |                     | SOIC-16<br>Wide Body                    |  |

| Si8238AD-D-IS                 | Si8238AD-AS                   | VIA, VIB | Dual Driver   |                 | 5 V             |                     |                                         |  |

| Si8238BD-D-IS                 | Si8238BD-AS                   | VIA, VIB | Dual Driver   |                 | 8 V             | 5.0 kVrms           |                                         |  |

| Si8238AD-D-IS3                | Si8238AD-AS3                  | VIA, VIB | Dual Driver   | 4.0 A           | 5 V             |                     | SOIC-14                                 |  |

| Si8238BD-D-IS3                | Si8238BD-AS3                  | VIA, VIB | Dual Driver   |                 | 8 V             |                     | Wide Body<br>with increased<br>creepage |  |

1. All packages are RoHS-compliant with peak reflow temperatures of 260 °C according to the JEDEC industry standard classifications and peak solder temperatures.

2. "Si" and "SI" are used interchangeably.

3. An "R" at the end of the part number denotes tape and reel packaging option.

4. The temperature ranges is -40 to +125 °C.

5. Automotive-Grade devices (with an "–A" suffix) are identical in construction materials, topside marking, and electrical parameters to their Industrial-Grade (with an "–I" suffix) version counterparts. Automotive-Grade products are produced utilizing full automotive process flows and additional statistical process controls throughout the manufacturing flow. The Automotive-Grade part number is included on shipping labels.

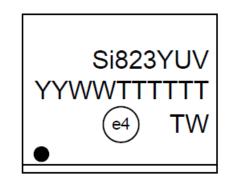

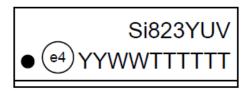

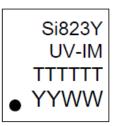

6. In the top markings of each device, the Manufacturing Code represented by either "RTTTTT" or "TTTTTT" contains as its first character a letter in the range N through Z to indicate Automotive-Grade.

# **Table of Contents**

| 1. | Ordering Guide                                                                                                                                                                         | • |   | • | • |   | • | • |   | • | • | • | • | • |   | • | • | . 2        |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------------|

| 2. | System Overview                                                                                                                                                                        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | . 8        |

|    | 2.1 Top Level Block Diagrams                                                                                                                                                           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | . 8        |

|    | 2.2 Functional Description                                                                                                                                                             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .10        |

|    | 2.3 Typical Operating Characteristics (0.5 Amp)                                                                                                                                        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | . 11       |

|    | 2.4 Typical Operating Characteristics (4.0 Amp)                                                                                                                                        |   |   | • |   |   |   |   |   |   |   |   |   |   |   |   |   | .14        |

|    | 2.5 Family Overview and Logic Operation During Startup                                                                                                                                 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

|    | 2.5.1 Products                                                                                                                                                                         |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

|    | 2.6 Power Supply Connections                                                                                                                                                           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

|    | 2.7 Power Dissipation Considerations                                                                                                                                                   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

|    | 2.8 Layout Considerations                                                                                                                                                              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

|    | 2.9 Undervoltage Lockout Operation                                                                                                                                                     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

|    | 2.9.1 Device Startup                                                                                                                                                                   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

|    | 2.9.2 Undervoltage Lockout                                                                                                                                                             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .21        |

|    | 2.9.3 Undervoltage Lockout (UVLO)                                                                                                                                                      |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

|    | 2.9.4 Control Inputs                                                                                                                                                                   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

|    | 2.10 Programmable Dead Time and Overlap Protection                                                                                                                                     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

| 3. | Electrical Specifications                                                                                                                                                              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

| •  | 3.1 Test Circuits                                                                                                                                                                      |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

| 4  | Applications.                                                                                                                                                                          |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

| 4. | 4.1 High-Side/Low-Side Driver                                                                                                                                                          |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

|    | 4.1 High-Side/Low-Side Driver                                                                                                                                                          |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

| _  |                                                                                                                                                                                        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

| 5. | Pin Descriptions                                                                                                                                                                       | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 35         |

| 6. | Package Outlines                                                                                                                                                                       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

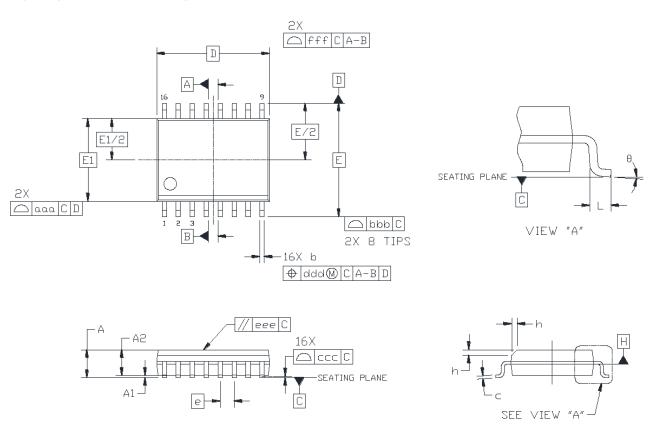

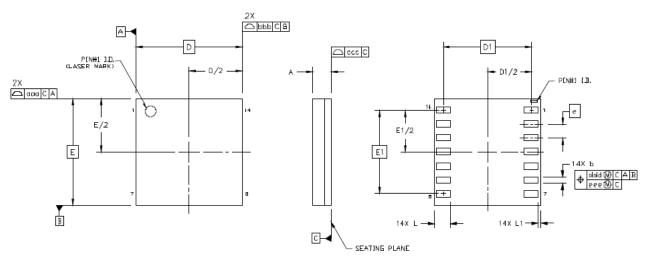

|    | 6.1 Package Outline: 16-Pin Wide Body SOIC                                                                                                                                             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

|    | 6.2 Package Outline: 14-Pin Wide Body SOIC                                                                                                                                             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

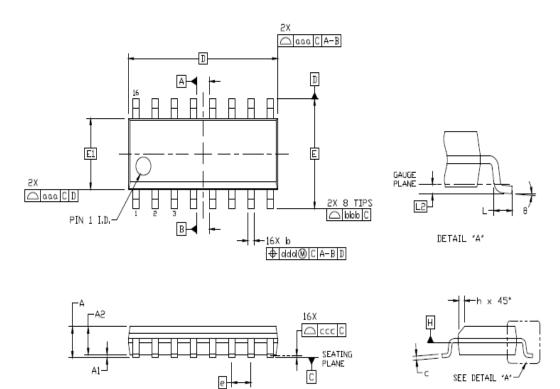

|    | 6.3 Package Outline: 16-Pin Narrow Body SOIC                                                                                                                                           |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

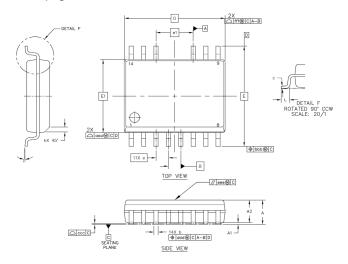

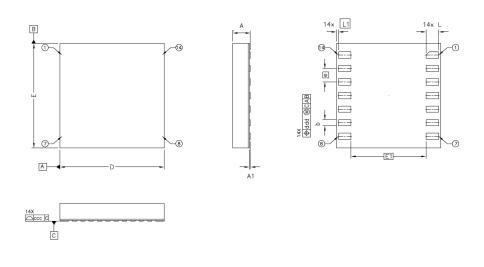

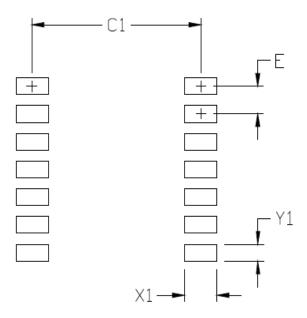

|    | 6.4 Package Outline: 14 LD LGA (5 x 5 mm)                                                                                                                                              |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

|    | 6.5 Package Outline: 14 LD QFN                                                                                                                                                         | • | • | · | • | • | • | • | • | • | • | • | • | • | • | • | • | .47        |

|    |                                                                                                                                                                                        |   |   |   |   |   | _ |   |   |   | _ | _ |   |   |   |   | _ | 48         |

| 7. | Land Patterns                                                                                                                                                                          | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |            |

| 7. | Land Patterns <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<> |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

| 7. |                                                                                                                                                                                        |   |   |   |   |   |   |   |   |   |   |   | • | • |   |   |   | .48        |

| 7. | 7.1 Land Pattern: 16-Pin Wide Body SOIC                                                                                                                                                | • |   |   |   | • |   |   | • | • |   |   |   |   | • |   | • | .48<br>.49 |

| 8. | Top Markings                                      | 2 |

|----|---------------------------------------------------|---|

|    | 8.1 Si823x Top Marking (14/16-Pin Wide Body SOIC) | 2 |

|    | 8.2 Si823x Top Marking (16-Pin Narrow Body SOIC)  | 3 |

|    | 8.3 Si823x Top Marking (14 LD LGA/QFN)            | 1 |

| 9. | Revision History                                  | 5 |

Si823x Data Sheet • System Overview

# 2. System Overview

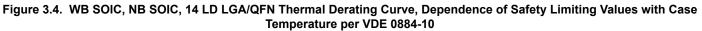

# 2.1 Top Level Block Diagrams

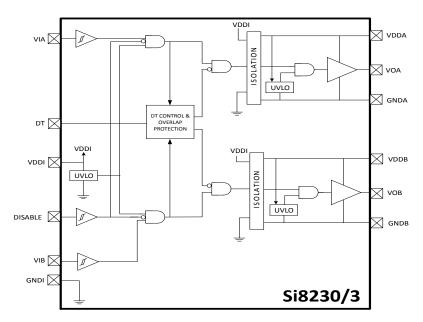

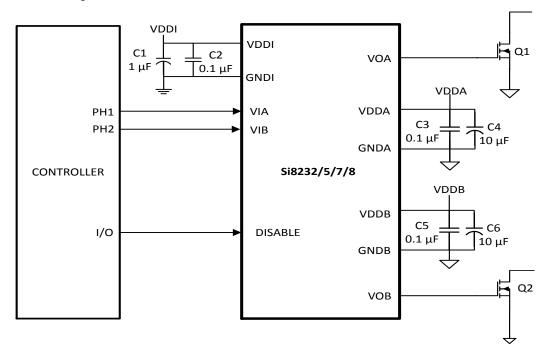

Figure 2.1. Si8230/3 Two-Input High-Side/Low-Side Isolated Drivers

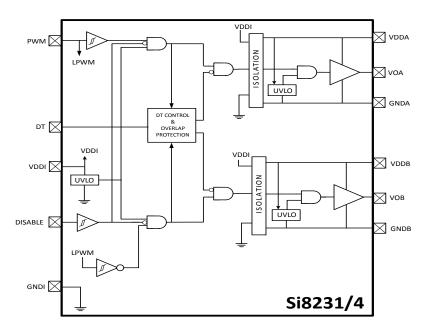

Figure 2.2. Si8231/4 Single-Input High-Side/Low-Side Isolated Drivers

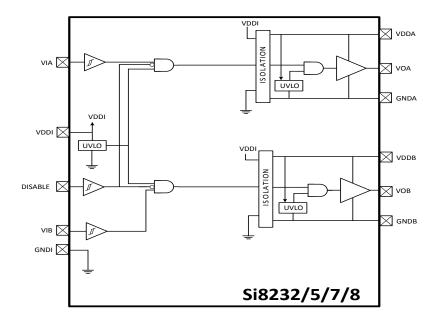

Figure 2.3. Si8232/5/7/8 Dual Isolated Drivers

## 2.2 Functional Description

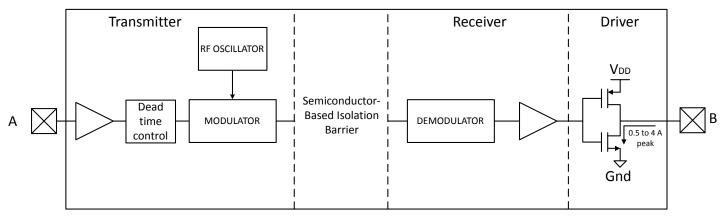

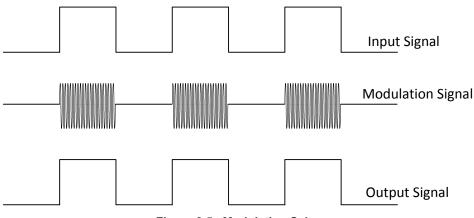

The operation of an Si823x channel is analogous to that of an optocoupler and gate driver, except an RF carrier is modulated instead of light. This simple architecture provides a robust isolated data path and requires no special considerations or initialization at start-up. A simplified block diagram for a single Si823x channel is shown in the figure below.

Figure 2.4. Simplified Channel Diagram

A channel consists of an RF Transmitter and RF Receiver separated by a semiconductor-based isolation barrier. Referring to the Transmitter, input A modulates the carrier provided by an RF oscillator using on/off keying. The Receiver contains a demodulator that decodes the input state according to its RF energy content and applies the result to output B via the output driver. This RF on/off keying scheme is superior to pulse code schemes as it provides best-in-class noise immunity, low power consumption, and better immunity to magnetic fields. See the figure below for more details.

Figure 2.5. Modulation Scheme

#### 2.3 Typical Operating Characteristics (0.5 Amp)

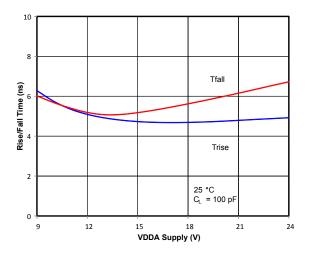

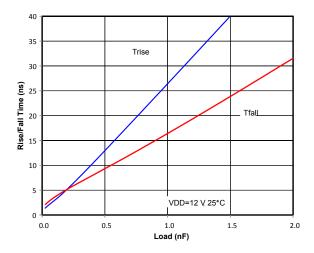

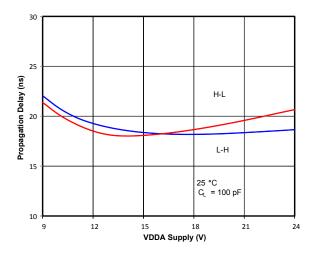

The typical performance characteristics depicted in Figure 2.6 Rise/Fall Time vs. Supply Voltage on page 11 through Figure 2.15 Output Source Current vs. Temperature on page 12 are for information purposes only. Refer to Table 3.1 Electrical Characteristics<sup>1</sup> on page 24 for actual specification limits.

Figure 2.6. Rise/Fall Time vs. Supply Voltage

Figure 2.8. Rise/Fall Time vs. Load

Figure 2.7. Propagation Delay vs. Supply Voltage

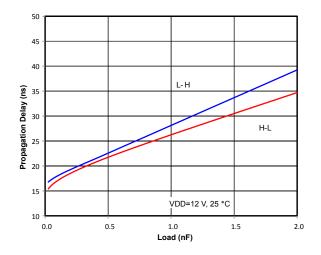

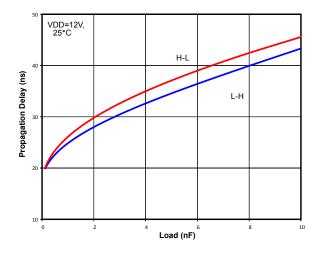

Figure 2.9. Propagation Delay vs. Load

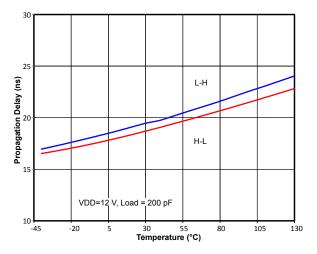

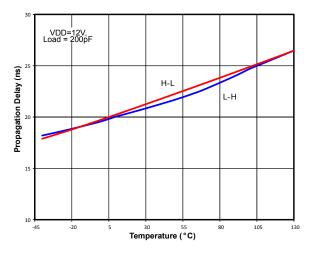

Figure 2.10. Propagation Delay vs. Temperature

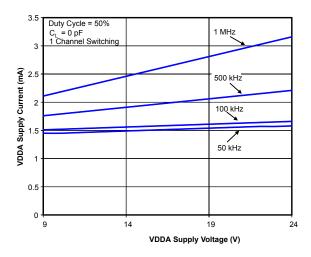

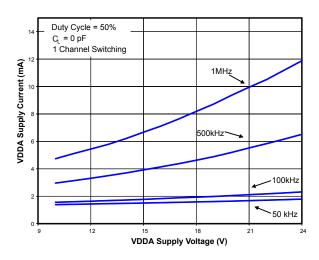

Figure 2.12. Supply Current vs. Supply Voltage

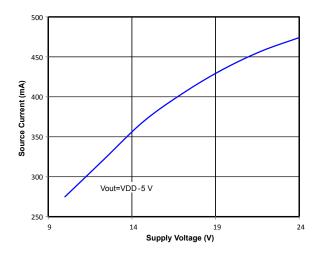

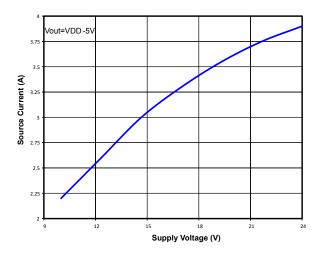

Figure 2.14. Output Source Current vs. Supply Voltage

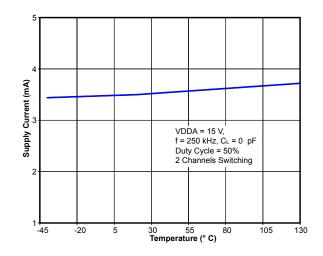

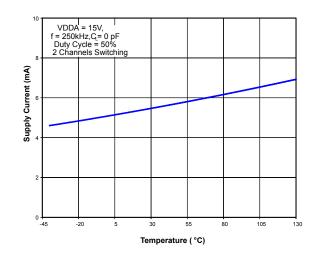

Figure 2.11. Supply Current vs. Temperature

Figure 2.13. Supply Current vs. Supply Voltage

Figure 2.15. Output Source Current vs. Temperature

Figure 2.16. Output Sink Current vs. Supply Voltage

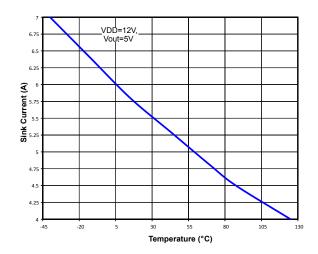

Figure 2.17. Output Sink Current vs. Temperature

## 2.4 Typical Operating Characteristics (4.0 Amp)

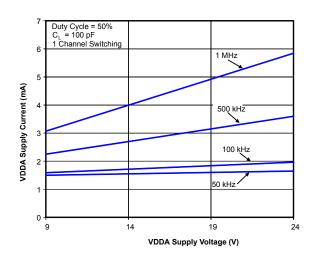

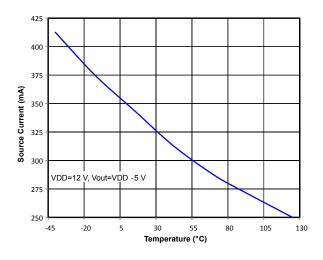

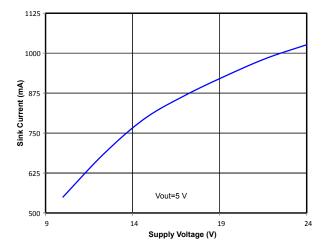

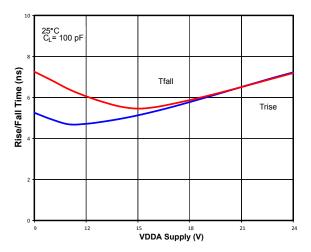

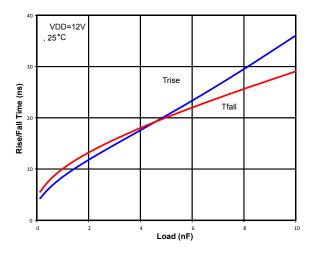

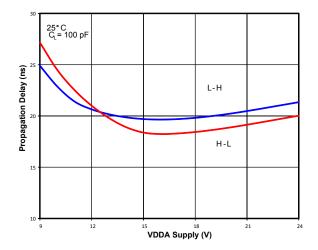

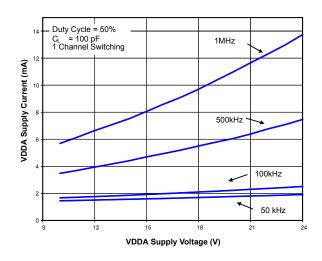

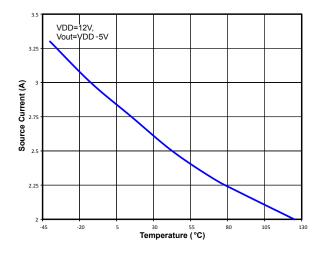

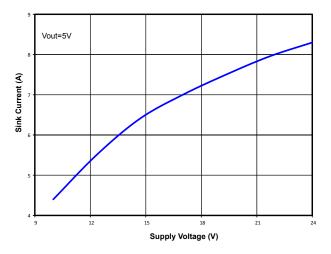

The typical performance characteristics depicted in Figure 2.18 Rise/Fall Time vs. Supply Voltage on page 14 through Figure 2.27 Output Source Current vs. Temperature on page 15 are for information purposes only. Refer to Table 3.1 Electrical Characteristics<sup>1</sup> on page 24 for actual specification limits.

Figure 2.18. Rise/Fall Time vs. Supply Voltage

Figure 2.20. Rise/Fall Time vs. Load

Figure 2.19. Propagation Delay vs. Supply Voltage

Figure 2.21. Propagation Delay vs. Load

Figure 2.22. Propagation Delay vs. Temperature

Figure 2.24. Supply Current vs. Supply Voltage

Figure 2.26. Output Source Current vs. Supply Voltage

Figure 2.23. Supply Current vs. Temperature

Figure 2.25. Supply Current vs. Supply Voltage

Figure 2.27. Output Source Current vs. Temperature

Figure 2.28. Output Sink Current vs. Supply Voltage

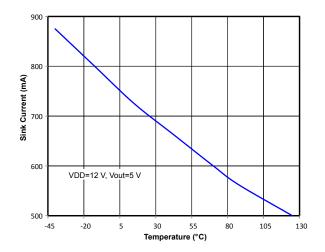

Figure 2.29. Output Sink Current vs. Temperature

## 2.5 Family Overview and Logic Operation During Startup

The Si823x family of isolated drivers consists of high-side, low-side, and dual driver configurations.

## 2.5.1 Products

The table below shows the configuration and functional overview for each product in this family.

| Table 2.1. | Si823x | Family | Overview |

|------------|--------|--------|----------|

|------------|--------|--------|----------|

| Part Number | Configuration      | Overlap Protection | Programmable<br>Dead Time | Inputs   | Peak Output Cur-<br>rent (A) |

|-------------|--------------------|--------------------|---------------------------|----------|------------------------------|

| Si8230      | High-Side/Low-Side | $\checkmark$       | $\checkmark$              | VIA, VIB | 0.5                          |

| Si8231      | High-Side/Low-Side | $\checkmark$       | $\checkmark$              | PWM      | 0.5                          |

| Si8232/7    | Dual Driver        | —                  | —                         | VIA, VIB | 0.5                          |

| Si8233      | High-Side/Low-Side | $\checkmark$       | $\checkmark$              | VIA, VIB | 4.0                          |

| Si8234      | High-Side/Low-Side | $\checkmark$       | $\checkmark$              | PWM      | 4.0                          |

| Si8235/8    | Dual Driver        | —                  | —                         | VIA, VIB | 4.0                          |

# 2.5.2 Device Behavior

The table below consists of truth tables for the Si8230/3, Si8231/4, and Si8232/5/7/8 families.

| Table 2.2. | Si823x | Family | Truth | Table <sup>1</sup> |

|------------|--------|--------|-------|--------------------|

|------------|--------|--------|-------|--------------------|

|                |                |                                   | Si823     | 30/3 (High | i-Side/Lo | w-Side) Truth Table                                                       |

|----------------|----------------|-----------------------------------|-----------|------------|-----------|---------------------------------------------------------------------------|

| Inp            | outs           | VDDI State                        | Disable   | Ou         | tput      | Notes                                                                     |

| VIA            | VIB            |                                   |           | VOA        | VOB       |                                                                           |

| L              | L              | Powered                           | L         | L          | L         | Output transition occurs after internal dead time expires.                |

| L              | Н              | Powered                           | L         | L          | Н         | Output transition occurs after internal dead time expires.                |

| Н              | L              | Powered                           | L         | Н          | L         | Output transition occurs after internal dead time expires.                |

| Н              | н              | Powered                           | L         | L          | L         | Invalid state. Output transition occurs after internal dead time expires. |

| X <sup>2</sup> | X <sup>2</sup> | Unpowered                         | Х         | L          | L         | Output returns to input state within 7 µs of VDDI power restoration.      |

| Х              | Х              | Powered                           | Н         | L          | L         | Device is disabled.                                                       |

| Si8231/4       | (PWM In        | put High-Side/                    | Low-Side) | Truth Tab  | ble       |                                                                           |

| PWM            | Input          | t VDDI State Disable Output Notes |           | Notes      |           |                                                                           |

|                |                |                                   |           | VOA        | VOB       |                                                                           |

| I              | Н              | Powered                           | L         | Н          | L         | Output transition occurs after internal dead time expires.                |

|                | L              | Powered                           | L         | L          | Н         | Output transition occurs after internal dead time expires.                |

| >              | < <sup>2</sup> | Unpowered                         | Х         | L          | L         | Output returns to input state within 7 µs of VDDI power restoration.      |

|                | Х              | Powered                           | Н         | L          | L         | Device is disabled.                                                       |

| Si8232/5       | /7/8 (Dua      | Driver) Truth                     | Table     |            |           |                                                                           |

| Inp            | outs           | VDDI State                        | Disable   | Ou         | tput      | Notes                                                                     |

| VIA            | VIB            | -                                 |           | VOA        | VOB       | -                                                                         |

| L              | L              | Powered                           | L         | L          | L         | Output transition occurs immediately (no internal dead time).             |

| L              | н              | Powered                           | L         | L          | Н         | Output transition occurs immediately (no internal dead time).             |

| Н              | L              | Powered                           | L         | Н          | L         | Output transition occurs immediately (no internal dead time).             |

| Н              | н              | Powered                           | L         | Н          | н         | Output transition occurs immediately (no internal dead time).             |

|                | X <sup>2</sup> | Unpowered                         | Х         | L          | L         | Output returns to input state within 7 µs of VDDI power restoration.      |

| X <sup>2</sup> |                |                                   |           |            |           |                                                                           |

1. This truth table assumes VDDA and VDDB are powered. If VDDA and VDDB are below UVLO, see 2.9 Undervoltage Lockout Operation for more information.

2. Note that an input can power the input die through an internal diode if its source has adequate current.

Si823x Data Sheet • System Overview

#### 2.6 Power Supply Connections

Isolation requirements mandate individual supplies for VDDI, VDDA, and VDDB. The decoupling caps for these supplies must be placed as close to the VDD and GND pins of the Si823x as possible. The optimum values for these capacitors depend on load current and the distance between the chip and the regulator that powers it. Low effective series resistance (ESR) capacitors, such as Tantalum, are recommended.

#### 2.7 Power Dissipation Considerations

Proper system design must assure that the Si823x operates within safe thermal limits across the entire load range. The Si823x total power dissipation is the sum of the power dissipated by bias supply current, internal parasitic switching losses, and power dissipated by the series gate resistor and load. Equation 1 shows total Si823x power dissipation.

$$P_{D} = (V_{DDI})(I_{DDI}) + 2(I_{DD2})(V_{DD2}) + (f)(Q_{G})(V_{DD2})\left[\frac{R_{P}}{R_{P} + R_{G}}\right] + (f)(Q_{G})(V_{DD2})\left[\frac{R_{N}}{R_{N} + R_{G}}\right] + 2fCintV_{DD2}^{2}$$

where:

P<sub>D</sub> is the total Si823x device power dissipation (W)

I<sub>DDI</sub> is the input-side maximum bias current (3 mA)

I<sub>DD2</sub> is the driver die maximum bias current (2.5 mA)

Cint is the internal parasitic capacitance (75 pF for the 0.5 A driver and 370 pF for the 4.0 A driver)

VDDI is the input-side VDD supply voltage (2.7 to 5.5 V)

$V_{DD2}$  is the driver-side supply voltage (10 to 24 V)

f is the switching frequency (Hz)

$\mathsf{Q}_{\mathsf{G}}$  is the gate charge of the FET being driven

R<sub>G</sub> is the external gate resistor

$R_P$  is the  $R_{DS(ON)}$  of the driver pull-up switch: ( $Rp = 15 \Omega$  for the 0.5 A driver;  $Rp = 2.7 \Omega$  for the 4.0 A driver)

$R_N$  is the  $R_{DS(ON)}$  of the driver pull-down switch: (Rn = 5  $\Omega$  for the 0.5 A driver and 1  $\Omega$  for the 4.0 A driver)

#### **Equation 1**

Power dissipation example for 0.5 A driver using Equation 1 with the following givens:

V<sub>DD1</sub> = 5.0 V

V<sub>DD2</sub> = 12 V

f = 350 kHz

$R_G$  = 22  $\Omega$

Q<sub>G</sub> = 25 nC

$$Pd = 0.015 + 0.060 + (350 \times 10^3)(25 \times 10^{-9})(12)(\frac{5}{5+22}) + (350 \times 10^3)(25 \times 10^{-9})(12)(\frac{15}{15+22}) + 2[(350 \times 10^3)(75 \times 10^{-12})(144)] = 145 \text{ mW}$$

Si823x Data Sheet • System Overview

From which the driver junction temperature is calculated using Equation 2, where:

Pd is the total Si823x device power dissipation (W)

θja is the thermal resistance from junction to air (105 °C/W in this example)

T<sub>A</sub> is the ambient temperature

$T_i = P_d \times \Theta_{ia} \times T_A = (0.145)(105) + 20 = 35.2^{\circ}C$

The maximum power dissipation allowable for the Si823x is a function of the package thermal resistance, ambient temperature, and maximum allowable junction temperature, as shown in Equation 2:

$$P_{Dmax} \leq \frac{T_{jmax} - T_A}{\varTheta ja}$$

where:

P<sub>Dmax</sub> = Maximum Si823x power dissipation (W)

T<sub>imax</sub> = Si823x maximum junction temperature (150 °C)

$T_A$  = Ambient temperature (20 °C)

Oja = Si823x junction-to-air thermal resistance (105 °C/W)

# Equation 2

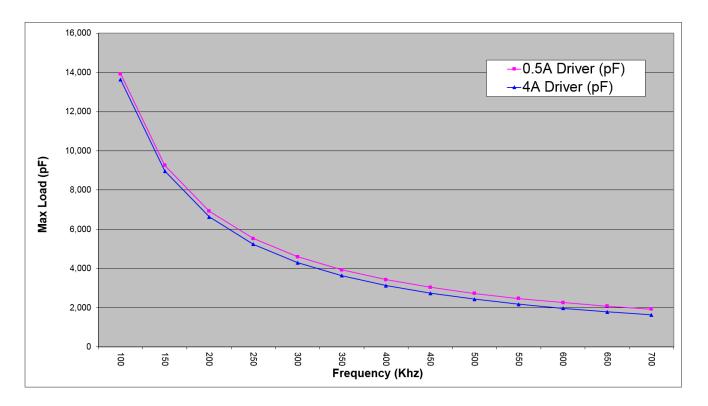

Substituting values for  $P_{Dmax} T_{jmax}$ ,  $T_A$ , and  $\theta_{ja}$  into Equation 2 results in a maximum allowable total power dissipation of 1.29 W. Maximum allowable load is found by substituting this limit and the appropriate data sheet values from Table 3.1 Electrical Characteristics<sup>1</sup> on page 24 into Equation 1 and simplifying. The result is Equation 3 (0.5 A driver) and Equation 4 (4.0 A driver), both of which assume VDDI = 5 V and VDDA = VDDB = 18 V.

$$Q_{G(MAX)} = \frac{0.164}{f} - 3.05 \times 10^{-9}$$

# **Equation 3**

$$Q_{G(MAX)} = \frac{0.634}{f} - 5.81 \times 10^{-9}$$

#### **Equation 4**

Equation 3 and Equation 4 are graphed in the figure below, where the points along the load line represent the package dissipation-limited value of CL for the corresponding switching frequency.

## 2.8 Layout Considerations

It is most important to minimize ringing in the drive path and noise on the Si823x VDD lines. Care must be taken to minimize parasitic inductance in these paths by locating the Si823x as close to the device it is driving as possible. In addition, the VDD supply and ground trace paths must be kept short. For this reason, the use of power and ground planes is highly recommended. A split ground plane system having separate ground and VDD planes for power devices and small signal components provides the best overall noise performance.

## 2.9 Undervoltage Lockout Operation

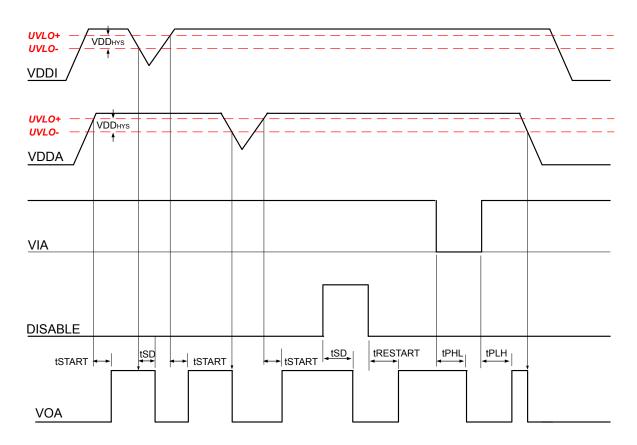

Device behavior during start-up, normal operation and shutdown is shown in Figure 2.30 Device Behavior during Normal Operation and Shutdown on page 21, where UVLO+ and UVLO- are the positive-going and negative-going thresholds respectively. Note that outputs VOA and VOB default low when input side power supply (VDDI) is not present.

## 2.9.1 Device Startup

Outputs VOA and VOB are held low during power-up until VDD is above the UVLO threshold for time period tSTART. Following this, the outputs follow the states of inputs VIA and VIB.

## 2.9.2 Undervoltage Lockout

Undervoltage Lockout (UVLO) is provided to prevent erroneous operation during device startup and shutdown or when VDD is below its specified operating circuits range. The input (control) side, Driver A and Driver B, each have their own undervoltage lockout monitors.

The Si823x input side enters UVLO when VDDI  $\leq$  VDDI<sub>UV-</sub>, and exits UVLO when VDDI > VDDI<sub>UV+</sub>. The driver outputs, VOA and VOB, remain low when the input side of the Si823x is in UVLO and their respective VDD supply (VDDA, VDDB) is within tolerance. Each driver output can enter or exit UVLO independently. For example, VOA unconditionally enters UVLO when VDDA falls below VDDA<sub>UV-</sub> and exits UVLO when VDDA rises above VDDA<sub>UV+</sub>.

Figure 2.30. Device Behavior during Normal Operation and Shutdown

#### 2.9.3 Undervoltage Lockout (UVLO)

The UVLO circuit unconditionally drives VO low when VDD is below the lockout threshold. Upon power up, the Si823x is maintained in UVLO until VDD rises above VDD<sub>UV+</sub>. During power down, the Si823x enters UVLO when VDD falls below the UVLO threshold plus hysteresis (i.e., VDD  $\leq$  VDD<sub>UV+</sub> – VDD<sub>HYS</sub>).

#### 2.9.4 Control Inputs

VIA, VIB, and PWM inputs are high-true, TTL level-compatible logic inputs. A logic high signal on VIA or VIB causes the corresponding output to go high. For PWM input versions (Si8231/4), VOA is high and VOB is low when the PWM input is high, and VOA is low and VOB is high when the PWM input is low.

## 2.9.5 Disable Input

When brought high, the DISABLE input unconditionally drives VOA and VOB low regardless of the states of VIA and VIB. Device operation terminates within tSD after DISABLE = $V_{IH}$  and resumes within tRESTART after DISABLE =  $V_{IL}$ . The DISABLE input has no effect if VDDI is below its UVLO level (i.e., VOA, VOB remain low).

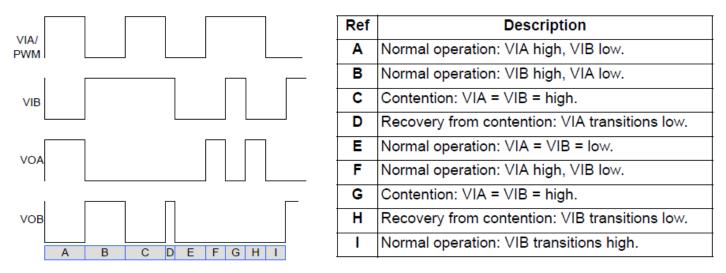

## 2.10 Programmable Dead Time and Overlap Protection

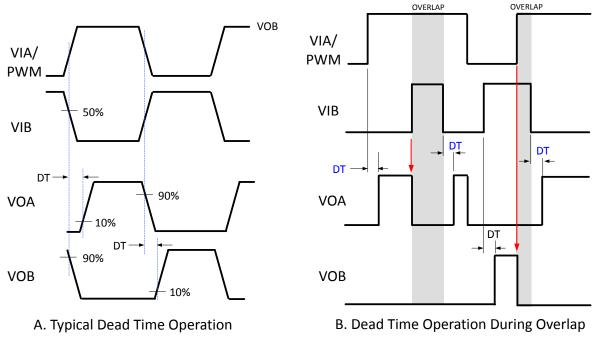

All high-side/low-side drivers (Si8230/1/3/4) include programmable overlap protection to prevent outputs VOA and VOB from being high at the same time. These devices also include programmable dead time, which adds a user-programmable delay between transitions of VOA and VOB. When enabled, dead time is present on all transitions, even after overlap recovery. The amount of dead time delay (DT) is programmed by a single resistor (RDT) connected from the DT input to ground per Equation 5. Note that the dead time pin can be tied to VDDI or left floating to provide a nominal dead time at approximately 400 ps.

DT ≈ 10 × RDT

where:

DT = dead time (ns) and

RDT = dead time programing resistor (k $\Omega$ )

#### **Equation 5**

The device driving VIA and VIB should provide a minimum dead time of TDD to avoid activating overlap protection. Input/output timing waveforms for the two-input drivers are shown in Figure 2.31 Input / Output Waveforms for High-Side / Low-Side Two-Input Drivers on page 22, and dead time waveforms are shown in Figure 2.32 Dead Time Waveforms for High-Side / Low-Side Two-input Drivers on page 23.

Figure 2.31. Input / Output Waveforms for High-Side / Low-Side Two-Input Drivers

# 3. Electrical Specifications

# Table 3.1. Electrical Characteristics<sup>1</sup>

# $2.7 \text{ V} < \text{VDDI} < 5.5 \text{ V}, \text{VDDA} = \text{VDDB} = 12 \text{ V} \text{ or } 15 \text{ V}, \text{ TA} = -40 \text{ to } +125 \text{ °C}, \text{ Typical specs at } 25 \text{ °C}, \text{ T}_{\text{J}} = -40 \text{ to } +150 \text{ °C}$

| Parameter                                       | Symbol                | Test Condition                                                                 | Min                        | Тур  | Мах   | Unit  |

|-------------------------------------------------|-----------------------|--------------------------------------------------------------------------------|----------------------------|------|-------|-------|

| DC Specifications                               |                       |                                                                                |                            |      |       |       |

| Input-side Power Supply                         | VDDI                  | Si8230/1/2/3/4/5                                                               | 4.5                        | _    | 5.5   | V     |

| Voltage                                         |                       | Si8237/8                                                                       | 2.7                        | _    | 5.5   |       |

| Driver Supply Voltage                           | VDDA, VDDB            | Voltage between VDDA and<br>GNDA, and VDDB and GNDB<br>(See 1. Ordering Guide) | 6.5                        | _    | 24    | V     |

| Input Supply Quiescent                          | IDDI(Q)               | Si8230/2/3/5/7/8                                                               | —                          | 2    | 3     | mA    |

| Current                                         |                       | Si8231/4                                                                       | _                          | 3.5  | 5     | mA    |

| Output Supply Quiescent<br>Current              | IDDA(Q), IDDB(Q)      | Current per channel                                                            | _                          |      | 3.0   | mA    |

| Input Supply Active Current                     | IDDI                  | Input freq = 500 kHz, no load                                                  | —                          | 3.5  | _     | mA    |

| Output Supply Active Current                    | IDDA                  | Current per channel with                                                       | —                          | 6    | _     | mA    |

|                                                 | IDDB                  | Input freq = 500 kHz, no load                                                  |                            |      |       |       |

| Input Pin Leakage Current                       | IVIA, IVIB, IPWM      |                                                                                | -10                        | —    | +10   | µA dc |

| Input Pin Leakage Current<br>(Si8230/1/2/3/4/5) | IDISABLE              |                                                                                | -10                        |      | +10   | µA dc |

| Input Pin Leakage Current<br>(Si8237/8)         |                       |                                                                                | -1000                      | _    | +1000 | -     |

| Logic High Input Threshold                      | VIH                   |                                                                                | 2.0                        |      | _     | V     |

| Logic Low Input Threshold                       | VIL                   |                                                                                | —                          | _    | 0.8   | V     |

| Input Hysteresis                                | VI <sub>HYST</sub>    | Si8230/1/2/3/4/5/7/8                                                           | 400                        | 450  | _     | mV    |

| Logic High Output Voltage                       | VOAH, VOBH            | IOA, IOB = -1 mA                                                               | (VDDA /<br>VDDB)<br>— 0.04 | _    | _     | V     |

| Logic Low Output Voltage                        | VOAL, VOBL            | IOA, IOB = 1 mA                                                                | —                          | _    | 0.04  | V     |

| Output Short-Circuit Pulsed<br>Sink Current     | IOA(SCL), IOB(SCL)    | Si8230/1/2/7, Figure 3.1 IOL<br>Sink Current Test Circuit on<br>page 27        | _                          | 0.5  | -     | A     |

|                                                 |                       | Si8233/4/5/8, Figure 3.1 IOL<br>Sink Current Test Circuit on<br>page 27        | _                          | 4.0  | -     | A     |

| Output Short-Circuit Pulsed<br>Source Current   | IOA(SCH),<br>IOB(SCH) | Si8230/1/2/7, Figure 3.2 IOH<br>Source Current Test Circuit on<br>page 27      | -                          | 0.25 | -     | A     |

|                                                 |                       | Si8233/4/5/8, Figure 3.2 IOH<br>Source Current Test Circuit on<br>page 27      | -                          | 2.0  | -     | A     |

| Parameter                            | Symbol                                       | Test Condition                 | Min  | Тур  | Мах  | Unit |

|--------------------------------------|----------------------------------------------|--------------------------------|------|------|------|------|

| Output Sink Resistance               | R <sub>ON(SINK)</sub>                        | Si8230/1/2/7                   | _    | 5.0  | —    | Ω    |

|                                      |                                              | Si8233/4/5/8                   | _    | 1.0  | _    | Ω    |

| Output Source Resistance             | R <sub>ON(SOURCE)</sub>                      | Si8230/1/2/7                   | _    | 15   | _    | Ω    |

|                                      |                                              | Si8233/4/5/8                   | _    | 2.7  | —    | Ω    |

| VDDI Undervoltage Threshold          | VDDI <sub>UV+</sub>                          | VDDI rising (Si8230/1/2/3/4/5) | 3.60 | 4.0  | 4.45 | V    |

| VDDI Undervoltage Threshold          | VDDI <sub>UV-</sub>                          | VDDI falling                   | 3.30 | 3.70 | 4.15 | V    |

|                                      |                                              | (Si8230/1/2/3/4/5)             |      |      |      |      |

| VDDI Lockout Hysteresis              | VDDI <sub>HYS</sub>                          | (Si8230/1/2/3/4/5)             | _    | 250  | _    | mV   |

| VDDI Undervoltage Threshold          | VDDI <sub>UV+</sub>                          | VDDI rising (Si8237/8)         | 2.15 | 2.3  | 2.5  | V    |

| VDDI Undervoltage Threshold          | VDDI <sub>UV-</sub>                          | VDDI falling (Si8237/8)        | 2.10 | 2.22 | 2.40 | V    |

| VDDI Lockout Hysteresis              | VDDI <sub>HYS</sub>                          | (Si8237/8)                     | _    | 75   | _    | mV   |

| VDDA, VDDB Undervoltage<br>Threshold | VDDA <sub>UV+</sub> , VDDB <sub>UV+</sub>    | VDDA, VDDB rising              |      |      |      |      |

| 5 V Threshold                        | _                                            |                                | 5.20 | 5.80 | 6.30 | V    |

| 8 V Threshold                        | _                                            |                                | 7.50 | 8.60 | 9.40 | V    |

| 10 V Threshold                       | _                                            |                                | 9.60 | 11.1 | 12.2 | V    |

| 12.5 V Threshold                     |                                              |                                | 12.4 | 13.8 | 14.8 | V    |

| VDDA, VDDB Undervoltage<br>Threshold | VDDA <sub>UV-</sub> , VDDB <sub>UV-</sub>    | VDDA, VDDB falling             |      |      |      |      |

| 5 V Threshold                        |                                              |                                | 4.90 | 5.52 | 6.0  | V    |

| 8 V Threshold                        |                                              |                                | 7.20 | 8.10 | 8.70 | V    |

| 10 V Threshold                       |                                              |                                | 9.40 | 10.1 | 10.9 | V    |

| 12.5 V Threshold                     |                                              |                                | 11.6 | 12.8 | 13.8 | V    |

| VDDA, VDDB<br>Lockout Hysteresis     | VDDA <sub>HYS</sub> ,<br>VDDB <sub>HYS</sub> | UVLO voltage = 5 V             | _    | 280  | _    | mV   |

| VDDA, VDDB<br>Lockout Hysteresis     | VDDA <sub>HYS</sub> ,<br>VDDB <sub>HYS</sub> | UVLO voltage = 8 V             | —    | 600  | -    | mV   |

| VDDA, VDDB<br>Lockout Hysteresis     | VDDA <sub>HYS</sub> ,<br>VDDB <sub>HYS</sub> | UVLO voltage = 10 V or 12.5 V  | _    | 1000 | -    | mV   |

| AC Specifications                    | 1                                            |                                |      | 1    | 1    | 1    |

| Minimum Pulse Width                  |                                              |                                | _    | 10   | _    | ns   |

| Propagation Delay                    | t <sub>PHL</sub> , t <sub>PLH</sub>          | CL = 200 pF                    | _    | 30   | 45   | ns   |

| Pulse Width Distortion               | PWD                                          |                                | _    | -    | 5.60 | ns   |

| Minimum Overlap Time <sup>2</sup>    | TDD                                          | DT = VDDI, No-Connect          | _    | 0.4  | _    | ns   |

| Parameter                          | Symbol                         | Test Condition                                                                                                                           | Min | Тур | Мах  | Unit  |

|------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|

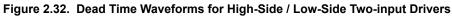

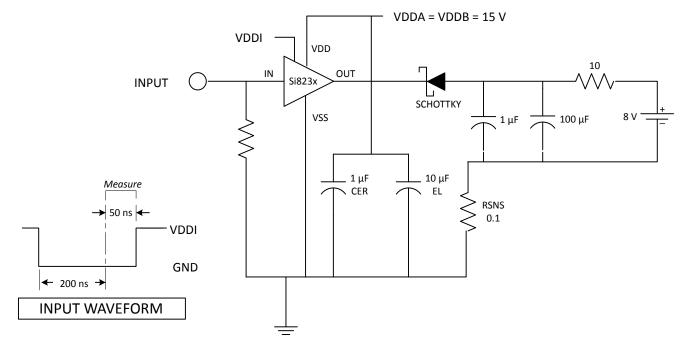

| Programmed Dead Time <sup>3</sup>  | DT                             | Figure 2.32 Dead Time Wave-<br>forms for High-Side / Low-Side<br>Two-input Drivers on page 23,<br>RDT = 100 k                            | 730 | 900 | 1170 | ns    |

|                                    |                                | Figure 2.32 Dead Time Wave-<br>forms for High-Side / Low-Side<br>Two-input Drivers on page 23,<br>RDT = 6 k                              | 55  | 70  | 75   | ns    |

| Output Rise and Fall Time          | t <sub>R</sub> ,t <sub>F</sub> | C <sub>L</sub> = 200 pF (Si8230/1/2/7)                                                                                                   | _   | _   | 20   | ns    |

|                                    |                                | C <sub>L</sub> = 200 pF (Si8233/4/5/8)                                                                                                   | _   | _   | 12   | ns    |

| Shutdown Time from<br>Disable True | t <sub>SD</sub>                |                                                                                                                                          | _   | _   | 60   | ns    |

| Restart Time from<br>Disable False | trestart                       |                                                                                                                                          | _   | _   | 60   | ns    |

| Device Start-up Time               | t <sub>START</sub>             | Time from VDD_ = VDD_UV+ to<br>VOA, VOB = VIA, VIB                                                                                       | _   | _   | 40   | μs    |

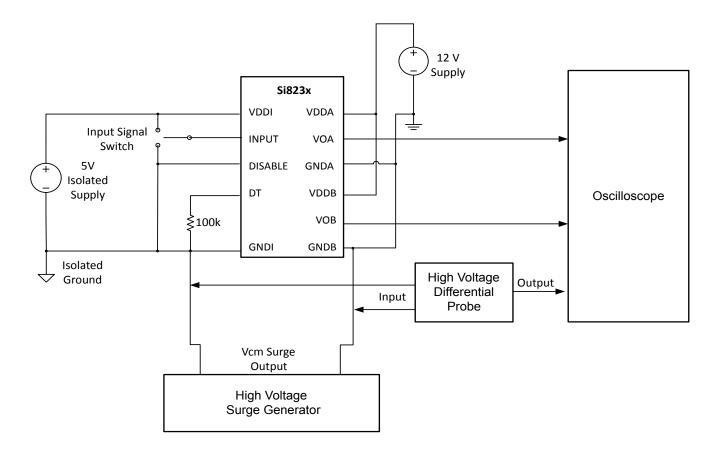

| Common Mode<br>Transient Immunity  | СМТІ                           | VIA, VIB, PWM = VDDI or 0 V<br>V <sub>CM</sub> = 1500 V<br>(see Figure 3.3 Common Mode<br>Transient Immunity Test Circuit<br>on page 28) | 20  | 45  | _    | kV/µs |

2. TDD is the minimum overlap time without triggering overlap protection (Si8230/1/3/4 only).

3. The largest RDT resistor that can be used is 220 k $\Omega.$

# 3.1 Test Circuits

Figures Figure 3.1 IOL Sink Current Test Circuit on page 27, Figure 3.2 IOH Source Current Test Circuit on page 27, and Figure 3.3 Common Mode Transient Immunity Test Circuit on page 28 depict sink current, source current, and common-mode transient immunity test circuits, respectively.

Figure 3.2. IOH Source Current Test Circuit

Figure 3.3. Common Mode Transient Immunity Test Circuit

# Table 3.2. Regulatory Information<sup>1</sup>

## CSA

The Si823x is certified under CSA Component Acceptance Notice 5A. For more details, see Master Contract Number 232873.

60950-1, 62368-1: Up to 600 V<sub>RMS</sub> reinforced insulation working voltage; up to 1000 V<sub>RMS</sub> basic insulation working voltage.

60601-1: Up to 250 V<sub>RMS</sub> working voltage and 2 MOPP (Means of Patient Protection).

VDE

The Si823x is certified according to VDE 0884-10 and EN 60950-1. For more details, see certificates 40018443, 40030763.

0884-10: Up to 891 Vpeak for basic insulation working voltage.

60950-1: Up to 600 V<sub>RMS</sub> reinforced insulation working voltage; up to 1000 V<sub>RMS</sub> basic insulation working voltage.

# UL

The Si823x is certified under UL1577 component recognition program. For more details, see File E257455.

Rated up to 5000  $V_{\text{RMS}}$  isolation voltage for basic protection.

CQC

The Si823x is certified under GB4943.1-2011. For more details, see certificates CQC13001096106, CQC13001096108, and CQC 17001178087.

Rated up to 600  $V_{RMS}$  reinforced insulation working voltage; up to 1000  $V_{RMS}$  basic insulation working voltage.

## Note:

1. Regulatory Certifications apply to 2.5 kV<sub>RMS</sub> rated devices which are production tested to 3.0 kV<sub>RMS</sub> for 1 sec. Regulatory Certifications apply to 3.75 kV<sub>RMS</sub> rated devices which are production tested to 4.5 kV<sub>RMS</sub> for 1 sec. Regulatory Certifications apply to 5.0 kV<sub>RMS</sub> rated devices which are production tested to 6.0 kV<sub>RMS</sub> for 1 sec. Regulatory Certifications for 1 sec. For more information, see 1. Ordering Guide.

|                                                         |                 |                |                                     | Value                                                                          |                                            |      |

|---------------------------------------------------------|-----------------|----------------|-------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------|------|

| Parameter Symbol                                        | Symbol          | Test Condition | WBSOIC-14/16<br>5 kV <sub>RMS</sub> | WBSOIC-14/16<br>NBSOIC-16<br>2.5 kV <sub>RMS</sub> / 3.75<br>kV <sub>RMS</sub> | 14 LD LGA<br>/QFN<br>2.5 kV <sub>RMS</sub> | Unit |

| Nominal External Air<br>Gap<br>(Clearance) <sup>1</sup> | CLR             |                | 8.0                                 | 8.0/4.01                                                                       | 3.5                                        | mm   |

| Nominal External Track-<br>ing (Creepage) <sup>1</sup>  | CPG             |                | 8.0                                 | 8.0/4.01                                                                       | 3.5                                        | mm   |

| Minimum Internal Gap<br>(Internal Clearance)            | DTI             |                | 0.014                               | 0.014                                                                          | 0.014                                      | mm   |

| Tracking Resistance                                     | CTI or PTI      | IEC60112       | 600                                 | 600                                                                            | 600                                        | V    |

| Erosion Depth                                           | ED              |                | 0.019/0.122                         | 0.019/0.122                                                                    | 0.021                                      | mm   |

| Resistance<br>(Input-Output) <sup>2</sup>               | R <sub>IO</sub> |                | 10 <sup>12</sup>                    | 10 <sup>12</sup>                                                               | 10 <sup>12</sup>                           | Ω    |

| Capacitance<br>(Input-Output) <sup>2</sup>              | C <sub>IO</sub> | f = 1 MHz      | 1.4                                 | 1.4                                                                            | 1.4                                        | pF   |

| Input Capacitance <sup>3</sup>                          | CI              |                | 4.0                                 | 4.0                                                                            | 4.0                                        | pF   |

# Table 3.3. Insulation and Safety-Related Specifications

## Notes:

1. The values in this table correspond to the nominal creepage and clearance values as detailed in 6.1 Package Outline: 16-Pin Wide Body SOIC, 6.2 Package Outline: 14-Pin Wide Body SOIC, 6.3 Package Outline: 16-Pin Narrow Body SOIC, 6.4 Package Outline: 14 LD LGA (5 x 5 mm), 6.5 Package Outline: 14 LD QFN. VDE certifies the clearance and creepage limits as 4.7 mm minimum for the NB SOIC and 8.5 mm minimum for the WB SOIC package. UL does not impose a clearance and creepage minimum for component level certifications. CSA certifies the clearance and creepage of the WB SOIC package with designation "IS3" as 8 mm minimum. CSA certifies the clearance and creepage limits as 3.9 mm minimum for the NB SOIC and 7.6 mm minimum for the WB SOIC package with package designation "IS" as listed in the data sheet.

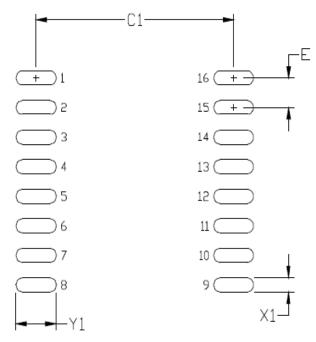

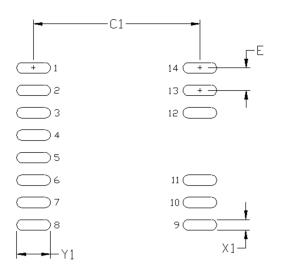

2. To determine resistance and capacitance, the Si823x is converted into a 2-terminal device. Pins 1–8 (1–7, 14 LD LGA/QFN) are shorted together to form the first terminal and pins 9–16 (8–14, 14 LD LGA/QFN) are shorted together to form the second terminal. The parameters are then measured between these two terminals.

3. Measured from input pin to ground.

| Table 3.4. | IEC 60664-1 | Ratings |

|------------|-------------|---------|

|------------|-------------|---------|

| Parameter                   | Test Condition                              | S             |            |                  |

|-----------------------------|---------------------------------------------|---------------|------------|------------------|

|                             |                                             | WB SOIC-14/16 | NB SOIC-16 | 14 LD<br>LGA/QFN |

| Basic Isolation Group       | Material Group                              | I             | I          | I                |

| Installation Classification | Rated Mains Voltages < 150 V <sub>RMS</sub> | I-IV          | I-IV       | I-IV             |

|                             | Rated Mains Voltages < 300 V <sub>RMS</sub> | I-IV          | 1-111      | I-III            |

|                             | Rated Mains Voltages < 400 V <sub>RMS</sub> | 1-111         | I-II       | 1-11             |

|                             | Rated Mains Voltages < 600 $V_{RMS}$        | I-III         | I-II       | I-II             |

# Table 3.5. VDE 0884-10 Insulation Characteristics<sup>1</sup>

|                                                     |                   |                                                                                                                                              | Charac           | teristic                    |        |

|-----------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------|--------|

| Parameter                                           | Symbol            | Test Condition                                                                                                                               | WB<br>SOIC-14/16 | NB SOIC-16<br>14 LD LGA/QFN | Unit   |

| Maximum Working Insula-<br>tion Voltage             | V <sub>IORM</sub> |                                                                                                                                              | 891              | 560                         | V peak |

| Input to Output Test Volt-<br>age                   | V <sub>PR</sub>   | Method b1<br>(V <sub>IORM</sub> x 1.875 = V <sub>PR</sub> ,<br>100%<br>Production Test, t <sub>m</sub> = 1 sec,<br>Partial Discharge < 5 pC) | 1671             | 1050                        | V peak |

| Transient Overvoltage                               | V <sub>IOTM</sub> | t = 60 s                                                                                                                                     | 6000             | 4000                        | V peak |

| Surge Voltage                                       | V <sub>IOSM</sub> | Tested per IEC 60065 with<br>surge voltage of 1.2 μs/50<br>μs<br>Si823xxB/C/D tested with<br>4000 V                                          | 3077             | 3077                        | V peak |

| Pollution Degree (DIN VDE<br>0110, Table 1)         |                   |                                                                                                                                              | 2                | 2                           |        |

| Insulation Resistance at $T_{S}$ , $V_{IO}$ = 500 V | R <sub>S</sub>    |                                                                                                                                              | >10 <sup>9</sup> | >10 <sup>9</sup>            | Ω      |

| *Note:                                              |                   | 1                                                                                                                                            |                  | 1                           |        |

1. Maintenance of the safety data is ensured by protective circuits. The Si823x provides a climate classification of 40/125/21.

| Parameter                                  | Symbol         | Test<br>Condition                                                                                                                                                                                                                                          | WB SOIC-14/16 | NB SOIC-16 | 14 LD<br>LGA/QFN | Unit |

|--------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|------------------|------|

| Case<br>Temperature                        | Τ <sub>S</sub> |                                                                                                                                                                                                                                                            | 150           | 150        | 150              | °C   |

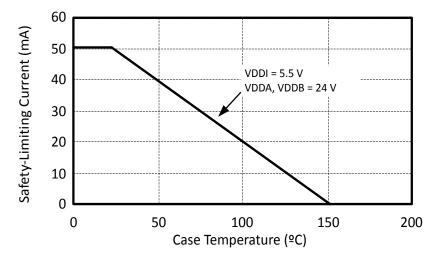

| Safety Input Current                       | I <sub>S</sub> | $\begin{array}{l} \theta_{JA} = 100 \ ^{\circ}C/W \ (WB \ SO-IC-14/16), \\ 105 \ ^{\circ}C/W \ (NB \ SOIC-16, \\ 14 \ LD \ LGA/QFN) \\ V_{DDI} = 5.5 \ V, \\ V_{DDA} = V_{DDB} = 24 \ V, \\ T_{J} = 150 \ ^{\circ}C, \ T_{A} = 25 \ ^{\circ}C \end{array}$ | 50            | 50         | 50               | mA   |

| Device Power Dissipa-<br>tion <sup>2</sup> | P <sub>D</sub> |                                                                                                                                                                                                                                                            | 1.2           | 1.2        | 1.2              | W    |

# Table 3.6. VDE 0884-10 Safety Limiting Values<sup>1</sup>

1. Maximum value allowed in the event of a failure. Refer to the thermal derating curve in Figures Figure 3.4 WB SOIC, NB SOIC, 14 LD LGA/QFN Thermal Derating Curve, Dependence of Safety Limiting Values with Case Temperature per VDE 0884-10 on page 31.

2. The Si82xx is tested with  $V_{DDI}$  = 5.5 V,  $V_{DDA}$  =  $V_{DDB}$  = 24 V,  $T_{J}$  = 150 °C,  $C_{L}$  = 100 pF, input 2 MHz 50% duty cycle square wave.

| Table 3.7. | Thermal | Characteristics |

|------------|---------|-----------------|

|            |         |                 |

| Parameter                                | Symbol        | WB<br>SOIC-14/16 | NB<br>SOIC-16 | 14 LD LGA/QFN | Unit |

|------------------------------------------|---------------|------------------|---------------|---------------|------|

| IC Junction-to-Air<br>Thermal Resistance | $\theta_{JA}$ | 100              | 105           | 105           | °C/W |

# Table 3.8. Absolute Maximum Ratings<sup>1</sup>