# SC8721A High Efficiency, Synchronous, Buck-Boost Converter with Four Integrated MOSFET

# 1 Descriptions

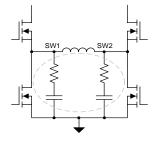

SC8721A is a synchronous 4-switch buck-boost converter with four integrated switches. It is able to effectively output voltage no matter it is higher, lower or equal to the input voltage.

SC8721A supports very wide input and output voltage range. It can support applications from 2.7V to 22V input range and 2.7V to 22V output range. Through its I2C interface, user can program the output voltage and output current limit and switching frequency. VINREG voltage can be adjusted by external resistor.

SC8721A employs current-mode control and supports output current limit, dynamic output voltage adjustment, internal current limit, output short protection and over temperature protections to ensure safety under different abnormal conditions.

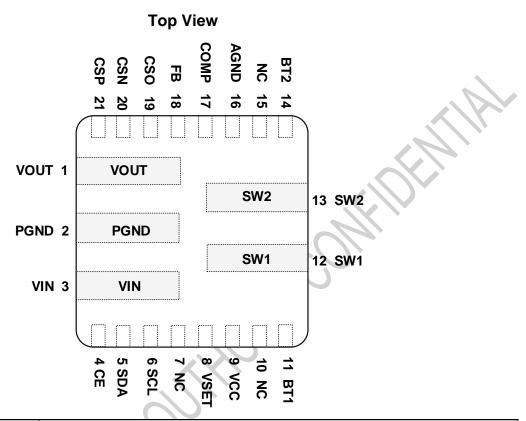

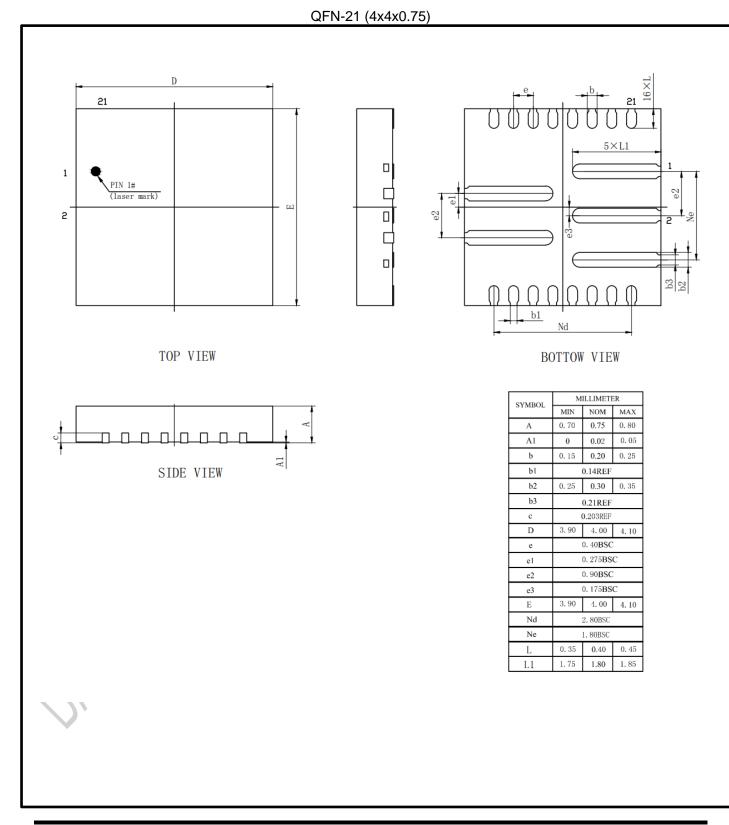

The IC is in a 21 pin 4x4 QFN package.

# 3 Applications

- USB Power Delivery

- Wall Adapter

- Type C Hub

- Industry Power Supplies

# 2 Features

- High Efficiency Buck-Boost Conversion

- Integrated Switches, 10 mΩ for Q1/4, 20 mΩ for Q2/3

- Wide VIN Range: 2.7 V to 22 V, 25V sustainable

- Wide VOUT Range: 2.7 V to 22 V, 25V sustainable

- Dynamic Output Voltage Control

- Adjustable Switching Frequency

- Output Voltage Cable Drop Compensation

- I2C Programmable Output Voltage

- I2C Programmable Output Current Limit

- Output Current Monitor

- Under Voltage Protection, Over Voltage Protection, Over Current Protection

- Short Protection

- Thermal Shutdown Protection

- QFN-21 4 x 4 Package

# 4 Device Information

| Part Number | Package    | Dimension              |  |

|-------------|------------|------------------------|--|

| SC8721AQFER | 21 pin QFN | 4.0mm x 4.0mm x 0.75mm |  |

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

# 5 Typical Application Circuit

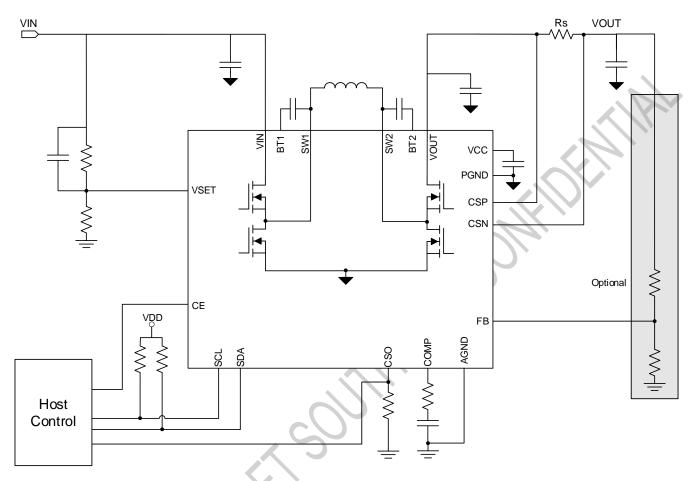

### Typical application circuit 1. current sense at VOUT

Copyright © 2019, Southchip Semiconductor Technology (Shanghai) Co., Ltd.

, other

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

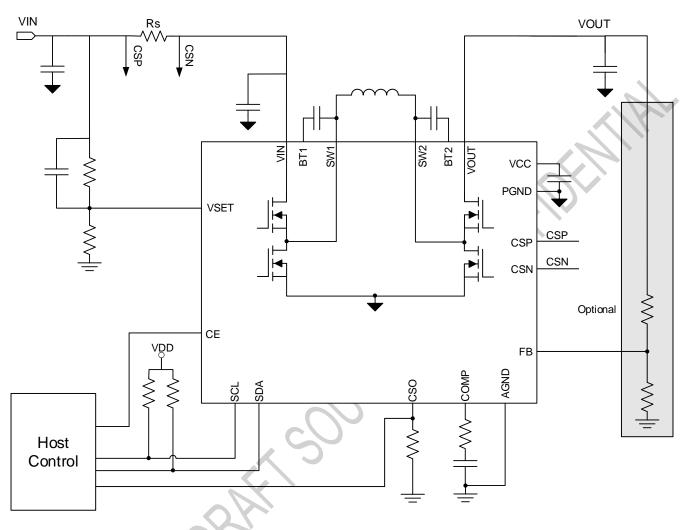

Typical application circuit 2. current sense at VIN

**Note:** User can place current sense resistor at VIN or VOUT according to application requirement. SC8721A constantly regulates the sense resistor current at setting value, which is decided by internal register and CSO resistor. Please refer to **Output Current Limit** for current setting specification.

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

# 6 Terminal Configuration and Functions

| TER    | MINAL | 1/0 | DESCRIPTION                                                                                                                                                             |

|--------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER | NAME  | 1/0 | DESCRIPTION                                                                                                                                                             |

| 1      | VOUT  | I/O | The power output node of the converter.                                                                                                                                 |

| 2      | PGND  | I/O | Power ground. User shall connect PGND and AGND together on PCB.                                                                                                         |

| 3      | VIN   | I/O | the power input node of the converter.                                                                                                                                  |

| 4      | CE    |     | Chip enable pin, active high: pull this pin to logic low to disable the chip. This pin is internally pulled high.                                                       |

| 5      | SDA   | I/O | I2C interface data. Connect SDA to the logic rail through a pull up resistor (typical 10 k $\Omega$ ).                                                                  |

| 6      | SCL   | I   | I2C interface clock. Connect SCL to the logic rail through a pull up resistor (typical 10 k $\Omega$ ).                                                                 |

| 7      | NC    |     | Must be floating                                                                                                                                                        |

| 8      | VSET  | Ю   | VINREG internal 1.2V voltage reference. Set the VINREG voltage by resistor divider from to this pin                                                                     |

| 9      | VCC   | 0   | Output of an internal regulator. Connect a 2.2 $\mu$ F ceramic capacitor from VCC to PGND pin close to the IC. The regulator provides supply for internal gate drivers. |

SOUTHCHIP SOUTHCHIP SEMICONDUCTOR

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

| 10 | NC   |     | Must be floating                                                                                                                                           |

|----|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | BT1  | I   | Connect a 100nF ceramic capacitor between BT1 pin and SW1 pin to provide the boosted bias voltage for high side gate driver.                               |

| 12 | SW1  | I/O | Switching Node 1. Connect to inductor.                                                                                                                     |

| 13 | SW2  | I/O | Switching Node 2. Connect to inductor.                                                                                                                     |

| 14 | BT2  | I   | Connect a 100nF ceramic capacitor between BT2 pin and SW2 pin to provide the boosted bias voltage for high side gate driver.                               |

| 15 | NC   |     |                                                                                                                                                            |

| 16 | AGND | I/O | Analog ground. User shall connect PGND and AGND together on PCB.                                                                                           |

| 17 | COMP | I   | Connect a RC network to compensate the control loop.                                                                                                       |

| 18 | FB   | I   | Feedback node of VOUT output voltage. Set the VOUT output voltage by the resistor divider connected at this pin.                                           |

| 19 | CSO  | 0   | Use this pin to monitor the current sensed by CSP and CSN pin. The voltage of CSO is proportional to the sense current.                                    |

| 20 | CSN  | I   | Negative input of an internal current sense amplifier. Connect a current sense resistor (typical 10 m $\Omega$ ) between CSP and CSN to sense the current. |

| 21 | CSP  | I   | Positive input of an internal current sense amplifier. Connect a current sense resistor (typical 10 m $\Omega$ ) between CSP and CSN to sense the current. |

Chillippine in Car and C

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                           |                                         |     | MIN  | MAX | Unit |

|-------------------------------------------|-----------------------------------------|-----|------|-----|------|

|                                           | CE, SDA, SCL, CSEL, VSET, COMP, CSO, FB |     | -0.3 | 5.5 | V    |

| Voltage range at                          | VCC                                     |     | -0.3 | 6.5 | V    |

| Voltage range at terminals <sup>(2)</sup> | VIN, VOUT, CSP, CSN                     |     | -0.3 | 25  | V    |

|                                           | SW1, SW2                                |     | -0.3 | 25  | V    |

|                                           | BT1, BT2                                |     | -0.3 | 32  | V    |

|                                           | CSP to CSN                              |     | -10  | 10  | V    |

|                                           | BT1 to SW1, BT2 to SW2                  | C   | -0.3 | 6.5 | V    |

| TJ                                        | Operating junction temperature range    | C / | -40  | 150 | °C   |

| T <sub>stg</sub>                          | Storage temperature range               | 00  | -65  | 150 | °C   |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

# 7.2 Thermal Information(TBD)

| THERMAL RESISTA | NCE <sup>(1)</sup>                     | QFN-21 (4mmX4mm) | UNIT |

|-----------------|----------------------------------------|------------------|------|

| θ <sub>JA</sub> | Junction to ambient thermal resistance | TBD              | °C/W |

| θ <sub>JC</sub> | Junction to case resistance            | TBD              | °C/W |

(1) Measured on JESD51-7, 4-layer PCB.

# 7.3 Handling Ratings

| PARAMETER          | DEFINITION                                                   | MIN  | MAX | UNIT |

|--------------------|--------------------------------------------------------------|------|-----|------|

| ESD <sup>(1)</sup> | Human body model (HBM) ESD stress voltage <sup>(2)</sup>     | -2   | 2   | kV   |

| LOD                | Charged device model (CDM) ESD stress voltage <sup>(3)</sup> | -750 | 750 | V    |

(1) Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

(2) Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(3) Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.4 Recommended Operating Conditions

|      |                    | MIN | МАХ | UNIT |

|------|--------------------|-----|-----|------|

| VIN  | VIN voltage range  | 2.7 | 22  | V    |

| VOUT | VOUT voltage range | 2.7 | 22  | V    |

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

|      | VIN Capacitance, VOUT capacitance | 30   |    | μF |

|------|-----------------------------------|------|----|----|

| L    | Inductance                        | 2.2  | 10 | μH |

| Rs   | Current Sense Resistor            | 5    | 10 | mΩ |

| Rcso | Current Limit setting resistor    |      | 64 | КΩ |

|      | HILL BAR                          | CONF |    |    |

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

# 7.5 Electrical Characteristics(TBD)

$T_J$ = 25°C and VIN = 12V, Rs=10m $\Omega$ , Rcso=64k $\Omega$  unless otherwise noted.

| PARAMETE              | R                                  | TEST CONDITIONS                              | MIN  | ТҮР               | MAX  | UNIT |

|-----------------------|------------------------------------|----------------------------------------------|------|-------------------|------|------|

| SUPPLY VC             | DLTAGE                             |                                              |      |                   |      |      |

|                       | VIN under-voltage lockout          | Rising edge                                  |      | 2.5               |      | V    |

| V <sub>UVLO</sub>     | threshold                          | Hysteresis                                   |      | 160               |      | mV   |

| Ι <sub>Q</sub>        | Quiescent current into VIN         | VIN = 8V, VOUT = 5V<br>CE = H, non-switching | 1.5  |                   | mA   |      |

| ISHUTDOWN             | Shutdown current VIN               | VIN = 8V, CE = L                             |      | 5.5               |      | μA   |

| ISTANDBY              | Standby current from VIN           | VIN=8V, Standby mode, CE=H                   |      | 30                |      | μA   |

| VCC, DIRVE            | ER AND POWER SWITCH                |                                              |      | $\langle \rangle$ |      |      |

|                       |                                    | VIN = 9V                                     | 4.4  | 5                 | 5.5  | V    |

| Vcc                   | VCC regulation voltage             | VIN= 5V, ICC = 30mA                          | 4    |                   |      | V    |

| I <sub>VCC_LIM</sub>  | VCC current limit                  | VIN = 9V, VCC = 4V                           |      | 80                |      | mA   |

| R <sub>DSon_HS</sub>  | High side MOS on resistance        |                                              |      | 10                |      | mΩ   |

| R <sub>DSon_LS</sub>  | Low side MOS on resistance         |                                              |      | 20                |      | mΩ   |

| REFERENC              | E VOLTAGE FOR VOUT                 |                                              |      |                   |      |      |

| V <sub>FB</sub>       | FB reference voltage               |                                              | 0.99 | 1                 | 1.01 | V    |

| V <sub>FB_OVP</sub>   | FB OVP threshold, over FB target   | Rising edge                                  |      | 110%              |      |      |

| _ 1                   |                                    | Hysteresis                                   |      | 2%                |      |      |

| VINOVP                | Absolute OVP threshold for VIN     |                                              |      | 22                |      | V    |

| V <sub>SHORT</sub>    | Short circuit detection threshold  |                                              |      | 0.7               |      | V    |

| $V_{INREG_REF}$       | VSET reference voltage             |                                              |      | 1.2               |      | V    |

| CURRENT               |                                    |                                              | -    |                   |      | -    |

| I <sub>LIM</sub>      | Output current limit accuracy      | I <sub>OUT</sub> R <sub>S</sub> ≥ 20mV       | -5%  |                   | 5%   |      |

| I <sub>OCP</sub>      | Internal current limit             |                                              |      | 10                |      | А    |

| ERROR AM              | PLIFIER                            |                                              |      |                   |      |      |

| Gm <sub>EA</sub>      | Error amplifier gm                 |                                              |      | 0.16              |      | mS   |

| Rout                  | Error amplifier output resistance  |                                              |      | 20                |      | MΩ   |

| ISINK_COMP            | COMP sink current                  |                                              |      | 27                |      | μA   |

| I <sub>SRC_COMP</sub> | COMP source current                |                                              |      | 16                |      | μA   |

| I <sub>BIAS_FB</sub>  | FB pin input bias current          | FB in regulation                             |      |                   | 50   | nA   |

| LOGIC CON             | ITROL                              |                                              | •    |                   |      | •    |

| R <sub>PH</sub>       | CE pin internal pull high resistor |                                              |      | 2                 |      | MΩ   |

| VIL                   | CE pin input low voltage           |                                              |      |                   | 0.4  | V    |

| V <sub>IH</sub>       | CE pin input high voltage          |                                              | 1.2  |                   |      | V    |

| Frequency             |                                    | 1                                            |      |                   |      |      |

| F <sub>sw</sub>       | Switching frequency                | REG08 = 0x00                                 |      | 260               |      | kHz  |

# SOUTHCHIP SOUTHCHIP SEMICONDUCTOR

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

|                                        | REG08 = 0x01(default)     | 500 | kHz       |

|----------------------------------------|---------------------------|-----|-----------|

|                                        | REG08 = 0x02              | 720 | kHz       |

|                                        | REG08 = 0x03              | 920 | kHz       |

|                                        |                           |     |           |

| ternal soft-start time                 | From 10% to 90% VOUT      | 15  | ms        |

| (SDA, SCL)                             |                           |     | $\square$ |

| DA/SCL logic low input voltage<br>vel  | V <sub>PULL_UP</sub> = 3V | 0.4 | v         |

| DA/SCL logic high input voltage<br>/el | V <sub>PULL_UP</sub> = 3V | 2   | V         |

| DA sink current                        | V <sub>SDA</sub> = 0.4 V  | 20  | mA        |

| C clock frequency                      |                           | 400 | kH        |

| TDOWN                                  |                           |     |           |

| ermal shutdown temperature (1)         |                           | 160 | °C        |

| ermal shutdown hysteresis (1)          | ~                         | 30  | °C        |

|                                        |                           |     |           |

| S                                      |                           |     |           |

|                                        |                           |     |           |

# 8 Feature Description

# 8.1 Chip Enable

The IC is enabled or disabled by CE signal. When CE input is logic high, the IC is enabled; when CE input is logic low, the IC is disabled. The CE pin is pulled high by 2 M $\Omega$  resistor internally.

### 8.2 Soft Start

The IC implements soft start feature to prevent inrush current during startup in discharging mode. After the discharging mode is enabled, the IC ramps up the internal reference voltage in around 15ms. The output voltage follows the reference, so it starts up slowly. Meantime, the IC ramps up the current limits during the startup. If a heavy load is applied before the output voltage is established, the IC may fail to start up due to the current limit.

# 8.3 Output Voltage Setting

### 8.3.1 External Setting method

When FB\_SEL signal is 0, the output voltage is set by the resistor divider connected at FB pin and can be calculated as below.

$$VOUT = VFB_{REF} \times (1 + \frac{RUP}{RDOWN})$$

Where:

$V_{FB\_REF}$  is the internal reference voltage 1V,  $R_{UP}$  and  $R_{DOWN}$  are the resistors connected from VOUT to FB and to AGND.

### 8.3.2 Internal Setting method

When FB\_SEL signal is 1, the out voltage can be programmed internally via IIC. VOUT offset voltage is decided by 10-bit register (Reg03<7:0> and Reg04<1:0>), a 20mV/step resolution is given.

FB\_ON is the mask control bit of VOUT\_REF register. Only when FB\_ON=1, the VOUT\_REF register value is valid, the VOUT voltage is 5V default. FB\_DIR is the direction control bit.

If FB\_DIR=0, the VOUT voltage is:

VOUT = 5V + OFFSET

If FB\_DIR=1, the VOUT voltage is:

# SC8721A DATASHEET DRAFT

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

### 8.3.3 Dynamic Output Control

In discharging mode, output voltage can be set via IIC. In IIC, there's a load function, after Load is set to 1, VOUT starts to ramp at the speed of 1mV/us.

### 8.3.4 Cable drop compensation

VOUT has a cable drop compensation. The slope can be programmed via I2C registers. If external feedback resistor is applied, Rup must be 100K to have the designed slope.

# 8.4 Output Current Limit

The output current limit can be set by internal register and external resistor.

$$IOUT\_LIM = \frac{(CSO\_SET + 1) * 4mV * 2k\Omega}{Rs^*Rcso}$$

where

CSO\_SET is reference voltage, set by Reg 0x01<7:0>;

R<sub>cso</sub> = Resistors at CSO pin;

Rs = Current sense resistor value to sense output current;

When output is overload, the IC regulates the output current at setting current limit value and output voltage decreases automatically.

# 8.5 Output Current Monitor

In discharging mode, the output current can be monitored in real time by external ADC sampling CSO pins.

$$IOUT = \frac{Vcso * 2k\Omega}{Rs^*Rcso}$$

where

VCSO is voltage of CSO pin;

R<sub>cso</sub> = Resistors at CSO pin;

R<sub>S</sub> = Current sense resistor value to sense IBUS current;

# 8.6 Self-adaptive Input Voltage Regulation

The IC features dynamic VIN power management. The allowed minimum VIN operation voltage is VINREG threshold, which can be set by resistor divider at the VSET pin. During charging, if the output current is higher than VIN's current capability, the input source will be overloaded, and the VIN voltage is pulled low. Once the VIN voltage drops at VINREG threshold, the IC reduces the output voltage automatically and regulates the VIN voltage at VINREG threshold. the VINREG voltage is set by the resistor divider connected at VSET pin and can be calculated as below.

VINREG = VSET\_REF x

$$(1 + \frac{RUP}{RDOWN})$$

Where:

$V_{\text{SET}\_\text{REF}}$  is the internal reference voltage 1.2V,  $R_{\text{UP}}$  and  $R_{\text{DOWN}}$  are the resistors connected from VIN to VSET and to AGND.

Connect VSET pin with  $10k\Omega$  pull-up resistor to VCC, or set Reg06<4> to 0, VINREG function is disabled.

# 8.7 Register Load function

When output current limit and output voltage register value is set via I2C, Load bit (Reg0x05<1>) must be set to 1, then value can be loaded to corresponding registers.

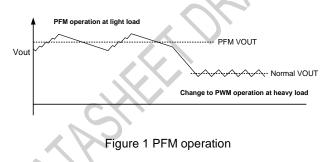

# 8.8 PWM/PFM Operation

The IC supports two operation modes: PWM mode and PFM mode.

In PWM mode, the IC always works with constant switching frequency for the whole load range. This helps achieve the best output voltage performance, but the efficiency is low at light load condition because of the high switching loss.

In PFM mode, the IC still works with constant switching frequency under heavy load condition, but under light load condition, it changes to pulse frequency modulation operation to reduce the switching loss. The efficiency can be improved under light load condition while output voltage ripple will be a little larger compared with PWM operation. Below figure shows the output voltage behavior of PFM mode.

# 8.9 Switching Frequency

The SC8721A provides four switching frequency selection from 230kHz/500kHz/720kHz/920kHz.

# 8.10 VCC Driver Voltage

The IC integrates a VCC regulator so to generate the driver voltage for internal driver circuit. The VCC is supplied by VIN

# SC8721A DATASHEET DRAFT

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

and is clamped to 5V. Connect a  $2.2\mu F$  ceramic capacitor from VCC to PGND pin close to the IC.

# 8.11 Loop Compensation

The internal control loop should be compensated by the resistor and capacitor connected at COMP pin. 10 k $\Omega$  resistor and 22 nF capacitor are suggested for most applications. If faster response is required, the user can increase the resistor value but should keep R\*C value unchanged. After changing the compensation, check and make sure the loop is stable under target conditions.

### 8.9 Standby Mode

When CE signal is high and DIS\_DCDC bit is 1, the IC enters into Standby mode. In this mode, the IC stops switching to save the quiescent current. The other functions are still valid, and the MCU can still control the IC through I2C.

# 8.10 Shutdown Mode

When CE signal is low, the IC enters into Shutdown mode. In this mode, the IC stops working and disables the I2C interface to save the power.

# 8.12 Protections

### 8.12.1 Over Voltage Protection

The IC supports three mechanisms for over voltage protection.

The first is once the IC detects the VIN voltage is higher than typical 22V, the IC stops switching until the voltage drops below the threshold.

The second is once the IC detects the VOUT voltage is higher than the setting target by typical 10%(FB\_SEL=0), the IC stops switching until the voltage drops below the threshold.

The third is once the IC detects the VOUT voltage is 500mV higher than the setting target (FB\_SEL=1), the IC stops switching until the voltage drops below the threshold.

### 8.12.2 Over Current Protection

The IC implements internal current limit at 10A. Once the IC detects the inductor current is higher than 10A, it reduces the switching duty cycle, and keeps the inductor current from increasing.

### 8.12.3 Output Short Circuit Protection

The IC supports FB pin short circuit protection when external divider resistor is applied to adjust voltage in discharging mode. During power on, the IC monitors the FB pin status. Once it detects the FB pin is short to ground, it still starts up and limits the VOUT voltage at 5V fixed voltage. This helps protect the circuits connected at VOUT pin from over voltage stress.

Besides FB short circuit protection, the IC also monitors the VOUT voltage all the time. Once it detects the VOUT voltage drops below short circuit protection threshold, typical 0.7V, the IC begins to hiccup.

### 8.12.4 Over Temperature Protection

Once the IC detects the chip junction temperature exceeds the threshold (160°C typical), the IC goes into thermal shutdown and stops switching. When the junction temperature falls below typical 130°C, the IC resumes operation.

### 8.13 I2C and Registers

### 8.13.1 I2C Interface

The IC features I2C interface, so the MCU or controller can control the IC flexibly. The 7-bit I2C address of the chip is 0x62 (8-bit address is 0xC4 for write command, 0xC5 for read command). The SDA and SCL pins are open drain and must be connected to the positive supply voltage via a current source or pull-up resistor. When the bus is free, both lines are HIGH. The I2C interface supports both standard mode (up to 100kbits) and fast mode (up to 400k bits with 5 k $\Omega$  pull up resistor at SCL pin and SDA pin respectively).

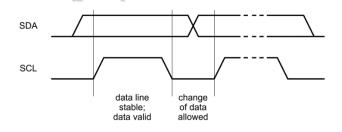

### 8.13.1.1 Data Validity

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. One clock pulse is generated for each data bit transferred.

Figure 2 Bit transfer on the I2C bus

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

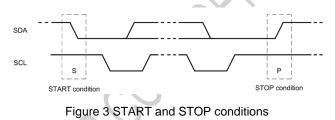

### 8.13.1.2 START and STOP Conditions

All transactions begin with a START (S) and are terminated by a STOP (P). A HIGH to LOW transition on the SDA line while SCL is HIGH defines a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition.

START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition.

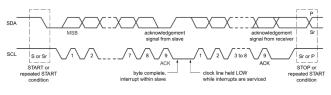

### 8.13.1.3 Byte Format

Every byte put on the SDA line must be eight bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte must be followed by an Acknowledge bit. Data is transferred with the Most Significant Bit (MSB) first. If a slave cannot receive or transmit another complete byte of data until it has performed some other function, for example servicing an internal interrupt, it can hold the clock line SCL LOW to force the master into a wait state. Data transfer then continues when the slave is ready for another byte of data and releases clock line SCL.

Figure 4 Data transfer on the I2C bus

# 8.13.1.4 Acknowledge (ACK) and Not Acknowledge (NACK)

The acknowledge takes place after every byte. The acknowledge bit allows the receiver to signal the transmitter that the byte was successfully received and another byte may be sent. During data is transferred, the master can either be the transmitter or the receiver. No matter what it is, the master generates all clock pulses, including the acknowledge ninth clock pulse.

The transmitter releases the SDA line during the acknowledge clock pulse so the receiver can pull the SDA line LOW and it remains stable LOW during the HIGH period of this clock pulse.

When SDA remains HIGH during this ninth clock pulse, this is defined as the Not Acknowledge signal. The master can then generate either a STOP condition to abort the transfer, or a repeated START condition to start a new transfer.

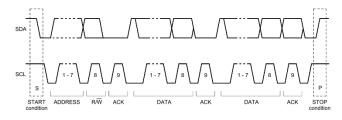

### 8.13.1.5 The slave address and R/W bit

Data transfers follow the format shown in below. After the START condition (S), a slave address is sent. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W) — a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated START condition (Sr) and address another slave without first generating a STOP condition.

Figure 5 A complete data transfer

Figure 6 The first byte after the START procedure

# SC8721A DATASHEET DRAFT

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

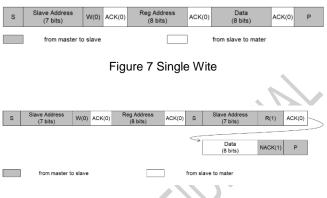

### 8.13.1.6 Single Read and Write

Figure 8 Single Read

If the register address is not defined, the charger IC send back NACK and go back to the idle state.

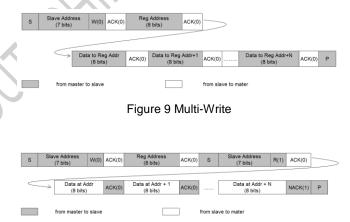

### 8.13.1.7 Multi-Read and Multi-Write

The IC supports multi-read and multi-write for continuous registers.

Figure 10 Multi-Read

### SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

# **9** Application Information (TBD)

### 9.1 Input and Output Capacitor Selection

Since MLCC ceramic capacitor has good high frequency filtering and low ESR, X5R or X7R capacitors are recommended for input and output capacitors. Typically, three 22  $\mu$ F ceramic input capacitors and three 22  $\mu$ F ceramic output capacitors work for most applications. The input / output capacitors should be places as close to VIN / CSN pins as possible, and they should be also near the PGND pins or thermal pad.

Capacitors' derating effect under DC bias should be taken into account when selecting the capacitors. Ceramic capacitor normally loses its most capacitance at the rated voltage, so leave margin on voltage rating to ensure adequate effective capacitance. For example, if the highest operating voltage is 12V, select 16V or 25V capacitor.

Besides this, high value electrolytic capacitor or tantalum capacitor is recommended to place in parallel with the ceramic capacitors at output to improve the load transient response.

### 9.2 Inductor Selection

Because the selection of inductor affects the loop stability and the power efficiency, inductor is one of the most important components for the DCDC design.

The IC can work with inductors between 2.2  $\mu$ H to 10  $\mu$ H range for most applications. A higher value is suggested to keep the inductor current ripple  $\leq$  30% of the DC current.

Compared with high value inductor in the same package size, a lower value inductor normally has smaller DC resistance (DCR), so can reduce the conduction power loss, which can be calculated roughly as

$PL_DC = IL^2 \cdot DCR$

IL is the average value of inductor current, and it equals to IIN or IOUT.

However, besides DCR, the core loss or AC loss of an inductor also affects the power efficiency a lot. The low value inductor causes large inductor current ripple, thus high core loss or AC loss, so it is not always the low value inductor supports the higher efficiency.

Since the core loss is related to the inductor material type, and normally the inductor vendors don't provide the core loss data, it is very difficult to suggest what inductor value can result in higher efficiency. As a rule of thumb, high value inductor like 4.7  $\mu$ H to 10  $\mu$ H is recommended for applications where the difference between input voltage and output voltage is big, such as 5V to 20V; while for those applications where input voltage is close to output voltage but large current is on power path, low value inductor like 2.2  $\mu$ H is suggested.

For applications where efficiency or thermal dissipation is very important, it is highly suggested that the user chooses the inductor in larger package size for lower DCR, and also tests the efficiency with different inductor values, so to find the best combination to achieve the highest efficiency.

The saturation current is another important parameter when selecting the inductor. The inductance can decrease 20% to 35% when the current approaches saturation level, so the user should make sure the saturation current is higher than the inductor peak current during the operation.

The inductor peak current can be calculated by below formula.

$$IL_peak = IIN + \frac{VIN \cdot (VOUT - VIN \cdot \eta)}{2 \cdot fsw \cdot L \cdot VOUT} \quad (VOUT \ge VIN)$$

$$IL_peak = IOUT + \frac{VOUT \cdot (VIN - VOUT)}{2 \cdot fsw \cdot L \cdot VIN \cdot n} \quad (VOUT < VBIN)$$

$\eta$  is the power conversion efficiency. User can use 90% for calculation.

fsw is the switching frequency

L is the inductor value

When selecting inductor, the inductor saturation current must be higher than the peak inductor current with enough margin (20% margin is recommended). The rating current of the inductor must be higher than the output current.

# 9.3 Current Sense Resistor

The  $R_s$  in the typical application circuit are current sense resistors for current limit functions.

A high resistor value can result in high current limit / monitor accuracy but causes high conductor loss. Typically, 10 m $\Omega$  is recommended. But for applications where efficiency is more important than accuracy, lower value is suggested.

When selecting the current sense resistor, its power rating and temperature coefficient should also be considered.

The power dissipation can be roughly calculated as  $P=I^2R$ , where I is the highest current flowing through it. The power rating should be higher than the calculated value.

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

The resistor value varies with temperature and the variation is decided by its temperature coefficient. If high accuracy of limit or monitor is required, select as lower temperature coefficient as possible.

### 9.4 Snubber Circuit

The RC snubber circuits at SWx nodes as shown below can be used to suppress the switching spike so to improve the EMC performance. A typical snubber circuit is composed by a 2.2 $\Omega$  resistor and 1nF capacitor. The user can reduce the resistance and increase the capacitance further to improve the EMC. However, because it often causes higher switching loss and results in lower efficiency, it is suggested not to add snubber circuits unless necessary.

Figure 15 Snubber circuit at SWx nodes

The IC also allows user adding a driver resistor for the low side MOSFET at VOUT side to slow down the switching, thus to reduce the switching spike improve the EMC performance. However, because the driver resistor also causes higher switching loss and thus lower efficiency, it is suggested not to add the driver resistor unless necessary.

If the driver resistor is needed, a 0603 resistor should be used, and it should be placed near the IC.

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

|               | ter Type | Default value<br>@POR | Bit 7      | Bit 6      | Bit 5    | Bit 4     | Bit 3    | Bit 2       | Bit 1     | Bit 0    |

|---------------|----------|-----------------------|------------|------------|----------|-----------|----------|-------------|-----------|----------|

| 1H CSO        | R/W      | 1111 0000             |            |            |          | CSC       | O_SET    |             |           |          |

| 2H SLOPE_COM  | IP R/W   | xxxx xx00             |            | RESERVED   |          |           |          |             |           | OMP      |

| 3H VOUT_SET_I | MSB R/W  | 0000 0000             |            |            |          | VOUT_S    | SET_MSB  |             |           |          |

| 4H VOUT_SET_L | _SB R/W  | xxx0 0000             |            | RESERVED   |          | FB_SEL    | FB_ON    | FB_DIR      | VOUT_SE   | T_LSB    |

| 5H GLOBAL_CT  | RL R/W   | xxxx x000             |            |            | RESERVED |           | $\sim$   | DIS_DCDC    | REG_LOAD  | RESERVED |

| 6H SYS_SET    | R/W      | 10x1 xxxx             | EN_PWM     | EXT_DT     | RESERVED | EN_VINREG |          | RESERVE     | D         |          |

| 7H RESERVED   | R/W      | XXXX XXXX             |            |            | •        | RESE      | ERVED    |             |           |          |

| 8H FREQ_SET   | R/W      | 0000 0001             |            |            | F        | RESERVED  |          |             | FREQ_     | SET      |

| 9H STATUS_1   | R        | 0000 0000             | VOUT_SHORT | VOUT_VIN_H | RESERVED | RESERVED  | THD      | RESERVED    | RESERVED  | OCP      |

| AH STATUS_2   | R        | 0000 0000             | VINOVP     | RESERVED   | RESERVED | RESERVED  | RESERVED | VINREG_FLAG | IBUS_FLAG | RESERVED |

|               |          |                       |            | ORA        |          |           |          |             |           |          |

Copyright © 2019, Southchip Semiconductor Technology (Shanghai) Co., Ltd.

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

| Bit | Mode | Bit Name               | Default value<br>@POR | Description                                                                                                                                                                                                                                                                           | Notes                                                             |

|-----|------|------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| 7-0 | R/W  | CSO voltage<br>setting | 1111 0000             | CSO_SET used to set VOUT current reference limit<br>The output current limit is calculated as:<br>$IOUT_ILIM = \frac{(CSO_SET+1)*4mV*2k\Omega}{Rs*Rcso}$<br>CSO_SET range:0~255<br>0000 0000: 0<br>0000 0001: 1<br>0000 0010: 2<br><br>1111 0000: 240 (default)<br><br>1111 1111: 255 | CSO_SET is<br>clamped to<br>be higher<br>than 0x08<br>internally. |

### Table 1 0x01H CSO\_SET Register

# Table 2 0x02H SLOPE\_COMP Register

| Bit | Mode | Bit Name   | Default value<br>@POR | Description                                               | Notes |

|-----|------|------------|-----------------------|-----------------------------------------------------------|-------|

| 7-2 | R/W  | Reserved   | 000000                | Internal use. Don't overwrite this bit.                   |       |

| 1-0 | R/W  | SLOPE_COMP | 00                    | SLOPE_COMP is used to set VOUT cable drop<br>compensation |       |

|     |      |            |                       | 00: no slope compensation(default)                        |       |

|     |      |            | 2                     | 01: 50mV/A                                                |       |

|     |      |            |                       | 10: 100mV/A                                               |       |

|     |      |            |                       | 11:150mV/A                                                |       |

# Table 3 0x03H VOUT \_SET\_MSB Register

| Bit        | Mode | Bit Name     | Default value<br>@POR | Description                                               | Notes |

|------------|------|--------------|-----------------------|-----------------------------------------------------------|-------|

| 7-0        | R/W  | VOUT_SET_MSB | 000000                | The highest 8-bit of the VOUT_ SET.                       |       |

| $\bigcirc$ |      |              |                       | VOUT_SET_MSB and VOUT_SET_LSB are used to set<br>VOUT_SET |       |

|            |      |              |                       | The VOUT_SET is calculated as:                            |       |

|            |      |              |                       | VOUT_SET = VOUT_SET_MSB x4+VOUT_SET_LSB) x 20mV           |       |

SOUTHCHIP SOUTHCHIP SEMICONDUCTOR

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

# Table 4 0x04H VOUT\_SET Register

| Bit | Mode | Bit Name     | Default value<br>@POR | Description                                                                                                                                                                                                                                             | Notes |

|-----|------|--------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7-5 | R/W  | Reserved     | 000                   | Internal use. Don't overwrite this bit                                                                                                                                                                                                                  |       |

| 4   | R/W  | FB_SEL       | 0                     | VOUT voltage setting control, only for discharging mode:<br>0: External VOUT setting, VOUT output voltage is set by<br>resistor divider at FB pin<br>1: Internal VOUT setting, VOUT output voltage is set by<br>VOUT _SET_MSB, VOUT _SET_LSB and FB_DIR |       |

| 3   | R/W  | FB_ON        | 0                     | VOUT_SET mask bit<br>0: VOUT voltage is not allowed to be revised<br>1: VOUT voltage is allowed to be revised                                                                                                                                           |       |

| 2   | R/W  | FB_DIR       | 0                     | VOUT_SET_direction:<br>0: Increment(default)<br>1: Decrement                                                                                                                                                                                            |       |

| 1-0 | R/W  | VOUT_SET_LSB | 00                    | The lowest 2-bit of the VOUT_SET                                                                                                                                                                                                                        |       |

# Table 5 0x05H GLOBAL\_CTRL Register

| Bit | Mode | Bit Name     | Default value<br>@POR | Description                                                                                 | Notes |

|-----|------|--------------|-----------------------|---------------------------------------------------------------------------------------------|-------|

| 7-3 | R/W  | Reserved     | 0000                  | Internal use. Don't overwrite this bit                                                      |       |

| 2   | R/W  | DIS_DCDC     | 0                     | DCDC switching control:                                                                     |       |

|     |      |              |                       | 0: enable(default)                                                                          |       |

|     |      |              |                       | 1: disable                                                                                  |       |

| 1   | R/W  | Load         | ο                     | Write 1 to load register (CSO_SET/VOUT_SET /FB_DIR) and clear to 0 automatically after read |       |

| 0   | R/W  | Reserved bit | 0                     | Internal use. Don't overwrite this bit                                                      |       |

|     | -    |              | Table 6 0x            | 06H SYS_SET Register                                                                        |       |

### Table 6 0x06H SYS\_SET Register

| Bit               | Mode | Bit Name | Default value<br>@POR | Description                        | Notes |

|-------------------|------|----------|-----------------------|------------------------------------|-------|

| 7                 | R/W  | EN_PWM   | 1                     | EN_ PWM:                           |       |

| $\langle \rangle$ |      |          |                       | 0: disable, auto pwm mode          |       |

|                   |      |          |                       | 1: enable, force pwm mode(default) |       |

| 6                 | R/W  | EXT_DT   | 0                     | Switching dead time setting:       |       |

|                   |      |          |                       | 0: 20ns(default)                   |       |

|                   |      |          |                       | 1: 40ns                            |       |

# SOUTHCHIP SOUTHCHIP SEMICONDUCTOR

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

| 5   | R/W | Reserved bit  | 0           | Internal use. Don't overwrite this bit |  |

|-----|-----|---------------|-------------|----------------------------------------|--|

| 4   | R/W | EN_VINREG_PFM | 1           | VINREG enable control:                 |  |

|     |     |               |             | 0: disable                             |  |

|     |     |               |             | 1: enable (default)                    |  |

| 3-0 | R/W | Reserved bit  | 0000        | Internal use. Don't overwrite this bit |  |

|     |     |               | Table 7 0x0 | 7H TERM SET Register                   |  |

### Table 7 0x07H TERM\_SET Register

| Bit | Mode | Bit Name     | Default value<br>@POR | Description Notes                      |

|-----|------|--------------|-----------------------|----------------------------------------|

| 7-0 | R/W  | Reserved bit | 00000000              | Internal use. Don't overwrite this bit |

|     |      |              |                       |                                        |

# Table 8 0x08H FREQ\_SET Register

| Bit | Mode | Bit Name      | Default value<br>@POR | Description                            | Notes |

|-----|------|---------------|-----------------------|----------------------------------------|-------|

| 7-2 | R/W  | Reserved bit  | 000000                | Internal use. Don't overwrite this bit |       |

| 1-0 | R/W  | Frequency set | 01                    | Switching frequency setting:           |       |

|     |      |               |                       | 00: 260kHz                             |       |

|     |      |               | С                     | 01: 500kHz(default)                    |       |

|     |      |               |                       | 10: 720kHz                             |       |

|     |      |               |                       | 11: 920kHz                             |       |

# Table 9 0x09H STATUS\_1 Register

| Bit | Mode | Bit Name     | Default value<br>@POR | Description                            | Notes |

|-----|------|--------------|-----------------------|----------------------------------------|-------|

| 7   | R    | VOUT SHORT   | 0                     | 1: VOUT<0.7V happens                   |       |

| 6   | R    | VOUT_VOUT_H  | 0                     | 0: VOUT < VIN                          |       |

|     |      | <b>)</b>     |                       | 1: VOUT > VIN                          |       |

| 5   | R    | Reserved bit | 0                     | Internal use. Don't overwrite this bit |       |

| 4   | R    | Reserved bit | 0                     | Internal use. Don't overwrite this bit |       |

| 3   | R    | THD          | 0                     | 1: Thermal shutdown                    |       |

| 2   | R    | Reserved bit | 0                     | Internal use. Don't overwrite this bit |       |

| 1   | R    | Reserved bit | 0                     | Internal use. Don't overwrite this bit |       |

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

| 0 | R | OCP | 0 | 1: Internal over current protection happens |  |

|---|---|-----|---|---------------------------------------------|--|

|---|---|-----|---|---------------------------------------------|--|

### Table 10 0x0AH STATUS\_2 Register

| Bit | Mode | Bit Name     | Default value<br>@POR | Description Notes                                           |

|-----|------|--------------|-----------------------|-------------------------------------------------------------|

| 7   | R    | VINOVP       | 0                     | 1: VIN higher than absolute voltage threshold (22V) happens |

| 6   | R    | Reserved bit | 0                     | Internal use. Don't overwrite this bit                      |

| 5   | R    | Reserved bit | 0                     | Internal use. Don't overwrite this bit                      |

| 4   | R    | Reserved bit | 0                     | Internal use. Don't overwrite this bit                      |

| 3   | R    | Reserved bit | 0                     | Internal use. Don't overwrite this bit                      |

| 2   | R    | VINREG_FLAG  | 0                     | 1: IC working in VINREG loop                                |

| 1   | R    | IBUS_FLAG    | 0                     | 1: IC working in current limit loop                         |

| 0   | R    | Reserved bit | 0                     | Internal use. Don't overwrite this bit                      |

|     |      |              | ZAF                   | .00                                                         |

|     |      |              | RAF                   | 500                                                         |

|     |      |              | RAF                   |                                                             |

|     |      |              | RAF                   |                                                             |

|     |      |              |                       | ŝ                                                           |

Copyright © 2019, Southchip Semiconductor Technology (Shanghai) Co., Ltd.

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

# **MECHANICAL DATA**

SEMICONDUCTOR SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

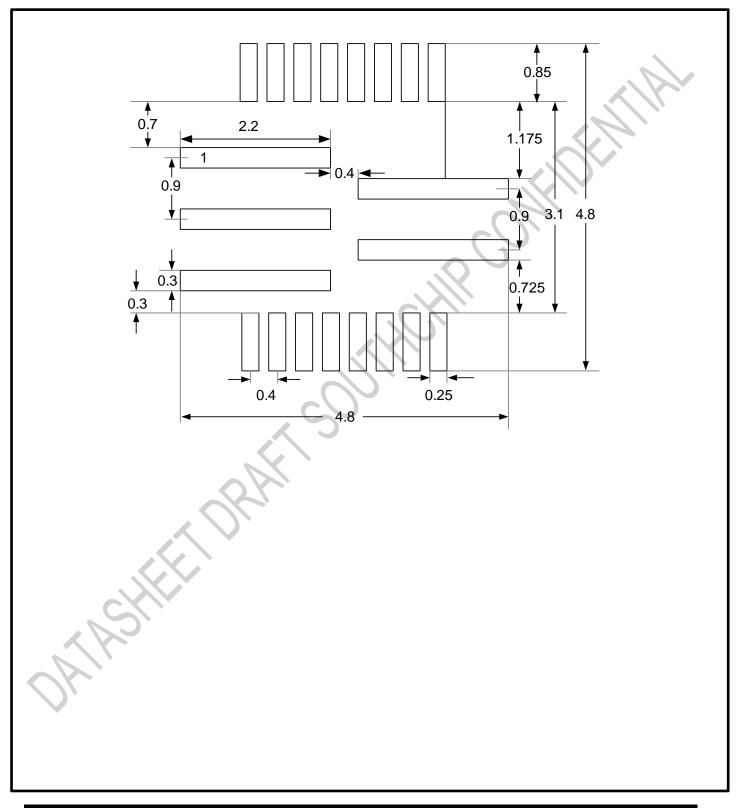

# **RECOMMENDED FOOTPRINT**

QFN-21 (4x4x0.75) (Unit: mm)

单击下面可查看定价,库存,交付和生命周期等信息

>>SOUTHCHIP(南芯)