# **High Performance PWM Controller for Fly-back**

## **Descriptions**

SC3030 is a high performance, multi-mode fly-back PWM controller (CCM/QR/DCM).

SC3030 provides an adaptive switching frequency foldback to achieve higher efficiency in the whole loading range. At heavy load or full load, it operates up to 67kHz frequency. When loading decreases, it operates in green mode with valley switching for high efficiency. And at no load, the IC will operate in Burst mode to reduce power consumption.

It provides functions of low start-up current, fast start-up, low standby power consumption. The burst mode with extremely low operation current (185uA) and significantly reduces standby power consumption to meet the efficiency regulations.

The SC3030 offers comprehensive protection to prevent the circuit from damage under abnormal conditions.

Furthermore, the features of frequency jittering and smart driving function can minimize the noise and improve EMI performance.

### **Features**

- Internal Soft Start

- 67kHz Maximum Switching Frequency

- CCM @ Heavy Load and Low Line

- Valley switching operation @ Green mode

- Burst Mode @ Light Load & No Load

- Ultra-low operation current @Burst mode/Fault Mode

- Frequency Jitter for EMI improvement

- Driver capability: 300mA/-600mA

- Comprehensive Protection

- VDD over voltage protection

- VDD under voltage lock out

- Cycle by cycle current limiting

- Two level over current protection

- Output over voltage protection

- Adaptive output short protection

- Over Load protection

- Brown in/out with auto-recovery

- SOT23-6 package available

## **Applications**

AC-DC adapters for Portable Devices

## 4 Device Information

| ORDER NUMBER | PACKAGE | BODY SIZE             |

|--------------|---------|-----------------------|

| SC3030SBER   | SOT23-6 | 2.9mm x 2.8mm x 1.1mm |

## **SC3030SBER Functional Table**

| ORDER NUMBER        | SC3030 |

|---------------------|--------|

| Maximum Frequency   | 67kHz  |

| V <sub>ZCDOVP</sub> | 3.55V  |

| OLP                 | A      |

| Bulk Cap OVP        |        |

| Brown In/Out        | A      |

| Valley Switching    | Y      |

| Others Protections  | A      |

A: Auto-recovery;

Y: The feature is enabled

/ : The feature is not enabled

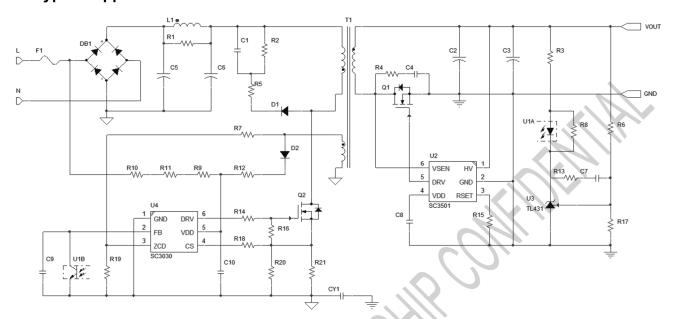

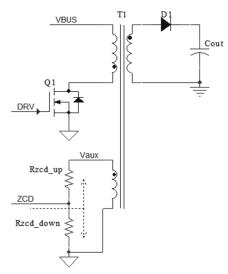

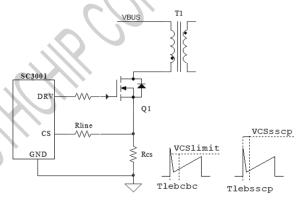

# 5 Typical Application Circuit

Fig. 1 Typical application circuit

# 6 Terminal Configuration and Functions

Fig. 2 Top view (SOT23-6)

| TERM        | TERMINAL |     |                                                                                                                                                                                                                          |  |  |  |  |

|-------------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NUMBER NAME |          | I/O | DESCRIPTION                                                                                                                                                                                                              |  |  |  |  |

| 1           | GND      | PWR | Power Ground.                                                                                                                                                                                                            |  |  |  |  |

| 2           | FB       | ı I | Secondary side feedback through opto-coupler. A capacitor is needed to connect to GND.                                                                                                                                   |  |  |  |  |

| 3           | ZCD      | I   | Voltage Sense. The ZCD voltage is used to detect resonant valleys for quasi-resonant switching. This pin detects the output voltage information and diode current discharge time based on the auxiliary winding voltage. |  |  |  |  |

| 4           | cs       | I   | Current Sense. This pin connects to a current-sense resistor to sense the MOSFET current for Peak-Current-Mode control.                                                                                                  |  |  |  |  |

| 5           | VDD      | PWR | Power Supply. This pin is typically connected to an external VDD capacitor.                                                                                                                                              |  |  |  |  |

| 6           | DRV      | 0   | Totem-pole output to drive the external power MOSFET, Maximum Voltage is clamped to 12V internally.                                                                                                                      |  |  |  |  |

## **Specifications**

## 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) (1)

| Item                           | Description                          | Min. | Тур. | Max. | Unit |

|--------------------------------|--------------------------------------|------|------|------|------|

|                                | VDD to GND                           | -0.3 | -    | +40  | V    |

| Voltage range at terminals (2) | DRV to GND                           | -0.3 | -    | +20  | V    |

|                                | Other Pins to GND                    | -0.3 | - <  | +6.5 | V    |

| T <sub>J</sub>                 | Operating Junction temperature range | -40  | -    | 150  | °C   |

| T <sub>stg</sub>               | Storage temperature range            | -65  |      | 150  | °C   |

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress (1) ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device

### **Thermal Information** 7.2

| THERMAL RESISTA | NCE (1)                                | SOT23-6(2.9mmx2.9mm) | UNIT |

|-----------------|----------------------------------------|----------------------|------|

| $\theta_{JA}$   | Junction to ambient thermal resistance | 220                  | °C/W |

| $\theta_{JC}$   | Junction to case resistance            | 110                  | °C/W |

<sup>(1)</sup> Measured on JESD51-7, 2-layer PCB.

## 7.3 Handling Ratings

| PARAMETER | DEFINITION                                        | MIN | MAX | UNIT |

|-----------|---------------------------------------------------|-----|-----|------|

| ESD (1)   | Human body model (HBM) ESD stress voltage (2)     | -2  | +2  | kV   |

| ESD       | Charged device model (CDM) ESD stress voltage (3) | -1  | +1  | kV   |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows (2) safe manufacturing with a standard ESD control process.

Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe (3) manufacturing with a standard ESD control process.

## 7.4 Recommended Operating Conditions

| PARAMETER        | TEST CONDITIONS                 | MIN | TYP | MAX                | UNIT |

|------------------|---------------------------------|-----|-----|--------------------|------|

| VDD to GND       | VDD voltage range to GND        | 10  |     | $V_{\text{DDOVP}}$ | ٧    |

| DRV to GND       | DRV voltage range to GND        | 0   |     | 15                 | ٧    |

| Others to GND    | Other pins voltage range to GND | 0   |     | 5.5                | ٧    |

| C <sub>VDD</sub> | VDD Capacitor                   | 2.2 |     | 22                 | uF   |

| T <sub>A</sub>   | Operating ambient temperature   | -40 |     | 85                 | °C   |

| TJ               | Operating junction temperature  | -40 |     | 125                | °C   |

## 7.5 Electrical Characteristics

VDD=15V,  $T_J$ = -40°C~125°C, unless otherwise noted.

| PARAMETEI               | २                                                     | TEST CONDITIONS              | MIN  | TYP  | MAX  | UNIT   |

|-------------------------|-------------------------------------------------------|------------------------------|------|------|------|--------|

| SUPPLY VO               | LTAGE (VDD)                                           |                              | •    |      |      |        |

| $V_{DDON}$              | VDD on threshold voltage                              |                              | 15.4 | 16.2 | 17.0 | V      |

| $V_{\text{DDOFF}}$      | VDD off threshold voltage                             |                              | 7.0  | 7.5  | 8.0  | V      |

| $V_{DDHOLDL}$           | VDD holding entry point voltage                       |                              |      | 7.9  |      | V      |

| $V_{DDHOLDH}$           | VDD holding exit point voltage                        |                              |      | 8.5  |      | V      |

| I <sub>ST</sub>         | Startup current                                       | VDD < V <sub>DDON</sub> -1V  |      | 2.5  | 8.0  | uA     |

| I <sub>VDD</sub>        | Operating current                                     | Cload = 1nF                  |      | 2    |      | mA     |

| I <sub>VDDBT</sub>      | Burst mode current                                    | V <sub>FB</sub> < 0.5V       |      | 185  | 220  | uA     |

| I <sub>VDDFAULT</sub>   | Hold up current in fault mode                         |                              |      | 80   |      | uA     |

| T <sub>DFAULT</sub>     | Hold on time in fault mode                            | (                            |      | 1    |      | S      |

| I <sub>VDDFAULT1</sub>  | VDD sink current                                      | After T <sub>DFAULT</sub> 1S | 5    | 1.2  | 2.0  | mA     |

| $V_{\text{DDOVP}}$      | VDD OVP                                               |                              | 34.5 | 36.2 | 38.0 | V      |

| $I_{VDDOVP}$            | VDD OVP sink current                                  | V <sub>DD</sub> > 37.5V      |      | 3    |      | mA     |

| $T_{VDDOVP}$            | VDD OVP debounce time                                 |                              |      | 160  |      | us     |

| ZERO VOLTA              | AGE DETECTION (ZCD)                                   |                              |      |      |      |        |

| V <sub>ZCDOVP</sub>     | ZCD OVP                                               |                              | 3.37 | 3.55 | 3.73 | V      |

| N <sub>ZCDOVP</sub>     | ZCD OVP debounce counter                              |                              |      | 4    |      | Cycles |

| I <sub>ZCDMAX</sub>     | Maximum ZCD Clamp source current                      | (C)                          | 1    |      |      | mA     |

| $V_{ZCDCLAMP}$          | ZCD Clamp voltage                                     | I <sub>ZCDCLAMP</sub> =1.0mA |      | -120 |      | mV     |

| T <sub>LEB1OVP</sub>    | Leading edge blanking time1                           | FB = 0.65V                   |      | 1.6  |      | us     |

| T <sub>LEB2OVP</sub>    | Leading edge blanking time2                           | FB = 2.20V                   |      | 2.3  |      | us     |

| $V_{ZCDH}$              | ZCD valley detection rising edge                      | V <sub>DRV</sub> = low       | 0.40 | 0.45 | 0.50 | V      |

| I <sub>ZCDBI</sub>      | Line voltage brown in clamp current threshold in ZCD  |                              | 135  | 155  | 175  | uA     |

| I <sub>ZCDBO</sub>      | Line voltage brown out clamp current threshold in ZCD |                              | 115  | 140  | 165  | uA     |

| T <sub>DZCDBO</sub>     | ZCD brown out debounce time                           |                              |      | 60   |      | mS     |

| I <sub>LINECOMPST</sub> | Line voltage compensation threshold ZCD clamp current |                              |      | 210  |      | uA     |

| K <sub>LINECOMP</sub>   | The ratio of line voltage compensation                |                              | 0.17 | 0.20 | 0.22 |        |

| FEEDBACK                | VOLTAGE (FB)                                          |                              |      |      |      |        |

| V <sub>FBOPEN</sub>     | Open Loop Voltage                                     | I <sub>FB</sub> = 0          | 2.80 | 3.0  | 3.2  | V      |

| $R_{FB}$                | FB pull-up resistor                                   |                              |      | 8    |      | kΩ     |

| $V_{FBOLP}$             | OLP                                                   |                              | 2.30 | 2.50 | 2.7  | V      |

| $T_{FBOLP}$             | Debounce time of FB open loop protection              | V <sub>FB</sub> > 2.4V       |      | 64   |      | mS     |

| V <sub>FBBSTH</sub>     | FB voltage when DRV starts pulsing                    |                              | 0.4  | 0.6  |      | V      |

## **SC3030 DATASHEET DRAFT**

SOUTHCHIP SEMICONDUCTOR SOUTHCHIP CONFIDENTIAL SUBJECT TO CHANGE

| $V_{FBBSTHYS}$         | V <sub>FBBSTH</sub> hysteresis voltage                        |                        |      | 0.1   |      | V      |

|------------------------|---------------------------------------------------------------|------------------------|------|-------|------|--------|

| CURRENT S              | ENSE (CS)                                                     |                        |      |       |      |        |

| Tsscs                  | Soft start time of CS threshold                               |                        |      | 5     |      | mS     |

| Vcslimit               | Cycle by cycle current limited                                |                        | 0.47 | 0.495 | 0.52 | V      |

| T <sub>LEBCBC</sub>    | Leading edge blanking time                                    |                        |      | 350   |      | ns     |

| Vcs_sscp               | Secondary rectifier short protection                          |                        | 0.9  | 1.0   | 1.1  | V      |

| Ncs_sscp               | Secondary rectifier short circuit protection debounce counter |                        |      | 3     |      | Cycles |

| T <sub>LEBSSCP</sub>   | Leading edge blanking time                                    |                        |      | 200   |      | ns     |

| V <sub>CSSLOPE</sub>   | Slope compensation                                            |                        | 8.5  | 10,0  | 11.5 | mV/us  |

| V <sub>CSMIN</sub>     | CS minimum voltage                                            |                        |      | 0.1   |      | V      |

| $\Delta V_{\text{CS}}$ | CS jitter                                                     |                        | 2    | ±5    |      | %      |

| Тліт                   | CS jitter cycle                                               |                        | )    | 480   |      | cycles |

| GATE DRIVE             | ER (DRV)                                                      | CAIL                   |      |       |      | •      |

| V <sub>OL</sub>        | Driver output low voltage                                     | VDD=15V                |      |       | 0.5  | V      |

| V <sub>OH</sub>        | Driver output high voltage                                    | VDD=15V                | 8.0  |       |      | V      |

| $V_{\text{OH2}}$       | Driver output high voltage2                                   | VDD>V <sub>DDOFF</sub> | 6.0  |       |      | V      |

| I <sub>DRVSOURCE</sub> | DRV maximum source current                                    | V <sub>DRV</sub> < 1V  |      | 300   |      | mA     |

| I <sub>DRVSINK</sub>   | DRV maximum sink current                                      | V <sub>DRV</sub> > 9V  |      | 600   |      | mA     |

| $V_{\text{CLAMP}}$     | Output clamp voltage                                          | (                      |      | 11    |      | V      |

| T <sub>R</sub>         | Output rising time 1.2V ~ 10.8V                               | CL=1nF                 |      | 200   |      | ns     |

| T <sub>F</sub>         | Output falling time 10.8V ~ 1.2V                              | CL=1nF                 |      | 50    |      | ns     |

| Oscillator fo          | r Switching Frequency                                         |                        |      |       |      |        |

| F <sub>SWMAX</sub>     | Switching frequency                                           | $V_{FB} = V_{FBOLP}$   |      | 67    |      | kHz    |

| F <sub>SWMIN</sub>     | Minimum frequency                                             |                        |      | 21    |      | kHz    |

| T <sub>OFFMAX</sub>    | Maximum off time                                              | After SS, without ZCD  |      | 145   |      | us     |

| D <sub>MAX</sub>       | Maximum duty cycle                                            |                        |      | 78    |      | %      |

| Internal Ove           | r-Temperature Protection (OTP)                                |                        |      |       |      |        |

| ОТРн                   | OTP Temperature                                               |                        |      | 150   |      | °C     |

| OTP <sub>HYS</sub>     | OTP Hysteresis                                                |                        |      | 30    |      | °C     |

|                        | T                                                             |                        |      |       |      |        |

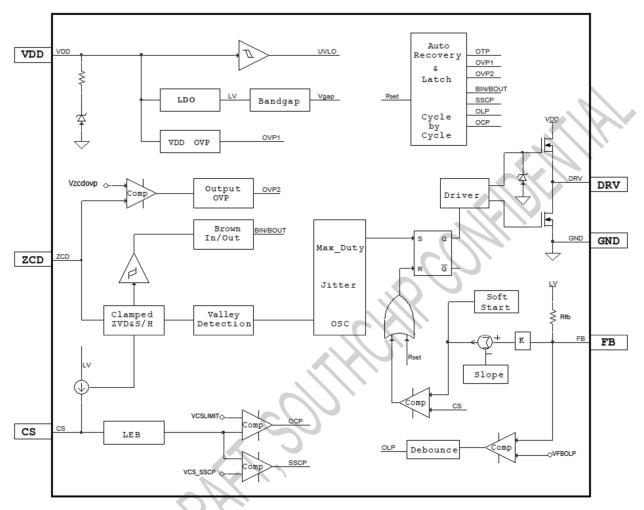

# 8 Functional Block Diagram

Fig. 3 Function Block Diagram

SOUTHCHIP CONFIDENTIAL SUBJECT TO CHANGE

## 9 Feature Description

SC3030 is a high performance, multi-mode fly-back PWM controller (CCM/QR/DCM). SC3030 provides an adaptive switching frequency fold-back to achieve higher efficiency in the whole loading range. At heavy load or full load, it operates up to 67kHz frequency. When loading decreases, it operates in green mode with valley switching for high efficiency. And at no load, the IC will operate in Burst mode to reduce power consumption.

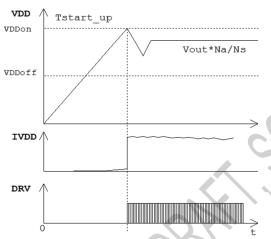

## 9.1 Start-up

During the startup period, the controller draws a little current  $I_{VDD}$  less than 2uA. This allows a high-impedance start-up resistor, which offers a convenient and efficient way to reduce the standby power.

Fig. 4 VDD start-up waveform

The start-up time can be estimated by the following equation:

$$T_{START-UP} \approx \frac{C_{VDD*}V_{DDON}}{V_{RIII K}} * R_{START_{UP}}$$

Where,  $C_{VDD}$  is VDD cap,  $V_{BULK}$  is the bulk cap voltage,  $R_{START-UP}$  is the resistor connected between bulk cap positive terminal and VDD cap.

An integrated 5ms soft start is used in the chip to reduce the voltage and current stress. During the soft start-up period, the Vcs threshold gradually rises from 0.1V to 0.5V. Once the secondary side regulation loop is stable, the Vcs is controlled by the feedback loop.

### 9.2 VDD UVLO

A hysteresis Under Voltage Lock Out (UVLO) comparator is implemented in SC3030. The turn-on and turn-off thresholds are fixed at 16.5V and 7.5V respectively. This hysteresis ensures that the VDD capacitor can be small enough during start-up. A large hysteresis is essential to ensure the IC work properly during the start-up period, even for a small VDD capacitor.

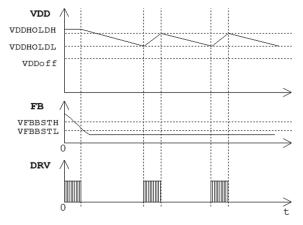

## 9.3 VDD Holding Mode

After the system starts, the VDD capacitor can be charged by the auxiliary winding. There are some operation condition changes (load changes, output voltage adjustment, burst mode), may lead the primary side DRV stop working when the output value is higher than the set value. Furthermore, the VDD voltage will be lower than VDDOFF and the system will stop. To avoid this situation, a VDD holding circuitry is designed, which starts working when VDD drops below VDDHOLDL and stops working when VDD rises above VDDHOLDH. The working process is shown in below:

Fig. 5 VDD holding circuitry

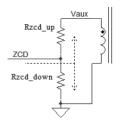

## 9.4 Brown IN/OUT Detection

The ZCD pin is used to monitor the voltage on the Bulk capacitor and perform brown In/Out. Working principle: When the primary switch is turned on, the voltage  $V_{AUX}$  on the auxiliary winding is negative. The value of  $V_{AUX}$  is proportional to the line voltage. The clamp circuit built in the ZCD pin clamps the voltage of the ZCD to  $V_{ZCDCLAMP}$  through a current source.

The detailed equations are shown as below:

$$\frac{V_{AUX}}{R_{ZCD-UP}} = I_{ZCDCLAP}$$

and  $V_{AUX} = \frac{V_{BULK}}{N_P} * N_{AUX}$

The V<sub>AUX</sub> is negatively associated with I<sub>ZCD</sub>. V<sub>AUX</sub> is a negative value. When I<sub>ZCD</sub> is greater than I<sub>ZCDBI</sub>, the Brown in process is executed and the system starts to work. When the value of IzcD is less than IzcDBO and lasts for a certain period of time, the line voltage is considered to be too low and brown out protection is triggered.

Fig. 6. Brown In/Out detection

## 9.5 Operation Mode

SC3030 provides an adaptive switching frequency foldback to achieve higher efficiency in the whole loading range. At heavy load or full load, it operates up to 67kHz switching frequency. When loading decreases, it operates in green mode with valley switching for high efficiency. And at no load, the IC will operate in Burst mode to reduce power consumption.

When the system is under no load or extremely light load, the IC will operate in BURST mode to reduce power dissipation. In this condition, switching loss of MOSFET is the main power dissipation. The DRV will be disabled immediately if V<sub>FB</sub> drops below V<sub>FBBSTL</sub>. When V<sub>FB</sub> rises up to V<sub>FBBSTH</sub>, the DRV starts to pulse again.

When under medium load condition, the system operates in green mode (DCM or QR). The switching frequency will linearly increase from 21kHz to 67kHz. That means, when load increases, the switching frequency is increased. When output load continues increasing, the IC will enter CCM and switching at a constant frequency of 67kHz for high efficiency.

SOUTHCHIP CONFIDENTIAL SUBJECT TO CHANGE

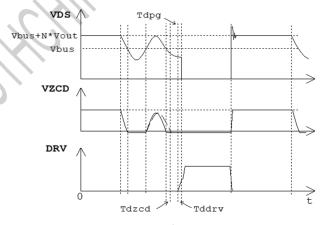

## 9.6 Valley Switching

ZCD pin can detect the freewheel information on the secondary side. In QR mode, when the voltage of ZCD turns to a negative value, it means that after a quarter of the resonant period, the primary MOS can be turned on, and valley opening helps to improve efficiency and improve EMI performance. In order to achieve the best valley opening, it can be achieved by appropriately adjusting TDZCD and TDDRV, where TDPG is an internal fixed delay. T<sub>DZCD</sub> can be adjusted by connecting a small capacitor in parallel with  $R_{ZCDDWON}$ . The recommended value is 10 ~ 11pF. TDDDRV can be adjusted by connecting DRV resistors in series.

Fig. 7 Valley Switching

## 9.7 Internal Slope Compensation

A slope compensation circuitry is built-in to simplify the system design. When the switcher is on, a ramp voltage is added to the sensed voltage across the CS pin, which helps to stabilize the system and prevent sub-harmonic oscillations.

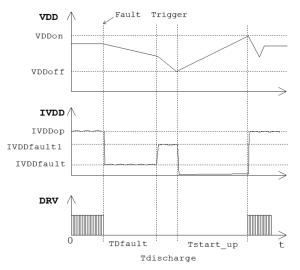

## 9.8 Auto-Recovery after Failure

SC3030 has complete protection functions, such as: VDD over voltage protection, VDD under voltage lock out, two level over current protection, output over voltage protection, Output short protection, over Load protection, brown IN/Out with auto-recovery. Unless otherwise specified,

these protections are auto-recovery. After the protection is triggered, the system enters the protection mode, and the VDD power consumption is reduced. After the  $T_{DEAULT}$  delay, the VDD sink current increases until  $V_{DDOFF}$ , and VDD starts the restart process. The detailed process is as follows.

Fig. 8 Auto-Recovery Process

### 9.9 VDD OVP

When the VDD voltage is higher than the  $V_{DDOVP}$  threshold voltage at least  $T_{VDDOVP}$ , in the case of a sink current of  $I_{VDDOVP}$ , DRV will be shut down. The VDD OVP function is an auto-recovery protection.

## 9.10 ZCD OVP

The auxiliary winding demagnetization voltage  $V_{AUX}$  is proportional to the output voltage.  $V_{ZCD}$  sensing the  $V_{AUX}$  via the divided resistors can be used to sample the output voltage after some blanking time. The output over voltage can be calculated as:

$$\frac{V_{AUX} * R_{ZCD-DOWN}}{R_{ZCD-DOWN} + R_{ZCD-UP}} > V_{ZCDOVP}$$

$$\frac{V_{AUX}}{N_A} = \frac{V_{OUT}}{N_S}$$

The blanking time can ignore the voltage ringing from leakage inductance of transformer. With the increase of VFB, the blanking time is from 1.4uS to 2.15uS.

SOUTHCHIP CONFIDENTIAL SUBJECT TO CHANGE

Fig. 9 ZCD Over Voltage Protection

## 9.11 Over Current Protection

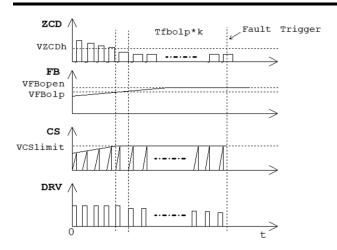

Two levels of overcurrent protection are integrated. One is cycle-by-cycle current limiting for overload protection. VCSSSCP is the fast protection for the case of secondary rectifier rectification shorted. The overcurrent protection and its shielding time are shown in the figure below.

Fig. 10 LEB of OCP

## 9.12 Adaptive Over Load Protection (AOLP)

An adaptive over load protection is implemented in the SC3030. When the voltage of VFB is higher than  $V_{FBOLP}$  and lasts for a period of time  $T_{FBOLP}$ , overload protection will be triggered. In particular, when the voltage of VFB is higher than  $V_{FBOLP}$ , if the peak voltage of ZCD pin is lower than  $V_{ZCDH}$ , the delay of  $T_{FBOLP}$  will be shortened. In the Fig.10, when  $V_{ZCD}$  is lower than  $V_{ZCDH}$ , the coefficient K is less than 1. The AOLP can reduce the power loss when secondary side is shorted.

SOUTHCHIP CONFIDENTIAL SUBJECT TO CHANGE

Fig. 11 Adaptive Over Load Protection

## 9.13 On-Chip OTP

An internal OTP circuit is embedded inside to provide the worst-case protection for SC3030. When the chip temperature rises higher than the OTP<sub>H</sub>, the controller will be disabled and works in the failure mode until the chip is cooled down below the hysteresis OTP<sub>HYS</sub>.

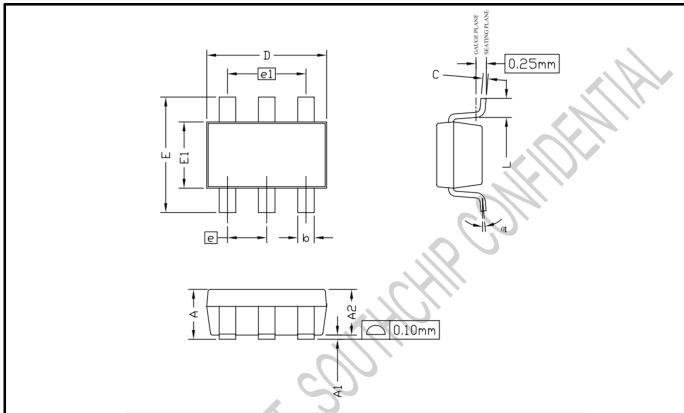

## **MECHANICAL DATA**

SOT23-6 (2.9mmx2.8mmx1.1mm)

| SYMBOLS  | DIMENS | IONS IN MILLI | METERS | DIMI       | ENSIONS IN INC | CHES  |  |

|----------|--------|---------------|--------|------------|----------------|-------|--|

| 31 MBOLS | MIN    | NOM           | MAX    | MIN        | NOM            | MAX   |  |

| A        | 0.90   | <del></del>   | 1.25   | 0.035      |                | 0.049 |  |

| A1       | 0.00   |               | 0.15   | 0.00       |                | 0.006 |  |

| A2       | 0.70   | 1.10          | 1.20   | 0.028      | 0.043          | 0.047 |  |

| b        | 0.30   | 0.40          | 0.50   | 0.012      | 0.016          | 0.020 |  |

| C        | 0.08   | 0.13          | 0.20   | 0.003      | 0.005          | 0.008 |  |

| D        | 2.70   | 2.90          | 3.10   | 0.106      | 0.114          | 0.122 |  |

| E        | 2.50   | 2.80          | 3.10   | 0.098      | 0.110          | 0.122 |  |

| E1       | 1.50   | 1.60          | 1.70   | 0.059      | 0.063          | 0.067 |  |

| e        |        | 0.95 BSC.     |        |            | 0.037BSC.      |       |  |

| e1       |        | 1.90 BSC.     |        | 0.075 BSC. |                |       |  |

| L        | 0.30   |               | 0.60   | 0.012      |                | 0.024 |  |

| θ1       | 00     |               | 80     | 00         |                | 80    |  |

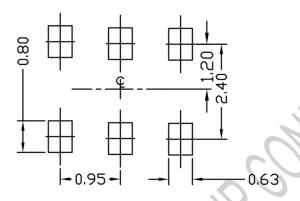

## RECOMMENDED FOOTPRINT

## **Example Board Layout**

UNIT: mm

## NOTES:

- Publication IPC-7351 is recommended for alternate designs

- Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting recommendations for vias placed in the thermal pad

Copyright © 2020, Southchip Semiconductor Technology (Shanghai) Co., Ltd.

# 单击下面可查看定价,库存,交付和生命周期等信息

# >>SOUTHCHIP