# SC8949 High Efficiency, Synchronous, Bi-directional Buck Charger Converter with Integrated MOSFETs and I2C Interface

# **1** Description

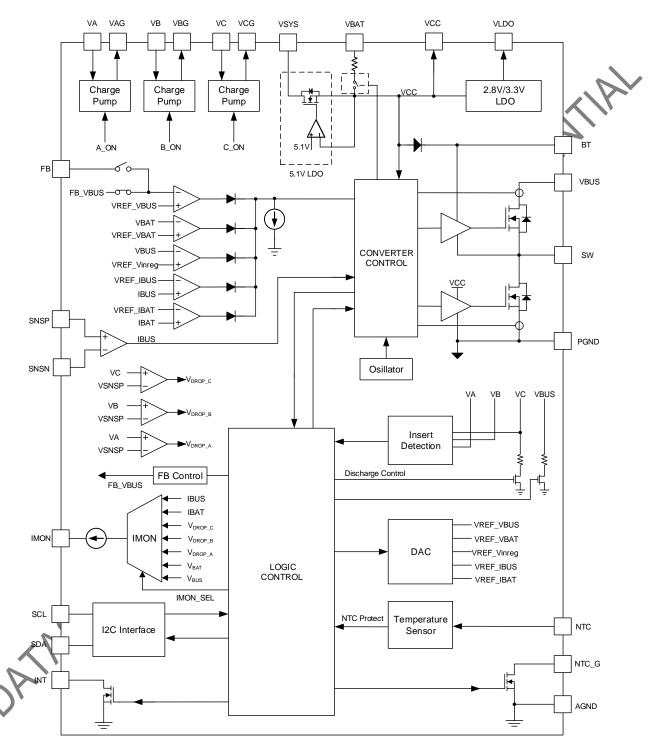

SC8949 is a synchronous buck charger with reverse boost discharging function. It integrates two N-channel MOSFETs with ultra-low Rdson and can support 5V high efficiency charging and discharging operation.

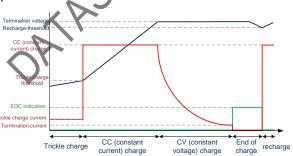

In charging mode, it steps down the input voltage to effectively charge the single cell battery. SC8949 supports trickle charging, constant current (CC) charging and constant voltage (CV) charging management functions automatically. When working in discharging mode (reverse boost mode), it can support 5V output and achieve up to 93% efficiency with 3V battery voltage for 5V4A output load.

The SC8949 features I2C interface, so the user can easily control the charging/discharging mode, and program the charging current, charging voltage, output voltage, and output current limits through I2C. It also monitors the VBUS status of up to three USB ports and provides three NMOS gate drivers to control the power path independently.

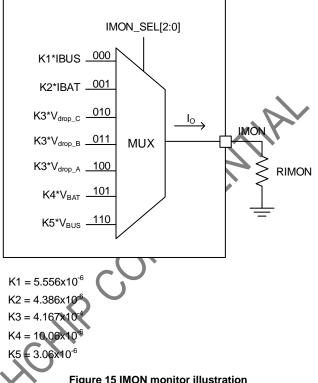

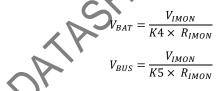

The IC also provides IMON pin, through which the MCU can monitor the VBUS / VBAT voltage, IBUS / IBAT current and the current of each port in real time. The NTC function guarantees the battery operation safety. All these features help simplify the system design and reduce the BOM.

The SC8949 supports under voltage protection, over voltage protection, over current protection, short circuit protection and over temperature protections to ensure safety under different abnormal conditions.

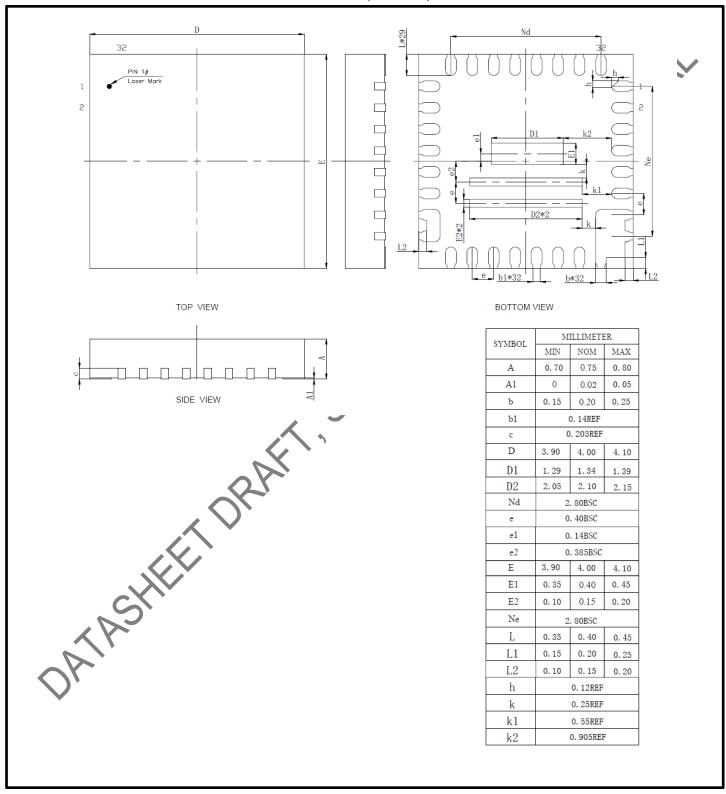

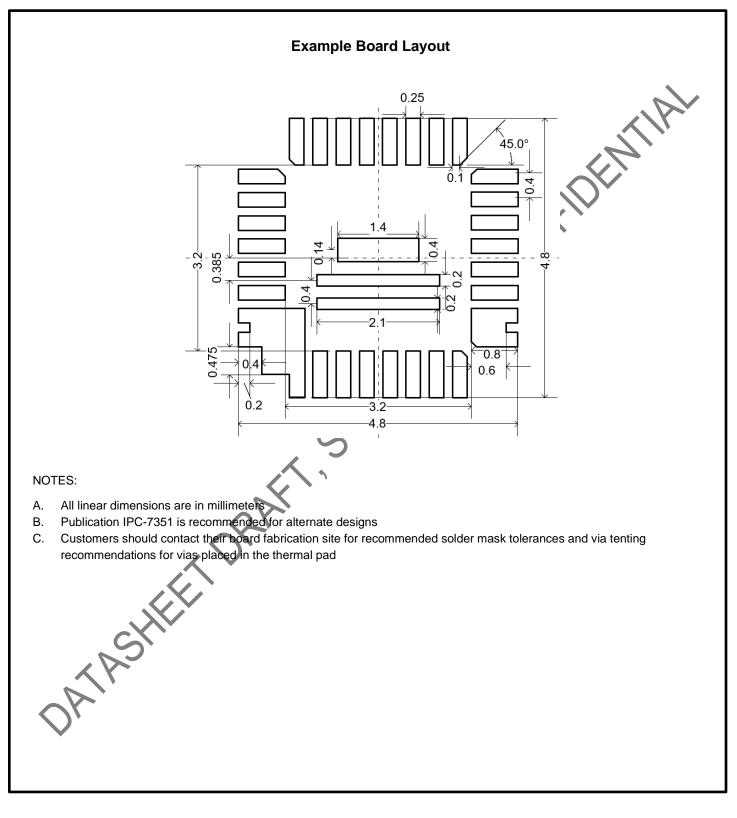

SC8949 adopts 32 pin 4mm x 4mm QFN package.

# 3 Applications

- Power Bank

- Li-ion Battery Charger

- Fast Charge

Smart USB Sockets

# 2 Features

- Charging management, including trickle charging, CC charging, CV charging and charging termination function

- 5V VBUS voltage operation

- Programmable battery voltage from 4.1V to 4.5V

- Integrated MOSFET with ultra-low Rdson

- Support 3V VBAT to 5V4A output with 93% efficiency

- Programmable VINREG voltage

- Programmable current limit with 25mA/step

- Programmable output voltage with 10mV/step

- Programmable cable drop compensation

- Insert detection for up to three USB ports

- Integrate N-Gate drivers for up to three USB ports

- Voltage and current monitor through IMON pin

- Supports pass-through operation

- Charging status indication

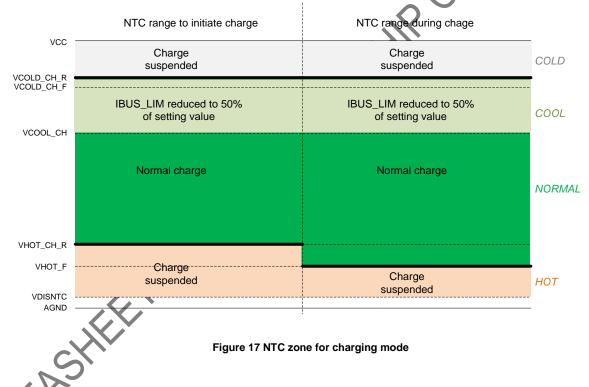

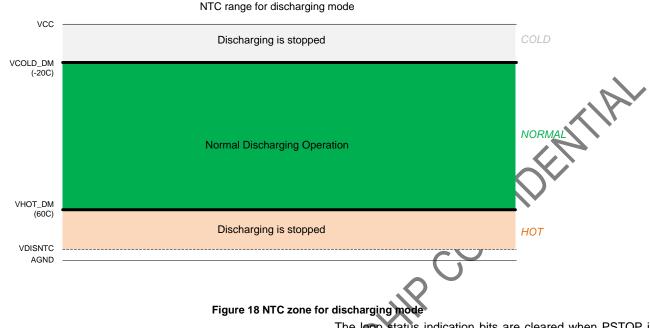

- Support NTC function

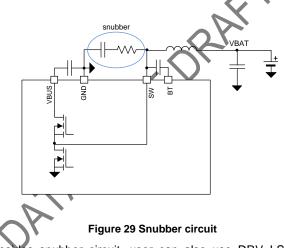

- Under voltage protection and over voltage protection

- Over current protection, short circuit indication and thermal shutdown protection

- QFN-32 4x4 package

## 4 Device Information

| ORDER NUMBER | PACKAGE    | BODY SIZE              |

|--------------|------------|------------------------|

| SC8949QFER   | 32 pin QFN | 4.0mm x 4.0mm x 0.75mm |

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

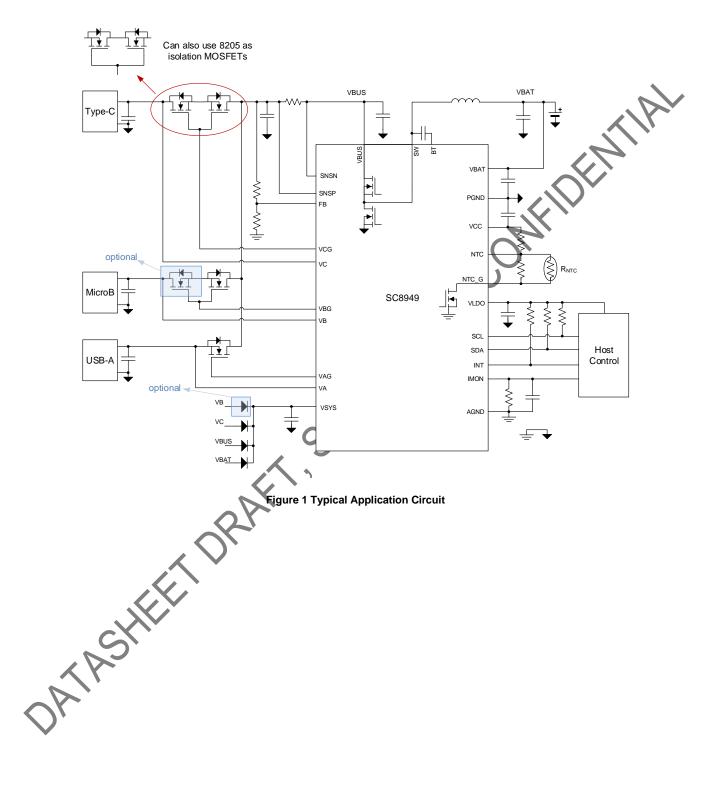

# **5** Typical Application Circuit

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

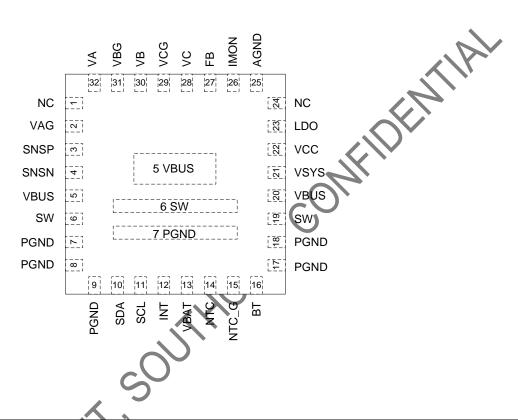

# 6 Terminal Configuration and Functions

#### TOP VIEW

| TERMINAL  |       | I/O | DESCRIPTION                                                                                                                                             |

|-----------|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER    | NAME  | 1/0 | DESCRIPTION                                                                                                                                             |

| 1, 24     | NC    | ĨC, | NC pin. Leave it floating                                                                                                                               |

| 2         | VAG   | ο   | NMOS gate driver to control the external NMOS of VA port. Controlled by VAG_ON bit                                                                      |

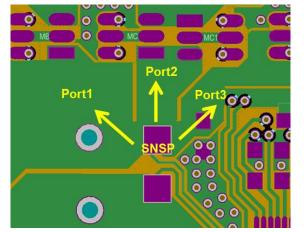

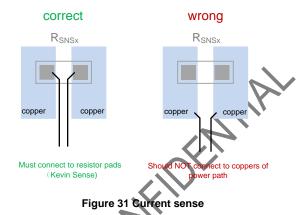

| 3         | SNSP  | _   | Positive input of a current sense amplifier. Connect to one pad of the 10 m $\Omega$ current sense resistor to sense the current into or out from VBUS. |

| 4         | SINSN | I   | Negative input of a current sense amplifier. Connect to one pad of the 10 m $\Omega$ current sense resistor to sense the current into or out from VBUS. |

| 5, 20     | VBUS  | Ю   | Power node of the buck charger.                                                                                                                         |

| 6, 19     | SW    | IO  | Switching Node. Connect to the inductor.                                                                                                                |

| 7-9,17-18 | PGND  | Ю   | Power ground. Connect PGND and AGND together at a single point close to the IC.                                                                         |

| 10        | SDA   | Ю   | I2C data line. Connect with a pull up resistor (typical 4.7 k $\Omega$ ).                                                                               |

| 11        | SCL   | Ι   | I2C clock line. Connect with a pull up resistor (typical 4.7 k $\Omega$ ).                                                                              |

# **SOUTHCHIP SEMICONDUCTOR**

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

| 12 | INT   | 0                       | Open drain output for interrupt signal.                                                                                                                                              |

|----|-------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13 | VBAT  | I                       | Supply current to the IC and also sense the battery voltage. Connect to the battery positive node. Place a 1 $\mu$ F capacitor from this pin to AGND as close to the IC as possible. |

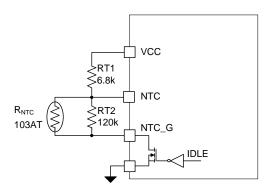

| 14 | NTC   | I                       | Connect to the Negative Temperature Coefficient (NTC) thermistor to sense the battery cell temperature for protection.                                                               |

| 15 | NTC_G | 0                       | Open drain output. It disconnects the NTC resistor from ground in idle mode automatically to save power.                                                                             |

| 16 | ВТ    | I                       | Bootstrap a bias voltage for high side MOSFET driver. Connect a 100nF capacitor between BT pin and SW pin.                                                                           |

| 21 | VSYS  | I                       | Power supply to the IC. Connect to power rails with diodes.<br>Place a 1 $\mu$ F capacitor from this pin to PGND as close to the IC as possible.                                     |

| 22 | VCC   | О                       | Output of internal 5V linear regulator.<br>Connect a 1 $\mu$ F capacitor from VCC pin to <b>FGND</b> as close to the IC as possible.                                                 |

| 23 | LDO   | 0                       | Output of internal linear regulator. The output voltage can be set to 3.3Vor 2.8V through register.                                                                                  |

| 25 | AGND  | IO                      | Analog ground. Connect PGND and AGND together at a single point close to the IC.                                                                                                     |

| 26 | IMON  | 0                       | Used to monitor VBUS / VBAT voltage, IBUS / IBAT current, and the voltage drop of isolation MOS for VA / VB / VC ports                                                               |

| 27 | FB    | I                       | Feedback node of VBUS voltage for external VBUS setting.                                                                                                                             |

| 28 | VC    | I                       | Used to sense the VBUS status of the VC port. Connect a 1 $\mu\text{F}$ capacitor between VC and GND close to the USB port                                                           |

| 29 | VCG   | 0                       | NMOS gate driver to control the external NMOS of VC port. Controlled by VCG_ON bit.                                                                                                  |

| 30 | VB    | $\langle \circ \rangle$ | Used to sense the VBUS status of the VB port. Connect a 1 $\mu F$ capacitor between VB and GND close to the USB port                                                                 |

| 31 | VBG   | ο                       | NMOS gate driver to control the external NMOS of VB port. Controlled by VBG_ON bit.                                                                                                  |

| 32 | CVA   | I                       | Used to sense the VBUS status of the VA port. Connect a 1 $\mu F$ capacitor between VA and GND close to the USB port                                                                 |

| K  | A     |                         | ·                                                                                                                                                                                    |

| OF |       |                         |                                                                                                                                                                                      |

SC8949 DATASHEET DRAFT

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

# 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                           |                                                     | MIN  | MAX | UNIT |

|-------------------------------------------|-----------------------------------------------------|------|-----|------|

|                                           | VA, VB, VC, VBUS, VSYS, SNSP, SNSN                  | -0.3 | 9   |      |

|                                           | SW                                                  | -3   | 9   | V    |

| Voltage range at terminals <sup>(2)</sup> | BT to SW                                            | -0.3 | 6.5 | V    |

|                                           | VAG, VBG, VCG                                       | -0.3 | 14  | V    |

|                                           | FB, IMON, VCC, LDO, NTC, NTC_G, VBAT, INT, SCL, SDA | -0.3 | 6.5 | V    |

| TJ                                        | Operating junction temperature range                | -40  | 150 | °C   |

| T <sub>stg</sub>                          | Storage temperature range                           | -65  | 150 | °C   |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

## 7.2 Thermal Information

| THERMAL RESISTA | QFN-32 (4mmX4mm)                       | UNIT |      |

|-----------------|----------------------------------------|------|------|

| θ <sub>JA</sub> | Junction to ambient thermal resistance | 45   | °C/W |

| θ <sub>JC</sub> | Junction to case resistance            | 9    | °C/W |

(1) Measured on JESD51-7, 4-layer PCB.

# 7.3 Handling Ratings

| PARAMETER          | DEFINITION                                                   | MIN  | MAX | UNIT |

|--------------------|--------------------------------------------------------------|------|-----|------|

| ESD <sup>(1)</sup> | Human body model (HBM) ESD stress voltage <sup>(2)</sup>     | -2   | 2   | kV   |

|                    | Charged device model (CDM) ESD stress voltage <sup>(3)</sup> | -750 | 750 | V    |

(1) Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

(2) Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(3) Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.4 Recommended Operating Conditions

|      |                                                            | MIN | ТҮР | MAX | UNIT |

|------|------------------------------------------------------------|-----|-----|-----|------|

| VBUS | VBUS voltage range –internal setting for discharging mode  | 5   |     | 6   | V    |

|      | VBUS voltage range – external setting for discharging mode | 4.5 |     | 6   | V    |

|      | VBUS voltage range – for charging mode                     | 4.4 |     | 6   | V    |

| VBAT | VBAT voltage range                                         | 2.6 |     | 4.5 | V    |

# SOUTHCHIP SEMICONDUCTOR

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

| CBUS             | Bulk capacitor for VBUS (effective value) | 30  |     |     | μF |

|------------------|-------------------------------------------|-----|-----|-----|----|

| C <sub>BAT</sub> | Bulk capacitor for VBAT (effective value) | 30  |     |     | μF |

| L                | Inductance                                | 1.5 | 2.2 | 3.3 | μH |

| R <sub>SNS</sub> | Current sense resistor                    | 10  |     | 10  | mΩ |

| T <sub>A</sub>   | Operating ambient temperature             | -40 |     | 85  | °C |

| TJ               | Operating junction temperature            | -40 |     | 125 | °C |

| DAIA             | south south                               |     |     |     |    |

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

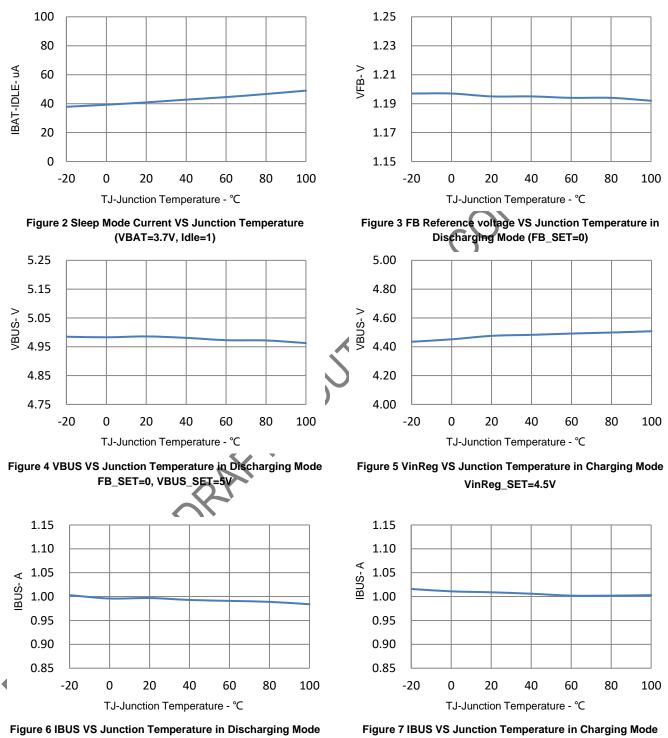

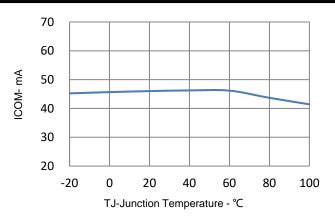

#### 7.5 Electrical Characteristics

$T_{J}\text{=}~25^{\circ}\text{C}$  and  $V_{\text{BUS}}$  = 5V,  $V_{\text{BAT}}$  = 3.6V unless otherwise noted.

| PARAMETER                     |                                     | TEST CONDITIONS                                                        | MIN   | ТҮР  | MAX  | UNIT |

|-------------------------------|-------------------------------------|------------------------------------------------------------------------|-------|------|------|------|

| SUPPLY VO                     | LTAGE                               |                                                                        |       |      |      |      |

|                               | VBUS under-voltage lockout          | Rising edge                                                            | 2.4   | 2.5  | 2.7  |      |

| V <sub>UVLO_VBUS</sub>        | threshold                           | Hysteresis                                                             |       | 180  | ~    | mV   |

|                               | VBAT under-voltage lockout          | Discharging mode, Rising edge                                          |       | 2.47 | 2.6  | V    |

| $V_{UVLO_VBAT}$               | threshold                           | Hysteresis                                                             |       | 220  |      | mV   |

| $I_{Q_VSYS}$                  | Quiescent current into VSYS         | VSYS > VBAT; IDLE = 0,                                                 |       | 0.12 | 0.2  | mA   |

| I <sub>Q_VBAT</sub>           | Quiescent current into VBAT         | non-switching, NTC and FB resistor dividers' bias current not included |       | 5    | 10   | μA   |

|                               |                                     | VSYS open, IDLE = 1                                                    |       | 40   | 70   | μA   |

| I <sub>SB_VBAT</sub>          | Standby current into VBAT           | VSYS > VBAT, IDLE = 1                                                  |       | 3    | 20   | μA   |

| I <sub>SB_VSYS</sub>          | Standby current into VSYS           | VSYS = 5V, IDLE = 1                                                    |       | 70   | 120  | μA   |

| VCC AND LI                    | 00                                  |                                                                        | Z     |      |      |      |

| V <sub>cc</sub>               | VCC regulation voltage              | ICC = 1~70mA<br>IDLE = 0/1                                             | 4.9   | 5.1  | 5.35 | v    |

| 1                             | VCC regulator ourrent limit         | VSYS = VCC + 1V, IDLE = 0/1                                            | 70    | 100  | 130  | mA   |

| I <sub>VCC_LIM</sub>          | VCC regulator current limit         | VCC = 0V                                                               |       | 30   |      | mA   |

| $V_{CC\_DROP}$                | VCC dropout voltage                 | VSYS = 5V, ICC = 70mA                                                  |       | 360  | 440  | mV   |

| VLDO                          | LDO regulation voltage              | LDO set to 3.3V, ILDO = 1~50mA                                         | 3.23  | 3.30 | 3.37 | V    |

| V LDO                         | LDO regulation voltage              | LDO set to 2.8V, ILDO = 1~50mA                                         | 2.73  | 2.80 | 2.87 | V    |

| $V_{\text{LDO}\_\text{DROP}}$ | LDO dropout voltage                 | 1LDO = 50mA, VBAT = 2.7V                                               | 440   | 500  | 640  | mV   |

| SWITCHING                     | AND POWER SWITCH                    |                                                                        |       |      |      |      |

|                               | 0.5                                 | FSW_SET = 00                                                           | 220   | 300  | 380  | kHz  |

| Fsw                           | Switching frequency                 | FSW_SET = 01                                                           | 340   | 450  | 560  | kHz  |

| I SW                          | Switching requercy                  | FSW_SET = 10                                                           | 450   | 600  | 750  | kHz  |

|                               |                                     | FSW_SET = 11                                                           | 550   | 735  | 930  | kHz  |

| $R_{\text{dson}\_\text{HS}}$  | On resistance of high side MOS      |                                                                        |       | 11   |      | mΩ   |

| $R_{\text{dson}\_\text{LS}}$  | On resistance of low side MOS       |                                                                        |       | 8.5  |      | mΩ   |

| VOLTAGE A                     | ND CURRENT IN CHARGING MODE         |                                                                        |       |      |      |      |

|                               |                                     | VBAT_SET = 000, 4.1V target                                            | 4.059 | 4.08 | 4.1  | V    |

| ~~                            |                                     | VBAT_SET = 001, 4.2V target                                            | 4.158 | 4.18 | 4.2  | V    |

| S,                            |                                     | VBAT_SET = 010, 4.25V target                                           | 4.208 | 4.23 | 4.25 | V    |

| V <sub>BAT_ACC</sub>          | Battery voltage regulation accuracy | VBAT_SET = 011, 4.3V target                                            | 4.257 | 4.28 | 4.3  | V    |

|                               |                                     | VBAT_SET = 100, 4.35V target                                           | 4.307 | 4.33 | 4.35 | V    |

|                               |                                     | VBAT_SET = 101, 4.4V target                                            | 4.356 | 4.38 | 4.4  | V    |

|                               |                                     | VBAT_SET = 110, 4.45V target                                           | 4.406 | 4.43 | 4.45 | V    |

# SC8949 DATASHEET DRAFT

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

| Vear. Set = 111, 4.5V target         4.455         4.48         4.5         V           Vear. Set = 101, 4.5V target         4.265         4.48         4.5         V           Vear. Set = 000, 4.4V target         4.265         4.42         4.54         V           VinREG_SET = 001, 4.5V target         4.365         4.52         4.64         V           VinREG_SET = 010, 4.6V target         4.462         4.63         4.74         V           VinREG_SET = 101, 4.6V target         4.462         4.63         4.74         V           VinREG_SET = 101, 4.6V target         4.656         4.83         4.65         V           VinREG_SET = 101, 4.8V target         4.753         4.93         5.06         V           Vince         Over VBAT target         1176KL charge current, measured at<br>BAT         1176KL set = 0         130         260         390         mA           Vince         End of charge current, measured at<br>BAT         1176KL SET = 1         010         20         355         240         mA           Itrus         End of charger current threshold,<br>measured at IBAT         1176KL_SET = 01         90         200         300         mA           Itrus         End of charger current threshold,<br>measured at IBAT         1176KL_SET = 10<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                       |                                     |                                 |       | IFIDENTIAL, |       |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------|---------------------------------|-------|-------------|-------|----|

| Vinsea.vcc         VINREG voltage regulation<br>accuracy         VINREG_SET = 001, 4.5V target         4.365         4.52         4.64         V           VINREG_SET = 010, 4.6V target         4.462         4.63         4.73         4.85         V           VINREG_SET = 100, 4.6V target         4.559         4.73         4.85         V           VINREG_SET = 100, 4.6V target         4.656         4.83         4.50         V           VINREG_SET = 101, 4.7V target         4.656         4.83         4.50         V           VINREG_SET = 101, 4.9V target         4.656         4.83         4.50         V           Vinneg         Trickle charge voltage threshold,<br>over VBAT target         Rising edge         64%         560         680         mA           Iter_ms.         End of charge voltage threshold,<br>measured at IBAT         ITRK_SET = 0         135         240         mA           Iter_ms.         End of charge current threshold,<br>measured at IBAT         ITERM_SET = 01         190         300         400         mA           Iter.ms.         Recharge threshold         ITERM_SET = 01         190         300         400         mA           Iter.ms.         Recharge threshold         ITERM_SET = 01         190         300         400         mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |                                     | VBAT_SET = 111, 4.5V target     | 4.455 | 4.48        | 4.5   | V  |

| Verses         VINREG voltage regulation<br>accuracy         VINREG_SET = 010, 4.6V target         4.462         4.63         4.74         V           VINREG_SET = 010, 4.6V target         4.559         4.73         4.85         V           VINREG_SET = 100, 4.8V target         4.656         4.83         4.95         V           VINREG_SET = 101, 4.9V target         4.656         4.83         4.95         V           VinREG_SET = 101, 4.9V target         4.753         4.93         6.95         V           VinREG_SET = 101, 4.9V target         4.753         4.93         6.95         V           VinREG_SET = 011, 4.9V target         4.753         4.93         6.95         V           VinREG_SET = 101, 4.9V target         64%         66%         66%         M           Iso1         Trickle charge voltage threshold,<br>over VBAT target         ITRRL_SET = 0         130         260         390         mA           Iters_ae         End of charge voltage threshold,<br>measured at IBAT         ITERM_SET = 0         90         200         300         mA           Iters_ae         EOC detection degiltch time         ITERM_SET = 1         190         300         mA           Iters_ae         Recharge threshold         RECH_SET = 0         96.0%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |                                     | VINREG_SET = 000, 4.4V target   | 4.268 | 4.42        | 4.54  | V  |

| Viner         VINREG voltage regulation<br>accuracy         Image: Control of the second of the s                                                                                                                                |                       |                                     | VINREG_SET = 001, 4.5V target   | 4.365 | 4.52        | 4.64  | V  |

| Vesces Acc         accuracy         VINREG_SET = 011, 4.7V target         4.559         4.73         4.85           VINREG_SET = 100, 4.8V target         4.656         4.83         4.65         V           VINREG_SET = 101, 4.8V target         4.656         4.83         4.65         V           VinkeG_SET = 101, 4.9V target         4.753         4.93         5.08         V           VinkeG_SET = 101, 4.9V target         4.753         4.93         5.08         V           VinkeG_SET = 101, 4.9V target         4.753         4.93         5.08         V           VinkeG_SET = 101, 4.9V target         4.753         4.93         5.08         V           Itax mode         Introduction over VBAT target         Intr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       | VINREG voltage regulation           | VINREG_SET = 010, 4.6V target   | 4.462 | 4.63        | 4.74  | V  |

| Image: control of the second                                                                                                          | VINREG_ACC            |                                     | VINREG_SET = 011, 4.7V target   | 4.559 | 4.73        | 4.85  |    |

| Trickle charge voltage threshold,<br>over VBAT target         Reing edge<br>Hysteresis         64%         66%         68%         near<br>Poil           Iaxr_mod.         Trickle charge current, measured at<br>IBAT         ITRKL_SET = 0         130         260         390         mA           Vsoc         End of charge voltage threshold,<br>over VBAT target         ITRKL_SET = 1         490         540         680         mA           Itresu         End of charge voltage threshold,<br>over VBAT target         ITERM_SET = 00         20         135         240         mA           Itresu         End of charge current threshold,<br>measured at IBAT         ITERM_SET = 01         90         200         300         mA           Itresu         EOC detection degitch time         ITERM_SET = 01         190         300         400         mA           Itresu, EE         EOC detection degitch time         Itresu, SET = 0         190         300         400         mA           Itresu, SL         Recharge threshold         RECUSSET_0         96.0%         97.6%         98.8%         Itresu           Isous_um         Recharge threshold         RECUSSET_0         96.0%         97.6%         98.8%         Itresu         Itresu         S           Isous_um         Recharge threshold <td< td=""><td></td><td></td><td>VINREG_SET = 100, 4.8V target</td><td>4.656</td><td>4.83</td><td>4.95</td><td>v</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |                                     | VINREG_SET = 100, 4.8V target   | 4.656 | 4.83        | 4.95  | v  |

| Vrisol.         Investigation of the second second procession of the second second procession of the second second procession of the second secon                                                                                                                   |                       |                                     | VINREG_SET = 101, 4.9V target   | 4.753 | 4.93        | 5.05  | V  |

| Over VBA1 target         Hysteresis         K           IbAT_TR0L         Trickle charge current, measured at<br>IBAT         ITRKL_SET = 0         130         260         390         mA           IBAT         End of charge voltage threshold,<br>over VBAT target         ITRKL_SET = 1         000         540         680         mA           IFTEM         End of charge voltage threshold,<br>measured at IBAT         ITERM_SET = 00         20         135         240         mA           ITERM_SET = 01         90         200         300         mA           ITERM_SET = 10         190         300         400         mA           ITERM_SET = 10         190         300         400         mA           Iteres_seg         EOC detection deglitch time         4         s           VRECH         Recharge threshold         RECHISET = 1         96.0%         97.6%         98.8%           VRECH         Recharge threshold         IBUS_LIM set to 3A, DIR = 0/1         -5%         5%         1           Ibus_LIM         IBUS current limit accuract         IBUS_LIM set to 3A, DIR = 0/1         -5%         5%         1           Ibus_LIM         Minimum JBUS current limit<br>clamping value docuract         Min_IBUS_clamp_setting = 10         170         250                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VTOK                  |                                     | Rising edge                     | 64%   | 66%         | 68%   |    |

| IBAT_TRUE         IBAT         ITRKL_SET = 1         400         540         680         mA           VEoC         End of charge voltage threshold,<br>over VBAT target         1TRKL_SET = 1         987%         99%         100%           Iterm         End of charge voltage threshold,<br>measured at IBAT         1TERM_SET = 00         20         135         240         mA           ItERM_SET = 00         20         135         240         mA           ItERM_SET = 01         90         200         300         mA           ItERM_SET = 10         190         300         400         mA           Iteoc_steg         EOC detection deglitch time         4         s         s           VRECH         Recharge threshold         RECHISET = 1         95.0%         96.4%         97.8%           VRECH         Recharge threshold         IBUS_LIM set to 3A, DIR = 0/1         -5%         5%         1           Ibus_LIM         IBUS current limit accuracy         IBUS_LIM set to 2A, DIR = 0/1         -5%         5%         1           Ibus_LIM         IBUS_LIM set to 5A, DIR = 0/1         -5%         5%         1         1           Ibus_LIM         Itemp.setting = 10         170         260         330         mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | V IRKL                | over VBAT target                    | Hysteresis                      |       | 4%          |       |    |

| IBAI         ITRKL_SET = 1         M00         540         680         mA           VEoc         End of charge voltage threshold,<br>over VBAT target         ITERM_SET = 00         20         135         240         mA           Interm         End of charger current threshold,<br>measured at IBAT         ITERM_SET = 00         20         135         240         mA           ITERM_SET = 01         90         200         300         mA           ITERM_SET = 10         190         300         400         mA           ITERM_SET = 10         190         300         400         mA           Itecc_exeg         EOC detection deglitch time         4         s           VRECH         Recharge threshold         RECH_SET = 0         96.0%         97.6%         98.8%           VRECH         IBUS_LIM set to 3A, DIR = 0/1         -5%         5%         IBUS_LIM set to 2A, DIR = 0/1         -5%         5%           IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%         mA         MA           IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%         mA           In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | la                    | Trickle charge current, measured at | ITRKL_SET = 0                   | 130   | 260         | 390   | mA |

| Vecc         over VBAT target         IDD/s           Interval         End of charger current threshold<br>measured at IBAT         ITERM_SET = 00         20         135         240         mA           ITERM_SET = 01         90         200         300         mA           ItERM_SET = 10         190         300         400         mA           ItERM_SET = 11         290         400         500         mA           VaccH         Recharge threshold         RECIPIENT         95.0%         96.4%         97.8%           URRENT LIMIT         IBUS_LIM set to 3A, DIR = 0/1         -5%         5%         1           IBUS_LIM         IBUS current limit accuracy         IBUS_LIM set to 2A, DIR = 0/1         -5%         5%         1           IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%         mA         1         1           IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%         MA         1         1         1         20%         20%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 'BAI_IRKL             | IBAT                                | ITRKL_SET = 1                   | 400   | 540         | 680   | mA |

| ITERM         End of charger current threshold,<br>measured at IBAT         ITERM_SET = 01         90         200         300         mA           ITERM_SET = 10         190         300         400         mA           ITERM_SET = 10         190         300         400         mA           ITERM_SET = 10         190         300         400         mA           Iteoc_seg         EOC detection deglitch time         4         s           VRECH         Recharge threshold         RECHISET = 0         96.0%         97.6%         98.6%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>EOC</sub>      |                                     |                                 | 98%   | 99%         | 100%  |    |

| ITEEM         Interstant of the strange of an one based of the strange of an one based of the strange of an one based of the strange of the                                                                                                                   |                       |                                     | ITERM_SET = 00                  | 20    | 135         | 240   | mA |

| International field         ITERM_SET = 10         190         300         400         mA           Iteoc_deg         EOC detection deglitch time         290         400         500         mA           Iteoc_deg         EOC detection deglitch time         4         s           VRECH         Recharge threshold         RECH_SET=0         96.0%         97.6%         98.8%           CURRENT LIMIT         RECH_SET=1         95.0%         96.4%         97.8%            IBUS_LIM         IBUS current limit accuracy         IBUS_LIM set to 3A, DIR = 0/1         -5%         5%            IBUS_LIM         IBUS current limit couracy         IBUS_LIM set to 2A, DIR = 0/1         -5%         5%            IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%              IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%              IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%              IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%              IBUS_LIM set to 0.5A, DIR = 0/1         -20%         300         mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                     | •                                   | ITERM_SET = 01                  | 90    | 200         | 300   | mA |

| teoc_deg         EOC detection deglitch time         4         s           VRECH         Recharge threshold         RECH_SET_0         96.0%         97.6%         98.8%           CURRENT LIMIT         RECH_SET_1         95.0%         96.4%         97.8%            IBUS_LIM         IBUS current limit accuracy         IBUS_LIM set to 3A, DIR = 0/1         -5%         5%            IBUS_LIM         IBUS current limit accuracy         IBUS_LIM set to 2A, DIR = 0/1         -5%         5%            IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%              IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%              IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%              IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%              IBUS_LIM set to 0.5A, DIR = 0/1         120         200         280         mA            IBUS_LIM set to 0.5A, DIR = 0         120         200         280         mA            IBUS_LIM set to 0.5A, DIR = 0         50         125         330         mA            I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ITERM                 |                                     | ITERM_SET = 10                  | 190   | 300         | 400   | mA |

| Recharge threshold         RECH-SET = 0         96.0%         97.6%         98.8%           RECH-SET = 1         95.0%         96.4%         97.8%           CURRENT LIMIT           IBUS_LIM         IBUS current limit accuracy         IBUS_LIM set to 3A, DIR = 0/1         -5%         5%           IBUS_LIM         IBUS current limit accuracy         IBUS_LIM set to 2A, DIR = 0/1         -5%         5%           IBUS_LIM set to 0.5A, DIR = 0/1         -5%         5%         1           IBUS_LIM set to 0.5A, DIR = 0/1         -5%         20%           Min_IBUS_clamp_setting = 00         50         125         200         mA           Min_IBUS_clamp_setting = 01         120         200         280         mA           Min_IBUS_clamp_setting = 10         170         250         330         mA           Min_IBUS_clamp_setting = 11         220         300         380         mA           IBAT_LIM = 00, DIR = 0         3.6         3.9         4.3         A           IBAT_LIM = 10, DIR = 0         7         7.6         8.3         A           IBAT_LIM = 00, DIR = 1         5.2         5.7         6.3         A           IBAT_LIM = 01, DIR = 1         7         7.6         8.3 <td></td> <td>ITERM_SET = 11</td> <td>290</td> <td>400</td> <td>500</td> <td>mA</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |                                     | ITERM_SET = 11                  | 290   | 400         | 500   | mA |

| VRECH         Recharge threshold         RECH_SET = 1         95.0%         96.4%         97.8%           CURRENT LIMIT         IBUS_CURRENT LIMIT         IBUS_LIM set to 3A, DIR = 0/1         -5%         5%         1           IBUS_LIM         IBUS current limit accuracy         IBUS_LIM set to 3A, DIR = 0/1         -5%         5%         1           IBUS_LIM set to 0.5A, DIR = 0/1         -5%         5%         1         20%         20%           IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%         1         10         200         280         mA           IBUS_MIN         Minimum IBUS current limit<br>clamping value accuracy         Min_IBUS_clamp_setting = 01         120         200         280         mA           Min_IBUS_clamp_setting = 10         170         250         330         mA           Min_IBUS_clamp_setting = 11         220         300         380         mA           IBAT_LIM = 00, DIR = 0         3.6         3.9         4.3         A           IBAT_LIM = 10, DIR = 0         7         7.6         8.3         A           IBAT_LIM = 00, DIR = 1         5.2         5.7         6.3         A           IBAT_LIM = 01, DIR = 1         7         7.6         8.3         A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $t_{\text{EOC\_deg}}$ | EOC detection deglitch time         | $\sim$                          |       | 4           |       | s  |

| RECH_SET = 1         95.0%         96.4%         97.8%           CURRENT LIMIT         IBUS_LIM set to 3A, DIR = 0/1         -5%         5%           IBUS_LIM set to 2A, DIR = 0/1         -5%         5%         1           IBUS_LIM set to 0.5A, DIR = 0/1         -5%         5%         1           IBUS_LIM set to 0.5A, DIR = 0/1         -5%         5%         1           IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%         1           IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%         1           IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%         1           IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%         1           IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%         MA           Min_IBUS_clamp_setting = 00         50         125         200         MA           Min_IBUS_clamp_setting = 10         170         250         330         MA           Min_IBUS_clamp_setting = 11         220         300         380         MA           IBAT_LIM = 00, DIR = 0         5.5         5.7         6.0         A           IBAT_LIM = 00, DIR = 0         7         7.6         8.3         A           IBAT_LIM = 00,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V                     | Deck owner there also also          | RECH_SET = 0                    | 96.0% | 97.6%       | 98.8% |    |

| IBUS_LIM         IBUS current limit accuracy         IBUS_LIM set to 3A, DIR = 0/1         -5%         5%           IBUS_LIM set to 2A, DIR = 0/1         -5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         5%         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VRECH                 | Recharge threshold                  | RECH_SET = 1                    | 95.0% | 96.4%       | 97.8% |    |

| IBUS_LIM         IBUS current limit accuracy         IBUS_LIM set to 2A, DIR = 0/1         -5%         5%           IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         1000         10000         1000         1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CURRENT LIN           | літ                                 |                                 |       |             |       |    |

| IBUS_LIM set to 0.5A, DIR = 0/1         -20%         20%           IBUS_MIN         Minimum IBUS current limit<br>clamping value accuracy         Min_IBUS_clamp_setting = 00         50         125         200         mA           Min_IBUS_clamp_setting = 01         120         200         280         mA           Min_IBUS_clamp_setting = 01         170         250         330         mA           Min_IBUS_clamp_setting = 10         170         250         330         mA           Min_IBUS_clamp_setting = 11         220         300         380         mA           Min_IBUS_clamp_setting = 11         220         300         380         mA           IBAT_LIM = 00, DIR = 0         3.6         3.9         4.3         A           IBAT_LIM = 01, DIR = 0         5.5         5.7         6.0         A           IBAT_LIM = 10, DIR = 0         7         7.6         8.3         A           IBAT_LIM = 00, DIR = 1         5.2         5.7         6.3         A           IBAT_LIM = 01, DIR = 1         7         7.6         8.3         A           IBAT_LIM = 10, DIR = 1         7         7.6         8.3         A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |                                     | IBUS_LIM set to 3A, DIR = 0/1   | -5%   |             | 5%    |    |

| IBUS_MIN         Min_IBUS_current limit<br>clamping value accuracy         Min_IBUS_clamp_setting = 00         50         125         200         mA           Min_IBUS_clamp_setting = 01         120         200         280         mA           Min_IBUS_clamp_setting = 10         170         250         330         mA           Min_IBUS_clamp_setting = 10         170         250         330         mA           Min_IBUS_clamp_setting = 11         220         300         380         mA           Min_IBUS_clamp_setting = 11         220         300         380         mA           IBAT_LIM = 00, DIR = 0         3.6         3.9         4.3         A           IBAT_LIM = 01, DIR = 0         5.5         5.7         6.0         A           IBAT_LIM = 10, DIR = 0         7         7.6         8.3         A           IBAT_LIM = 10, DIR = 1         5.2         5.7         6.3         A           IBAT_LIM = 01, DIR = 1         7         7.6         8.3         A           IBAT_LIM = 01, DIR = 1         7         7.6         8.3         A           IBAT_LIM = 10, DIR = 1         7         7.6         8.3         A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I <sub>BUS_LIM</sub>  | IBUS current limit accuracy         | IBUS_LIM set to 2A, DIR = 0/1   | -5%   |             | 5%    |    |

| IBUS_MIN         Minimum IBUS current limit<br>clamping value accuracy         Min_IBUS_clamp_setting = 01         120         200         280         mA           Min_IBUS_clamp_setting = 10         170         250         330         mA           Min_IBUS_clamp_setting = 10         170         250         330         mA           Min_IBUS_clamp_setting = 11         220         300         380         mA           IBAT_LIM = 00, DIR = 0         3.6         3.9         4.3         A           IBAT_LIM = 01, DIR = 0         5.5         5.7         6.0         A           IBAT_LIM = 10, DIR = 0         7         7.6         8.3         A           IBAT_LIM = 00, DIR = 1         5.2         5.7         6.3         A           IBAT_LIM = 00, DIR = 1         5.2         5.7         6.3         A           IBAT_LIM = 00, DIR = 1         5.2         5.7         6.3         A           IBAT_LIM = 00, DIR = 1         7         7.6         8.3         A           IBAT_LIM = 01, DIR = 1         7         7.6         8.3         A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |                                     | IBUS_LIM set to 0.5A, DIR = 0/1 | -20%  |             | 20%   |    |

| Ibus_MIN         Imminuity of constraint intercement         Imminuity of constraint intercement<                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |                                     | Min_IBUS_clamp_setting = 00     | 50    | 125         | 200   | mA |

| Min_IBUS_clamp_setting = 10         170         250         330         mA           Min_IBUS_clamp_setting = 11         220         300         380         mA           Min_IBUS_clamp_setting = 11         220         300         380         mA           IBAT_LIM = 00, DIR = 0         3.6         3.9         4.3         A           IBAT_LIM = 01, DIR = 0         5.5         5.7         6.0         A           IBAT_LIM = 10, DIR = 0         7         7.6         8.3         A           IBAT_LIM = 10, DIR = 0         8.8         9.5         10.5         A           IBAT_LIM = 01, DIR = 1         5.2         5.7         6.3         A           IBAT_LIM = 01, DIR = 1         7         7.6         8.3         A           IBAT_LIM = 01, DIR = 1         7         7.6         8.3         A           IBAT_LIM = 01, DIR = 1         7         7.6         8.3         A           IBAT_LIM = 01, DIR = 1         7         7.6         8.3         A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                     | Minimum IBUS current limit          | Min_IBUS_clamp_setting = 01     | 120   | 200         | 280   | mA |

| IBAT_LIM         IIBAT_LIM         IIIBAT_LIM         IIIBAT_LIM         IIIBAT_LIM         IIIIA         IIIIA         IIIIA         IIIIA         IIIIA         IIIIA         IIIIIA         IIIIA         IIIIIA         IIIIIA         IIIIIA         IIIIIA         IIIIIA         IIIIIIA         IIIIIIIIA         IIIIIIIIA         IIIIIIIIIIIIIA         IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BUS_MIN               | clamping value accuracy             | Min_IBUS_clamp_setting = 10     | 170   | 250         | 330   | mA |

| $IBAT\_LIM = 01, DIR = 0$ $IBAT\_LIM = 01, DIR = 0$ $IBAT\_LIM = 10, DIR = 0$ $IBAT\_LIM = 10, DIR = 0$ $IBAT\_LIM = 10, DIR = 0$ $IBAT\_LIM = 11, DIR = 0$ $IBAT\_LIM = 11, DIR = 0$ $IBAT\_LIM = 00, DIR = 1$ $IBAT\_LIM = 00, DIR = 1$ $IBAT\_LIM = 01, DIR = 1$ $IBAT\_LIM = 01, DIR = 1$ $IBAT\_LIM = 01, DIR = 1$ $IBAT\_LIM = 10, DIR $ |                       |                                     | Min_IBUS_clamp_setting = 11     | 220   | 300         | 380   | mA |

| $I_{BAT\_LIM} = 01, DIR = 1$ $IBAT\_LIM = 01, DIR = 1$                                                                                                                                                                                                                                                                                                                   | 1                     | S.                                  | IBAT_LIM = 00, DIR = 0          | 3.6   | 3.9         | 4.3   | А  |

| $I_{BAT\_LIM} = 01, DIR = 1$ $IBAT\_LIM = 01, DIR = 1$                                                                                                                                                                                                                                                                                                                   | <b></b>               | K                                   | IBAT_LIM = 01, DIR = 0          | 5.5   | 5.7         | 6.0   | А  |

| $I_{BAT\_LIM} = 01, DIR = 1$ $IBAT\_LIM = 01, DIR = 1$                                                                                                                                                                                                                                                                                                                   | ~~)                   |                                     | IBAT_LIM = 10, DIR = 0          | 7     | 7.6         | 8.3   | A  |

| IBAT_LIM = 00, DIR = 1         5.2         5.7         6.3         A           IBAT_LIM = 01, DIR = 1         7         7.6         8.3         A           IBAT_LIM = 10, DIR = 1         8.8         9.5         10.5         A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\langle \rangle$     |                                     | IBAT_LIM = 11, DIR = 0          | 8.8   | 9.5         | 10.5  | А  |