# ESDALC6V1W5

## Quad TRANSIL<sup>™</sup> array for data protection

## Main applications

Where transient overvoltage protection in ESD sensitive equipment is required, such as :

- Computers

- Printers

- Communication systems

- Cellular phones and accessories

- Wireline and wireless telephone sets

- Set top boxes

### Features

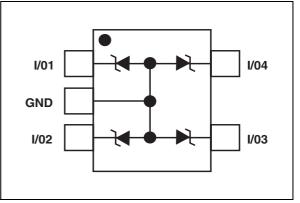

- 4 Unidirectional Transil functions

- Breakdown voltage:

V<sub>BR</sub> = 6.1 V minimum

- Low leakage current: < 1 µA

- Low capacitance: 7.5 pF at 3 V

- Very small PCB area < 4.2 mm<sup>2</sup> typically

### Description

The ESDALCxxxWx are monolithic suppressors designed to protect components connected to data and transmission lines against ESD.

These devices clamp the voltage just above the logic level supply for positive transients, and to a diode drop below ground for negative transients.

### **Benefits**

- High ESD protection level: up to 25 kV

- High integration

#### Order codes

| Part Number | Marking |  |  |

|-------------|---------|--|--|

| ESDALC6V1W5 | C61     |  |  |

#### ESDALC6V1W5 Functional diagram

### Complies with the following standards

#### IEC61000-4-2

Level 4 15 kV (air discharge) 8 kV(contact discharge)

#### MIL STD 883E - Method 3015-7 Class 3

25 kV HBM (Human Body Model)

TM: TRANSIL is a trademark of STMicroelectronics

January 2006

www.st.com

# 1 Characteristics

| Table 1. | Absolute Ratings   | $(T = 25^{\circ}C)$ |

|----------|--------------------|---------------------|

|          | Absolute natilitys | $(1_{amb} - 25 C)$  |

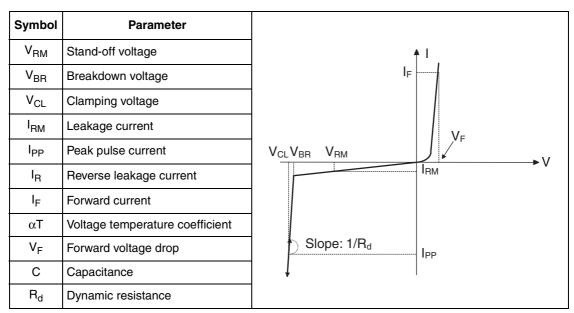

| Symbol           | Parameter                                         | Value       | Unit |

|------------------|---------------------------------------------------|-------------|------|

| P <sub>PP</sub>  | Peak pulse power (8/20 µs)                        | 25          | W    |

| Тj               | Junction temperature                              | 150         | °C   |

| T <sub>stg</sub> | Storage temperature range                         | -55 to +150 | °C   |

| TL               | Maximum lead temperature for soldering during 10s | 260         | °C   |

| T <sub>op</sub>  | Operating temperature range <sup>(1)</sup>        | -40 to +150 | °C   |

1. The values of the operating parameters versus temperature are given through curves and  $\alpha T$  parameter.

## **1.1** Electrical Characteristics (Tamb = 25°C)

|              | V <sub>BR</sub> @ I <sub>R</sub> |      | I <sub>RM</sub> @ V <sub>RM</sub> |      | R <sub>d</sub> | αΤ                  | С                    |                 |

|--------------|----------------------------------|------|-----------------------------------|------|----------------|---------------------|----------------------|-----------------|

| Part Numbers | min.                             | max. |                                   | max. |                | typ. <sup>(1)</sup> | max. <sup>(2)</sup>  | typ.<br>3V bias |

|              | v                                | v    | mA                                | μA   | v              | Ω                   | 10 <sup>-4</sup> /°C | pF              |

| ESDALC6V1W5  | 6.1                              | 7.2  | 1                                 | 1    | 3              | 1.1                 | 6                    | 7.5             |

1. Square pulse  $I_{pp}$  = 15 A,  $t_p$  = 2.5  $\mu s$

2.  $V_{BR} = aT^* (T_{amb} - 25 \text{ °C}) * V_{BR} (25 \text{ °C})$

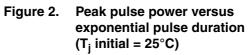

# Figure 1. Peak power dissipation versus initial junction temperature

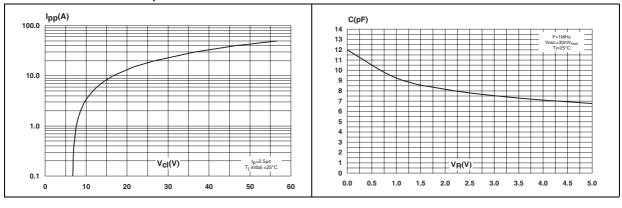

Figure 3. Clamping voltage versus peak pulse Figure 4. current ( $T_j$  initial = 25°C, rectangular waveform,  $t_p$  = 2.5 µs)

Capacitance versus reverse applied voltage (typical values)

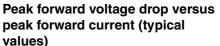

Figure 5. Relative variation of leakage current Figure 6. versus junction temperature (typical values)

57

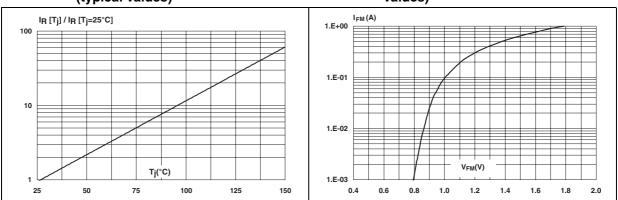

# Figure 7. ESD response to IEC61000-4-2 (air discharge 15 kV, positive surge)

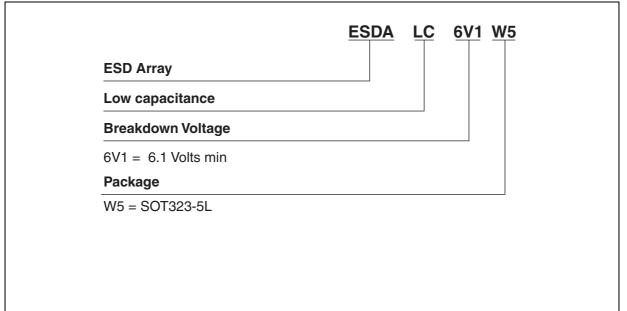

# 2 Ordering information scheme

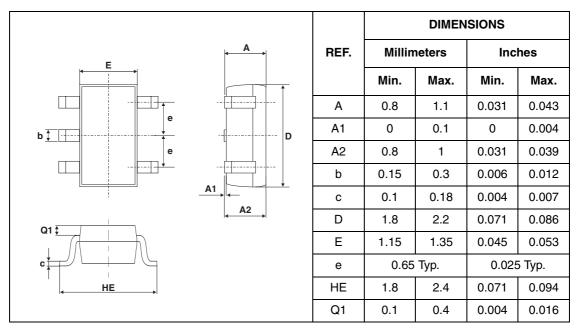

## 3 Package mechanical data

### 3.1 SOT323-5L package

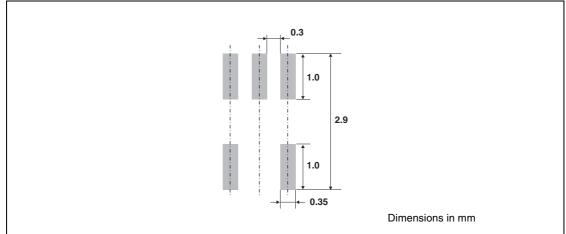

### Figure 8. Footprint dimensions

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

6/7

# 4 Ordering information

| Part Number | Marking | Package   | Weight | Base qty | Delivery mode |

|-------------|---------|-----------|--------|----------|---------------|

| ESDALC6V1W5 | C61     | SOT323-5L | 5.4 mg | 3000     | Tape & reel   |

# 5 Revision history

| Date        | Revision | Changes                                                                                                                                                                              |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Jun-2002    | 4A       | Previous issue                                                                                                                                                                       |

| 10-Jan-2006 | 5        | Reformatted to current template.<br>Figure 5: Range of T <sub>j</sub> extended to 150 °C.<br>Figure 6: Peak forward voltage drop versus peak forward current (typical values) added. |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2006 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

7/7

单击下面可查看定价,库存,交付和生命周期等信息

>>STMicro(意法半导体)