## High voltage high/low-side driver

Datasheet - production data

**SO-16**

#### **Features**

- High voltage rail up to 600 V

- dV/dt immunity ± 50 V/nsec in full temperature range

- Driver current capability: 290 mA source, 430 mA sink

- Switching times 75/35 nsec rise/fall with 1 nF load

- 3.3 V, 5 V TTL/CMOS inputs with hysteresis

- Integrated bootstrap diode

- Operational amplifier for advanced current sensing

- · Comparator for fast fault protection

- Smart shutdown function

- Adjustable deadtime

- Interlocking function

- Compact and simplified layout

- · Bill of material reduction

### **Applications**

- Home appliances

- Motor drivers

- DC, AC, PMDC and PMAC motors

- FOC and sensorless BEMF detection systems

- Industrial applications and drives

This is information on a product in full production.

- Induction heating

- HVAC

- Factory automation

- Power supply systems

### **Description**

The L6390 is a full featured high voltage device manufactured with the BCD <sup>TM</sup> "offline" technology. It is a single-chip half-bridge gate driver for N-channel power MOSFETs or IGBTs. The high-side (floating) section is able to work with voltage rail up to 600 V.

Both device outputs can sink and source 430 mA and 290 mA respectively. Prevention from cross conduction is ensured by interlocking and programmable deadtime functions.

The device has dedicated input pins for each output and a shutdown pin. The logic inputs are CMOS/TTL compatible down to 3.3 V for easy interfacing with control devices. Matched delays between low-side and high-side sections guarantee no cycle distortion and allow high frequency operation.

The L6390 embeds an operational amplifier suitable for advanced current sensing in applications such as field oriented motor control or for sensorless BEMF detection. A comparator featuring advanced smartSD function is also integrated in the device, ensuring fast and effective protection against fault events like overcurrent, overtemperature, etc.

The L6390 device features also UVLO protection on both the lower and upper driving sections, preventing the power switches from operating in low efficiency or dangerous conditions.

The integrated bootstrap diode as well as all of the integrated features of this IC make the application PCB design easier, more compact and simple thus reducing the overall bill of material.

The device is available in an SO-16 tube and tape and reel packaging options.

## **Contents**

| 1  | Block diagram                            |    |  |  |  |  |

|----|------------------------------------------|----|--|--|--|--|

| 2  | Pin connection                           | 4  |  |  |  |  |

| 3  | Electrical data                          | 5  |  |  |  |  |

|    | 3.1 Absolute maximum ratings             | 5  |  |  |  |  |

|    | 3.2 Thermal data                         | 5  |  |  |  |  |

|    | 3.3 Recommended operating conditions     | 6  |  |  |  |  |

| 4  | Electrical characteristics               | 7  |  |  |  |  |

|    | 4.1 AC operation                         | 7  |  |  |  |  |

|    | 4.2 DC operation                         | 9  |  |  |  |  |

| 5  | Timing and waveforms definitions         | 12 |  |  |  |  |

| 6  | Input logic                              | 14 |  |  |  |  |

| 7  | Smart shutdown function                  | 15 |  |  |  |  |

| 8  | Typical application diagram              | 18 |  |  |  |  |

| 9  | Bootstrap driver                         | 19 |  |  |  |  |

|    | C <sub>BOOT</sub> selection and charging | 19 |  |  |  |  |

| 10 | Package information                      | 21 |  |  |  |  |

|    | 10.1 SO-16 package information           | 21 |  |  |  |  |

| 11 | Order codes                              | 23 |  |  |  |  |

| 12 | Revision history                         | 24 |  |  |  |  |

L6390 Block diagram

# 1 Block diagram

BOOTSTRAP DRIVER \_FLOATING STRUCTURE BOOT vcc ¢ --- from LVG UV DETECTION UV DETECTION HVG DRIVER 15 LEVEL SHIFTER HVG **LOGIC** SHOOT THROUGH PREVENTION out 🖒 LIN ( V<sub>C</sub>C LVG DRIVER LVG SD LATCH SD/OD 5V SMART SD COMPARATOR 10 GND 6 CP+ DEAD VCC TIME OPAMP OP+  $OPOUT \phi^{\frac{7}{2}}$

Figure 1. Block diagram

Pin connection L6390

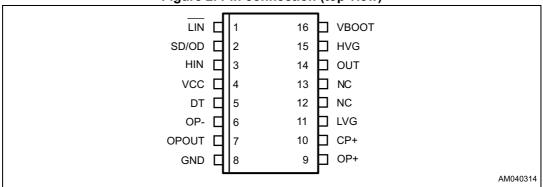

## 2 Pin connection

Figure 2. Pin connection (top view)

Table 1. Pin description

| Pin no. | Pin name           | Туре | Function                                                         |

|---------|--------------------|------|------------------------------------------------------------------|

| 1       | LIN                | I    | Low-side driver logic input (active low)                         |

| 2       | SD/OD (1)          | I/O  | Shutdown logic input (active low)/open drain (comparator output) |

| 3       | HIN                | I    | High-side driver logic input (active high)                       |

| 4       | VCC                | Р    | Lower section supply voltage                                     |

| 5       | DT                 | I    | Deadtime setting                                                 |

| 6       | OP-                | I    | Op amp inverting input                                           |

| 7       | OPOUT              | 0    | Op amp output                                                    |

| 8       | GND                | Р    | Ground                                                           |

| 9       | OP+                | I    | Op amp non-inverting input                                       |

| 10      | CP+                | I    | Comparator input                                                 |

| 11      | LVG <sup>(1)</sup> | 0    | Low-side driver output                                           |

| 12, 13  | NC                 |      | Not connected                                                    |

| 14      | OUT                | Р    | High-side (floating) common voltage                              |

| 15      | HVG <sup>(1)</sup> | 0    | High-side driver output                                          |

| 16      | BOOT               | Р    | Bootstrap supply voltage                                         |

The circuit provides less than 1 V on the LVG and HVG pins (at I<sub>sink</sub> = 10 mA), with V<sub>CC</sub> > 3 V. This allows

the omission of the "bleeder" resistor connected between the gate and the source of the external MOSFET

normally used to hold the pin low; the gate driver assures low impedance also in SD condition.

L6390 Electrical data

## 3 Electrical data

## 3.1 Absolute maximum ratings

Table 2. Absolute maximum ratings

| Comple of             | Dougranton                                       | Va                     | lue                     | l l mit |

|-----------------------|--------------------------------------------------|------------------------|-------------------------|---------|

| Symbol                | Parameter                                        | Min.                   | Max.                    | Unit    |

| V <sub>CC</sub>       | Supply voltage                                   | - 0.3                  | 21                      | V       |

| V <sub>OUT</sub>      | Output voltage                                   | V <sub>BOOT</sub> - 21 | V <sub>BOOT</sub> + 0.3 | V       |

| V <sub>BOOT</sub>     | Bootstrap voltage                                | - 0.3                  | 620                     | V       |

| V <sub>hvg</sub>      | High-side gate output voltage                    | V <sub>OUT</sub> - 0.3 | V <sub>BOOT</sub> + 0.3 | V       |

| V <sub>Ivg</sub>      | Low-side gate output voltage                     | - 0.3                  | V <sub>CC</sub> + 0.3   | V       |

| V <sub>OP+</sub>      | Op amp non-inverting input                       | - 0.3                  | V <sub>CC</sub> + 0.3   | V       |

| V <sub>OP-</sub>      | Op amp inverting input                           | - 0.3                  | V <sub>CC</sub> + 0.3   | V       |

| V <sub>CP+</sub>      | Comparator input voltage                         | - 0.3                  | V <sub>CC</sub> + 0.3   | V       |

| Vi                    | Logic input voltage                              | - 0.3                  | 15                      | V       |

| V <sub>od</sub>       | Open drain voltage                               | - 0.3                  | 15                      | V       |

| dV <sub>OUT</sub> /dt | Allowed output slew rate                         | -                      | 50                      | V/ns    |

| P <sub>tot</sub>      | Total power dissipation (T <sub>A</sub> = 25 °C) | -                      | 800                     | mW      |

| T <sub>J</sub>        | Junction temperature                             | -                      | 150                     | °C      |

| T <sub>stg</sub>      | Storage temperature                              | -50                    | 150                     | °C      |

| ESD                   | Human body model                                 |                        | 2                       | kV      |

### 3.2 Thermal data

Table 3. Thermal data

|   | Symbol              | Parameter                              | SO-16 | Unit |

|---|---------------------|----------------------------------------|-------|------|

| Ī | R <sub>th(JA)</sub> | Thermal resistance junction to ambient | 120   | °C/W |

Electrical data L6390

## 3.3 Recommended operating conditions

Table 4. Recommended operating conditions

| Symbol                         | Pin     | Parameter               | Test condition                      | Min.               | Max. | Unit |

|--------------------------------|---------|-------------------------|-------------------------------------|--------------------|------|------|

| V <sub>CC</sub>                | 4       | Supply voltage          | -                                   | 12.5               | 20   | V    |

| V <sub>BO</sub> <sup>(1)</sup> | 16 - 14 | Floating supply voltage | -                                   | 12.4               | 20   | V    |

| V <sub>OUT</sub>               | 14      | DC output voltage       | -                                   | - 9 <sup>(2)</sup> | 580  | ٧    |

| f <sub>sw</sub>                | -       | Switching frequency     | HVG, LVG load C <sub>L</sub> = 1 nF | -                  | 800  | kHz  |

| TJ                             | -       | Junction temperature    | -                                   | -40                | 125  | °C   |

<sup>1.</sup>  $V_{BO} = V_{BOOT} - V_{OUT}$

6/25 DocID14493 Rev 11

<sup>2.</sup> LVG off.  $V_{CC}$  = 12.5 V. Logic is operational if  $V_{BOOT}$  > 5 V. Refer to the AN2738 for more details.

## 4 Electrical characteristics

## 4.1 AC operation

Table 5. AC operation electrical characteristics (V<sub>CC</sub> = 15 V; T<sub>J</sub> = +25 °C)

| Symbol           | Pin          | Parameter                                                                | Test condition                                                                     | Min. | Тур. | Max. | Unit |

|------------------|--------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>on</sub>  | 1 vs. 11     | High/low-side driver turn-on propagation delay                           | V <sub>OUT</sub> = 0 V                                                             | 50   | 125  | 200  | ns   |

| t <sub>off</sub> | 3 vs. 15     | High/low-side driver turn-off propagation delay                          | $V_{BOOT} = V_{CC}$ $C_L = 1 \text{ nF}$ $V_i = 0 \text{ to } 3.3 \text{ V}$       | 50   | 125  | 200  | ns   |

| t <sub>sd</sub>  | 2 vs. 11, 15 | Shutdown to high/low-side driver propagation delay                       | See Figure 4 on page 12                                                            | 50   | 125  | 200  | ns   |

| t <sub>isd</sub> | -            | Comparator triggering to high/low-side driver turn-off propagation delay | Measured applying a voltage step from 0 V to 3.3 V to pin CP+.                     | 50   | 200  | 250  | ns   |

| MT               | -            | Delay matching, HS and LS turn-on/off                                    | -                                                                                  | -    | -    | 30   | ns   |

|                  |              |                                                                          | R <sub>DT</sub> = 0, C <sub>L</sub> = 1 nF                                         | 0.1  | 0.18 | 0.25 | μS   |

|                  |              | $R_{DT}$ = 37 k $\Omega$ , $C_L$ = 1 nF,<br>$C_{DT}$ = 100 nF            | 0.48                                                                               | 0.6  | 0.72 | μS   |      |

| DT               | 5            | Deadtime setting range <sup>(1)</sup>                                    | $R_{DT} = 136 \text{ k}\Omega, C_{L} = 1 \text{ nF},$<br>$C_{DT} = 100 \text{ nF}$ | 1.35 | 1.6  | 1.85 | μS   |

|                  |              |                                                                          | $R_{DT}$ = 260 k $\Omega$ , $C_L$ = 1 nF, $C_{DT}$ = 100 nF                        | 2.6  | 3.0  | 3.4  | μS   |

|                  |              |                                                                          | R <sub>DT</sub> = 0, C <sub>L</sub> = 1 nF                                         | 1    | -    | 80   | ns   |

|                  |              |                                                                          | $R_{DT}$ = 37 k $\Omega$ , $C_L$ = 1 nF,<br>$C_{DT}$ = 100 nF                      | -    | -    | 120  | ns   |

| MDT              | -            | Matching deadtime <sup>(2)</sup>                                         | $R_{DT}$ = 136 k $\Omega$ , $C_L$ = 1 nF,<br>$C_{DT}$ = 100 nF                     | -    | -    | 250  | ns   |

|                  |              |                                                                          | $R_{DT}$ = 260 k $\Omega$ , $C_{L}$ = 1 nF,<br>$C_{DT}$ = 100 nF                   | ı    | -    | 400  | ns   |

| t <sub>r</sub>   | 11, 15       | Rise time                                                                | C <sub>L</sub> = 1 nF                                                              | -    | 75   | 120  | ns   |

| t <sub>f</sub>   | 11, 10       | Fall time                                                                | C <sub>L</sub> = 1 nF                                                              | -    | 35   | 70   | ns   |

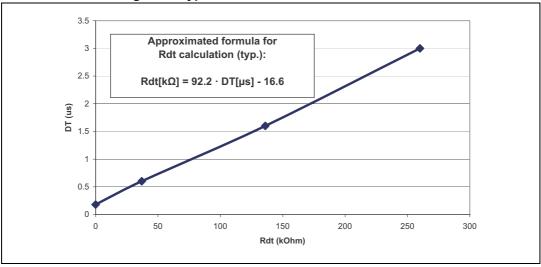

<sup>1.</sup> See Figure 3.

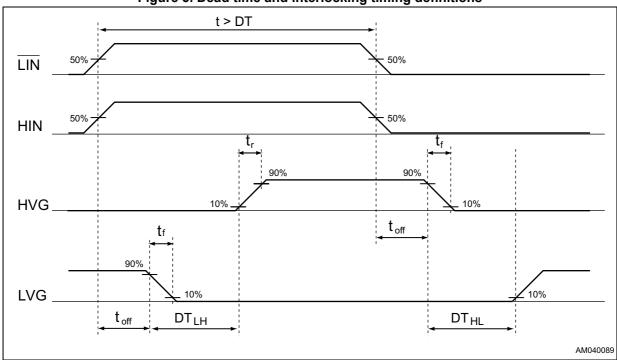

<sup>2.</sup> MDT =  $|DT_{LH} - DT_{HL}|$  see Figure 6 on page 13.

Electrical characteristics L6390

Figure 3. Typical deadtime vs. DT resistor value

# 4.2 DC operation

Table 6. DC operation electrical characteristics ( $V_{CC}$  = 15 V;  $T_J$  = + 25 °C)

| Symbol                     | Pin       | Parameter                                         | Test condition                                                                                                                                                                                                                                                        | Min. | Тур. | Max. | Unit |  |  |

|----------------------------|-----------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|--|

| Low supply voltage section |           |                                                   |                                                                                                                                                                                                                                                                       |      |      |      |      |  |  |

| V <sub>CC_hys</sub>        |           | V <sub>CC</sub> UV hysteresis                     | -                                                                                                                                                                                                                                                                     | 1200 | 1500 | 1800 | mV   |  |  |

| V <sub>CC_thON</sub>       |           | V <sub>CC</sub> UV turn-ON threshold              | -                                                                                                                                                                                                                                                                     | 11.5 | 12   | 12.5 | V    |  |  |

| V <sub>CC_thOFF</sub>      |           | V <sub>CC</sub> UV turn-OFF threshold             | -                                                                                                                                                                                                                                                                     | 10   | 10.5 | 11   | V    |  |  |

| I <sub>QCCU</sub>          | 4         | Undervoltage quiescent supply current             | $\begin{aligned} & V_{CC} = 10 \text{ V} \\ & \overline{\text{SD}} = 5 \text{ V}; \overline{\text{LIN}} = 5 \text{ V}; \\ & \text{HIN} = \text{GND}; \\ & R_{DT} = 0  \Omega; \\ & \text{CP+} = \text{OP+} = \text{GND}; \\ & \text{OP-} = 5 \text{ V} \end{aligned}$ | 90   | 120  | 150  | μА   |  |  |

| I <sub>QCC</sub>           |           | Quiescent current                                 | $\begin{aligned} & \underbrace{V_{CC}} = 15 \text{ V} \\ & \widehat{SD} = 5 \text{ V}; \widehat{LIN} = 5 \text{ V}; \\ & \text{HIN = GND;} \\ & R_{DT} = 0  \Omega; \\ & \text{CP+ = OP+ = GND;} \\ & \text{OP- = 5 V} \end{aligned}$                                 | 300  | 720  | 1000 | μА   |  |  |

| V <sub>ref</sub>           | -         | Internal reference voltage                        | -                                                                                                                                                                                                                                                                     | 500  | 540  | 580  | mV   |  |  |

| Bootstrapp                 | ed supply | voltage section <sup>(1)</sup>                    |                                                                                                                                                                                                                                                                       |      |      |      |      |  |  |

| V <sub>BO_hys</sub>        |           | V <sub>BO</sub> UV hysteresis                     | -                                                                                                                                                                                                                                                                     | 1200 | 1500 | 1800 | mV   |  |  |

| V <sub>BO_thON</sub>       |           | V <sub>BO</sub> UV turn-ON threshold              | -                                                                                                                                                                                                                                                                     | 11.1 | 11.5 | 12.1 | V    |  |  |

| V <sub>BO_thOFF</sub>      |           | V <sub>BO</sub> UV turn-OFF threshold             | -                                                                                                                                                                                                                                                                     | 9.8  | 10   | 10.6 | V    |  |  |

| I <sub>QBOU</sub>          | 16        | Undervoltage V <sub>BO</sub> quiescent current    | $V_{BO}$ = 9 V<br>$\overline{SD}$ = 5 V; $\overline{LIN}$ and<br>HIN = 5 V;<br>$R_{DT}$ = 0 $\Omega$ ;<br>CP+ = $OP+$ = $GND$ ;<br>OP- = 5 V                                                                                                                          | 30   | 70   | 110  | μА   |  |  |

| I <sub>QBO</sub>           |           | V <sub>BO</sub> quiescent current                 | $V_{BO}$ = 15 V<br>$\overline{SD}$ = 5 V; $\overline{LIN}$ and<br>HIN = 5 V;<br>$R_{DT}$ = 0 $\Omega$ ;<br>CP+ = $OP+$ = $GND$ ;<br>OP- = 5 V                                                                                                                         | 30   | 150  | 240  | μА   |  |  |

| I <sub>LK</sub>            | -         | High voltage leakage current                      | V <sub>hvg</sub> = V <sub>OUT</sub> = V <sub>BOOT</sub> = 600 V                                                                                                                                                                                                       | ı    | -    | 10   | μА   |  |  |

| R <sub>DS(on)</sub>        | -         | Bootstrap driver on-<br>resistance <sup>(2)</sup> | LVG ON                                                                                                                                                                                                                                                                | -    | 120  | -    | Ω    |  |  |

Electrical characteristics L6390

Table 6. DC operation electrical characteristics ( $V_{CC}$  = 15 V;  $T_{J}$  = + 25 °C) (continued)

| Symbol             | Pin                     | Parameter                                      | Test condition                              | Min. | Тур. | Max. | Unit |  |  |  |

|--------------------|-------------------------|------------------------------------------------|---------------------------------------------|------|------|------|------|--|--|--|

| Driving buf        | Driving buffers section |                                                |                                             |      |      |      |      |  |  |  |

| I <sub>so</sub>    | - 11, 15                | High/low-side source short-<br>circuit current | $V_{IN} = V_{ih} (t_p < 10 \ \mu s)$        | 200  | 290  | -    | mA   |  |  |  |

| I <sub>si</sub>    | 11, 15                  | High/low-side sink short-<br>circuit current   | $V_{IN} = V_{il} (t_p < 10 \ \mu s)$        | 250  | 430  | -    | mA   |  |  |  |

| Logic input        | ts                      |                                                |                                             |      |      |      |      |  |  |  |

| V <sub>il</sub>    | 1, 2, 3                 | Low level logic threshold voltage              | -                                           | 0.8  | -    | 1.1  | V    |  |  |  |

| $V_{ih}$           | 1, 2, 3                 | High level logic threshold voltage             | -                                           | 1.9  | -    | 2.25 | V    |  |  |  |

| V <sub>il_S</sub>  | 1, 3                    | Single input voltage                           | LIN and HIN connected together and floating | -    | -    | 0.8  | V    |  |  |  |

| I <sub>HINh</sub>  | 3                       | HIN logic "1" input bias current               | HIN = 15 V                                  | 110  | 175  | 260  | μА   |  |  |  |

| I <sub>HINI</sub>  |                         | HIN logic "0" input bias current               | HIN = 0 V                                   | -    | -    | 1    | μА   |  |  |  |

| I <sub>LINI</sub>  | 1                       | LIN logic "0" input bias current               | LIN = 0 V                                   | 3    | 6    | 20   | μА   |  |  |  |

| I <sub>LINh</sub>  |                         | LIN logic "1" input bias current               | LIN = 15 V                                  | -    | -    | 1    | μА   |  |  |  |

| I <sub>SDh</sub>   | - 2                     | SD logic "1" input bias current                | <del>SD</del> = 15 V                        | 10   | 40   | 100  | μА   |  |  |  |

| I <sub>SDI</sub>   | 1 4                     | SD logic "0" input bias current                | SD = 0 V                                    | -    | -    | 1    | μА   |  |  |  |

| R <sub>PD_SD</sub> | 2                       | SD input pull-down resistor                    | SD = 15 V                                   | 150  | 375  | 1500 | kΩ   |  |  |  |

<sup>1.</sup>  $V_{BO} = V_{BOOT} - V_{OUT}$

<sup>2.</sup>  $R_{DSON}$  is tested in the following way:  $R_{DSON}$  = [( $V_{CC}$  -  $V_{BOOT1}$ ) - ( $V_{CC}$  -  $V_{BOOT2}$ )] / [ $I_1(V_{CC},V_{BOOT1})$  -  $I_2(V_{CC},V_{BOOT2})$ ] where  $I_1$  is the pin 16 current when  $V_{BOOT}$  =  $V_{BOOT1}$ ,  $I_2$  when  $V_{BOOT}$  =  $V_{BOOT2}$ .

Table 7. Op amp characteristics<sup>(1)</sup> ( $V_{CC}$  = 15 V,  $T_{J}$  = +25 °C)

| Symbol             | Pin  | Parameter                         | Test condition                                                | Min. | Тур. | Max.               | Unit |

|--------------------|------|-----------------------------------|---------------------------------------------------------------|------|------|--------------------|------|

| V <sub>io</sub>    |      | Input offset voltage              | $V_{ic} = 0 \text{ V}, V_{o} = 7.5 \text{ V}$                 | -    | -    | 6                  | mV   |

| l <sub>io</sub>    |      | Input offset current              | V <sub>ic</sub> = 0 V, V <sub>o</sub> = 7.5 V                 | -    | 4    | 40                 | nA   |

| I <sub>ib</sub>    | 6, 9 | Input bias current <sup>(2)</sup> | v <sub>ic</sub> - 0 v, v <sub>o</sub> - 7.5 v                 | -    | 100  | 200                | nA   |

| V <sub>icm</sub>   |      | Input common mode voltage range   | -                                                             | 0    | -    | V <sub>CC</sub> -4 | V    |

| V <sub>OPOUT</sub> |      | Output voltage swing              | OPOUT = OP-; no load                                          | 0.07 | -    | V <sub>CC</sub> -4 | V    |

|                    | 7    | Output short-circuit current      | Source, $V_{id} = +1$ ; $V_o = 0 \text{ V}$                   | 16   | 30   | -                  | mA   |

| I <sub>o</sub>     |      | Output short-circuit current      | Sink, $V_{id} = -1$ ; $V_o = V_{CC}$                          | 50   | 80   | -                  | mA   |

| SR                 | -    | Slew rate                         | $V_i = 1 \div 4 \text{ V; } C_L = 100 \text{ pF;}$ unity gain | 2.5  | 3.8  | -                  | V/μs |

| GBWP               | -    | Gain bandwidth product            | V <sub>o</sub> = 7.5 V                                        | 8    | 12   | -                  | MHz  |

| A <sub>vd</sub>    | -    | Large signal voltage gain         | $R_L = 2 k\Omega$                                             | 70   | 85   | -                  | dB   |

| SVR                | -    | Supply voltage rejection ratio    | vs. V <sub>CC</sub>                                           | 60   | 75   | -                  | dB   |

| CMRR               | -    | Common mode rejection ratio       | -                                                             | 55   | 70   | -                  | dB   |

<sup>1.</sup> The operational amplifier is disabled when  $V_{\mbox{\footnotesize CC}}$  is in UVLO condition.

Table 8. Sense comparator characteristics<sup>(1)</sup> ( $V_{CC}$  = 15 V,  $T_{J}$  = +25 °C)

| Symbol              | Pin | Parameter                           | Test condition                                     | Min. | Тур. | Max. | Unit |

|---------------------|-----|-------------------------------------|----------------------------------------------------|------|------|------|------|

| l <sub>ib</sub>     | 10  | Input bias current                  | V <sub>CP+</sub> = 1 V                             | -    | -    | 1    | μΑ   |

| V <sub>OL</sub>     | 2   | Open drain low level output voltage | I <sub>OD</sub> = - 3 mA                           | -    | -    | 0.5  | V    |

| R <sub>ON_OD</sub>  | 2   | Open drain ON resistor              | -                                                  | -    | 125  | 167  | Ω    |

| t <sub>d_comp</sub> | -   | Comparator delay                    | SD/OD pulled to 5 V through 100 kΩ resistor        | -    | 90   | 130  | ns   |

| SR                  | 2   | Slew rate                           | $C_L = 180 \text{ pF}; R_{pu} = 5 \text{ k}\Omega$ | -    | 60   | -    | V/μs |

<sup>1.</sup> The comparator is disabled when  $\mathrm{V}_{\mathrm{CC}}$  is in UVLO condition.

<sup>2.</sup> Input bias current flows out the IC leads.

# 5 Timing and waveforms definitions

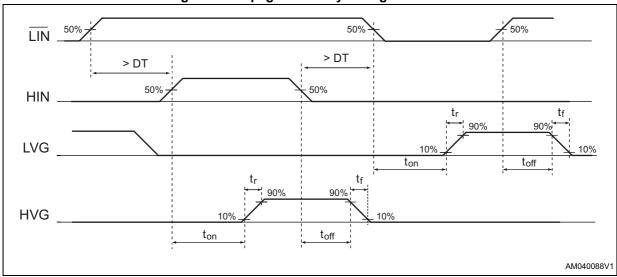

Figure 4. Propagation delay timing definition

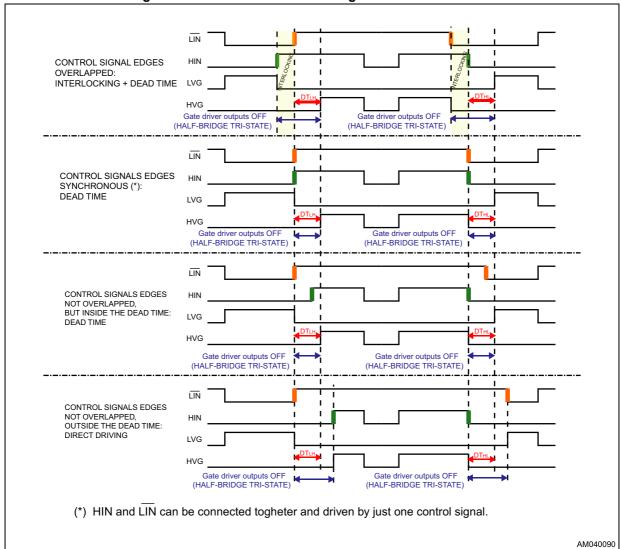

Figure 5. Dead time and interlocking timing definitions

Figure 6. Deadtime and interlocking waveforms definition

Input logic L6390

## 6 Input logic

Input logic is provided with an interlocking circuitry which avoids cross-conduction in case of wrong signals on LIN and HIN tries to turn-on both LVG and HVG outputs at the same times. In addition, to prevent cross conduction of the external MOSFETs, after each output is turned off, the other output cannot be turned on before a certain amount of time (DT) (see Figure 5: Dead time and interlocking timing definitions).

Table 9. Truth table

|    | Input            | Out              | tput |     |

|----|------------------|------------------|------|-----|

| SD | LIN              | HIN              | LVG  | HVG |

| L  | X <sup>(1)</sup> | X <sup>(1)</sup> | L    | L   |

| Н  | Н                | L                | L    | L   |

| Н  | L                | Н                | L    | L   |

| Н  | L                | L                | Н    | L   |

| Н  | Н                | Н                | L    | Н   |

<sup>1.</sup> X: don't care.

### 7 Smart shutdown function

The L6390 device integrates a comparator committed to the fault sensing function. The comparator has an internal voltage reference  $V_{ref}$  connected to the inverting input, while the non-inverting input is available on the pin 10. The comparator input can be connected to an external shunt resistor in order to implement a simple overcurrent detection function. The output signal of the comparator is fed to an integrated MOSFET with the open drain output available on the pin 2, shared with the  $\overline{SD}$  input. When the comparator triggers, the device is set in shutdown state and both its outputs are set to low level leaving the half-bridge in tristate.

Figure 7. Smart shutdown timing waveforms CP+ HIN/LIN **PROTECTION** HVG/LVG SD/OD  $au_2$ Open drain gate (internal)  $t_2$ Disable time Fast shut down: The driver outputs are set in SD state immediately after the comparator triggering even if the SD signal has not yet reach the lower input threshold. An approximation of the disable time is given by:  $t_1 \cong \tau_1 \cdot ln \left( \frac{V_{off} - V_{on}}{V_{il} - V_{on}} \right)$ SHUT-DOWN CIRCUIT  $t_2 \cong \tau_2 \cdot ln \left( \frac{V_{il} - V_{off}}{V_{ih} - V_{off}} \right)$  $R_{SD}$ where:  $\tau_1 = \left(R_{ON\_OD}//R_{SD}\right) \cdot C_{SD}$ SD/OD  $\tau_2 = \left(R_{PD\_SD}//R_{SD}\right) \cdot C_{SD}$ FROM/TO SMART

$$\begin{split} V_{on} &= \frac{R_{ON\_OD}}{R_{ON\_OD} + R_{SD}} \cdot V_{BIAS} \\ V_{off} &= \frac{R_{PD\_SD}}{R_{PD\_SD} + R_{SD}} \cdot V_{BIAS} \end{split}$$

CSD AM12947v2

In common overcurrent protection architectures the comparator output is usually connected to the SD input and an RC network is connected to this SD/OD line in order to provide a monostable circuit, which implements a protection time that follows the fault condition. Differently from the common fault detection systems, the L6390 smart shutdown architecture allows immediate turn-off of the outputs of the gate driver in the case of fault, by minimizing the propagation delay between the fault detection event and the actual output switch-off. In fact, the time delay between the fault detection and the output turn-off is no longer dependent on the value of the external RC network connected to the SD/OD pin. In the smart shutdown circuitry the fault signal has a preferential path which directly switches off the outputs after the comparator triggering. At the same time the internal logic turns on the open drain output and holds it on until the SD voltage goes below the SD logic input lower threshold. When such threshold is reached, the open drain output is turned off, allowing the external pull-up to recharge the capacitor. The driver outputs restart following the input pins as soon as the voltage at the SD/OD pin reaches the higher threshold of the SD logic input. The smart shutdown system provides the possibility to increase the time constant of the external RC network (that determines the disable time after the fault event) up to very large values without increasing the delay time of the protection.

Any external signal provided to the  $\overline{SD}$  pin is not latched and can be used as control signal in order to perform, for instance, PWM chopping through this pin. In fact when a PWM signal is applied to the  $\overline{SD}$  input and the logic inputs of the gate driver are stable, the outputs switch from the low level to the state defined by the logic inputs and vice versa.

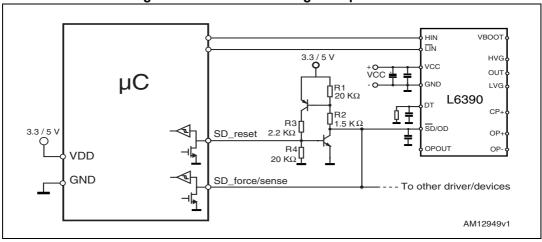

In some applications it may be useful to latch the driver in the shutdown condition for an arbitrary time, until the controller decides to reset it to normal operation. This may, for example, be achieved with a circuit similar to the one shown in *Figure 8*. When the open drain starts pulling down the  $\overline{SD}/OD$  pin, the external latch turns on and keeps the pin to GND, preventing it from being pulled up again once the  $\overline{SD}$  logic input lower threshold is reached and the internal open drain turns off. One pin of the controller is used to release the external latch, and one to externally force a shutdown condition and also to read the status of the  $\overline{SD}/OD$  pin.

Figure 8. Protection latching example circuit

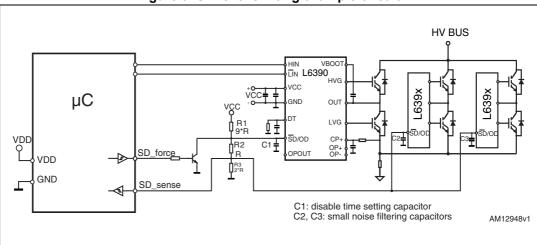

In applications using only one L6390 for the protection of several different legs (such as a single-shunt inverter, for example) it may be useful to implement the resistor divider shown in *Figure 9*. This simple network allows the pushing of the  $\overline{\text{SD}}$  pins of the other devices to a voltage lower than L6390  $V_{il}$ , so that each device can reach its low logic level regardless of part-to-part variations of the thresholds.

Figure 9. SD level shifting example circuit

# 8 Typical application diagram

PROM CONTROLLER LIN 1

FROM CONTROLLER LIN 1

Figure 10. Application diagram

L6390 Bootstrap driver

### 9 Bootstrap driver

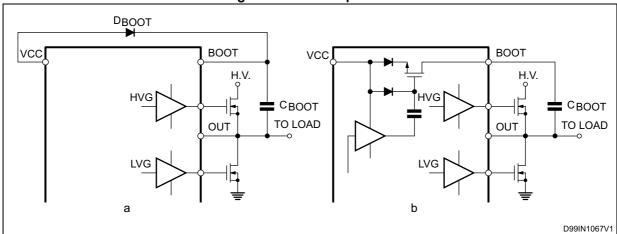

A bootstrap circuitry is needed to supply the high voltage section. This function is normally accomplished by a high voltage fast recovery diode (*Figure 11.a*). In the L6390 device a patented integrated structure replaces the external diode. It is realized by a high voltage DMOS, driven synchronously with the low-side driver (LVG), with a diode in series, as shown in *Figure 11.b*. An internal charge pump (*Figure 11.b*) provides the DMOS driving voltage.

### **C**BOOT selection and charging

To choose the proper  $C_{BOOT}$  value the external MOS can be seen as an equivalent capacitor. This capacitor  $C_{EXT}$  is related to the MOS total gate charge:

#### **Equation 1**

$$C_{EXT} = \frac{Q_{gate}}{V_{gate}}$$

The ratio between the capacitors  $C_{\text{EXT}}$  and  $C_{\text{BOOT}}$  is proportional to the cyclical voltage loss. It must be:

#### **Equation 2**

E.g.: if  $Q_{gate}$  is 30 nC and  $V_{gate}$  is 10 V,  $C_{EXT}$  is 3 nF. With  $C_{BOOT}$  = 100 nF the drop would be 300 mV.

If HVG must be supplied for a long time, the  $C_{BOOT}$  selection must also take the leakage and quiescent losses into account.

E.g.: HVG steady-state consumption is lower than 240  $\mu$ A, so if HVG T<sub>ON</sub> is 5 ms, C<sub>BOOT</sub> must supply 1.2  $\mu$ C to C<sub>EXT</sub>. This charge on a 1  $\mu$ F capacitor means a voltage drop of 1.2 V.

The internal bootstrap driver offers important advantages: the external fast recovery diode can be avoided (it usually has a high leakage current).

This structure can work only if  $V_{OUT}$  is close to GND (or lower) and, at the same time, the LVG is on. The charging time ( $T_{charge}$ ) of the  $C_{BOOT}$  is the time in which both conditions are fulfilled and it must be long enough to charge the capacitor.

The bootstrap driver introduces a voltage drop due to the DMOS  $R_{DSon}$  (typical value: 120  $\Omega$ ). This drop can be neglected at low switching frequency, but it should be taken into account when operating at high switching frequency.

Bootstrap driver L6390

The following equation is useful to compute the drop on the bootstrap DMOS:

#### **Equation 3**

$$V_{drop} = I_{charge}R_{dson} \rightarrow V_{drop} = \frac{Q_{gate}}{T_{charge}}R_{dson}$$

where  $Q_{gate}$  is the gate charge of the external power MOSFET,  $R_{dson}$  is the on-resistance of the bootstrap DMOS and  $T_{charge}$  is the charging time of the bootstrap capacitor.

For example: using a power MOSFET with a total gate charge of 30 nC, the drop on the bootstrap DMOS is about 1 V, if the  $T_{charge}$  is 5  $\mu s$ . In fact:

#### **Equation 4**

20/25

$$V_{drop} \, = \, \frac{30nC}{5\mu s} \cdot 120\Omega \sim 0.7 V$$

$V_{drop}$  should be taken into account when the voltage drop on  $C_{BOOT}$  is calculated: if this drop is too high, or the circuit topology doesn't allow a sufficient charging time, an external diode can be used.

Figure 11. Bootstrap driver

DocID14493 Rev 11

#### 10 **Package information**

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

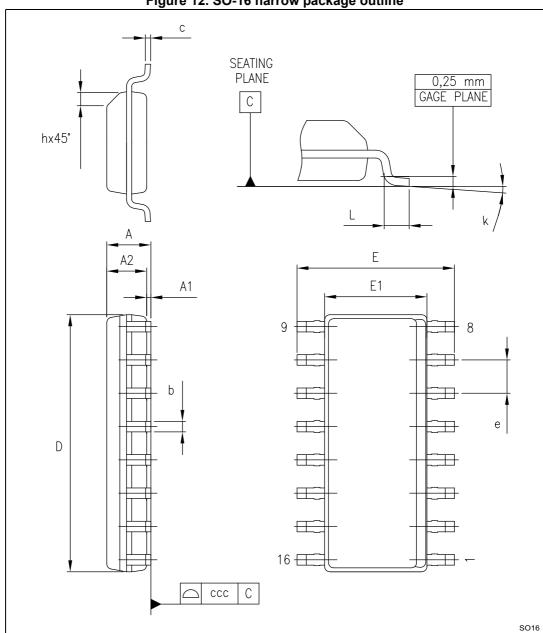

#### SO-16 package information 10.1

Figure 12. SO-16 narrow package outline

Package information L6390

Table 10. SO-16 narrow package mechanical data

| Current al |      | Dimensions (mm) |       |

|------------|------|-----------------|-------|

| Symbol     | Min. | Тур.            | Max.  |

| Α          | -    | -               | 1.75  |

| A1         | 0.10 | -               | 0.25  |

| A2         | 1.25 | -               | -     |

| b          | 0.31 | -               | 0.51  |

| С          | 0.17 | -               | 0.25  |

| D          | 9.80 | 9.90            | 10.00 |

| Е          | 5.80 | 6.00            | 6.20  |

| E1         | 3.80 | 3.90            | 4.00  |

| е          | -    | 1.27            | -     |

| h          | 0.25 | -               | 0.50  |

| L          | 0.40 | -               | 1.27  |

| k          | 0    | -               | 8°    |

| ccc        | -    | -               | 0.10  |

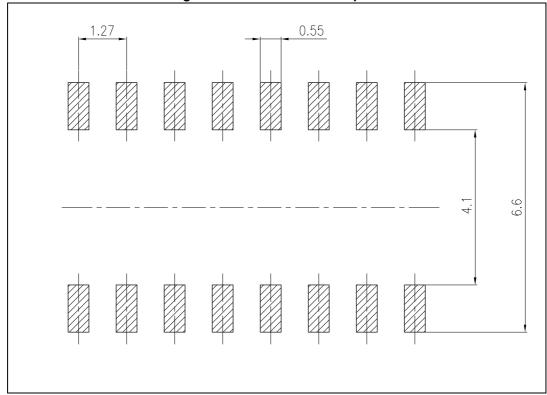

Figure 13. SO-16 narrow footprint

L6390 Order codes

# 11 Order codes

Table 11. Order codes

| Order code | Package | Packaging     |

|------------|---------|---------------|

| L6390D     | SO-16   | Tube          |

| L6390DTR   | SO-16   | Tape and reel |

Revision history L6390

# 12 Revision history

**Table 12. Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 11-Sep-2015 | 9        | Removed DIP-16 package from the whole document.  Updated <i>Table 3 on page 6</i> (added ESD parameter and value).  Updated <i>Table 4 on page 6</i> (updated R <sub>th(JA)</sub> value).  Updated note 1.and 2. below <i>Table 7 on page 10</i> (minor modifications, replaced V <sub>CBOOTx</sub> by V <sub>BOOTx</sub> ).  Minor modifications throughout document.                                                                                                                                                                                                                                |  |

| 07-Apr-2017 | 10       | Updated <i>Table 5 on page 7</i> (updated cross reference to <i>Figure 4 on page 12</i> instead of removed <i>Figure 3. Timing</i> ).  Updated <i>Table 6 on page 9</i> (added R <sub>PD_SD</sub> ) and <i>Table 8 on page 11</i> (added R <sub>ON_OD</sub> ).  Updated <i>Section 5 on page 12</i> (updated title, added <i>Figure 4</i> and <i>Figure 5</i> ).  Added <i>Section 6 on page 14</i> (and moved <i>Table 9: Truth table</i> to this section).  Updated <i>Figure 11 on page 20</i> and <i>Figure 12 on page 21</i> (replaced by new figure).  Minor modifications throughout document. |  |

| 21-Mar-2018 | 11       | Updated Figure of SO-16 package on page 1 and Figure 2: Pin connection (top view) on page 4.  Updated Table 5 on page 7 (updated DT and MDT test conditions).  Updated note 2. below Table 7 on page 11.  Updated Section 6 on page 14.  Minor modifications throughout document.                                                                                                                                                                                                                                                                                                                     |  |

### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics – All rights reserved

DocID14493 Rev 11

25/25

单击下面可查看定价,库存,交付和生命周期等信息

>>STMicroelectronics(意法半导体)