## USB charging controller with integrated power switch

Datasheet - production data

#### **Features**

- Compliant with USB charging specifications BC1.2. USB 2.0 and USB 3.0 standards

- Compliant with Chinese telecommunications industry standard YD/T 1591-2009

- Compatible with proprietary charging mode (Apple<sup>®</sup> 1 A / 2 A, BlackBerry<sup>®</sup>, Korean tablets)

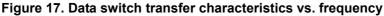

- · Wide bandwidth, low-loss USB 2.0 data switch

- Integrated  $V_{BUS}$  power switch with low  $R_{ON}$  of 65 m $\Omega$

- Constant current mode overcurrent protection

- Soft-start to limit inrush current

- Adjustable current limit up to 2.8 A

- Short-circuit, thermal and undervoltage protection

- Reverse voltage and reverse current protection

- · Deglitched fault reporting output

- Supports remote wakeup in S3

- Charging indication output in DCP and CDP modes

- Package: VFQFPN 16L 3 x 3 x 0.8 mm with exposed pad

- Temperature range: -40 up to 85 °C

- UL and CB recognized components (UL file number: E354278)

This is information on a product in full production.

## **Applications**

- USB ports / hubs

- Personal computers, all-in-one PCs

- Monitors

- Notebooks, ultrabooks

- Tablet PCs

- · Universal wall charging adapters

### **Description**

The STCC2540 device integrates, in one package, a USB charger controller, a wide bandwidth data switch, and a high current power switch. The device emulates several profiles compatible with the USB battery charging standard, BC1.2, Chinese telecommunications standard YD/T 1591-2009, and proprietary charger modes.

The device asserts the charging flag in DCP modes if the charging current is higher than the threshold. In CDP mode, it asserts the charging flag after the CDP negotiation if the charging current is higher than the threshold.

After the current drops below the threshold, the output is deasserted, allowing the host to turn off the high power DC-DC converter and reduce overall consumption in S4/S5 states, which is critical when the host is battery supplied.

www.st.com

Contents STCC2540

## **Contents**

| 1 | Fun  | ctional description                            | 3  |

|---|------|------------------------------------------------|----|

| 2 | Pin  | description                                    | 5  |

| 3 | Abs  | olute maximum ratings and operating conditions | 6  |

| 4 | Elec | ctrical characteristics                        | 7  |

| 5 | Арр  | lication information                           | 11 |

|   | 5.1  | Supported modes                                | 12 |

|   | 5.2  | Remote wakeup in S3                            | 13 |

|   | 5.3  | V <sub>BUS</sub> discharge                     |    |

|   | 5.4  | State machine                                  | 14 |

|   | 5.5  | Charging detection                             | 15 |

|   | 5.6  | Power switch                                   |    |

|   |      | Overcurrent conditions                         |    |

|   |      | Thermal protection                             | 15 |

|   |      | Undervoltage lockout                           | 15 |

|   |      | FAULT functionality                            | 16 |

|   |      | Current limit programming                      | 16 |

|   | 5.7  | Enable input                                   | 16 |

|   | 5.8  | Input and output capacitors                    | 17 |

| 6 | Турі | ical operating characteristics                 | 18 |

| 7 | Pacl | kage information                               | 28 |

| 8 | Orde | ering information                              | 30 |

| 9 | Revi | ision history                                  | 31 |

## 1 Functional description

The STCC2540 device integrates, in one package, a complete solution to charge portable devices through USB ports, including:

- Charger emulator compatible with USB battery charging BC1.2 standard, Chinese telecommunications standard YD/T 1591-2009 and proprietary charger such as Apple<sup>®</sup> divider mode, BlackBerry<sup>®</sup> and Korean tablet charging mode.

- 3 control pins, CTL1, CTL2, CTL3 allowing the host to select the emulation profile.

These pins may be controlled directly from the host USB controller or from the embedded controller.

- USB data switch with wide bandwidth up to 1100 MHz compliant with USB 2.0 standard. This wide bandwidth switch features low capacitance and low R<sub>ON</sub> resistance, allowing signals to pass with minimum edge and phase distortion.

- N-channel power switch with low  $R_{ON}$  resistance of 65 m $\Omega$  typ., high current limiter accuracy and high current output capability, 2.5 A typ. The current limit threshold can be adjusted with a good accuracy by an external resistor in the range 500 mA to 2.8 A (max.).

- Constant current mode protection is used to protect the device and the host system against overcurrent or short-circuit. Other protection includes reverse current and reverse voltage protection, undervoltage lockout and thermal shutdown.

- A deglitched output (FAULT) reporting the failure events of overcurrent, thermal shutdown and reverse current (backdrive) to V<sub>IN</sub>.

- Charging current sensing circuit. The output CHARGING is asserted if charging current is above 20 mA in CDP and DCP modes.

In CDP mode the charging flag is s asserted only if the CDP handshaking between the portable device and the host is performed before the current is above threshold. After the current drops below threshold, the output CHARGING is deasserted. The host system can then disable the high power DC-DC converter and thus reduce the power consumption. This is crucial when the host is battery supplied.

- An enable input (EN) to enable/disable the device.

The device is offered in a small, RoHS compliant VFQFPN 16L (3  $\times$  3  $\times$  0.8 mm) package with an exposed pad for effective cooling.

DocID024711 Rev 6

DP\_OUT DM\_OUT USB data Emulation DP\_IN DM\_IN switch profiles  $V_{IN}$ FAULT Thermal control CHARGING  $V_{IN}$ ILIM EN CTL1 CTL2 CTL3 UVLO Logic control  $V_{IN}$ Reverse current  $V_{IN}$ Power IN OUT switch Output . discharge **GND** AM00460V2

Figure 1. Block diagram

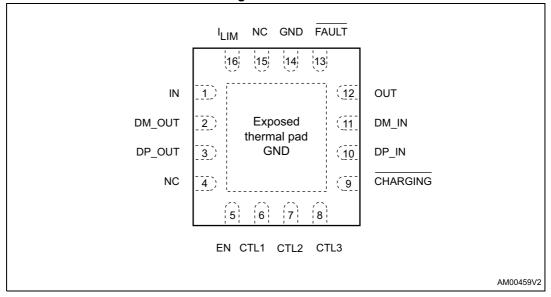

Figure 2. Pinout

STCC2540 Pin description

# 2 Pin description

Table 1. Pin description

| Pin no. | Name             | Туре | Description                                                                                               |

|---------|------------------|------|-----------------------------------------------------------------------------------------------------------|

| 1       | IN               | PWR  | Device and USB port power supply input                                                                    |

| 2, 3    | DM_OUT, DP_OUT   | I/O  | USB 2.0 data connection to system USB transmitter (DM = D-, DP = D+)                                      |

| 4       | NC               | -    | Not connected                                                                                             |

| 5       | EN               | I    | Logic level control input. When EN is low, power switch, data switch and emulator are OFF.                |

| 6, 7, 8 | CTL1, CTL2, CTL3 | ı    | Logic level control inputs to select charger mode (see <i>Table 5</i> ).                                  |

| 9       | CHARGING         | 0    | Active low open drain output, asserted when charging current is detected.                                 |

| 10, 11  | DP_IN, DM_IN     | I/O  | USB 2.0 data connection to system USB connector (DM = D-, DP = D+)                                        |

| 12      | OUT              | PWR  | USB port power supply output (V <sub>BUS</sub> )                                                          |

| 13      | FAULT            | 0    | Active low open drain output, asserted when overcurrent, overtemperature or reverse voltage are detected. |

| 14      | GND              | -    | Ground                                                                                                    |

| 15      | NC               | -    | Not connected                                                                                             |

| 16      | I <sub>LIM</sub> | I    | Current limit threshold programming resistor terminal.                                                    |

## 3 Absolute maximum ratings and operating conditions

Stressing the device beyond the rating listed in *Table 2: Absolute maximum ratings (AMR)* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated in *Table 3: Operating conditions* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute maximum ratings (AMR)

| Symbol                                                                                 | Parameter                                                                       | Value                        | Unit |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------|------|

| V <sub>IN</sub> , V <sub>OUT</sub>                                                     | Supply voltage                                                                  | -0.3 to 6.5                  |      |

| V <sub>EN</sub> , V <sub>CTLx</sub>                                                    | Logical input voltage                                                           | -0.3 to 6.5                  |      |

| V <sub>FAULT</sub> , V <sub>CHARGING</sub>                                             | Pull-up voltage (FAULT, CHARGING)                                               | -0.3 to 6.5                  | V    |

| V <sub>DP_OUT</sub> , V <sub>DM_OUT</sub> ,<br>V <sub>DP_IN</sub> , V <sub>DM_IN</sub> | Data switch pin voltage to ground                                               | -0.3 to V <sub>IN</sub> +0.3 |      |

| I <sub>DP_OUT</sub> , I <sub>DM_OUT</sub> , I <sub>DP_IN</sub> , I <sub>DM_IN</sub>    | Data switch current, switch ON                                                  | ±50                          | mA   |

| I <sub>O(OUT)</sub>                                                                    | Maximum power switch output current, power switch ON                            | Internally limited           | -    |

| I <sub>O(FAULT)</sub> , I <sub>O(CHARGING)</sub>                                       | Logical output sink current                                                     | 25                           | mA   |

| T <sub>STG</sub>                                                                       | Storage temperature (V <sub>IN</sub> OFF)                                       | -55 to +150                  |      |

| T <sub>SLD</sub>                                                                       | Lead solder temperature for 10 seconds temperature $(V_{IN}  \text{OFF})^{(1)}$ | 260                          | °C   |

| R <sub>thja</sub>                                                                      | Thermal resistance junction-to-ambient VFQFPN 16L <sup>(2)</sup>                | 60                           | °C/W |

| T <sub>j</sub>                                                                         | Maximum junction temperature (internally limited)                               | -40 to T <sub>STOP</sub>     | °C   |

| V <sub>ESD(OUT, DP_IN, DM_IN)</sub>                                                    | IEC61000-4-2 contact discharge<br>(OUT, DP_IN, DM_IN pins)                      | 8                            | kV   |

| V                                                                                      | JEDEC human body model (all pins) <sup>(3)</sup>                                | 2                            |      |

| V <sub>ESD</sub>                                                                       | JEDEC machine model (all pins)                                                  | 200                          | V    |

Reflow at temperature of 255 to 260 °C for time < 30 seconds (total thermal budget not to exceed 180 °C for a period from 90 to 150 seconds).

**Table 3. Operating conditions**

| Symbol          | Parameter                      | Value       | Unit |

|-----------------|--------------------------------|-------------|------|

| V <sub>IN</sub> | Supply voltage                 | 4.5 to 5.5  | V    |

| T <sub>A</sub>  | Ambient operating temperature  | -40 to +85  | °C   |

| T <sub>J</sub>  | Junction operating temperature | -40 to +125 |      |

6/32 DocID024711 Rev 6

<sup>2.</sup>  $R_{th}$  are typical values, given when mounted on a 4-layer PCB with vias.

Measured in recommended application circuit with 1 μF ceramic capacitor + 150 μF low ESR electrolytic capacitor connected between OUT and GND pins (see Figure 4: Typical application diagram).

## 4 Electrical characteristics

Table 4. Electrical characteristics  $V_{\rm IN}$  = 4.5 to 5.5 V, -40 °C <  $T_{\rm J}$  < 125 °C (unless otherwise specified)

| Symbol                     | Parameter                                                                  | Conditions                                                                                       | Min. | Тур.       | Max.       | Unit |

|----------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------|------------|------------|------|

| Current consumption        | 1                                                                          |                                                                                                  |      |            |            |      |

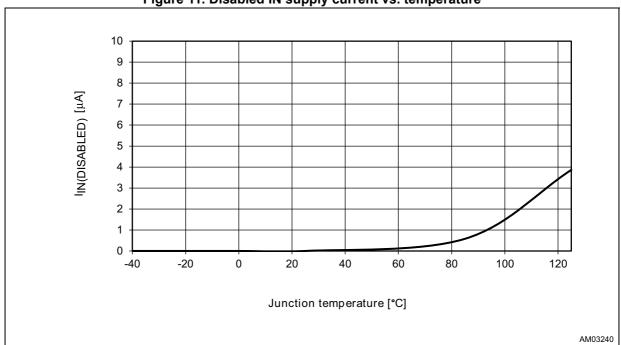

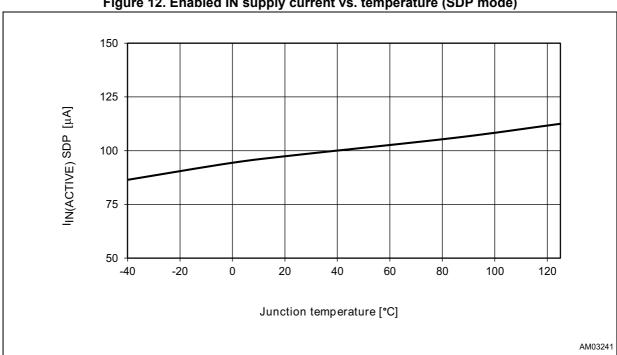

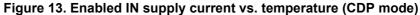

|                            |                                                                            | Mode CDP (111)                                                                                   |      | 110        | 160        |      |

|                            |                                                                            | Mode SDP (110 - 010)                                                                             |      | 100        | 150        |      |

| I <sub>ACTIVE</sub>        | Supply current in active state (EN = 1)                                    | Mode DCP auto-detect (001)  – Divider mode  – BC1.2                                              |      | 260<br>110 | 290<br>180 | μA   |

|                            |                                                                            | Mode DCP BC1.2 (100)                                                                             |      | 110        | 180        | ·    |

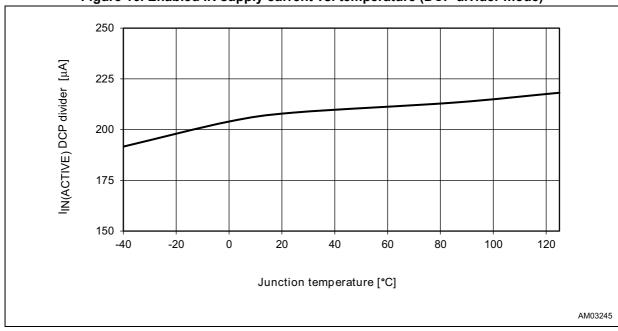

|                            |                                                                            | Mode DCP divider (101)                                                                           |      | 210        | 290        |      |

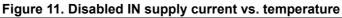

| I                          | Supply current in disable                                                  | EN = 0, T <sub>J</sub> = 25 °C                                                                   |      | 0.2        | 5          |      |

| I <sub>DISABLED</sub>      | state                                                                      | T <sub>J</sub> = 125 °C                                                                          |      |            | 60         |      |

| Power switch - DC pa       | rameters                                                                   |                                                                                                  |      |            |            |      |

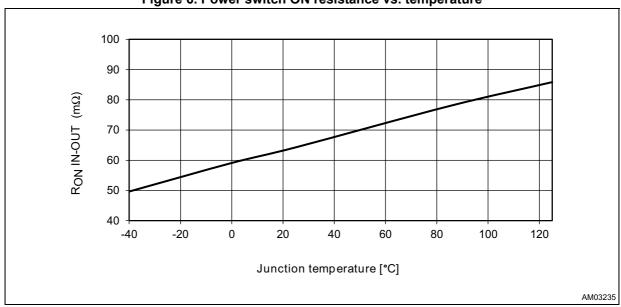

| 0                          | Static on-resistance                                                       | T <sub>J</sub> = 25 °C                                                                           |      | 65         |            | 0    |

| R <sub>ON</sub>            |                                                                            | -40 °C < T <sub>J</sub> < 125 °C                                                                 |      |            | 95         | mΩ   |

| I <sub>REVERSE</sub>       | Reverse leakage current in disabled state (absolute value)                 | $V_{OUT}$ = 5.5 V,<br>$V_{IN}$ = 0, $V_{EN}$ = 0, $T_{J}$ = 25 °C,<br>measured at IN             |      | 1          | 5          | μA   |

| ,                          |                                                                            | T <sub>J</sub> = 125 °C, other conditions the same as above                                      |      |            | 70         |      |

| V <sub>REVERSE</sub>       | Reverse voltage protection threshold (V <sub>OUT</sub> - V <sub>IN</sub> ) | V <sub>UVLO &lt;</sub> V <sub>IN &lt;</sub> V <sub>OUT</sub> , EN = 1,<br>power switch ON -> OFF |      | 60         |            | mV   |

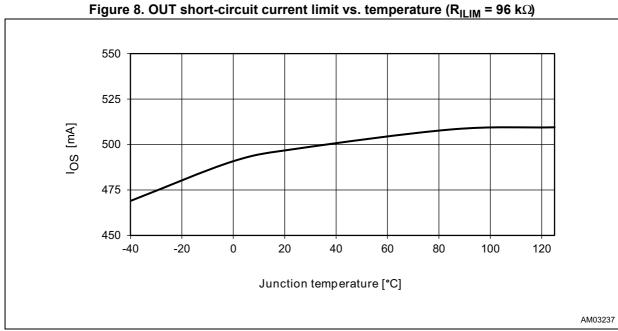

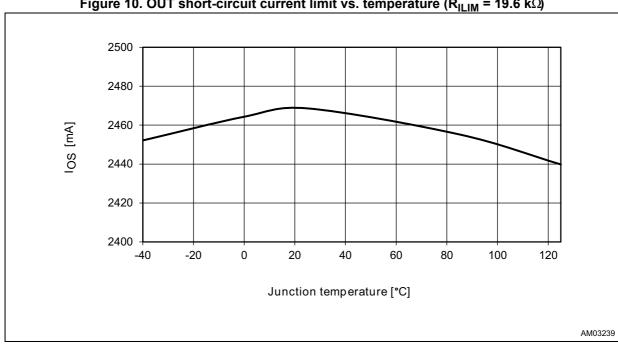

|                            |                                                                            | $R_{ILIM}$ = 96 k $\Omega$                                                                       | 340  | 500        | 625        |      |

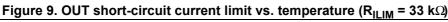

| l <sub>os</sub>            | Current limiter threshold                                                  | $R_{ILIM}$ = 33 k $\Omega$                                                                       | 1290 | 1450       | 1595       | mA   |

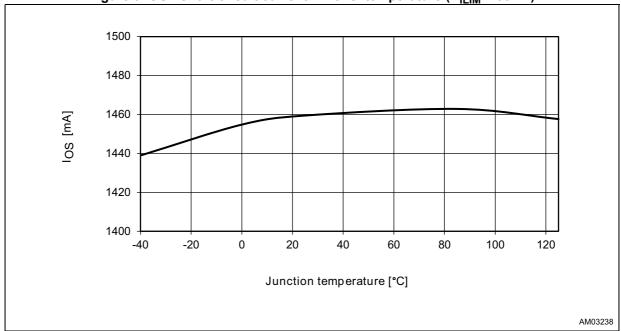

| OS                         | our ent in met un esticia                                                  | $R_{ILIM}$ = 19.6 k $\Omega$                                                                     | 2255 | 2450       | 2645       | ША   |

|                            |                                                                            | $R_{ILIM}$ = 17.2 k $\Omega$                                                                     |      | 2800       |            |      |

| $T_{STOP}$                 | Thermal shutdown threshold                                                 |                                                                                                  | 140  | 150        | 160        |      |

| T <sub>HYST</sub>          | Thermal shutdown hysteresis                                                |                                                                                                  |      | 20         |            | °C   |

| <sub>I</sub> EN            | EN input leakage current                                                   | V <sub>IN</sub> = 5.5 V, V <sub>EN</sub> = 0 V or 5 V                                            | -1   |            | 1          | μA   |

| VEN                        | Enable input turn-on, turn-off threshold voltage                           |                                                                                                  | 0.4  |            | 1.6        | V    |

| VHYST(EN)                  | Enable input turn-on, turn-off voltage hysteresis                          |                                                                                                  |      | 500        |            | mV   |

| $V_{OL(\overline{FAULT})}$ | FAULT output low voltage                                                   | I <sub>FAULT</sub> = 1 mA                                                                        |      |            | 180        |      |

Electrical characteristics STCC2540

Table 4. Electrical characteristics  $V_{IN}$  = 4.5 to 5.5 V, -40 °C <  $T_{J}$  < 125 °C (unless otherwise specified) (continued)

| Symbol                  | Parameter                                                                                | Conditions                                                                                                | Min. | Тур. | Max. | Unit |  |

|-------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|------|------|------|--|

| IOL(FAULT)              | FAULT output leakage current                                                             | V <sub>IN</sub> = 5.5 V, V <sub>FAULT</sub> = 5 V                                                         |      |      | 1    | μΑ   |  |

| t <sub>FAULT</sub>      | FAULT output deglitch delay FAULT assertion / deassertion delay in overcurrent condition |                                                                                                           | 7    | 9    | 12   | ms   |  |

| V <sub>UVLO</sub>       | Undervoltage lockout                                                                     | V <sub>IN</sub> rising                                                                                    | 3.9  | 4.1  | 4.3  | V    |  |

| V <sub>HYST(UVLO)</sub> | Undervoltage lockout hysteresis                                                          | T <sub>J</sub> = 25 °C                                                                                    |      | 100  |      | mV   |  |

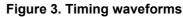

| Power switch - AC p     | parameters <sup>(1)</sup>                                                                | ,                                                                                                         | u .  | ı    |      |      |  |

| t <sub>ON</sub>         | Turn on, EN to OUT delay                                                                 |                                                                                                           |      | 0.8  |      |      |  |

| t <sub>OFF</sub>        | Turn off, EN to OUT delay                                                                | $C_{LOAD} = 1 \mu F, R_{LOAD} = 100 \Omega$                                                               |      | 0.3  |      |      |  |

| t <sub>R</sub>          | OUT (V <sub>BUS</sub> ) rise time                                                        | 0 4 5 5 400 0                                                                                             |      | 0.4  |      | ms   |  |

| t <sub>F</sub>          | OUT (V <sub>BUS</sub> ) fall time                                                        | $C_{LOAD} = 1 \mu F, R_{LOAD} = 100 \Omega$                                                               |      | 0.2  |      |      |  |

| t <sub>IOS</sub>        | Current limiter response time to short-circuit                                           | V <sub>IN</sub> = 5.5 V                                                                                   |      | 3.5  |      | μs   |  |

| Output discharge        | •                                                                                        |                                                                                                           | •    |      |      |      |  |

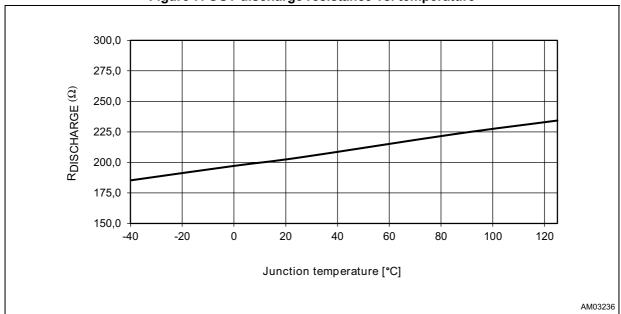

| R <sub>DISCHARGE</sub>  | Discharge resistor                                                                       |                                                                                                           | 140  | 200  | 300  | Ω    |  |

| High-speed data sw      | itch - DC parameters                                                                     |                                                                                                           |      |      |      |      |  |

| R <sub>ON</sub>         | Data switch on-resistance                                                                | Switch closed, V <sub>IN</sub> = 5 V,<br>I <sub>S</sub> = 8 mA, test voltage on<br>DP_OUT, DM_OUT = 0.4 V |      | 2.5  | 4    | _    |  |

| R <sub>ON</sub>         | Data switch on-resistance                                                                | Switch closed, V <sub>IN</sub> = 5 V,<br>I <sub>S</sub> = 8 mA, test voltage on<br>DP_OUT, DM_OUT = 3 V   |      | 2.7  | 4    | Ω    |  |

| I <sub>OFF</sub>        | OFF state leakage current                                                                | V <sub>EN</sub> = 0 V, VDP/DM_IN = 3.6 V,<br>VDP/DM_OUT = 0 V, measure<br>IDP/DM_OUT                      |      |      | 1.5  | μA   |  |

| High-speed data sw      | itch - AC parameters <sup>(1)</sup>                                                      |                                                                                                           |      | I    |      |      |  |

| X <sub>TALK</sub>       | DP, DM crosstalk                                                                         | $R_{TERM}$ = 50 $\Omega$ , $C_{LOAD}$ = 5 pF,<br>$V_S$ = 1 $V_{rms,}$ signal = 0 dBm,<br>f = 250 MHz      |      | 47   |      |      |  |

| O <sub>IRR</sub>        | OFF state isolation                                                                      | $R_{TERM}$ = 50 $\Omega$ , $C_{LOAD}$ = 5 pF,<br>$V_S$ = 1 $V_{rms}$ , signal = 0 dBm,<br>f = 250 MHz     |      | 17   |      | dB   |  |

| B <sub>w</sub>          | Bandwidth -3 dB                                                                          | $R_{TERM}$ = 50 $\Omega$ , $C_{LOAD}$ = 5 pF, signal = 0 dBm                                              |      | 1100 |      | MHz  |  |

| Charger emulator - I    | BC1.2 DCP mode                                                                           | •                                                                                                         | •    | •    |      |      |  |

| R <sub>DCP_RES</sub>    | DP_IN to DM_IN short resistance                                                          | CTLx configured for DCP<br>BC1.2                                                                          |      | 100  | 170  | Ω    |  |

8/32 DocID024711 Rev 6

Table 4. Electrical characteristics  $V_{IN}$  = 4.5 to 5.5 V, -40 °C <  $T_{J}$  < 125 °C (unless otherwise specified) (continued)

| Symbol                    | Symbol Parameter Conditions                                          |                                                                                                |      | Тур. | Max. | Unit |

|---------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|------|

| Charger emulator - d      |                                                                      | Conditions                                                                                     | Min. | .76. | ax.  | Sint |

| marger emulator - 0       | iiviuei iiioue                                                       |                                                                                                | •    | ı    | 1    |      |

| $V_{DM}$                  | DM_IN output voltage                                                 | Device set to DCP auto-detect                                                                  | 1.96 | 2    | 2.04 | V    |

| V <sub>DP</sub>           | DP_IN output voltage                                                 | mode or divider mode,<br>V <sub>IN</sub> = 5.0 V                                               | 2.65 | 2.7  | 2.75 | V    |

| $R_{DM}$                  | DM_IN output resistance                                              | Device set to DCP auto-detect                                                                  |      | 27   |      | kΩ   |

| $R_{DP}$                  | DP_IN output resistance                                              | mode of divider mode                                                                           |      | 27   |      | K22  |

| Charger emulator - E      | 3C1.2 CDP mode                                                       |                                                                                                |      | •    |      |      |

| V <sub>DM_SRC</sub>       | Voltage source on DM_IN for CDP detection                            | V <sub>DP_IN</sub> = 0.6 V, device in CDP<br>BC1.2 mode                                        | 0.5  | 0.6  | 0.7  |      |

| V <sub>DAT_REF</sub>      | DP_IN rising voltage threshold to turn on VDM_SRC                    |                                                                                                | 0.25 | 0.32 | 0.4  | V    |

| V <sub>DAT_REF_HYST</sub> | V <sub>DAT_REF</sub> hysteresis                                      | I <sub>DM IN</sub> = -250 μA, device in                                                        |      | 30   |      | mV   |

| $V_{LGC\_SRC}$            | DP_IN rising voltage<br>threshold to turn off<br>V <sub>DM_SRC</sub> | CDP BC1.2 mode                                                                                 | 0.8  |      | 1    | ٧    |

| V <sub>LGC_SRC_HYST</sub> | V <sub>LGC_SRC</sub> hysteresis                                      |                                                                                                |      | 30   |      | mV   |

| I <sub>DP_SINK</sub>      | DP_IN sink current                                                   | 0.4 < V <sub>DP_IN</sub> < 0.8 V, device in CDP BC1.2 mode                                     | 50   | 75   | 150  | μA   |

| Charger emulator - ti     | mings                                                                |                                                                                                |      |      |      |      |

| tchg_dgl_on               | Charging indication ON deglitch delay                                | From I <sub>OUT</sub> > I <sub>OUT</sub> _TH to CHARGING asserted                              |      | 0.5  |      |      |

| t <sub>CHG_DGL_OFF</sub>  | Charging indication OFF deglitch delay                               | From I <sub>OUT</sub> < I <sub>OUT_TH</sub> to CHARGING deasserted                             |      | 5    |      | S    |

| t <sub>VDM_</sub> SRC_ON  | DM_IN voltage source turn-<br>on time                                | From $V_{DP\_IN}$ 0 V -> 0.6 V to $V_{DM\_IN}$ = $V_{DM\_SRC}$ , CTLx configured for CDP BC1.2 |      | 8    |      |      |

| t <sub>VDM_SRC_OFF</sub>  | DM_IN voltage source turn-<br>off time                               | From $V_{DP\_IN}$ 0.6 V -> 0 V to $V_{DM\_IN} = \overline{0}$ V, CTLx configured for CDP BC1.2 |      |      | ms   |      |

| t <sub>VBUS_REAPP</sub>   | OUT discharge pulse width                                            | From V <sub>OUT</sub> falls to 0.7 V during                                                    |      | 350  | 400  |      |

DocID024711 Rev 6

Electrical characteristics STCC2540

Table 4. Electrical characteristics  $V_{IN}$  = 4.5 to 5.5 V, -40 °C <  $T_{J}$  < 125 °C (unless otherwise specified) (continued)

|                           | <u> </u>                                        |                                                                                           | T    | I _  | l    |      |

|---------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| Symbol                    | Parameter                                       | Conditions                                                                                | Min. | Тур. | Max. | Unit |

| Charger emulator - co     | ontrol pins CTLx                                |                                                                                           |      |      |      |      |

| V <sub>CTLx</sub>         | CTLx pins threshold voltage                     |                                                                                           | 0.4  |      | 1.6  | ٧    |

| V <sub>HYST(CTLx)</sub>   | Hysteresis voltage on CTLx pins                 |                                                                                           |      | 500  |      | mV   |

| I <sub>CTLx</sub>         | Leakage current                                 | V <sub>IN</sub> = 5.5 V, V <sub>CTLx</sub> = 0 V or 5 V                                   | -1   |      | 1    | μΑ   |

| Charger emulator - cl     | narging indication                              |                                                                                           |      |      |      |      |

| I <sub>OUT_TH</sub>       | Output current threshold for charging detection | DCP mode, CDP mode                                                                        |      | 20   |      | mA   |

| V <sub>OL(CHARGING)</sub> | CHARGING output low voltage                     | Charging detected (I <sub>OUT</sub> > I <sub>OUT_TH</sub> ), I <sub>CHARGING</sub> = 1 mA |      |      | 180  | mV   |

| I <sub>OL(CHARGING)</sub> | CHARGING output leakage current                 | V <sub>IN</sub> = 5.5 V, V <sub>CHARGING</sub> = 5 V                                      |      |      | 1    | μΑ   |

<sup>1.</sup> Guaranteed by design. Not tested in production.

## 5 Application information

The STCC2540 device is designed to be implemented into the PC on a USB port in order to emulate the wall charger adapter when the PC is in standby mode or OFF, and to allow higher charge current when the USB interface is used for data communication. In order to handle these functionalities, the STCC2540 device relies on USB BC1.2 specifications, Chinese telecommunications industry standard YD/T 1591-2009, and proprietary implementations.

- BC1.2 charging profiles are

- CDP: charging downstream port providing data communication plus charging (active USB data communications with 1.5 A support)

- SDP: standard downstream port providing data communication with no charging (active USB 3.0 data communications with 900 mA support or USB 2.0 data communications with 500 mA support)

- DCP: dedicated charging port (wall charger emulation with no data communication and 500 mA to 1.5 A support)

- · Chinese telecommunications standard

- D+ and D- shorted to allow charging

- Apple divider mode (2 A max. current)

- BlackBerry emulator mode

- Legacy mode (allowing 500 mA charging current)

- Korean tablet charging mode (D+ and D- shorted and pulled up to a certain voltage)

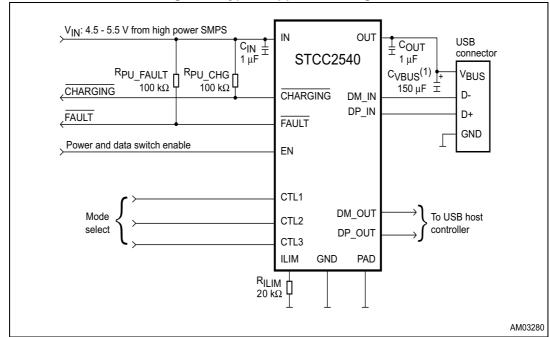

Figure 4. Typical application diagram

1.  $C_{VBUS}$  required by the USB specification.

DocID024711 Rev 6

### 5.1 Supported modes

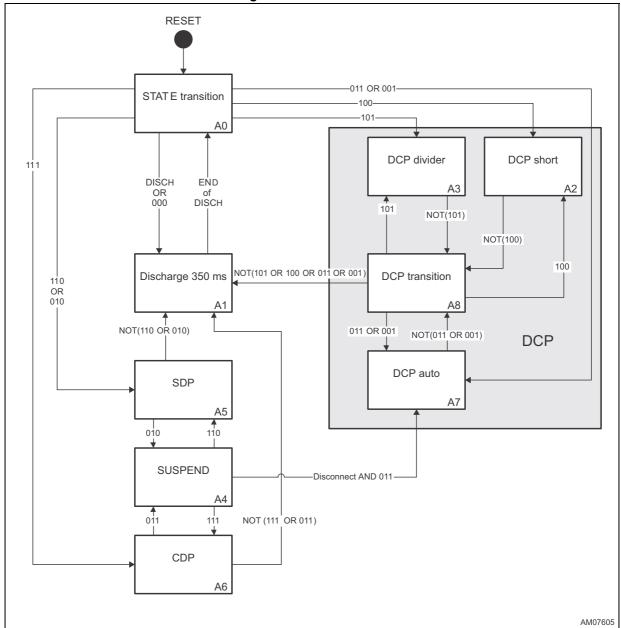

For more information refer to Section 5.4: State machine.

The STCC2540 device supports the following modes:

- SDP BC1.2

- CDP BC1.2

- SDP with remote wakeup for all USB devices

- CDP with remote wakeup for low-speed USB devices with automatic transition to DCP auto mode if a full-speed/high-speed USB device attached or after a USB device detached.

- DCP auto-detect: this mode permits auto-detection of charging modes between DCP BC1.2 (shorted D+, D-) and divider charging mode. It also supports BlackBerry charging mode and can charge legacy devices and Korean tablets.

- Forced DCP BC1.2 mode

- Forced DCP divider mode

The auto-detect mode starts in divider mode. If charging negotiation attempt is detected, there is an automatic transition to DCP BC1.2 mode. It is preceded by  $V_{BUS}$  discharge pulse to initialize the proper BC1.2 handshake process. If the BC1.2 device is detached, the circuit automatically returns to divider mode after a 10 s (typ.) timeout.

Note:

From an application point of view it means that after removing one device the user should wait for approx. 15 s before attaching another device.

Selection between these modes is done through the CTLx control pins. The CTLx pins may be controlled by the host in different ways:

- GPIO from embedded controller

- Hardware signals from USB host controller (SLP\_S3#, SLP\_S4#) and AC\_adapter signal from embedded controller

- Hardware signals SUSPEND from embedded controller and AC\_ADAPTER.

CTL2 Host state CTL1 CTL3 Mode description 0 Device off, output discharge 0 0 S0, S1, (S3)<sup>(2)</sup> 1 1 0 SDP S0, S1, (S3)<sup>(2)</sup> 1 1 1 CDP BC1.2 with charging detection. S3, (S0, S1)<sup>(2)</sup> 0 1 0 SDP with remote wakeup for all USB devices CDP with remote wakeup for low-speed USB devices / DCP auto mode for S3 0 1 1 full-speed or high-speed USB devices or after a USB device detached. S4, S5 0 0 1 DCP auto-detect mode without remote wakeup, with charging detection S4, S5 1 0 1 Forced DCP divider mode with charging detection Forced DCP BC1.2 mode with charging detection S4, S5

Table 5. Truth table control pins CTLx<sup>(1)</sup>

2. See Section 5.2 for further information.

<sup>1.</sup> On the transition from the CTLx = 111 to CTLx = 001, a synchronous transition of the CTL1 and CTL2 must be ensured.

## 5.2 Remote wakeup in S3

For more information refer to Section 5.4: State machine.

If the CTLx pins are controlled by hardware signals (such as SLP\_Sx# or SUSPEND), the CTLx combination changes when host transitions from S0 to S3 and back. In this case, the STCC2540 device can support remote wakeup of portable devices for the following transitions (i.e. no  $V_{BUS}$  discharge pulse and data switch ON):

- SDP S0 (CTLx = 110) to and from SDP S3 (CTLx = 010) for all USB devices

- SDP (CTLx = x10) and CDP S0 (CTLx = 111) to and from CDP S3 (CLx = 011) for low-speed USB devices only.

If the host system is in S3 mode (CTLx = 011), the system automatically turns into DCP auto mode for already attached full-speed / high-speed USB devices or after any USB device is detached. Thus, already attached full-speed / high-speed devices or newly attached devices are charged without the need of CTLx transition.

If the S0 to S3 transition is managed by GPIO from the embedded controller, the easiest solution is to keep the same levels on the CTLx pins (SDP or CDP modes). Therefore, remote wakeup in S3 is supported for all USB devices but the system does not automatically turn into DCP auto mode.

## 5.3 V<sub>BUS</sub> discharge

The  $V_{BUS}$  discharge pulse lasts for 350 ms typ. ( $t_{VBUS\_REAPP}$ ) and is performed for any transitions between the modes listed in *Table 5*, except the modes allowing remote wakeup in S3 [transitions (x10) and (111) to/from (011)] (see *Section 5.4*).

Permanent output discharge is provided in following modes:

- EN = 0, CTLx = xxx (ignored)

- EN = 1, CTLx = 000.

DocID024711 Rev 6

### 5.4 State machine

Figure 5. State machine

### 5.5 Charging detection

The STCC2540 device continuously monitors the current drawn by the portable device. While programmed in CDP or DCP mode, the STCC2540 device sends a charging flag to the system if the current through the USB power switch is above the charging threshold, set at 20 mA typ.: open drain active low output CHARGING is asserted.

Note:

In CDP mode, the charging flag is asserted only if the CDP handshaking between the portable device and the host is performed before the current is above the threshold.

If a device is charging (CDP mode) while the system is turned off and the battery supplied, the risk is that the charging process stops before the end of charge due to the system power-off. To avoid this, the flag CHARGING can be used by the host to prevent the switching-off of the high power DC-DC converter when the host goes to S5 state, even if battery supplied.

After the charging current drops below the threshold and the deglitch delay expires, the CHARGING output is deasserted.

#### 5.6 Power switch

#### Overcurrent conditions

When an overcurrent condition is detected, the device maintains a constant output current and reduces the voltage accordingly. There are two overload conditions:

- The first occurs when a short-circuit or a partial short-circuit is already present when

the device is being powered-up or enabled. The output voltage is held near zero

potential with respect to ground and the STCC2540 device ramps the output current to

I<sub>OS</sub> until the overload condition is removed or the device starts thermal cycle.

- The second condition is when a short-circuit, a partial short-circuit, or a transient overload occurs while the device is already enabled and powered-on. The STCC2540 device responds to an overcurrent condition within time t<sub>IOS</sub>. The current-sense amplifier is overdriven during this time and momentarily disables the internal current limit MOSFET. It then recovers and ramps the output current to I<sub>OS</sub>. Similar to previous conditions, it limits output current to I<sub>OS</sub> until the overload condition is removed or thermal cycle starts.

#### Thermal protection

The STCC2540 device has an internal thermal sensing circuit which monitors the operating temperature of the circuit. It disables the power switch operation if the die temperature exceeds temperature threshold  $T_{STOP}$ , set at 150 °C. The switch turns on if the temperature has cooled down by 20 °C.

#### Undervoltage lockout

The UVLO circuit disables the circuit until the input voltage reaches the UVLO turn-on threshold. Built-in hysteresis prevents unwanted on/off cycling due to input voltage drop during turn-on.

DocID024711 Rev 6

### **FAULT** functionality

The FAULT open drain active low output is asserted during overcurrent or overtemperature conditions. Signal is asserted until the fault is removed.

For overcurrent conditions, the STCC2540 device is designed to eliminate false FAULT reporting, by using an internal deglitch delay (9 ms typ.).

In the case of overtemperature, there is no deglitch delay and the FAULT signal is asserted immediately. It is deasserted with a delay after the device has cooled down and begins to turn on. This unidirectional glitch immunity prevents FAULT oscillation during an overtemperature event.

In the case of a fault condition, the host may disable the power switch by toggling EN input to logic low.

#### **Current limit programming**

The current limit can be adjusted by an external resistor in the range 500 mA to 2.8 A (max.). The programming resistor may be calculated using these equations:

**Equation 1**

$$I_{OS(typ)} = \frac{48000}{R_{ILIM}} (mA, k\Omega)$$

**Equation 2**

$$I_{OS(min)} = \frac{48000}{R_{ILIM}^{1.037}} (mA, k\Omega)$$

**Equation 3**

$$I_{OS(max)} = \frac{48000}{R_{ILIM}^{0.962}} (mA, k\Omega)$$

Equation 2 and Equation 3 allow the minimum and maximum variation to be estimated around the typical value predefined by the external resistor, R<sub>ILIM</sub>, given in Equation 1.

Equation 2 and Equation 3 do not take into consideration external resistor variations.

## 5.7 Enable input

The enable input (EN, active high) serves to turn off the STCC2540 device and achieve the lowest current consumption.

The behavior of the STCC2540 in disabled state (EN = 0) is following:

- Power switch, USB data switch and emulation profiles are turned off

- Output discharge circuit is turned on

- The FAULT and CHARGING flags are cleared (the FAULT and CHARGING outputs are set to Hi-Z mode).

## 5.8 Input and output capacitors

For proper functionality, the STCC2540 device requires two 1  $\mu$ F decoupling ceramic capacitors  $C_{IN}$  and  $C_{OUT}$  (see *Figure 4*). These capacitors should be placed as close as possible to the corresponding pins.

The electrolytic capacitor  $C_{VBUS}$  (see *Figure 4*) is required by the USB specification to suppress the voltage and current transients caused by hot plugging/unplugging the peripheral devices. This capacitor should be placed as close as possible to the USB connector. The recommended value is 150  $\mu$ F, low ESR type is preferred.

If the  $V_{IN}$  supply path is longer than approx. 150 mm, an additional capacitor is required and should be connected in parallel with the  $C_{IN}$  to suppress  $V_{IN}$  overvoltage transients caused by supply path inductance and fast current changes. The minimum value is 10  $\mu$ F, and a low ESR type is preferred.

DocID024711 Rev 6 17/32

# **6** Typical operating characteristics

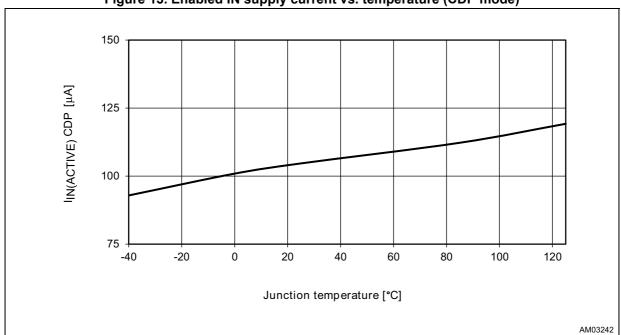

Figure 6. Power switch ON resistance vs. temperature

Figure 7. OUT discharge resistance vs. temperature

57

18/32 DocID024711 Rev 6

Figure 10. OUT short-circuit current limit vs. temperature (R $_{\rm ILIM}$  = 19.6 k $\Omega$ )

DocID024711 Rev 6 20/32

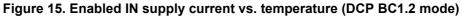

Figure 12. Enabled IN supply current vs. temperature (SDP mode)

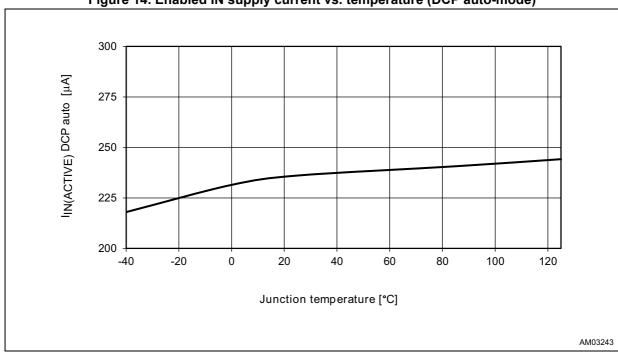

Figure 14. Enabled IN supply current vs. temperature (DCP auto-mode)

577

Figure 16. Enabled IN supply current vs. temperature (DCP divider mode)

DocID024711 Rev 6

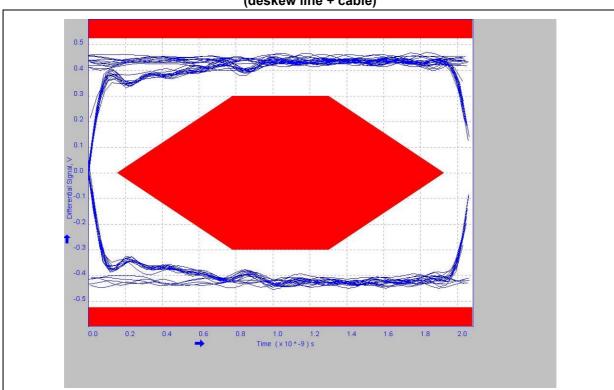

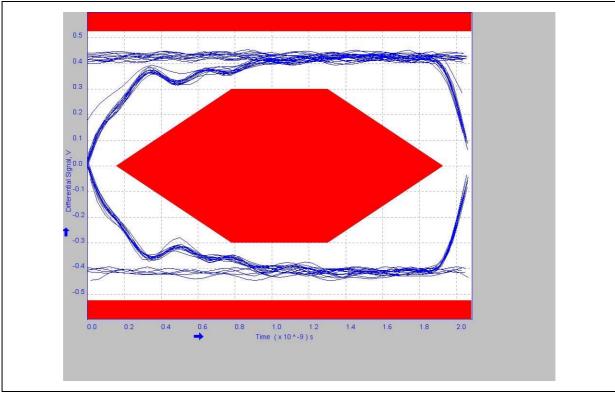

Figure 18. Eye diagram using USB compliance test pattern - without STCC2540 (deskew line + cable)

57/

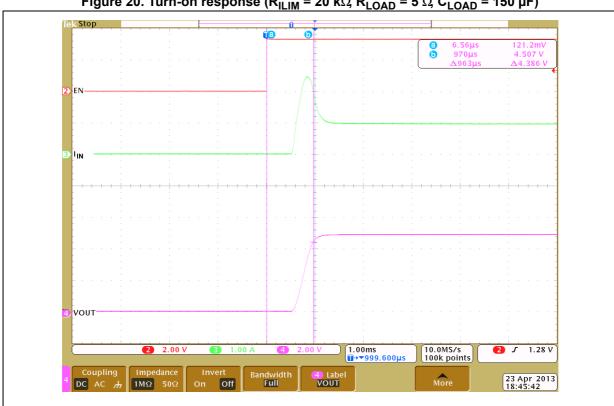

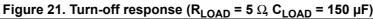

Figure 20. Turn-on response (R<sub>ILIM</sub> = 20 k $\Omega$ , R<sub>LOAD</sub> = 5  $\Omega$ , C<sub>LOAD</sub> = 150  $\mu$ F)

DocID024711 Rev 6

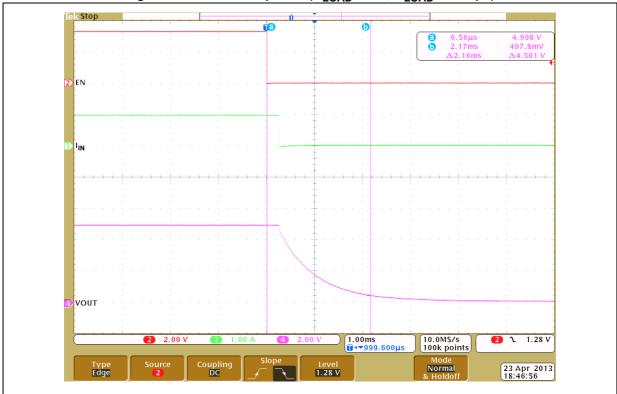

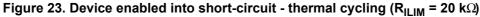

Figure 22. Device enabled into short-circuit ( $R_{ILIM}$  = 80.6 k $\Omega$ )

57

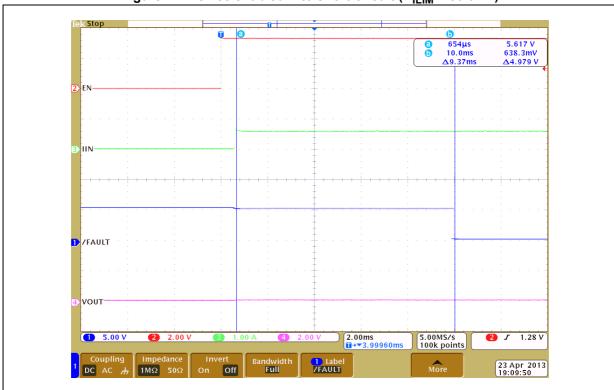

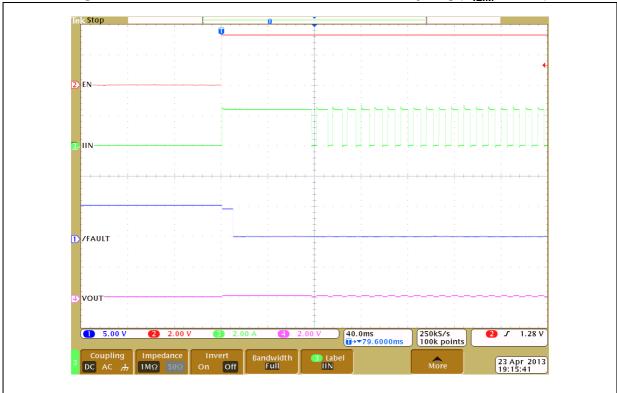

Figure 24. Short-circuit to full load recovery (R<sub>ILIM</sub> = 20 k $\Omega$ , R<sub>LOAD</sub> = 5  $\Omega$ , C<sub>LOAD</sub> = 150  $\mu$ F)

DocID024711 Rev 6

Package information STCC2540

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

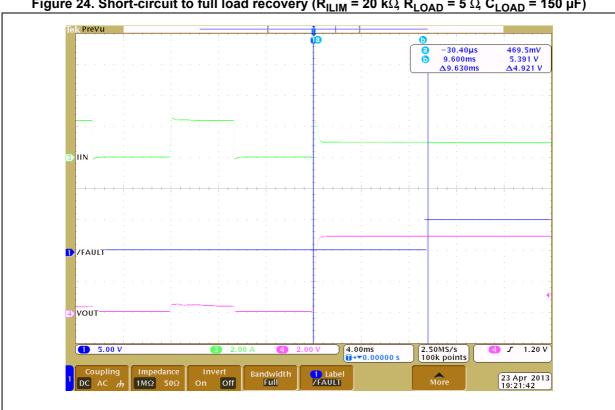

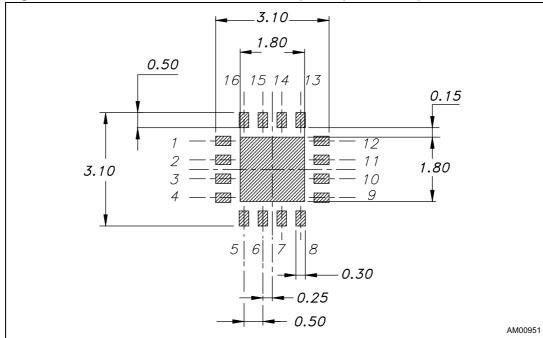

Figure 25. VFQFPN 16L 3 x 3 x 0.8 mm with exposed pad 1.7 package outline

STCC2540 Package information

Table 6. VFQFPN 16L 3 x 3 x 0.8 mm with exposed pad 1.7 package mechanical data  $^{(1)}$ ,  $^{(2)}$ ,  $^{(3)}$ ,  $^{(4)}$

|        |      | Dimensions |      |     |

|--------|------|------------|------|-----|

| Symbol |      | Notes      |      |     |

|        | Nom. | Min.       | Max. |     |

| А      | 0.75 | 0.70       | 0.80 |     |

| A1     | 0.02 | 0          | 0.05 |     |

| A3     | 0.20 |            |      |     |

| b      | 0.25 | 0.18       | 0.30 |     |

| D      | 3    | 2.90       | 3.10 |     |

| D2     | 1.70 | 1.50       | 1.80 |     |

| E      | 3    | 2.90       | 3.10 |     |

| E2     | 1.70 | 1.50       | 1.80 |     |

| е      | 0.50 |            |      |     |

| L      | 0.40 | 0.30       | 0.50 | (5) |

- 1. VFQFPN standard for "thermally enhanced very thin fine pitch quad flat package no leads".

- 2. The lead size is comprehensive of the thickness of the lead finishing material.

- 3. Dimensions do not include mold protrusion, not to exceed 0.15 mm.

- 4. Package outline exclusive of metal burr dimensions.

- 5. The value of "L", a JEDEC norm, is min. 0.35 max. 0.45.

Figure 26. VFQFPN 16L 3 x 3 x 0.8 mm with exposed pad 1.7 footprint recommended

Ordering information STCC2540

# 8 Ordering information

Table 7. Order codes

| Order code   | Temperature range | Marking | Package    | Packaging     |

|--------------|-------------------|---------|------------|---------------|

| STCC2540IQTR | -40 to 85 °C      | 2540CC  | VFQFPN 16L | Tape and reel |

30/32 DocID024711 Rev 6

STCC2540 Revision history

# 9 Revision history

**Table 8. Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29-May-2013 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 24-Jun-2013 | 2        | Updated <i>Features on page 1</i> (added "CB" components). Updated <i>Section 1: Functional description</i> (replaced 1000 MHz by 1100 MHz). Updated <i>Table 2</i> (added note <i>3.</i> ). Updated <i>Table 4</i> (updated parameters and conditions for IREVERSE I, IEN, IOL(FAULT), ICTLX, IOL(CHARGING), added typ. value for X <sub>TALK</sub> , O <sub>IRR</sub> , and B <sub>w</sub> , removed t <sub>PD</sub> and t <sub>SK</sub> symbols).                                                                                                                                     |

|             |          | Added Figure 4 on page 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |          | Added Note: in Section 5.1: Supported modes. Added Section 5.8: Input and output capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             |          | Added Section 6: Typical operating characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 06-Dec-2013 | 3        | Updated <i>Table 4</i> (updated min. conditions for $I_{OS}$ - $R_{ILIM}$ 96 k $\Omega$ and $R_{ILIM}$ 33 k $\Omega$ ). Updated <i>Table 5</i> (updated Host state column, added footnote 1. and 2.below table). Updated <i>Section 5.7</i> (replaced equation by <i>Equation 1</i> to <i>Equation 3</i> ). Minor modifications throughout document.                                                                                                                                                                                                                                     |

| 06-Jan-2014 | 4        | Corrected units in <i>Table 4 on page 7</i> (replaced "W" by " $\Omega$ " in R <sub>DISCHARGE</sub> , R <sub>ON</sub> and R <sub>DCP_RES</sub> symbols).                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 08-Jan-2014 | 5        | Updated Section : Features on page 1 (removed "2.5 A" from "Integrated $V_{BUS}$ power switch with low $R_{ON}$ of 65 m $\Omega$ " replaced "2.5 A" by "2.8 A (max.)" in "Adjustable current limit").  Added List of figures on page 3.  Updated Section 1: Functional description on page 3 [replaced "2.5 A" by "2.8 A (max.)"].  Updated Table 4 on page 7 (added " $R_{ILIM}$ = 17.2 k $\Omega$ " and typ. conditions of " $R_{ILIM}$ = 17.2 k $\Omega$ " for $I_{OS}$ symbol).  Updated Section : Current limit programming on page 16 [replaced "2.5 A (typ.)" by "2.8 A (max.)"]. |

| 25-Feb-2014 | 6        | Removed List of figures on page 3 Section 5.6: Power switch: updated Equation 2 and Equation 3 and added explanation of same.  Table 7: Order codes: updated "marking" of STCC2540IQTR                                                                                                                                                                                                                                                                                                                                                                                                   |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2014 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

DocID024711 Rev 6

单击下面可查看定价,库存,交付和生命周期等信息

>>STMicroelectronics(意法半导体)