### Energy saving high voltage converter for direct feedback

Datasheet - production data

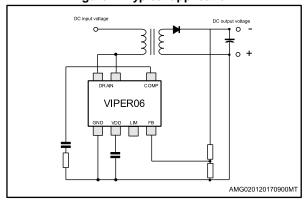

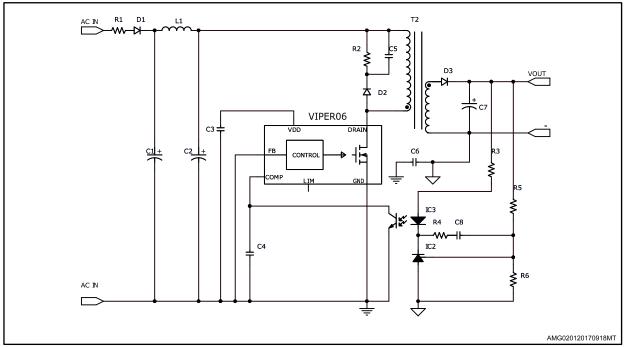

Figure 1: Typical application

#### **Applications**

- Replacement of capacitive power supplies

- Home appliances

- Power metering

- LED drivers

#### **Description**

The VIPER06 is an offline converter with an 800 V avalanche rugged power section, a PWM controller, a user-defined overcurrent limit, open-loop failure protection, hysteretic thermal protection, soft startup and safe auto-restart after any fault condition. The device is able to power itself directly from the rectified mains, eliminating the need for an auxiliary bias winding. Advanced frequency jittering reduces EMI filter cost. Burst mode operation and the device's very low power consumption both help to meet the standards set by energy-saving regulations.

#### **Features**

- 800 V avalanche rugged power section

- PWM operation with frequency jittering for low EMI

- Operating frequency:

- 30 kHz for VIPER06Xx

- 60 kHz for VIPER06Lx

- 115 kHz for VIPER06Hx

- No need for an auxiliary winding in low-power applications

- Standby power < 30 mW at 265 V<sub>AC</sub>

- Limiting current with adjustable set point

- On-board soft-start

- Safe auto-restart after a fault condition

- Hysteretic thermal shutdown

### **Contents**

| 1  |           | iagram                                           |    |

|----|-----------|--------------------------------------------------|----|

| 2  | Typical   | power                                            | 3  |

| 3  | Pin setti | ings                                             | 4  |

| 4  | Electrica | al data                                          | 5  |

|    | 4.1       | Maximum ratings                                  | 5  |

|    | 4.2       | Thermal data                                     | 5  |

|    | 4.3       | Electrical characteristics                       | 7  |

| 5  | Typical   | electrical characteristics                       | 9  |

| 6  | Typical   | circuit                                          | 12 |

| 7  |           | ection                                           |    |

| 8  | Hiah vol  | Itage current generator                          | 14 |

| 9  |           | or                                               |    |

| 10 |           | rtup                                             |    |

| 11 |           | ble current limit set point                      |    |

|    | _         |                                                  |    |

| 12 | -         | and COMP pin                                     |    |

| 13 |           | ode                                              |    |

| 14 |           | tic auto-restart after overload or short-circuit |    |

| 15 | Open-lo   | op failure protection                            | 19 |

| 16 | Layout (  | guidelines and design recommendations            | 20 |

| 17 | Package   | e information                                    | 22 |

|    | 17.1      | SSO10 package information                        | 22 |

|    | 17.2      | DIP-7 package information                        | 24 |

| 18 | Ordering  | g information                                    | 26 |

| 19 | Revision  | n history                                        | 27 |

|    |           |                                                  |    |

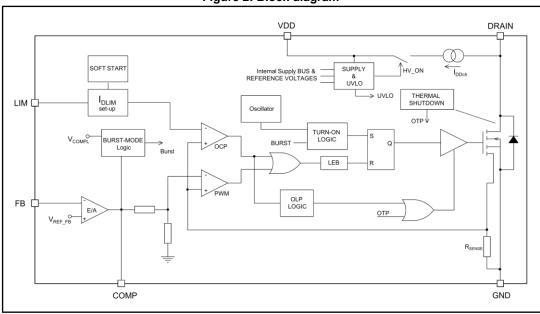

VIPER06 Block diagram

### 1 Block diagram

Figure 2: Block diagram

### 2 Typical power

Table 1: Typical power

| Part number | 2           | 30 V <sub>AC</sub> | 85-         | -265 V <sub>AC</sub>      |

|-------------|-------------|--------------------|-------------|---------------------------|

| Part number | Adapter (1) | Open frame (2)     | Adapter (1) | Open frame <sup>(2)</sup> |

| VIPER06     | 6 W         | 8 W                | 4 W         | 5 W                       |

#### Notes:

$<sup>^{(1)}</sup>$ Typical continuous power in non-ventilated enclosed adapter measured at 50 °C ambient.

<sup>&</sup>lt;sup>(2)</sup>Maximum practical continuous power in an open-frame design at 50 °C ambient, with adequate heat sinking.

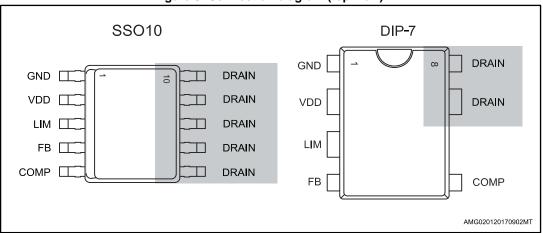

Pin settings VIPER06

# 3 Pin settings

Figure 3: Connection diagram (top view)

The copper area for heat dissipation has to be designed under the DRAIN pins.

**Table 2: Pin description**

| Pin   |       | Name  | Function                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP-7 | SSO10 | Name  | runction                                                                                                                                                                                                                                                                                                                                                             |

| 1     | 1     | GND   | Connected to the source of the internal power MOSFET and controller ground reference.                                                                                                                                                                                                                                                                                |

| 2     | 2     | VDD   | Supply voltage of the control section. This pin provides the charging current of the external capacitor.                                                                                                                                                                                                                                                             |

| 3     | 3     | LIM   | This pin allows setting the drain current limitation. The limit can be reduced by connecting an external resistor between this pin and GND. Pin left open if default drain current limitation is used.                                                                                                                                                               |

| 4     | 4     | FB    | Inverting input of the internal transconductance error amplifier.  Connecting the converter output to this pin through a single resistor results in an output voltage equal to the error amplifier reference voltage (see V <sub>FB_REF</sub> in <i>Table 6: "Supply section "</i> ). An external resistor divider is required for higher output voltages.           |

| 5     | 5     | COMP  | Output of the internal transconductance error amplifier. The compensation network has to be placed between this pin and GND to achieve stability and good dynamic performance of the voltage control loop. The pin is used also to directly control the PWM with an optocoupler. The linear voltage range extends from VCOMPL to VCOMPH (Table 6: "Supply section"). |

| 7, 8  | 6-10  | DRAIN | High-voltage drain pins. The built-in high-voltage switched startup bias current is drawn from these pins too. Pins connected to the metal frame to facilitate heat dissipation.                                                                                                                                                                                     |

VIPER06 Electrical data

#### 4 Electrical data

### 4.1 Maximum ratings

Table 3: Absolute maximum ratings

| Cumab al           | D:: (DID 7) | Parameter                                                         | V    | alue             | Unit |

|--------------------|-------------|-------------------------------------------------------------------|------|------------------|------|

| Symbol             | Pin (DIP-7) | Parameter                                                         | Min. | Max.             | Unit |

| V <sub>DRAIN</sub> | 7, 8        | Drain-to-source (ground) voltage                                  |      | 800              | V    |

| Eav                | 7, 8        | Repetitive avalanche energy (limited by T <sub>J</sub> = 150 °C)  |      | 2                | mJ   |

| I <sub>AR</sub>    | 7, 8        | Repetitive avalanche current (limited by T <sub>J</sub> = 150 °C) |      | 1                | Α    |

| Idrain             | 7, 8        | Pulse drain current (limited by T <sub>J</sub> = 150 °C)          |      | 2.5              | А    |

| $V_{COMP}$         | 5           | Input pin voltage                                                 | -0.3 | 3.5              | V    |

| $V_{FB}$           | 4           | Input pin voltage                                                 | -0.3 | 4.8              | V    |

| $V_{LIM}$          | 3           | Input pin voltage                                                 | -0.3 | 2.8              | V    |

| $V_{DD}$           | 2           | Supply voltage                                                    | -0.3 | Self-<br>limited | V    |

| $I_{DD}$           | 2           | Input current                                                     |      | 20               | mA   |

| D                  |             | Power dissipation at T <sub>A</sub> < 40 °C (DIP-7)               |      | 1                | W    |

| Ртот               |             | Power dissipation at T <sub>A</sub> < 50 °C (SSO10)               |      | 1                | W    |

| TJ                 |             | Operating junction temperature range                              | -40  | 150              | °C   |

| T <sub>STG</sub>   |             | Storage temperature                                               | -55  | 150              | °C   |

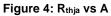

### 4.2 Thermal data

Table 4: Thermal data

| Symbol            | Parameter                                                        | Max. value<br>SSO10 | Max. value<br>DIP-7 | Unit |

|-------------------|------------------------------------------------------------------|---------------------|---------------------|------|

| R <sub>thJP</sub> | Thermal resistance junction pin (dissipated power = 1 W)         | 35                  | 40                  | °C/W |

| R <sub>thJA</sub> | Thermal resistance junction ambient (dissipated power = 1 W)     | 145                 | 110                 | °C/W |

| R <sub>thJA</sub> | Thermal resistance junction ambient (dissipated power = 1 W) (1) | 90                  | 90                  | °C/W |

#### Notes:

$<sup>^{(1)}</sup>$ When mounted on a standard single side FR4 board with 100 mm<sup>2</sup> (0.155 sq in) of Cu (35  $\mu$ m thick).

Electrical data VIPER06

6/28 DocID022794 Rev 2

VIPER06 Electrical data

#### 4.3 Electrical characteristics

$(T_J = -25 \text{ to } 125 \text{ }^{\circ}\text{C}, \ V_{DD} = 14 \ V^a \text{ unless otherwise specified}).$

Table 5: Power section

| Symbol              | Parameter                                     | Test condition                                                      | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------|---------------------------------------------------------------------|------|------|------|------|

| V <sub>BVDSS</sub>  | Breakdown voltage                             | $I_{DRAIN} = 1 \text{ mA}, V_{COMP} = GND,$ $T_{J} = 25 \text{ °C}$ | 800  |      |      | V    |

| loff                | OFF state drain current                       | V <sub>DRAIN</sub> = max rating,<br>V <sub>COMP</sub> = GND         |      |      | 60   | μΑ   |

| D                   | Drain-source on-state resistance              | I <sub>DRAIN</sub> = 0.2 A, T <sub>J</sub> = 25 °C                  |      |      | 32   | Ω    |

| R <sub>DS(on)</sub> | Diditi-Source off-state resistance            | I <sub>DRAIN</sub> = 0.2 A, T <sub>J</sub> = 125 °C                 |      |      | 67   | Ω    |

| Coss                | Effective (energy related) output capacitance | V <sub>DRAIN</sub> = 0 to 640 V                                     |      | 10   |      | pF   |

Table 6: Supply section

|                          |                                                          | Table 0. Supply Section                                                    |      |      |      |      |

|--------------------------|----------------------------------------------------------|----------------------------------------------------------------------------|------|------|------|------|

| Symbol                   | Parameter                                                | Test condition                                                             | Min. | Тур. | Max. | Unit |

| Voltage                  |                                                          |                                                                            | ·    |      |      |      |

| V <sub>DRAIN_START</sub> | Drain-source startup voltage                             |                                                                            | 25   |      | 45   | V    |

| I <sub>DDch1</sub>       | Startup charging current                                 | V <sub>DRAIN</sub> = 100 V to 640 V,<br>V <sub>DD</sub> = 4 V              | -0.6 |      | -1.8 | mA   |

| I <sub>DDch2</sub>       | Charging current during operation                        | V <sub>DRAIN</sub> = 100 V to 640 V,<br>V <sub>DD</sub> = 9 V falling edge | -7   |      | -14  | mA   |

| $V_{DD}$                 | Operating voltage range                                  |                                                                            | 11.5 |      | 23.5 | V    |

| $V_{DDclamp}$            | V <sub>DD</sub> clamp voltage                            | I <sub>DD</sub> = 15 mA                                                    | 23.5 |      |      | V    |

| $V_{DDon}$               | V <sub>DD</sub> startup threshold                        |                                                                            | 12   | 13   | 14   | V    |

| VDDCSon                  | VDD on internal high-voltage current generator threshold |                                                                            | 9.5  | 10.5 | 11.5 | V    |

| $V_{DDoff}$              | V <sub>DD</sub> undervoltage shutdown threshold          |                                                                            | 7    | 8    | 9    | V    |

| Current                  |                                                          |                                                                            |      |      |      |      |

| I <sub>DD0</sub>         | Operating supply current, not switching                  | F <sub>OSC</sub> = 0 kHz, V <sub>COMP</sub> = GND                          |      |      | 0.6  | mA   |

|                          |                                                          | V <sub>DRAIN</sub> = 120 V, F <sub>OSC</sub> = 30 kHz                      |      |      | 1.3  | mA   |

| $I_{DD1}$                | Operating supply current, switching                      | V <sub>DRAIN</sub> = 120 V, F <sub>OSC</sub> = 60 kHz                      |      |      | 1.45 | mA   |

|                          | ownorming                                                | V <sub>DRAIN</sub> = 120 V, F <sub>OSC</sub> = 115 kHz                     |      |      | 1.6  | mA   |

| I <sub>DDoff</sub>       | Operating supply current with VDD < VDDoff               | V <sub>DD</sub> = 5 V                                                      |      |      | 0.35 | mA   |

| I <sub>DDol</sub>        | Open-loop failure current threshold                      | V <sub>DD</sub> = V <sub>DDclamp</sub> V <sub>COMP</sub> = 3.3 V           | 4    |      |      | mA   |

$<sup>^{\</sup>rm a}$  Adjust V<sub>DD</sub> above V<sub>DDon</sub> startup threshold before setting to 14 V.

Electrical data VIPER06

**Table 7: Controller section**

|                        |                                          | Table 7: Controller section                                   |      |      |      |      |

|------------------------|------------------------------------------|---------------------------------------------------------------|------|------|------|------|

| Symbol                 | Parameter                                | Test condition                                                | Min. | Тур. | Max. | Unit |

| Error amplif           | ier                                      |                                                               |      |      |      |      |

| V <sub>REF_FB</sub>    | FB reference voltage                     |                                                               | 3.2  | 3.3  | 3.4  | V    |

| FB_PULL UP             | Current pull-up                          |                                                               |      | -1   |      | μΑ   |

| Gм                     | Transconductance                         |                                                               |      | 2    |      | mA/V |

| Current sett           | ing (LIM) pin                            |                                                               |      |      |      |      |

| V <sub>LIM_LOW</sub>   | Low-level clamp voltage                  | I <sub>LIM</sub> = -100 μA                                    |      | 0.5  |      | V    |

| Compensati             | on (COMP) pin                            |                                                               |      |      | l.   |      |

| Vсомрн                 | Upper saturation limit                   | T <sub>J</sub> = 25 °C                                        |      | 3    |      | V    |

| Vcompl                 | Burst mode threshold                     | T <sub>J</sub> = 25 °C                                        | 1    | 1.1  | 1.2  | V    |

| Vcompl_hys             | Burst mode hysteresis                    | T <sub>J</sub> = 25 °C                                        |      | 40   |      | mV   |

| Нсомр                  | ΔV <sub>COMP</sub> / ΔI <sub>DRAIN</sub> |                                                               | 3    |      | 6    | V/A  |

| R <sub>COMP(DYN)</sub> | Dynamic resistance                       | V <sub>FB</sub> = GND                                         |      | 15   |      | kΩ   |

|                        | Source / sink current                    | V <sub>FB</sub> > 100 mV                                      |      | 150  |      | μΑ   |

| Ісомр                  | Max source current                       | $V_{COMP} = GND, V_{FB} = GND$                                |      | 220  |      | μA   |

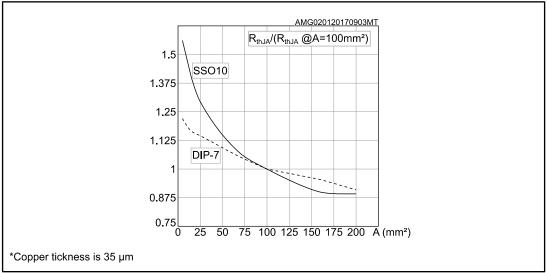

| Current limi           | tation                                   |                                                               | •    | •    |      |      |

| lDlim                  | Drain current limitation                 | $I_{LIM}$ = -10 $\mu$ A, $V_{COMP}$ = 3.3 $V$ , $T_J$ = 25 °C | 0.32 | 0.35 | 0.38 | А    |

| tss                    | Soft-start time                          |                                                               |      | 8.5  |      | ms   |

| T <sub>ON_MIN</sub>    | Minimum turn-on time                     |                                                               |      |      | 450  | ns   |

| I <sub>Dlim_bm</sub>   | Burst mode current limitation            | VCOMP = VCOMPL                                                |      | 85   |      | mA   |

| Overload               |                                          |                                                               |      |      |      |      |

| tovL                   | Overload time                            |                                                               |      | 50   |      | ms   |

| trestart               | Restart time after fault                 |                                                               |      | 1    |      | s    |

| Oscillator se          | ection                                   |                                                               |      |      | l.   |      |

|                        |                                          | VIPER06Xx                                                     | 27   | 30   | 33   | kHz  |

| Fosc                   | Switching frequency                      | VIPER06Lx                                                     | 54   | 60   | 66   | kHz  |

|                        |                                          | VIPER06Hx                                                     | 103  | 115  | 127  | kHz  |

|                        |                                          | Fosc = 30 kHz                                                 |      | ±2   |      | kHz  |

| $F_D$                  | Modulation depth                         | Fosc = 60 kHz                                                 |      | ±4   |      | kHz  |

|                        |                                          | F <sub>OSC</sub> = 115 kHz                                    |      | ±8   |      | kHz  |

| F <sub>M</sub>         | Modulation frequency                     |                                                               |      | 230  |      | Hz   |

| D <sub>MAX</sub>       | Maximum duty cycle                       |                                                               | 70   |      | 80   | %    |

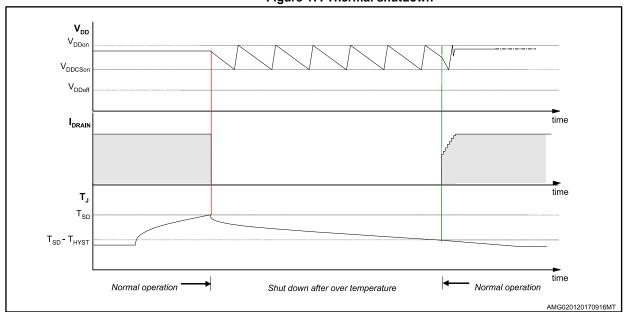

| Thermal shu            | ıtdown                                   |                                                               |      |      |      |      |

| T <sub>SD</sub>        | Thermal shutdown temperature             |                                                               | 150  | 160  |      | °C   |

| T <sub>HYST</sub>      | Thermal shutdown hysteresis              |                                                               |      | 30   |      | °C   |

8/28 DocID022794 Rev 2

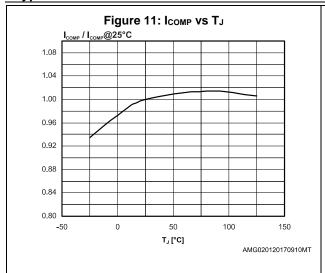

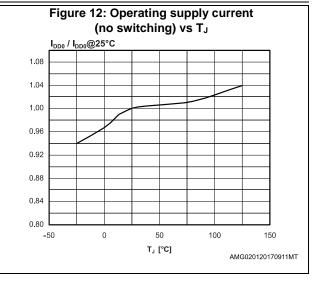

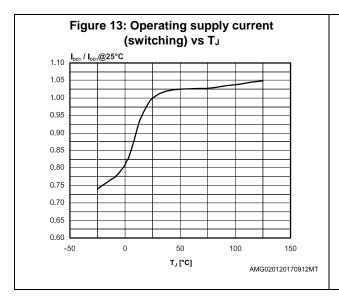

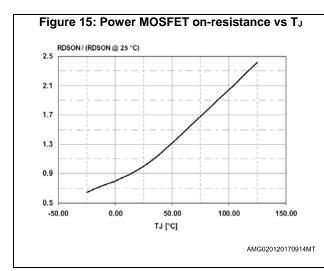

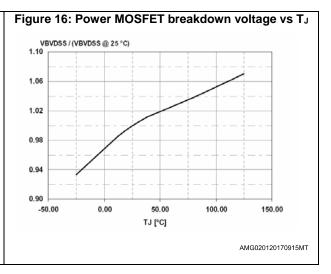

# 5 Typical electrical characteristics

577

DocID022794 Rev 2

9/28

10/28 DocID022794 Rev 2

Figure 17: Thermal shutdown

Typical circuit VIPER06

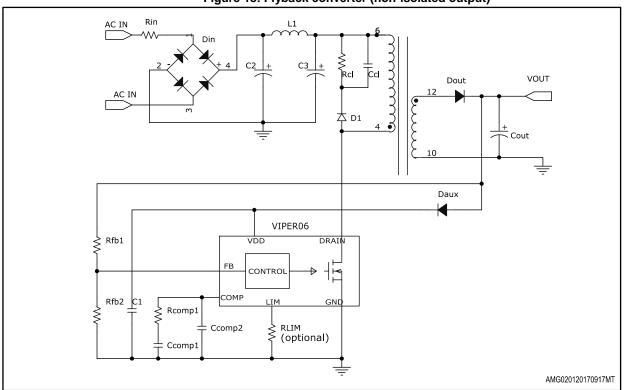

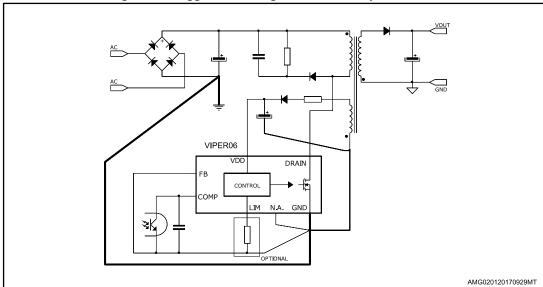

# 6 Typical circuit

Figure 18: Flyback converter (non-isolated output)

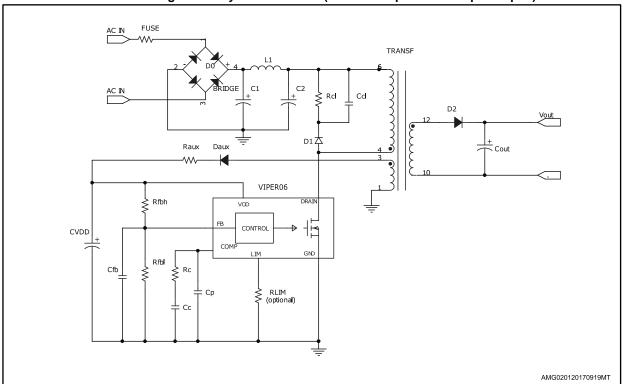

Figure 19: Flyback converter (isolated output)

VIPER06 Typical circuit

Figure 20: Flyback converter (isolated output without optocoupler)

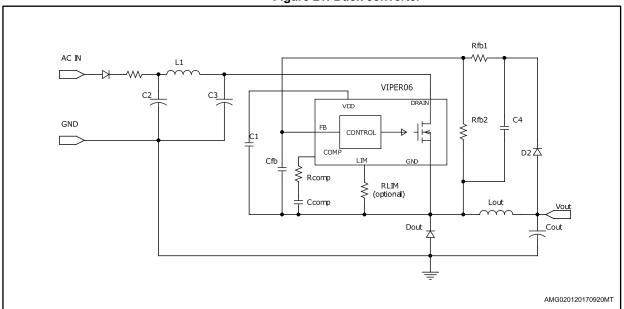

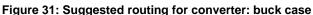

Figure 21: Buck converter

Power section VIPER06

#### 7 Power section

The power section is implemented with an N-channel power MOSFET with a breakdown voltage of 800 V min. and a typical  $R_{DS(on)}$  of 32  $\Omega$ . It includes a SenseFET structure to allow virtually lossless current sensing and the thermal sensor.

The gate driver of the power MOSFET is designed to supply a controlled gate current during both turn-ON and turn-OFF in order to minimize common-mode EMI. During UVLO conditions, an internal pull-down circuit holds the gate low in order to ensure that the power MOSFET cannot be turned ON accidentally.

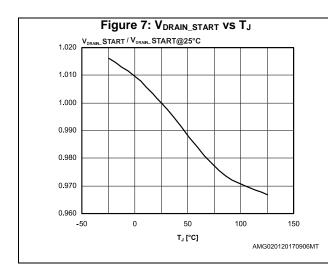

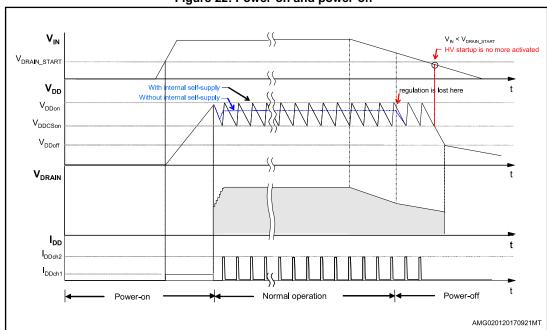

### 8 High voltage current generator

The high-voltage current generator is supplied by the DRAIN pin. At the first startup of the converter it is enabled when the voltage across the input bulk capacitor reaches the V<sub>DRAIN\_START</sub> threshold, sourcing a I<sub>DDch1</sub> current (see *Table 6: "Supply section"*). As the V<sub>DD</sub> voltage reaches the V<sub>DDon</sub> threshold, the power section starts switching and the high-voltage current generator is turned OFF. The VIPER06 is powered by the energy stored in the V<sub>DD</sub> capacitor.

In a steady-state condition, if the self-biasing function is used, the high-voltage current generator is activated between V<sub>DDCSon</sub> and V<sub>DDon</sub> (see *Table 6: "Supply section "*), delivering I<sub>DDch2</sub>, see *Table 6: "Supply section "* to the V<sub>DD</sub> capacitor during the MOSFET off-time (see *Figure 22: "Power-on and power-off"*).

The device can also be supplied through the auxiliary winding in which case the high-voltage current source is disabled during steady-state operation, provided that VDD is above  $V_{\text{DDCSon}}$ .

At converter power-down, the  $V_{DD}$  voltage drops and the converter activity stops as it falls below the  $V_{DDoff}$  threshold (see *Table 6: "Supply section"*).

Figure 22: Power-on and power-off

VIPER06 Oscillator

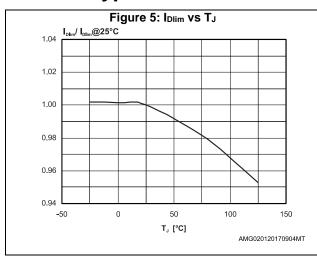

#### 9 Oscillator

The switching frequency is internally fixed at 30 kHz or 60 kHz or 115 kHz (respectively part numbers VIPER06Xx, VIPER06Lx and VIPER06Hx).

The switching frequency is modulated by approximately ±3 kHz (30 kHz version) or ±4 kHz (60 kHz version) or ±8 kHz (115 kHz version) at 230 Hz (typical) rate, so that the resulting spread spectrum action distributes the energy of each harmonic of the switching frequency over a number of sideband harmonics having the same energy on the whole, but smaller amplitudes.

### 10 Soft startup

During the converter's startup phase, the soft-start function progressively increases the cycle-by-cycle drain current limit, up to the default value I<sub>Dim</sub>. In this way the drain current is further limited and the output voltage is progressively increased, reducing the stress on the secondary diode. The soft-start time is internally fixed to t<sub>SS</sub>, see typical value in *Table 7:* "Controller section", and the function is activated for any attempt of converter startup and after a fault event.

This function helps prevent saturation of the transformer during startup and short-circuit.

### 11 Adjustable current limit set point

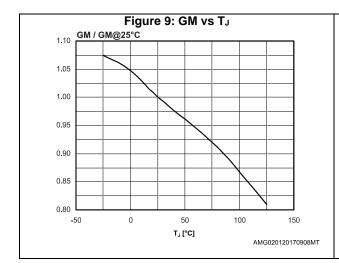

The VIPER06 includes a current-mode PWM controller. The drain current is sensed cycle-by-cycle through the integrated resistor R<sub>SENSE</sub> and the voltage is applied to the non-inverting input of the PWM comparator, see *Figure 2: "Block diagram"*. As soon as the sensed voltage is equal to the voltage derived from the COMP pin, the power MOSFET is switched OFF.

In parallel with the PWM operations, the comparator OCP, see *Figure 2: "Block diagram"*, checks the level of the drain current and switches OFF the power MOSFET in case the current is higher than the threshold I<sub>Dlim</sub>, see *Table 7: "Controller section"*.

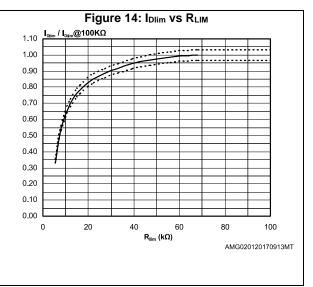

The level of the drain current limit  $I_{Dlim}$  can be reduced using a resistor  $R_{LIM}$  connected between the LIM and GND pins. Current is sunk from the LIM pin through the resistor  $R_{LIM}$  and the setup of  $I_{Dlim}$  depends on the level of this current. The relation between  $I_{Dlim}$  and  $R_{LIM}$  is shown in *Figure 14: "IDlim vs RLIM"*.

When the LIM pin is left open or if  $R_{LIM}$  has a high value (i.e. > 80 k $\Omega$ ), the current limit is fixed to its default value,  $I_{Dlim}$ , as given in *Table 7: "Controller section"*.

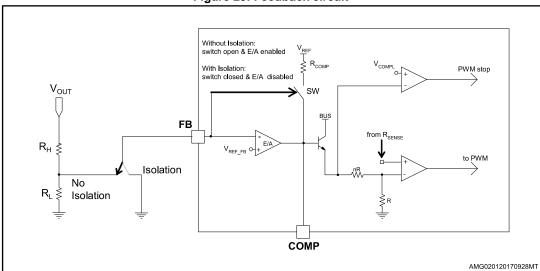

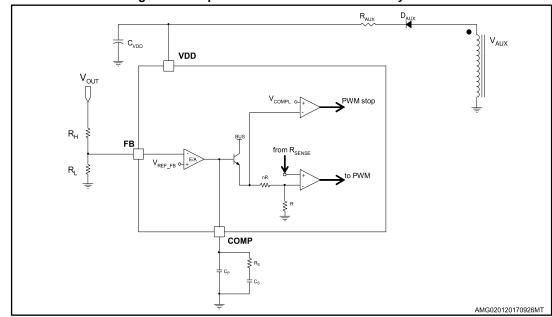

### 12 FB pin and COMP pin

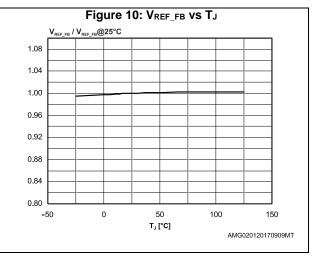

The device can be used both in non-isolated and isolated topology. In non-isolated topology, the feedback signal from the output voltage is applied directly to the FB pin as the inverting input of the internal error amplifier having the reference voltage, V<sub>REF\_FB</sub>, see *Table 7: "Controller section"*.

The output of the error amplifier sources and sinks the current, I<sub>COMP</sub>, respectively to and from the compensation network connected on the COMP pin. This signal is then compared in the PWM comparator with the signal coming from the SenseFET in order to switch off the power MOSFET on a cycle-by-cycle basis. See the *Figure 2: "Block diagram"* and the *Figure 23: "Feedback circuit"*.

When the power supply output voltage is equal to the error amplifier reference voltage, V<sub>REF\_FB</sub>, a single resistor has to be connected from the output to the FB pin. For higher output voltages the external resistor divider is needed. If the voltage on the FB pin is accidentally left floating, an internal pull-up protects the controller.

The output of the error amplifier is externally accessible through the COMP pin and it's used for the loop compensation, usually an RC network.

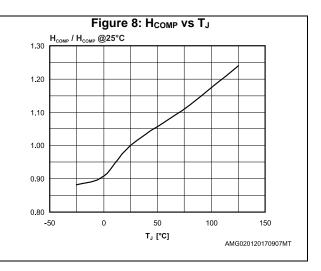

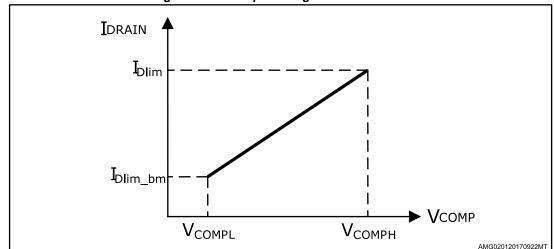

As shown in *Figure 23: "Feedback circuit"*, in case of an isolated power supply, the internal error amplifier has to be disabled (FB pin shorted to GND). In this case an internal resistor is connected between an internal reference voltage and the COMP pin, see *Figure 23: "Feedback circuit"*. The current loop has to be closed on the COMP pin through the optotransistor in parallel with the compensation network. The V<sub>COMP</sub> dynamic range is between V<sub>COMPL</sub> and V<sub>COMPH</sub> shown in *Figure 24: "COMP pin voltage versus IDRAIN"*.

When the voltage V<sub>COMP</sub> drops below the voltage threshold V<sub>COMPL</sub>, the converter enters burst mode, see *Section 13: "Burst mode"*.

When the voltage V<sub>COMP</sub> rises above the V<sub>COMPH</sub> threshold, the peak drain current, as well as the deliverable output power, will reach its limit.

Figure 23: Feedback circuit

VIPER06 Burst mode

Figure 24: COMP pin voltage versus IDRAIN

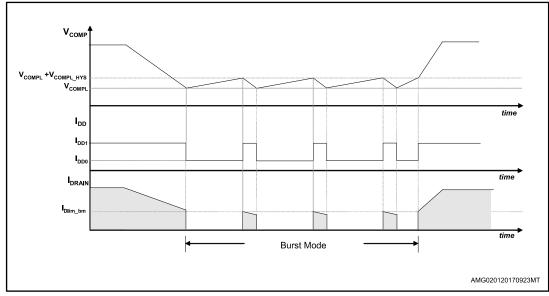

#### 13 Burst mode

When the voltage  $V_{\text{COMP}}$  drops below the threshold,  $V_{\text{COMPL}}$ , the power MOSFET is kept in the OFF state and the consumption is reduced to the  $I_{\text{DD0}}$  current, as reported on *Table 6:* "Supply section". In reaction to the loss of energy, the  $V_{\text{COMP}}$  voltage increases and as soon as it exceeds the threshold  $V_{\text{COMPL}} + V_{\text{COMPL}}$ , the converter starts switching again with a level of consumption equal to the  $I_{\text{DD1}}$  current. This ON-OFF operation mode, referred to as "burst mode" and shown in *Figure 25: "Load-dependent operating modes: timing waveforms"*, reduces the average frequency, which can go down even to a few hundreds hertz, thus minimizing all frequency-related losses and making it easier to comply with energy-saving regulations. During burst mode, the drain current limit is reduced to the value  $I_{\text{Dlim}\_\text{bm}}$  (given in *Table 7: "Controller section"*) in order to avoid the audible noise issue.

Figure 25: Load-dependent operating modes: timing waveforms

DocID022794 Rev 2

17/28

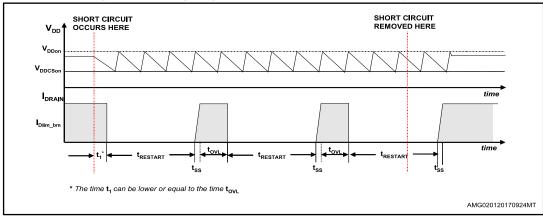

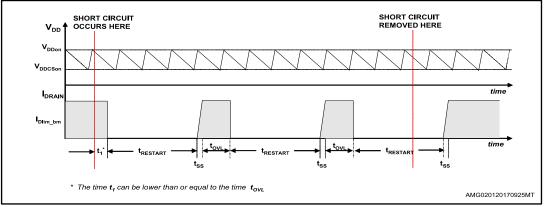

#### 14 Automatic auto-restart after overload or short-circuit

The overload protection is implemented automatically using the integrated up-down counter. Every cycle, it is incremented or decremented depending upon the current logic detection of the limit condition or not. The limit condition is the peak drain current, Inlim given in Table 7: "Controller section" or the one set by the user through the RLIM resistor, shown in Figure 14: "IDlim vs RLIM". After the reset of the counter, if the peak drain current is continuously equal to the level IDlim, the counter will be incremented until the fixed time, tovL, at which point the power MOSFET switch ON will be disabled. It will be activated again through the soft-start after the trestart time (see Figure 26: "Timing diagram: OLP sequence (IC externally biased)" and Figure 27: "Timing diagram: OLP sequence (IC internally biased)") and the time values mentioned in Table 7: "Controller section ".

For overload or short-circuit events, the power MOSFET switching will be stopped after a period of time dependent upon the counter with a maximum equal to toy. The protection sequence continues until the overload condition is removed, see Figure 26: "Timing diagram: OLP sequence (IC externally biased)" and Figure 27: "Timing diagram: OLP sequence (IC internally biased)". This protection ensures a low repetition rate of restart attempts of the converter, so that it works safely with extremely low power throughput and avoids overheating the IC in case of repeated overload events. If the overload is removed before the protection tripping, the counter will be decremented cycle-by-cycle down to zero and the IC will not be stopped.

Figure 26: Timing diagram: OLP sequence (IC externally biased)

Figure 27: Timing diagram: OLP sequence (IC internally biased)

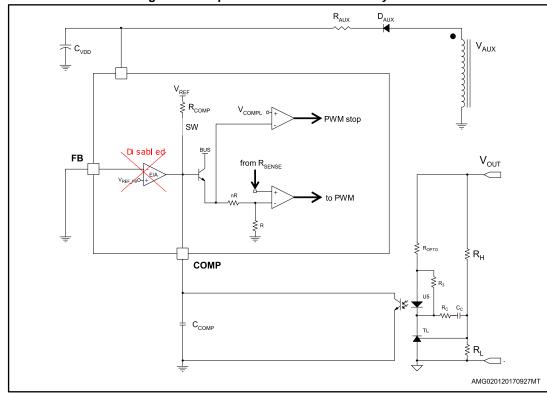

### 15 Open-loop failure protection

If the power supply has been designed using flyback topology and the VIPER06 is supplied by an auxiliary winding, as shown in *Figure 28: "FB pin connection for non-isolated flyback"* and *Figure 29: "FB pin connection for isolated flyback"*, the converter is protected against feedback loop failure or accidental disconnections of the winding.

The following description is applicable for the schematics of *Figure 28: "FB pin connection for non-isolated flyback"* and *Figure 29: "FB pin connection for isolated flyback"*, respectively the non-isolated flyback and the isolated flyback.

If  $R_H$  is open or  $R_L$  is shorted, the VIPER06 works at its drain current limitation. The output voltage,  $V_{OUT}$ , will increase as does the auxiliary voltage,  $V_{AUX}$ , which is coupled with the output through the secondary-to-auxiliary turns ratio.

As the auxiliary voltage increases up to the internal  $V_{DD}$  active clamp,  $V_{DDclamp}$  (the value is given in *Table 7: "Controller section"*) and the clamp current injected on the VDD pin exceeds the latch threshold,  $I_{DDol}$  (the value is given in *Table 7: "Controller section"*), a fault signal is internally generated.

In order to distinguish an actual malfunction from a bad auxiliary winding design, both the above conditions (drain current equal to the drain current limitation and current higher than  $I_{DDol}$  through the VDD clamp) have to be verified to reveal the fault.

If  $R_L$  is open or  $R_H$  is shorted, the output voltage,  $V_{OUT}$ , will be clamped to the reference voltage  $V_{REF\_FB}$  (for non-isolated flyback) or to the external TL voltage reference (for isolated flyback).

Figure 28: FB pin connection for non-isolated flyback

47/

Figure 29: FB pin connection for isolated flyback

#### 16 Layout guidelines and design recommendations

A proper printed circuit board layout is essential for correct operation of any switch-mode converter and this is true for the VIPer06 as well. Also some trick can be used to make the design rugged versus external influences.

Careful component placing, correct traces routing, appropriate traces widths and compliance with isolation distances are the major issues.

The main reasons to have a proper PCB routing are:

- Provide a noise free path for the signal ground and for the internal references, ensuring good immunity against switching noises

- Minimize the pulsed loops (both primary and secondary) to reduce the electromagnetic interferences, both radiated and conducted and passing more easily the EMC regulations.

The below list can be used as guideline when designing a SMPS using VIPer06.

- Signal ground routing should be routed separately from power ground and, in general, from any pulsed high current loop;

- Connect all the signal ground traces to the power ground, using a single "star point", placed close to the IC GND pin;

- With flyback topologies, when the auxiliary winding is used, it is suggested to connect

the VDD capacitor on the auxiliary return and then to the main GND using a single

track;

- The compensation network should be connected as close as possible to the COMP pin, maintaining the trace for the GND as short as possible;

20/28 DocID022794 Rev 2

- A small bypass capacitor (a few hundreds pF up to 0.1 µF) to GND might be useful to get a clean bias voltage for the signal part of the IC and protect the IC itself during EFT/ESD tests. A low ESL ceramic capacitor should be used, placed as close as possible to the VDD pin;

- When using SO16N package it is recommended to connect the pin 4 to GND pin, using a signal track, in order to improve the noise immunity. This is highly recommended in case of high nosily environment;

- The IC thermal dissipation takes place through the drain pins. An adequate heat sink copper area has to be designed under the drain pins to improve the thermal dissipation;

- It is not recommended to place large copper areas on the GND pins.

- Minimize the area of the pulsed loops (primary, RCD and secondary loops), in order to reduce its parasitic self- inductance and the radiated electromagnetic field: this will greatly reduce the electromagnetic interferences produced by the power supply during the switching.

Figure 30: Suggested routing for converter: flyback case

DocID022794 Rev 2

Package information VIPER06

### 17 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: **www.st.com**. ECOPACK® is an ST trademark.

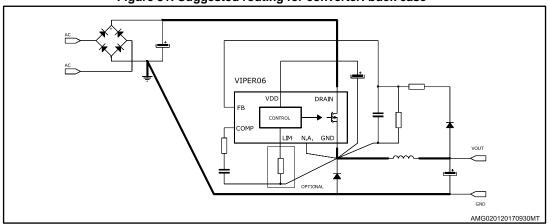

#### 17.1 SSO10 package information

Figure 32: SSO10 package outline

Table 8: SSO10 package mechanical data

| Dim. | mm   |      |      |  |  |

|------|------|------|------|--|--|

|      | Min. | Тур. | Max. |  |  |

| A    |      |      | 1.75 |  |  |

| A1   | 0.10 |      | 0.25 |  |  |

| A2   | 1.25 |      |      |  |  |

| b    | 0.31 |      | 0.51 |  |  |

| С    | 0.17 |      | 0.25 |  |  |

| D    | 4.80 | 4.90 | 5    |  |  |

| Е    | 5.80 | 6    | 6.20 |  |  |

| E1   | 3.80 | 3.90 | 4    |  |  |

| е    |      | 1    |      |  |  |

| h    | 0.25 |      | 0.50 |  |  |

| L    | 0.40 |      | 0.90 |  |  |

| K    | 0°   |      | 8°   |  |  |

Package information VIPER06

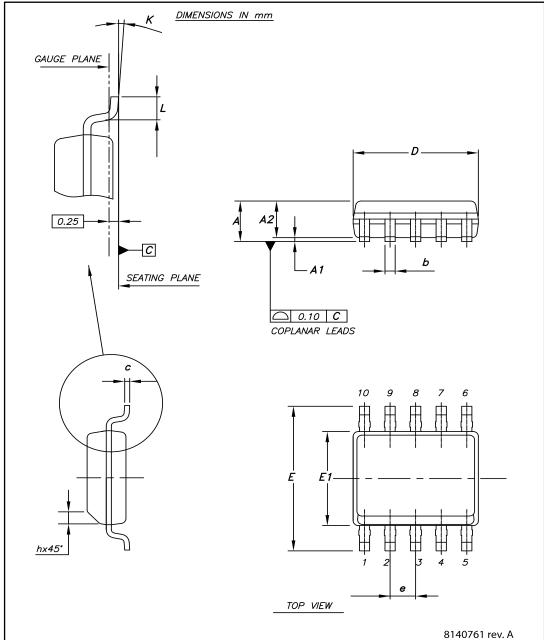

# 17.2 DIP-7 package information

Figure 33: DIP-7 package outline

Table 9: DIP-7 package mechanical data

| Dim.                |      | mm    |       | Notes |

|---------------------|------|-------|-------|-------|

|                     | Min. | Тур.  | Max.  | Notes |

| А                   |      |       | 5.33  |       |

| A1                  | 0.38 |       |       |       |

| A2                  | 2.92 | 3.30  | 4.95  |       |

| b                   | 0.36 | 0.46  | 0.56  |       |

| b2                  | 1.14 | 1.52  | 1.78  |       |

| С                   | 0.20 | 0.25  | 0.36  |       |

| D                   | 9.02 | 9.27  | 10.16 |       |

| E                   | 7.62 | 7.87  | 8.26  |       |

| E1                  | 6.10 | 6.35  | 7.11  |       |

| е                   |      | 2.54  |       |       |

| eA                  |      | 7.62  |       |       |

| eB                  |      |       | 10.92 |       |

| L                   | 2.92 | 3.30  | 3.81  |       |

| M <sup>(1)(2)</sup> |      | 2.508 |       | 6 - 8 |

| N                   | 0.40 | 0.50  | 0.60  |       |

| N1                  |      |       | 0.60  |       |

| O <sup>(2)(3)</sup> |      | 0.548 |       | 7 - 8 |

#### Notes:

#### General package performance

- The leads size is comprehensive of the thickness of the leads finishing material.

- Dimensions do not include mold protrusion, not to exceed 0,25 mm in total (both side).

- Package outline exclusive of metal burrs dimensions.

- Datum plane "H" coincident with the bottom of lead, where lead exits body.

- Ref. POA MOTHER doc. 0037880.

$<sup>^{(1)}</sup>$  Creepage distance > 800 V.

$<sup>^{\</sup>left(2\right)}$  Creepage distance as shown in the 664-1 CEI / IEC standard.

<sup>(3)</sup> Creepage distance 250 V.

Ordering information VIPER06

# 18 Ordering information

Table 10: Order codes

| Order code  | Package | Packing       |

|-------------|---------|---------------|

| VIPER06XN   |         |               |

| VIPER06LN   | DIP-7   | Tube          |

| VIPER06HN   |         |               |

| VIPER06XS   |         | Tube          |

| VIPER06XSTR |         | Tape and reel |

| VIPER06LS   | SSO10   | Tube          |

| VIPER06LSTR | 33010   | Tape and reel |

| VIPER06HS   |         | Tube          |

| VIPER06HSTR |         | Tape and reel |

VIPER06 Revision history

# 19 Revision history

Table 11: Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                 |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08-Mar-2012 | 1        | Initial release.                                                                                                                                                                                                                        |

| 01-Feb-2017 | 2        | Modified title in cover page.  Updated Section 4: "Electrical data", Section 4.2: "Thermal data" and Section 4.3: "Electrical characteristics".  Added Section 16: "Layout guidelines and design recommendations".  Minor text changes. |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved

单击下面可查看定价,库存,交付和生命周期等信息

>>STMicroelectronics(意法半导体)