Now

ADS8578S SBAS825-APRIL 2017

# ADS8578S 14-Bit, High-Speed, 8-Channel, Simultaneous-Sampling ADC with **Bipolar Inputs on a Single Supply**

#### Features 1

- 14-Bit ADC With Integrated Analog Front-End

- Simultaneous Sampling: 8 Channels

- Pin-Programmable Bipolar Inputs: ±10 V and ±5 V

- High Input Impedance: 1 MΩ

- 5-V Analog Supply: 2.3-V to 5-V Digital Supply

- Overvoltage Input Clamp With 7-kV ESD

- Low-Drift, On-Chip Reference (2.5 V) and Buffer

- **Excellent Performance:**

- 200-kSPS Max Throughput per Channels

- DNL: ±0.2 LSB; INL: ±0.2 LSB

- SNR: 85.8 dB; THD: -109 dB

- Overtemperature Performance:

- Max Offset Drift: 3 ppm/°C

- Gain Drift: 6 ppm/°C

- On-Chip Digital Filter for Oversampling

- Flexible Parallel, Byte, and Serial Interface

- Temperature Range: -40°C to +125°C

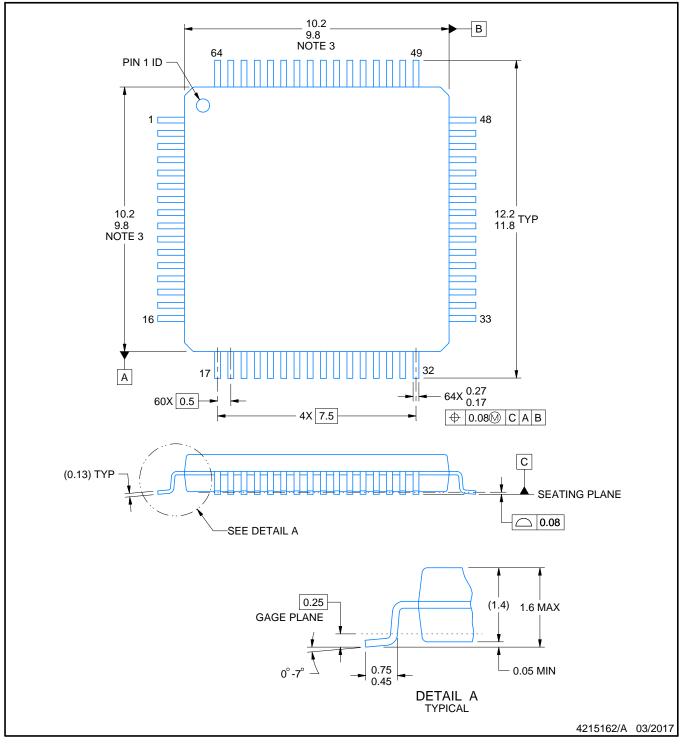

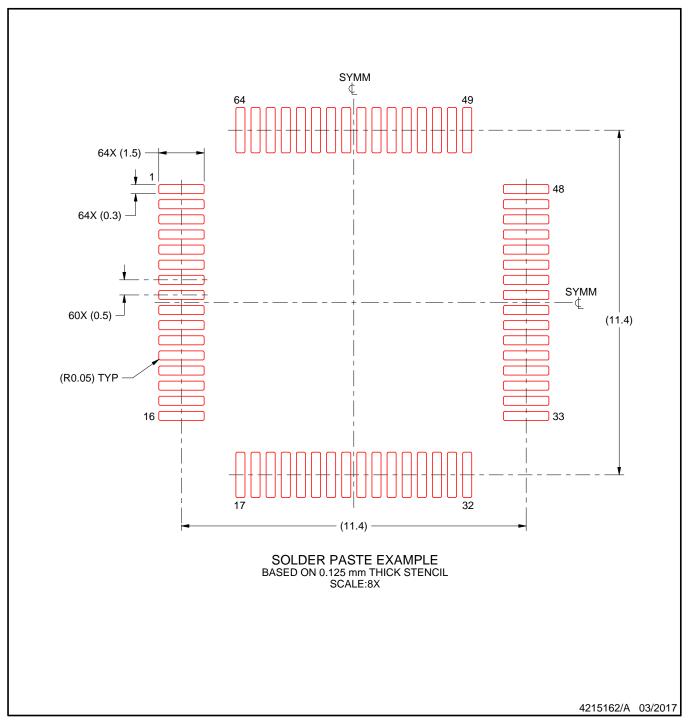

- Package: 64-Pin LQFP

#### Applications 2

- Monitoring and Control for Power Grids

- **Protection Relays**

- **Multiphase Motor Controls**

- Industrial Automation and Controls

- Multichannel Data Acquisition Systems

# 3 Description

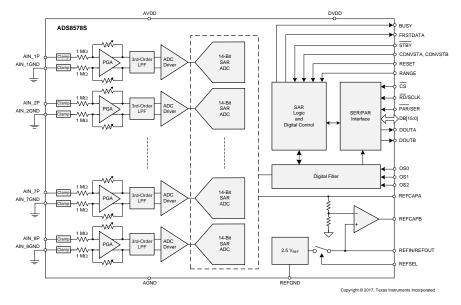

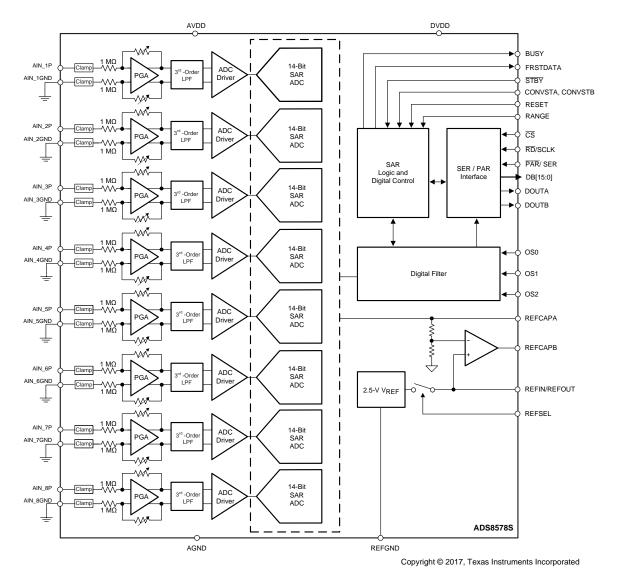

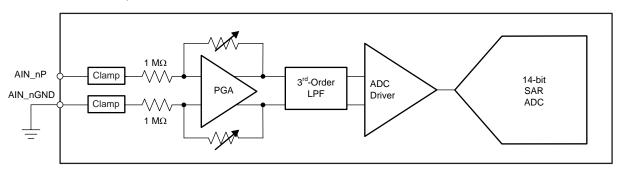

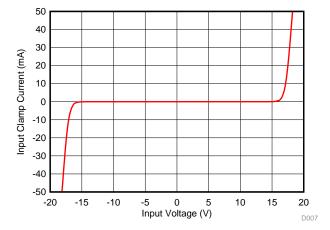

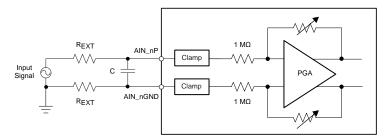

The ADS8578S device is an 8-channel, integrated data acquisition (DAQ) system based on a 14-bit successive approximation (SAR) analog-to-digital (ADC). All input channels converter are simultaneously sampled to achieve a maximum throughput of 200 kSPS per channel. The device features a complete analog front-end for each channel, including a programmable gain amplifier (PGA) with high input impedance of 1 M $\Omega$ , input clamp, low-pass filter, and an ADC input driver. The device also features a low-drift, precision reference with a buffer to drive the ADC. A flexible digital interface supporting serial, parallel, and parallel byte communication enables the device to be used with a variety of host controllers.

The ADS8578S can be configured to accept ±10-V or ±5-V true bipolar inputs using a single 5-V supply. The high input impedance allows direct connection with sensors and transformers, thus eliminating the need for external driver circuits. The high performance and accuracy, along with zero-latency conversions offered by this device, also make the ADS8578S a great choice for many industrial automation and control applications.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)     |  |  |  |  |  |

|-------------|-----------|---------------------|--|--|--|--|--|

| ADS8578S    | LQFP (64) | 10.00 mm × 10.00 mm |  |  |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimore PPOPLICTION DATA

# **Table of Contents**

| 1 | Features 1                                                                                             |

|---|--------------------------------------------------------------------------------------------------------|

| 2 | Applications 1                                                                                         |

| 3 | Description 1                                                                                          |

| 4 | Revision History 2                                                                                     |

| 5 | Device Family Comparison Table 3                                                                       |

| 6 | Pin Configuration and Functions 3                                                                      |

| 7 | Specifications                                                                                         |

|   | 7.1 Absolute Maximum Ratings 5                                                                         |

|   | 7.2 ESD Ratings 6                                                                                      |

|   | 7.3 Recommended Operating Conditions                                                                   |

|   | 7.4 Thermal Information                                                                                |

|   | 7.5 Electrical Characteristics                                                                         |

|   | 7.6 Timing Requirements: CONVST Control 10                                                             |

|   | 7.7 Timing Requirements: Data Read Operation 10                                                        |

|   | 7.8 <u>Timing Requirements:</u> Parallel Data Read Operation,<br><u>CS</u> and <u>RD</u> Tied Together |

|   | 7.9 <u>Timing Requirements: Parallel Data Read Operation,</u><br><u>CS</u> and <u>RD</u> Separate      |

|   | 7.10 Timing Requirements: Serial Data Read<br>Operation                                                |

|   | 7.11 Timing Requirements: Byte Mode Data Read<br>Operation                                             |

|   | 7.12 Timing Requirements: Oversampling Mode 11                                                         |

|   | 7.13 Timing Requirements: Exit Standby Mode 11                                                         |

|   | 7.14 Timing Requirements: Exit Shutdown Mode 12                                                        |

|   | 7.15 Switching Characteristics: CONVST Control 12                                                      |

|   | 7.16 Switching Characteristics: Parallel Data Read                                                     |

|   | Operation, CS and RD Tied Together                                                                     |

|    |      | Switching Characteristics: Parallel Data Read<br>Operation, CS and RD Separate | 13 |

|----|------|--------------------------------------------------------------------------------|----|

|    | 7.18 |                                                                                |    |

|    |      | Operation                                                                      | 14 |

|    |      | Switching Characteristics: Byte Mode Data Read                                 |    |

|    |      | Operation                                                                      |    |

| _  |      | Typical Characteristics                                                        |    |

| 8  |      | iled Description                                                               |    |

|    | 8.1  | Overview                                                                       |    |

|    | 8.2  | Functional Block Diagram                                                       |    |

|    | 8.3  | Feature Description                                                            |    |

|    | 8.4  | Device Functional Modes                                                        | 34 |

| 9  | Арр  | lication and Implementation                                                    | 47 |

|    | 9.1  | Application Information                                                        | 47 |

|    | 9.2  | Typical Application                                                            | 47 |

| 10 | Pow  | ver Supply Recommendations                                                     | 50 |

| 11 | Lay  | out                                                                            | 51 |

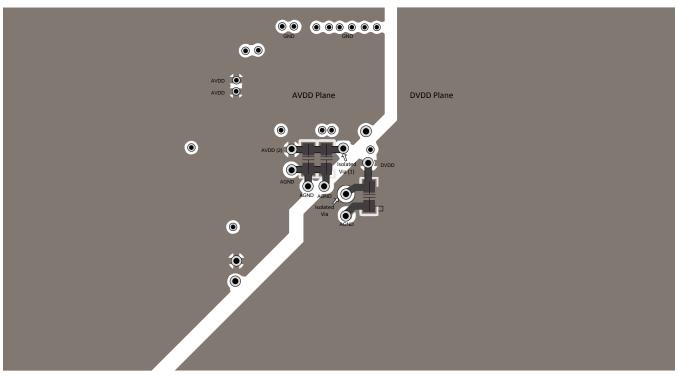

|    | 11.1 | Layout Guidelines                                                              | 51 |

|    | 11.2 | Layout Example                                                                 | 51 |

| 12 | Dev  | ice and Documentation Support                                                  | 53 |

|    | 12.1 | Documentation Support                                                          | 53 |

|    | 12.2 | Receiving Notification of Documentation Updates                                | 53 |

|    | 12.3 | Community Resources                                                            | 53 |

|    | 12.4 | Trademarks                                                                     | 53 |

|    | 12.5 | Electrostatic Discharge Caution                                                | 53 |

|    | 12.6 |                                                                                |    |

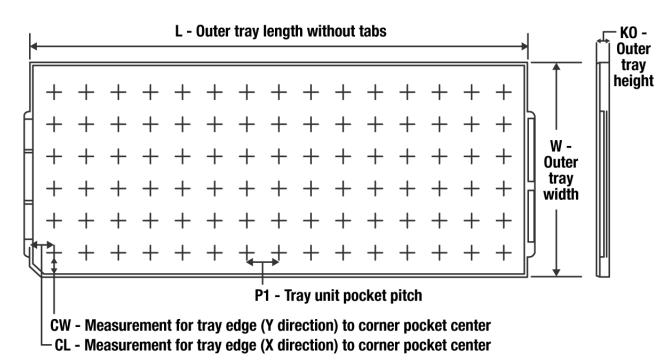

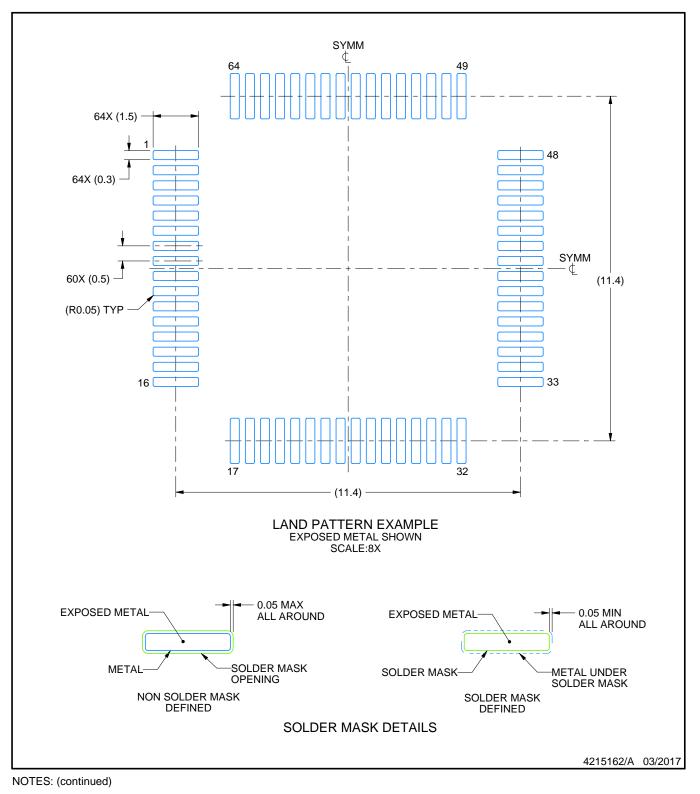

| 13 | Mec  | hanical, Packaging, and Orderable                                              |    |

| -  |      | rmation                                                                        | 53 |

|    |      |                                                                                |    |

# 4 Revision History

| DATE       | REVISION | NOTES            |

|------------|----------|------------------|

| April 2017 | *        | Initial release. |

Copyright © 2017, Texas Instruments Incorporated

# 5 Device Family Comparison Table

| PRODUCT  | RESOLUTION (Bits) | CHANNELS        | SAMPLE RATE (kSPS) |

|----------|-------------------|-----------------|--------------------|

| ADS8578S | 14                | 8, single-ended | 200                |

| ADS8588S | 16                | 8, single-ended | 200                |

| ADS8586S | 16                | 6, single-ended | 250                |

| ADS8584S | 16                | 4, single-ended | 330                |

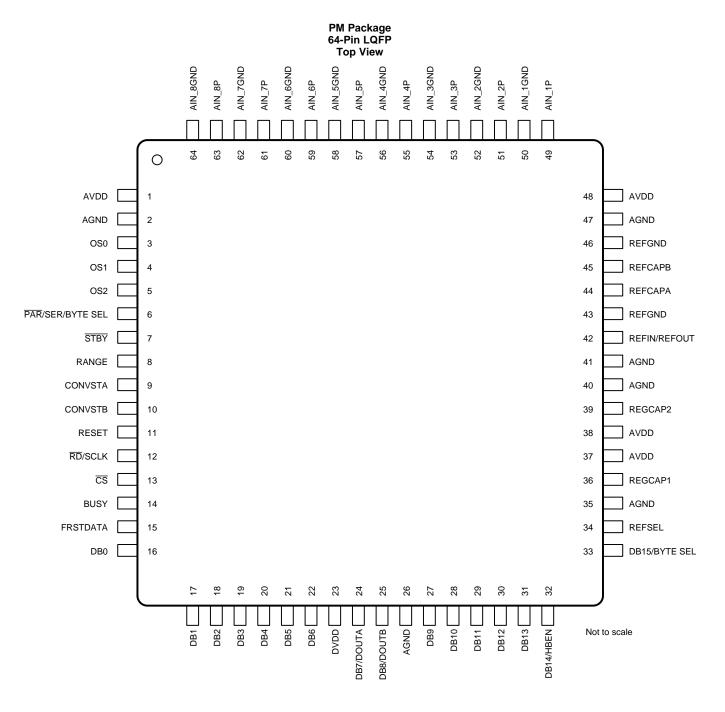

# 6 Pin Configuration and Functions

(1) AI = analog input; AO = analog output; AIO = analog input/output; DI = digital input; DO = digital output; DIO = digital input/output; P = power supply; and NC = no connect.

| AIN_1GND  | 50            | AI  | Al Analog input channel 1: negative input                                                                                                                                                                                                                |  |  |

|-----------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AIN_1P    | 49            | AI  | Analog input channel 1: positive input                                                                                                                                                                                                                   |  |  |

| AIN_2GND  | 52            | AI  | Analog input channel 2: negative input                                                                                                                                                                                                                   |  |  |

| AIN_2P    | 51            | AI  | Analog input channel 2: positive input                                                                                                                                                                                                                   |  |  |

| AIN_3GND  | 54            | AI  | Analog input channel 3: negative input                                                                                                                                                                                                                   |  |  |

| AIN_3P    | 53            | AI  | Analog input channel 3: positive input                                                                                                                                                                                                                   |  |  |

| AIN_4GND  | 56            | AI  | Analog input channel 4: negative input                                                                                                                                                                                                                   |  |  |

| AIN_4P    | 55            | AI  | Analog input channel 4: positive input                                                                                                                                                                                                                   |  |  |

| AIN_5GND  | 58            | AI  | Analog input channel 5: negative input                                                                                                                                                                                                                   |  |  |

| AIN_5P    | 57            | AI  | Analog input channel 5: positive input                                                                                                                                                                                                                   |  |  |

| AIN_6GND  | 60            | AI  | Analog input channel 6: negative input                                                                                                                                                                                                                   |  |  |

| AIN_6P    | 59            | AI  | Analog input channel 6: positive input                                                                                                                                                                                                                   |  |  |

| AIN_7GND  | 62            | AI  | Analog input channel 7: negative input                                                                                                                                                                                                                   |  |  |

| AIN_7P    | 61            | AI  | Analog input channel 7: positive input                                                                                                                                                                                                                   |  |  |

| AIN_8GND  | 64            | AI  | Analog input channel 8: negative input                                                                                                                                                                                                                   |  |  |

| AIN_8P    | 63            | AI  | Analog input channel 8: positive input                                                                                                                                                                                                                   |  |  |

| AVDD      | 1, 37, 38, 48 | Р   | Analog supply pins. Decouple these pins to the closest AGND pins (see the <i>Power Supply Recommendations</i> section).                                                                                                                                  |  |  |

| BUSY      | 14            | DO  | Active high digital output indicating an ongoing conversion (see the <i>BUSY</i> ( <i>Output</i> ) section)                                                                                                                                              |  |  |

| CONVSTA   | 9             | DI  | Active high logic input to control start of conversion for first half count of device input channels (see the CONVSTA, CONVSTB (Input) section)                                                                                                          |  |  |

| CONVSTB   | 10            | DI  | Active high logic input to control start of conversion for second half count of device input channels (see the <i>CONVSTA, CONVSTB (Input)</i> section)                                                                                                  |  |  |

| CS        | 13            | DI  | Active low logic input chip-select signal (see the CS (Input) section)                                                                                                                                                                                   |  |  |

| DB0       | 16            | DO  | DB0 is driven low in parallel interface mode; in parallel byte interface mode, DB0 is ADC data output bit 6 and is driven low (see the <i>DB[6:0]</i> section)                                                                                           |  |  |

| DB1       | 17            | DO  | Driven low in parallel interface mode; in parallel byte interface mode, DB1 is ADC data output bit 7 and is driven low (see the <i>DB[6:0]</i> section)                                                                                                  |  |  |

| DB2       | 18            | DO  | ADC data output bit 0 in parallel interface mode; in parallel byte interface mode, DB2 is ADC data output bits 8 and 0 and is driven low (see the <i>DB[6:0]</i> section)                                                                                |  |  |

| DB3       | 19            | DO  | ADC data output bit 1 in parallel interface mode; in parallel byte interface mode, DB3 is ADC data output bits 9 and 1 and is driven low (see the <i>DB[6:0]</i> section)                                                                                |  |  |

| DB4       | 20            | DO  | ADC data output bit 2 in parallel interface mode; in parallel byte interface mode, DB4 is ADC data output bits 10 and 2 and is driven low (see the <i>DB[6:0]</i> section)                                                                               |  |  |

| DB5       | 21            | DO  | ADC data output bit 3 in parallel interface mode; in parallel byte interface mode, DB5 is ADC data output bits 11 and 3 and is driven low (see the <i>DB[6:0]</i> section)                                                                               |  |  |

| DB6       | 22            | DO  | ADC data output bit 4 in parallel interface mode; in parallel byte interface mode, DB6 is ADC data output bits 12 and 4 and is driven low (see the <i>DB[6:0]</i> section)                                                                               |  |  |

| DB7/DOUTA | 24            | DO  | Multifunction logic output pin (see the <i>DB7/DOUTA</i> section):<br>this pin is ADC data output bit 5 in parallel interface mode, ADC data output bits 13 and 5 in<br>parallel byte interface mode, and is a data output pin in serial interface mode. |  |  |

| DB8/DOUTB | 25            | DO  | Multifunction logic output pin (see the <i>DB8/DOUTB</i> section):<br>this pin is ADC data output bit 6 in parallel interface mode and is a data output pin in serial<br>interface mode.                                                                 |  |  |

| DB9       | 27            | DO  | ADC data output bit 7 in parallel interface mode (see the DB[13:9] section)                                                                                                                                                                              |  |  |

| DB10      | 28            | DO  | ADC data output bit 8 in parallel interface mode (see the DB[13:9] section)                                                                                                                                                                              |  |  |

| DB11      | 29            | DO  | ADC data output bit 9 in parallel interface mode (see the DB[13:9] section)                                                                                                                                                                              |  |  |

| DB12      | 30            | DO  | ADC data output bit 10 in parallel interface mode (see the DB[13:9] section)                                                                                                                                                                             |  |  |

| DB13      | 31            | DO  | ADC data output bit 11 in parallel interface mode (see the <i>DB[13:9]</i> section)                                                                                                                                                                      |  |  |

| DB14/HBEN | 32            | DIO | Multifunction logic input or output pin (see the <i>DB14/HBEN</i> section):<br>this pin is ADC data output bit 12 in parallel interface mode, and is a control input pin for byte<br>selection (high or low) in parallel byte interface mode.            |  |  |

**Pin Functions**

DESCRIPTION

Analog ground pins

TYPE<sup>(1)</sup>

Ρ

NO. 2, 26, 35, 40, 41, 47

### SBAS825-APRIL 2017

NAME

AGND

Copyright © 2017, Texas Instruments Incorporated

### **Pin Functions (continued)**

| NAME             | NO.    | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                        |

|------------------|--------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DB15/BYTE SEL    | 33     | DIO                 | Multifunction logic input or output pin (see the <i>DB15/BYTE SEL</i> section): this pin is ADC data output bit 13 (MSB) in parallel interface mode, and is an active high control input pin to enable parallel byte interface mode.                               |

| DVDD             | 23     | Р                   | Digital supply pin; decouple with AGND on pin 26                                                                                                                                                                                                                   |

| FRSTDATA         | 15     | DO                  | Active high digital output indicating data read back from channel 1 of the device (see the<br>FRSTDATA (Output) section)                                                                                                                                           |

| OS0              | 3      | DI                  | Oversampling mode control pin (see the Oversampling Mode of Operation section)                                                                                                                                                                                     |

| OS1              | 4      | DI                  | Oversampling mode control pin (see the Oversampling Mode of Operation section)                                                                                                                                                                                     |

| OS2              | 5      | DI                  | Oversampling mode control pin (see the Oversampling Mode of Operation section)                                                                                                                                                                                     |

| PAR/SER/BYTE SEL | 6      | DI                  | Logic input pin to select between parallel, serial, or parallel byte interface mode (see the <i>Data Read Operation</i> section)                                                                                                                                   |

| RANGE            | 8      | DI                  | Multifunction logic input pin (see the <i>RANGE (Input</i> ) section):<br>when the STBY pin is high, this pin selects the input range of the device ( $\pm 10$ V or $\pm 5$ V); when the STBY pin is low, this pin selects between the standby and shutdown modes. |

| RD/SCLK          | 12     | DI                  | Multifunction logic input pin (see the <i>RD/SCLK (Input)</i> section): this pin is an active-low ready input pin in parallel and parallel byte interface, and is a clock input pin in serial interface mode.                                                      |

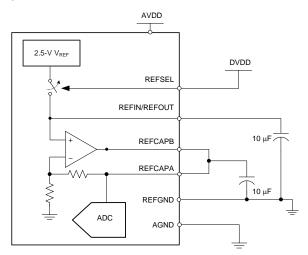

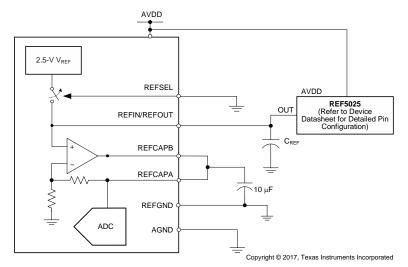

| REFCAPA          | 44     | AO                  | Reference amplifier output pin. This pin must be shorted to REFCAPB and decoupled to AGND using a low equivalent series resistance (ESR), 10-µF ceramic capacitor.                                                                                                 |

| REFCAPB          | 45     | AO                  | Reference amplifier output pin. This pin must be shorted to REFCAPA and decoupled to AGND using a low ESR, 10-µF ceramic capacitor.                                                                                                                                |

| REFGND           | 43, 46 | Р                   | Reference GND pin. This pin must be shorted to the analog GND plane and decoupled with REFIN/REFOUT on pin 42 using a $10-\mu$ F capacitor.                                                                                                                        |

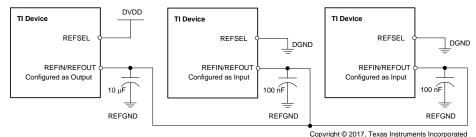

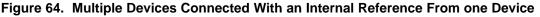

| REFIN/REFOUT     | 42     | AIO                 | This pin acts as an internal reference output when REFSEL is high;<br>this pin functions as input pin for the external reference when REFSEL is low; decouple with<br>REFGND on pin 43 using a 10-µF capacitor.                                                    |

| REFSEL           | 34     | DI                  | Active high logic input to enable the internal reference (see the REFSEL (Input) section)                                                                                                                                                                          |

| REGCAP1          | 36     | AO                  | Output pin 1 for the internal voltage regulator; decouple separately to AGND using a 1-µF capacitor                                                                                                                                                                |

| REGCAP2          | 39     | AO                  | Output pin 2 for the internal voltage regulator; decouple separately to AGND using a 1-µF capacitor                                                                                                                                                                |

| RESET            | 11     | DI                  | Active high logic input to reset the device digital logic (see the RESET (Input) section)                                                                                                                                                                          |

| STBY             | 7      | DI                  | Active low logic input to enter the device into one of the two power-down modes: standby or shutdown (see the <i>Power-Down Modes</i> section)                                                                                                                     |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

at  $T_A = 25^{\circ}C$  (unless otherwise noted)<sup>(1)</sup>

|                                             |                            |  | MIN  | MAX        | UNIT |

|---------------------------------------------|----------------------------|--|------|------------|------|

| AVDD to AGND                                | DD to AGND                 |  | -0.3 | 7.0        | V    |

| DVDD to AGND                                |                            |  | -0.3 | 7.0        | V    |

| Analog input voltage to AGND <sup>(2)</sup> |                            |  | -15  | 15         | V    |

| Digital input to AGND                       |                            |  | -0.3 | DVDD + 0.3 | V    |

| REFIN to AGND                               |                            |  | -0.3 | AVDD + 0.3 | V    |

| Input current to any pin except             | ot supplies <sup>(2)</sup> |  | -10  | 10         | mA   |

| Temperature                                 | Operating                  |  | -40  | 125        |      |

|                                             | Junction, T <sub>J</sub>   |  |      | 150        | °C   |

|                                             | Storage, T <sub>stg</sub>  |  | -65  | 150        |      |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Transient currents of up to 100 mA do not cause SCR latch-up.

XAS STRUMENTS

www.ti.com

# 7.2 ESD Ratings

|                                            |                                                                                |                               | VALUE | UNIT |  |

|--------------------------------------------|--------------------------------------------------------------------------------|-------------------------------|-------|------|--|

|                                            | Human-body model (HBM), per                                                    | All pins except analog inputs | ±2000 |      |  |

| V <sub>(ESD)</sub> Electrostatic discharge | ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                                          | Analog input pins only        | ±7000 | V    |  |

|                                            | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | All pins                      | ±500  | , v  |  |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (1)

(2)

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|      |                        | MIN  | NOM | MAX  | UNIT |

|------|------------------------|------|-----|------|------|

| AVDD | Analog supply voltage  | 4.75 | 5   | 5.25 | V    |

| DVDD | Digital supply voltage | 2.3  | 3.3 | AVDD | V    |

### 7.4 Thermal Information

|                       |                                              | ADS8578S  |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PM (LQFP) | UNIT |

|                       |                                              | 64 PINS   |      |

| $R_{	hetaJA}$         | Junction-to-ambient thermal resistance       | 46.0      | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 7.8       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 20.1      | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.3       | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 19.6      | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 7.5 Electrical Characteristics

minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +125°C, AVDD = 4.75 V to 5.25 V; typical specifications are at  $T_A = 25^{\circ}$ C; AVDD = 5 V, DVDD = 3 V,  $V_{REF} = 2.5$  V (internal), and  $f_{SAMPLE} = 200$  kSPS (unless otherwise noted)

|                      | PARAMETER                                              | TEST CO                                 | NDITIONS                            | MIN              | ТҮР                                 | МАХ  | UNIT               | TEST<br>LEVEL <sup>(1)</sup> |

|----------------------|--------------------------------------------------------|-----------------------------------------|-------------------------------------|------------------|-------------------------------------|------|--------------------|------------------------------|

| ANALOG INP           | UTS                                                    | 1                                       |                                     | J                |                                     |      |                    |                              |

|                      | Full-scale input span <sup>(2)</sup>                   | RANGE pin = 1                           |                                     | -10              |                                     | 10   |                    | А                            |

|                      | (AIN_nP to AIN_nGND)                                   | RANGE pin = 0                           |                                     | -5               |                                     | 5    | V                  | А                            |

|                      | Operating input range,                                 | RANGE pin = 1                           |                                     | -10              |                                     | 10   | V                  | А                            |

| AIN_nP               | positive input                                         | RANGE pin = 0                           | RANGE pin = 0                       |                  |                                     | 5    | v                  | А                            |

| AIN_ <i>n</i> GND    | Operating input range, negative input                  | All input ranges                        |                                     | -0.3             | 0                                   | 0.3  | V                  | В                            |

| R <sub>IN</sub>      | Input impedance                                        | At $T_A = 25^{\circ}C$                  |                                     | 0.85             | 1                                   | 1.15 | MΩ                 | В                            |

|                      | Input impedance drift                                  | All input ranges                        |                                     | -25              | ±7                                  | 25   | ppm/°C             | В                            |

| I <sub>lkg(in)</sub> | Input leakage current                                  | With voltage at A all input ranges      | $AIN_nP = V_{IN},$                  | (V <sub>IN</sub> | <sub>I</sub> – 2) / R <sub>IN</sub> |      | μΑ                 | A                            |

| SYSTEM PER           | FORMANCE                                               |                                         |                                     |                  |                                     |      |                    |                              |

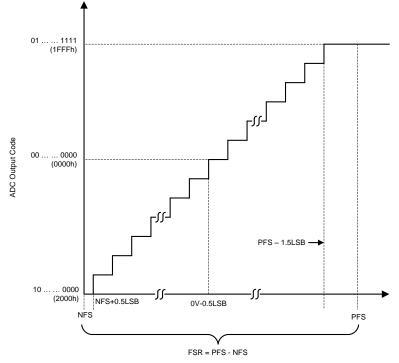

|                      | Resolution                                             |                                         |                                     | 14               |                                     |      | Bits               | А                            |

| NMC                  | No missing codes                                       |                                         |                                     | 14               |                                     |      | Bits               | А                            |

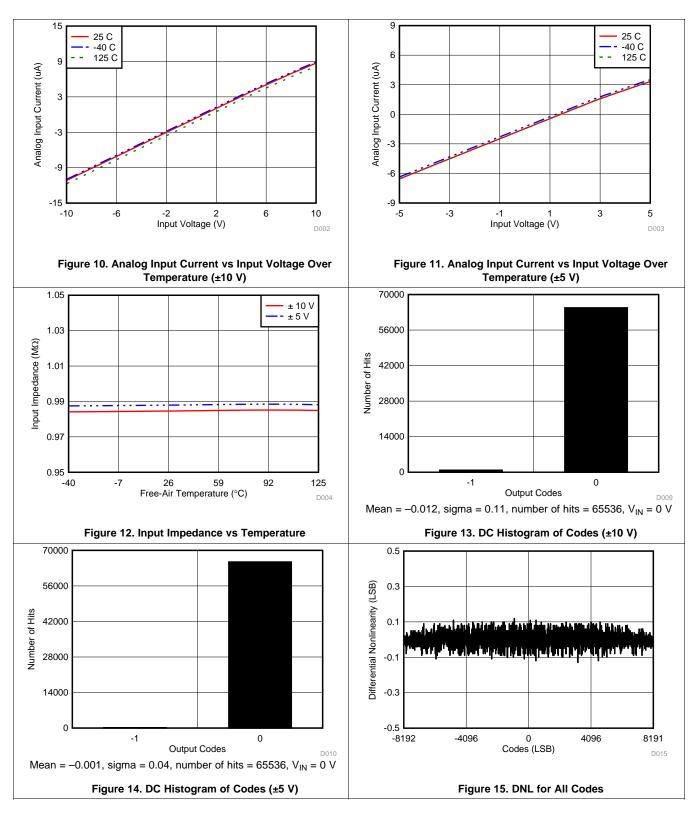

| DNL                  | Differential nonlinearity                              | All input ranges                        |                                     | -0.5             | ±0.2                                | 0.5  | LSB <sup>(3)</sup> | А                            |

| INL                  | Integral nonlinearity <sup>(4)</sup>                   | All input ranges                        |                                     | -0.45            | ±0.2                                | 0.45 | LSB                | А                            |

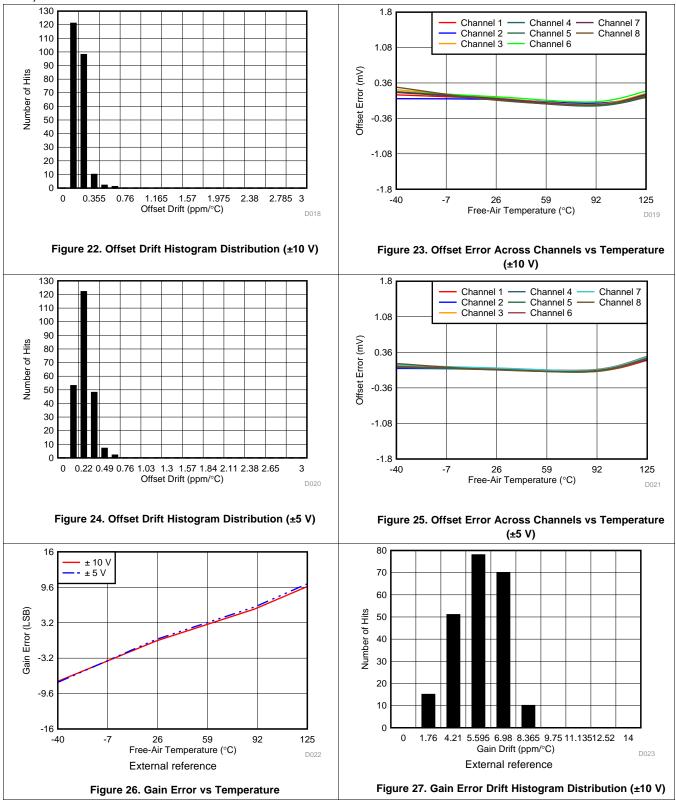

|                      |                                                        | All input<br>ranges,                    | $T_A = -40^{\circ}C$ to<br>+85°C    | -16              | ±1                                  | 16   | _                  | А                            |

| E <sub>G</sub>       | Gain error <sup>(5)</sup>                              | external<br>reference                   | T <sub>A</sub> = −40°C to<br>+125°C | -16              | ±1                                  | 24   |                    | А                            |

|                      |                                                        | All input ranges, internal reference    |                                     |                  | ±0.3                                |      |                    | А                            |

|                      | Gain error matching                                    | Input range = ±1<br>external and inte   |                                     |                  | 2                                   | 15   | 1.00               | А                            |

|                      | (channel-to-channel)                                   | Input range = ±5<br>external and inte   |                                     |                  | 2.5                                 | 15   | LSB                | А                            |

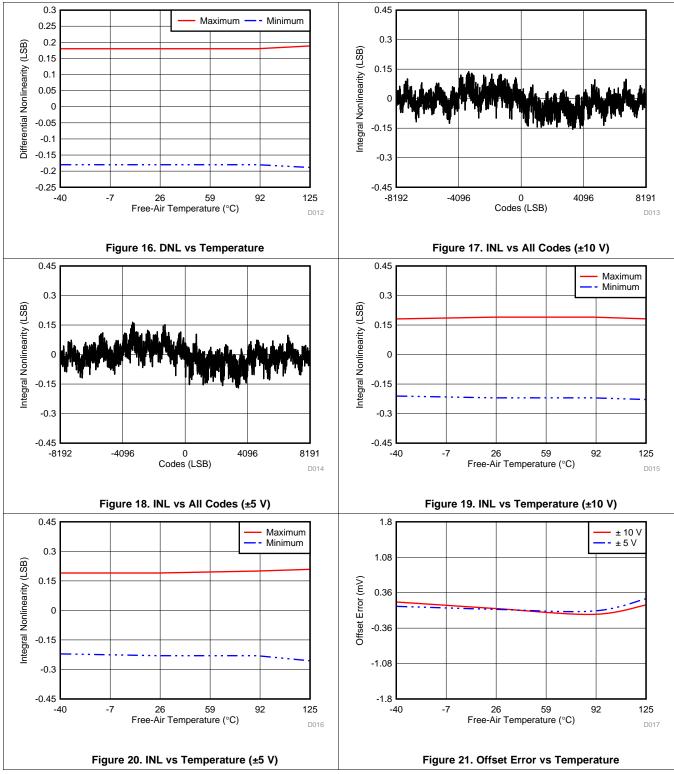

|                      |                                                        | All input ranges,<br>external reference |                                     | -14              | ±6                                  | 14   | ppm/°C             | В                            |

|                      | Gain error temperature drift                           | All input ranges, internal reference    | e                                   |                  | ±10                                 |      | ppin/ C            | В                            |

| -                    | Offset error                                           | Input range = ±1                        | 0 V                                 | -1.8             | ±0.15                               | 1.8  | mV                 | В                            |

| Eo                   | Onset end                                              | Input range = ±5                        | 5 V                                 | -1.8             | ±0.15                               | 1.8  | mv                 | В                            |

|                      | Offset error matching<br>(channel-to-channel)          | All input ranges                        |                                     |                  | 0.3                                 | 2.4  | mV                 | В                            |

|                      | Offset error temperature drift                         | All input ranges                        |                                     | -3               | ±0.3                                | 3    | ppm/°C             | В                            |

| SAMPLING D           | YNAMICS                                                |                                         |                                     |                  |                                     |      |                    |                              |

| t <sub>ACQ</sub>     | Acquisition time                                       |                                         |                                     | 1                |                                     |      | μs                 | А                            |

| f <sub>S</sub>       | Maximum throughput rate per channel<br>without latency | All eight channe                        | ls included                         |                  |                                     | 200  | kSPS               | А                            |

(1) Test Levels: (A) Tested at final test. Overtemperature limits are set by characterization and simulation. (B) Limits set by characterization and simulation, across temperature range. (C) Typical value only for information, provided by design simulation.

(2) Ideal input span, does not include gain or offset error.

(3) LSB = least significant bit.

(4) This parameter is the endpoint INL, not best-fit INL.

(5) Gain error is calculated after adjusting for offset error, which implies that positive full scale error = negative full scale error = gain error ÷ 2.

### **Electrical Characteristics (continued)**

minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +125°C, AVDD = 4.75 V to 5.25 V; typical specifications are at  $T_A = 25^{\circ}$ C; AVDD = 5 V, DVDD = 3 V,  $V_{REF} = 2.5$  V (internal), and  $f_{SAMPLE} = 200$  kSPS (unless otherwise noted)

|                                 | PARAMETER                                                 |                 | TEST CONDITIONS                                                                                                        | MIN    | ТҮР  | МАХ    | UNIT   | TEST<br>LEVEL <sup>(1)</sup> |   |

|---------------------------------|-----------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------|--------|------|--------|--------|------------------------------|---|

| DYNAMIC CHA                     | RACTERISTICS                                              |                 |                                                                                                                        |        |      |        |        |                              |   |

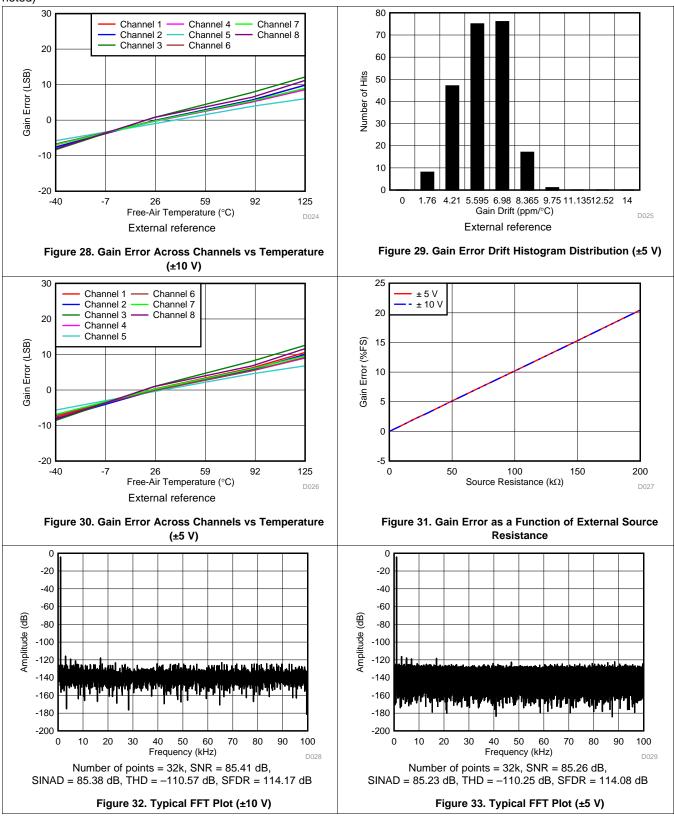

|                                 | Signal-to-noise ratio,                                    |                 | Input range = ±10 V                                                                                                    | 84.5   | 85.7 |        |        | А                            |   |

| SNR                             | no oversampling<br>(V <sub>IN</sub> – 0.5 dBFS at 1       | kHz)            | Input range = ±5 V                                                                                                     | 84.2   | 85.6 |        | dB     | А                            |   |

|                                 | Signal-to-noise ratio,                                    |                 | Input range = ±10 V                                                                                                    | 85.5   | 85.8 |        |        | А                            |   |

| SNR <sub>OSR</sub>              | oversampling = $4x$<br>(V <sub>IN</sub> - 0.5 dBFS at 13  | 80 Hz)          | Input range = ±5 V                                                                                                     | 85.2   | 85.6 |        | dB     | А                            |   |

| THD                             | Total harmonic distor<br>(V <sub>IN</sub> – 0.5 dBFS at 1 |                 | All input ranges                                                                                                       |        | -109 | -95    | dB     | В                            |   |

| 0.0.4.5                         | Signal-to-noise + dist                                    | ortion ratio,   | Input range = ±10 V                                                                                                    | 84.5   | 85.4 |        | 9      | A                            |   |

| SINAD                           | no oversampling<br>(V <sub>IN</sub> – 0.5 dBFS at 1       | kHz)            | Input range = ±5 V                                                                                                     | 84.3   | 85.3 |        | dB     | А                            |   |

|                                 | Signal-to-noise + dist                                    | ortion ratio,   | Input range = ±10 V                                                                                                    | 85.4   | 85.5 |        |        | А                            |   |

| SINAD <sub>OSR</sub>            | oversampling = 4x<br>(V <sub>IN</sub> – 0.5 dBFS at 13    | 80 Hz)          | Input range = ±5 V                                                                                                     | 85.2   | 85.4 |        | dB     | А                            |   |

| SFDR                            | Spurious-free dynam (V <sub>IN</sub> – 0.5 dBFS at 1      |                 | All input ranges                                                                                                       |        | -111 |        | dB     | В                            |   |

|                                 | Crosstalk isolation <sup>(7)</sup>                        |                 |                                                                                                                        |        | -95  |        | dB     | А                            |   |

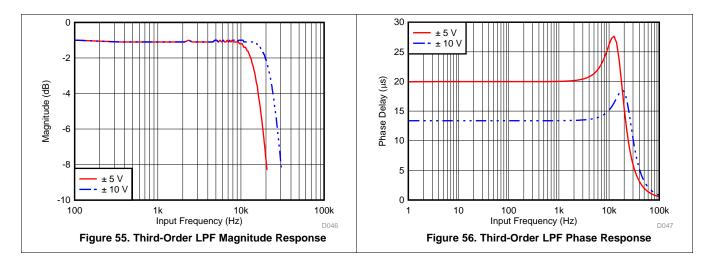

| BW/                             |                                                           | –3 dB           | At $T_A = 25^{\circ}C$ ,<br>input range = ±10 V                                                                        |        | 24   |        | kHz    | В                            |   |

| BW <sub>(-3 dB)</sub>           | Small-signal                                              | -5 0.5          | At $T_A = 25^{\circ}C$ ,<br>input range = $\pm 5 \text{ V}$                                                            |        | 16   |        | KIIZ   | В                            |   |

| BW                              | bandwidth                                                 | –0.1 dB         | At $T_A = 25^{\circ}C$ ,<br>input range = ±10 V                                                                        |        | 14   |        | – kHz  | kH7                          | В |

| BW <sub>(-0.1 dB)</sub>         |                                                           | -0.1 05         | At $T_A = 25^{\circ}C$ ,<br>input range = $\pm 5 V$                                                                    |        | 9.5  |        | KIIZ   | В                            |   |

| t <sub>GROUP</sub>              | Group delay                                               |                 | Input range = ±10 V                                                                                                    |        | 13   |        | μs     | С                            |   |

| GROUP                           | Croup dolay                                               |                 | Input range = ±5 V                                                                                                     |        | 19   |        | μο     | С                            |   |

| INTERNAL REF                    | ERENCE OUTPUT (R                                          |                 | 1                                                                                                                      | 1      |      |        |        | 1                            |   |

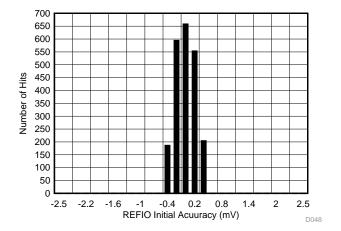

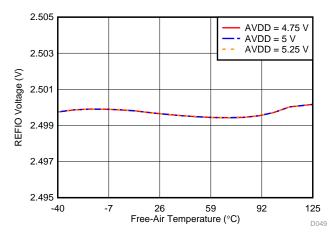

| V <sub>REF</sub> <sup>(8)</sup> | Voltage on the REFIN<br>(configured as output             |                 | At $T_A = 25^{\circ}C$                                                                                                 | 2.4975 | 2.5  | 2.5025 | V      | Α                            |   |

|                                 | Internal reference ter                                    | •               |                                                                                                                        |        | 7.5  |        | ppm/°C | В                            |   |

| $C_{(REFIN\_REFOUT)}$           | Decoupling capacitor<br>REFIN/REFOUT <sup>(9)</sup>       | on              |                                                                                                                        |        | 10   |        | μF     | В                            |   |

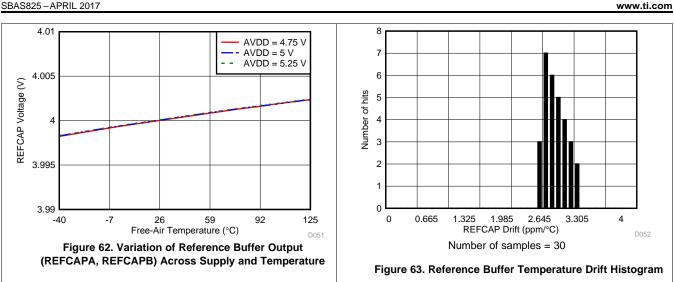

| V <sub>(REFCAP)</sub>           | Reference voltage to<br>(on the REFCAPA, R                |                 | At T <sub>A</sub> = 25°C                                                                                               | 3.996  | 4.0  | 4.004  | V      | А                            |   |

|                                 | Reference buffer out                                      | out impedance   |                                                                                                                        |        | 0.5  | 1      | Ω      | С                            |   |

|                                 | Reference buffer out<br>drift                             | out temperature |                                                                                                                        |        | 5    |        | ppm/°C | В                            |   |

| $C_{(REFCAP)}$                  | Decoupling capacitor<br>REFCAPB                           | on REFCAPA,     |                                                                                                                        |        | 10   |        | μF     | В                            |   |

|                                 | Turn-on time                                              |                 | $\begin{array}{l} C_{(\text{REFCAP})} = 10 \ \mu\text{F}, \\ C_{(\text{REFIN_REFOUT})} = 10 \ \mu\text{F} \end{array}$ |        | 25   |        | ms     | В                            |   |

| EXTERNAL REI                    | FERENCE INPUT (RE                                         | FSEL = 0)       |                                                                                                                        |        |      |        |        |                              |   |

| V <sub>REFIO_EXT</sub>          | External reference vo<br>(configured as input)            | ltage on REFIO  |                                                                                                                        | 2.475  | 2.5  | 2.525  | V      | В                            |   |

|                                 | Reference input impe                                      | edance          |                                                                                                                        |        | 100  |        | MΩ     | С                            |   |

|                                 | Reference input capa                                      | citance         |                                                                                                                        |        | 10   |        | pF     | С                            |   |

(6) Calculated on the first nine harmonics of the input frequency.

(7) Isolation crosstalk is measured by applying a full-scale sinusoidal signal up to 160 kHz to a channel, not selected in the multiplexing sequence, and measuring the effect on the output of any selected channel.

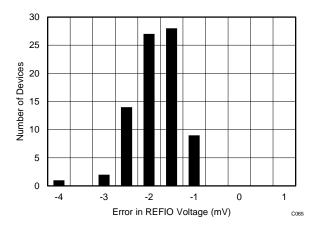

(8) Does not include the variation in voltage resulting from solder shift effects.

(9) Recommended to use an X7R-grade, 0603-size ceramic capacitor for optimum performance (see the Layout Guidelines section).

### **Electrical Characteristics (continued)**

minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +125°C, AVDD = 4.75 V to 5.25 V; typical specifications are at  $T_A = 25^{\circ}$ C; AVDD = 5 V, DVDD = 3 V,  $V_{REF} = 2.5$  V (internal), and  $f_{SAMPLE} = 200$  kSPS (unless otherwise noted)

|                          | PARAMETER                               | TEST CONDITIONS                                                                                          | MIN        | ТҮР  | МАХ                      | UNIT | TEST<br>LEVEL <sup>(1)</sup> |

|--------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------|------------|------|--------------------------|------|------------------------------|

| POWER-SUPP               | LY REQUIREMENTS                         |                                                                                                          |            |      |                          |      |                              |

| AVDD                     | Analog power-supply voltage             | Analog supply                                                                                            | 4.75       | 5    | 5.25                     | V    | А                            |

| DVDD                     | Digital power-supply voltage            | Digital supply range                                                                                     | 2.3        | 3.3  | AVDD                     | V    | А                            |

|                          | Analog supply current                   | For ADS8578S, AVDD = 5 V,<br>$f_S = 200 \text{ kSPS}$ ,<br>internal reference                            |            | 17.7 | 24.0                     | mA   | A                            |

| I <sub>AVDD_DYN</sub>    | (operational)                           | For ADS8578S, AVDD = 5 V,<br>$f_S = 200 \text{ kSPS}$ ,<br>external reference                            |            | 17.1 | 24.0                     | IIIA | A                            |

|                          | Analog supply current                   | For ADS8578S, AVDD = 5 V,<br>internal reference,<br>device not converting                                |            | 12.4 | 17.0                     |      | A                            |

| I <sub>AVDD_STC</sub>    | (static)                                | For ADS8578S, AVDD = 5 V,<br>external reference,<br>device not converting                                |            | 12.0 | 17.0                     | mA   | A                            |

| I                        | AVDD supply                             | At AVDD = 5 V, device in STDBY mode, internal reference                                                  |            | 4.2  | 5.5                      | mA   | А                            |

| I <sub>AVDD_STDBY</sub>  | STANDBY current                         | At AVDD = 5 V, device in STDBY mode, external reference                                                  |            | 3.8  | 5.5                      | ША   | А                            |

| I <sub>AVDD_PWR_DN</sub> | AVDD supply<br>power-down current       | At AVDD = 5 V, device in<br>PWR_DN, internal or external<br>reference,<br>$T_A = -40^{\circ}$ C to +85°C |            | 0.2  | 6                        | μA   | А                            |

| I <sub>DVDD_DYN</sub>    | Digital supply current                  | For ADS8578S,<br>DVDD = 3.3 V,<br>f <sub>S</sub> = 200 kSPS                                              |            | 0.15 | 0.3                      | mA   | A                            |

| IDVDD_STDBY              | DVDD supply STANDBY current             | At AVDD = 5 V, device in STDBY mode                                                                      |            | 0.05 | 1.5                      | μA   | А                            |

| I <sub>DVDD_PWR-DN</sub> | DVDD supply power-down current          | At AVDD = 5 V, device in<br>PWR_DN mode                                                                  |            | 0.05 | 1.5                      | μΑ   | А                            |

| DIGITAL INPU             | TS (CMOS)                               |                                                                                                          |            |      |                          |      |                              |

| V <sub>IH</sub>          | Digital high input voltage logic level  | DVDD > 2.3 V                                                                                             | 0.7 × DVDD |      | DVDD + 0.3               | V    | А                            |

| V <sub>IL</sub>          | Digital low input voltage logic level   | DVDD > 2.3 V                                                                                             | -0.3       |      | $0.3 \times \text{DVDD}$ | V    | А                            |

|                          | Input leakage current                   |                                                                                                          |            | 100  |                          | nA   | Α                            |

|                          | Input pin capacitance                   |                                                                                                          |            | 5    |                          | pF   | А                            |

| DIGITAL OUTF             | PUTS (CMOS)                             | 1                                                                                                        |            |      | I                        |      |                              |

| V <sub>OH</sub>          | Digital high output voltage logic level | I <sub>O</sub> = 100-μA source                                                                           | 0.8 × DVDD |      | DVDD                     | V    | А                            |

| V <sub>OL</sub>          | Digital low output voltage logic level  | I <sub>O</sub> = 100-μA sink                                                                             | 0          |      | 0.2 × DVDD               | V    | А                            |

|                          | Floating state leakage current          | Only for SDO                                                                                             |            | 1    |                          | μA   | А                            |

|                          | Internal pin capacitance                |                                                                                                          |            | 5    |                          | pF   | А                            |

| TEMPERATUR               | ERANGE                                  |                                                                                                          |            |      |                          |      |                              |

| T <sub>A</sub>           | Operating free-air temperature          |                                                                                                          | -40        |      | 125                      | °C   | А                            |

10 Submit Documentation Feedback

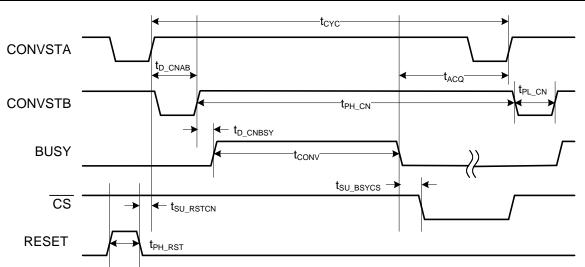

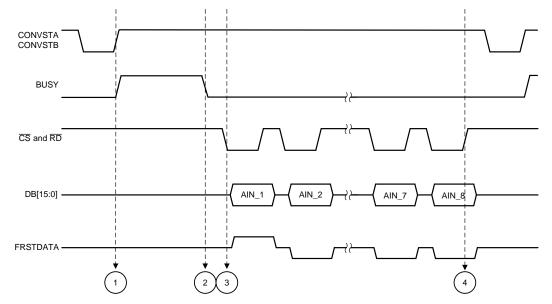

## 7.6 Timing Requirements: CONVST Control

minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +125°C, typical specifications are at  $T_A = 25^{\circ}$ C; AVDD = 5 V, 2.3 V ≤ DVDD ≤ 5.25 V,  $V_{REF} = 2.5$  V (internal), BUSY load = 20 pF,  $V_{IL}$  and  $V_{IH}$  at datasheet limits, and  $f_{SAMPLE} = 200$  kSPS (unless otherwise noted) (see Figure 1)

|                       |                                                                                      | MIN | NOM MAX | UNIT |

|-----------------------|--------------------------------------------------------------------------------------|-----|---------|------|

| t <sub>ACQ</sub>      | Acquisition time:<br>BUSY falling edge to rising edge of trailing CONVSTA or CONVSTB | 1   |         | μs   |

| t <sub>PH_CN</sub>    | CONVSTA, CONVSTB pulse high time                                                     | 25  |         | ns   |

| t <sub>PL_CN</sub>    | CONVSTA, CONVSTB pulse low time                                                      | 25  |         | ns   |

| t <sub>SU_BSYCS</sub> | Setup time: BUSY falling to CS falling                                               | 0   |         | ns   |

| t <sub>SU_RSTCN</sub> | Setup time: RESET falling to first rising edge of CONVSTA or CONVSTB                 | 25  |         | ns   |

| t <sub>PH_RST</sub>   | RESET pulse high time                                                                | 50  |         | ns   |

| t <sub>D_CNAB</sub>   | Delay between rising edges of CONVSTA and CONVSTB                                    |     | 500     | μs   |

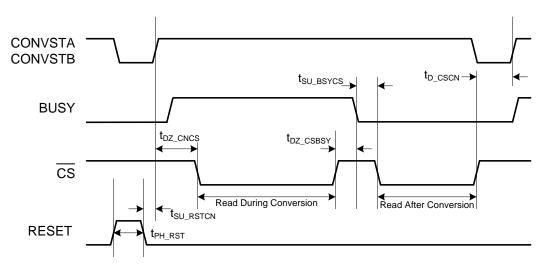

# 7.7 Timing Requirements: Data Read Operation

minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +125°C, typical specifications are at  $T_A = 25^{\circ}$ C; AVDD = 5 V, 2.3 V ≤ DVDD ≤ 5.25 V,  $V_{REF} = 2.5$  V (internal), BUSY load = 20 pF,  $V_{IL}$  and  $V_{IH}$  at datasheet limits, and  $f_{SAMPLE} = 200$  kSPS (unless otherwise noted) (see Figure 2)

|                       |                                                                                                                                   | MIN | NOM | MAX | UNIT |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>DZ_CNCS</sub>  | Delay between CONVSTA, CONVSTB rising edge to $\overline{\text{CS}}$ falling edge, start of data read operation during conversion | 10  |     |     | ns   |

| t <sub>DZ_CSBSY</sub> | Delay between $\overline{\text{CS}}$ rising edge to BUSY falling edge, end of data read operation during conversion               | 40  |     |     | ns   |

| t <sub>SU_BSYCS</sub> | Setup time: BUSY falling edge to $\overline{\text{CS}}$ falling edge, start of data read operation after conversion               | 0   |     |     | ns   |

| t <sub>D_CSCN</sub>   | Delay between $\overline{\text{CS}}$ rising edge to CONVSTA, CONVSTB rising edge, end of data read operation after conversion     | 10  |     |     | ns   |

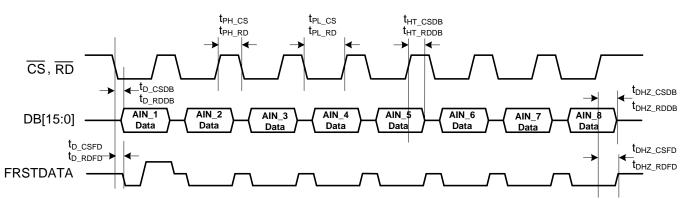

# 7.8 Timing Requirements: Parallel Data Read Operation, CS and RD Tied Together

minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +125°C, typical specifications are at  $T_A = 25^{\circ}$ C; AVDD = 5 V, 2.3 V ≤ DVDD ≤ 5.25 V,  $V_{REF} = 2.5$  V (internal), load on DB[15:0] and FRSTDATA = 20 pF,  $V_{IL}$  and  $V_{IH}$  at datasheet limits, and  $f_{SAMPLE} = 200$  kSPS (unless otherwise noted) (see Figure 3)

|                                                |                                                                                | MIN | NOM | MAX | UNIT |

|------------------------------------------------|--------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>PH_CS</sub> ,<br>t <sub>PH_RD</sub>     | CS and RD high time                                                            | 15  |     |     | ns   |

| t <sub>PL_CS</sub> ,<br>t <sub>PL_RD</sub>     | CS and RD low time                                                             | 15  |     |     | ns   |

| t <sub>HT_RDDB</sub> ,<br>t <sub>HT_CSDB</sub> | Hold time: $\overline{RD}$ and $\overline{CS}$ rising edge to DB[15:0] invalid | 2.5 |     |     | ns   |

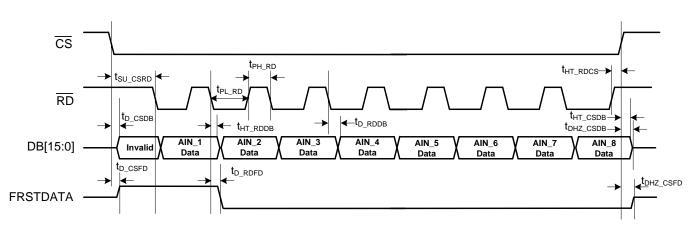

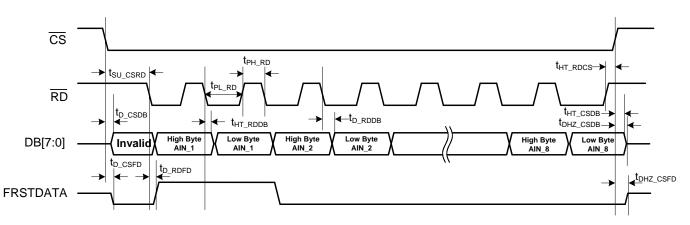

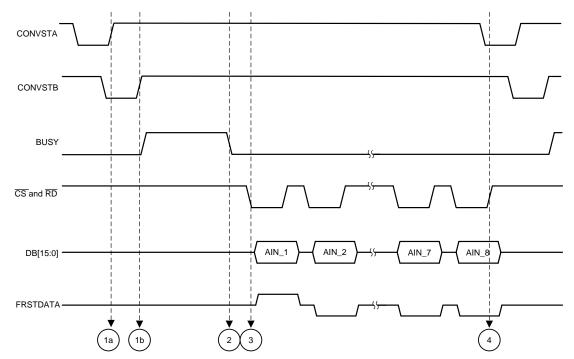

### 7.9 Timing Requirements: Parallel Data Read Operation, CS and RD Separate

minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +125°C, typical specifications are at  $T_A = 25^{\circ}$ C; AVDD = 5 V, 2.3 V ≤ DVDD ≤ 5.25 V,  $V_{REF} = 2.5$  V (internal), load on DB[15:0] and FRSTDATA = 20 pF,  $V_{IL}$  and  $V_{IH}$  at datasheet limits, and  $f_{SAMPLE} = 200$  kSPS (unless otherwise noted) (see Figure 4)

|                      |                                                                       | MIN | NOM | MAX | UNIT |

|----------------------|-----------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>SU_CSRD</sub> | Set-up time: CS falling edge to RD falling edge                       | 0   |     |     | ns   |

| t <sub>HT_RDCS</sub> | Hold time: $\overline{RD}$ rising edge to $\overline{CS}$ rising edge | 0   |     |     | ns   |

| t <sub>PL_RD</sub>   | RD low time                                                           | 15  |     |     | ns   |

| t <sub>PH_RD</sub>   | RD high time                                                          | 15  |     |     | ns   |

| t <sub>HT_CSDB</sub> | Hold time: CS rising edge to DB[15:0] becoming invalid                | 6   |     |     | ns   |

| t <sub>HT_RDDB</sub> | Hold time: RD rising edge to DB[15:0] becoming invalid                | 2.5 |     |     | ns   |

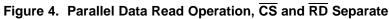

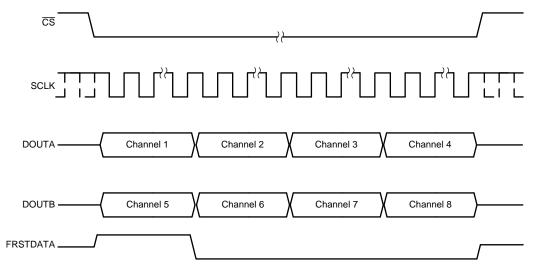

### 7.10 Timing Requirements: Serial Data Read Operation

minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +125°C, typical specifications are at  $T_A = 25^{\circ}$ C; AVDD = 5 V, 2.3 V ≤ DVDD ≤ 5.25 V,  $V_{REF} = 2.5$  V (internal), load on DOUTA, DOUTB, and FRSTDATA = 20 pF,  $V_{IL}$  and  $V_{IH}$  at datasheet limits, and  $f_{SAMPLE} = 200$  kSPS (unless otherwise noted) (see Figure 5)

|                      |                                                          | MIN  | NOM | MAX  | UNIT              |

|----------------------|----------------------------------------------------------|------|-----|------|-------------------|

| t <sub>SCLK</sub>    | SCLK time period                                         | 50   |     |      | ns                |

| t <sub>PH_SCLK</sub> | SCLK high time                                           | 0.45 |     | 0.55 | t <sub>SCLK</sub> |

| t <sub>PL_SCLK</sub> | SCLK low time                                            | 0.45 |     | 0.55 | t <sub>SCLK</sub> |

| t <sub>HT_CKDO</sub> | Hold time: SCLK rising edge to DOUTA, DOUTB invalid      | 7    |     |      | ns                |

| t <sub>su_cscк</sub> | Setup time: CS falling to first SCLK edge                | 8    |     |      | ns                |

| t <sub>HT_CKCS</sub> | Hold time: last SCLK active edge to $\overline{CS}$ high | 10   |     |      | ns                |

### 7.11 Timing Requirements: Byte Mode Data Read Operation

minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +125°C, typical specifications are at  $T_A = 25^{\circ}$ C; AVDD = 5 V, 2.3 V ≤ DVDD ≤ 5.25 V,  $V_{REF} = 2.5$  V (internal), load on DB[7:0] and FRSTDATA = 20 pF,  $V_{IL}$  and  $V_{IH}$  at datasheet limits, and  $f_{SAMPLE} = 200$  kSPS (unless otherwise noted) (see Figure 6)

|                      |                                                                          | MIN | NOM | MAX | UNIT |

|----------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>SU_CSRD</sub> | Setup time: $\overline{CS}$ falling edge to $\overline{RD}$ falling edge | 0   |     |     | ns   |

| t <sub>HT_RDCS</sub> | Hold time: $\overline{RD}$ rising edge to $\overline{CS}$ rising edge    | 0   |     |     | ns   |

| t <sub>PL_RD</sub>   | RD low time                                                              | 15  |     |     | ns   |

| t <sub>PH_RD</sub>   | RD high time                                                             | 15  |     |     | ns   |

| t <sub>HT_CSDB</sub> | Hold time: CS rising edge to DB[15:0] becoming invalid                   | 6   |     |     | ns   |

| t <sub>HT_RDDB</sub> | Hold time: RD rising edge to DB[15:0] becoming invalid                   | 2.5 |     |     | ns   |

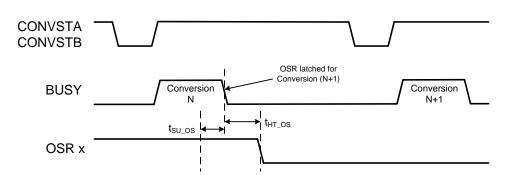

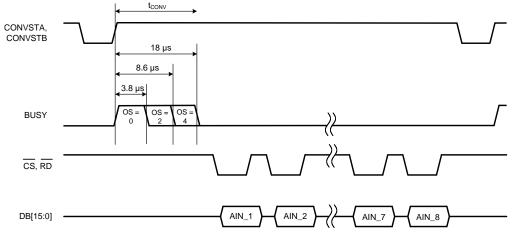

### 7.12 Timing Requirements: Oversampling Mode

|                    |                                 | MIN | NOM MA | X UNIT |

|--------------------|---------------------------------|-----|--------|--------|

| t <sub>HT_OS</sub> | Hold time: BUSY falling to OSx  | 20  |        | ns     |

| t <sub>SU_OS</sub> | Setup time: BUSY falling to OSx | 20  |        | ns     |

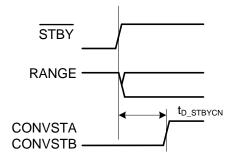

### 7.13 Timing Requirements: Exit Standby Mode

minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +125°C, typical specifications are at  $T_A = 25^{\circ}$ C, AVDD = 5 V, 2.3 V ≤ DVDD ≤ 5.25 V,  $V_{REF} = 2.5$  V (internal),  $V_{IL}$  and  $V_{IH}$  at datasheet limits, and  $f_{SAMPLE} = 200$  kSPS (unless otherwise noted) (see Figure 8)

|                       |                                                                                                     | MIN | NOM | MAX | UNIT |

|-----------------------|-----------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>D_STBYCN</sub> | Delay between $\overline{\text{STBY}}$ rising edge to CONVSTA or CONVSTB rising edge <sup>(1)</sup> | 100 |     |     | μs   |

(1) First conversion data must be discarded or RESET must be issued if the maximum timing is exceeded.

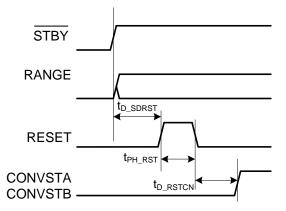

### 7.14 Timing Requirements: Exit Shutdown Mode

minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +125°C, typical specifications are at  $T_A = 25^{\circ}$ C; AVDD = 5 V, 2.3 V ≤ DVDD ≤ 5.25 V, V<sub>REF</sub> = 2.5 V (internal), V<sub>IL</sub> and V<sub>IH</sub> at datasheet limits, and f<sub>SAMPLE</sub> = 200 kSPS (unless otherwise noted) (see Figure 9)

|                      |                                                     |                                        | MIN | NOM | MAX | UNIT |

|----------------------|-----------------------------------------------------|----------------------------------------|-----|-----|-----|------|

|                      | RST RESET high time                                 | Internal reference mode                | 50  |     |     |      |

| t <sub>D_SDRST</sub> |                                                     | External reference mode <sup>(1)</sup> | 13  |     |     | ms   |

| t <sub>PH_RST</sub>  | RESET high time                                     |                                        | 50  |     |     | ns   |

| t <sub>D_RSTCN</sub> | Delay between RESET falling edge to CONVSTA or CONV | /STB rising edge                       | 25  |     |     | μs   |

(1) Excludes wake-up time for external reference device.

## 7.15 Switching Characteristics: CONVST Control

minimum and maximum specifications are at  $T_A = -40^{\circ}$ C to +125°C, typical specifications are at  $T_A = 25^{\circ}$ C; AVDD = 5 V, 2.3 V ≤ DVDD ≤ 5.25 V,  $V_{REF} = 2.5$  V (internal), BUSY load = 20 pF,  $V_{IL}$  and  $V_{IH}$  at datasheet limits, and  $f_{SAMPLE} = 200$  kSPS (unless otherwise noted) (see Figure 1)

| PARAMETER                                                                       | TEST CONDITIONS                                                                                                                   | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TYP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

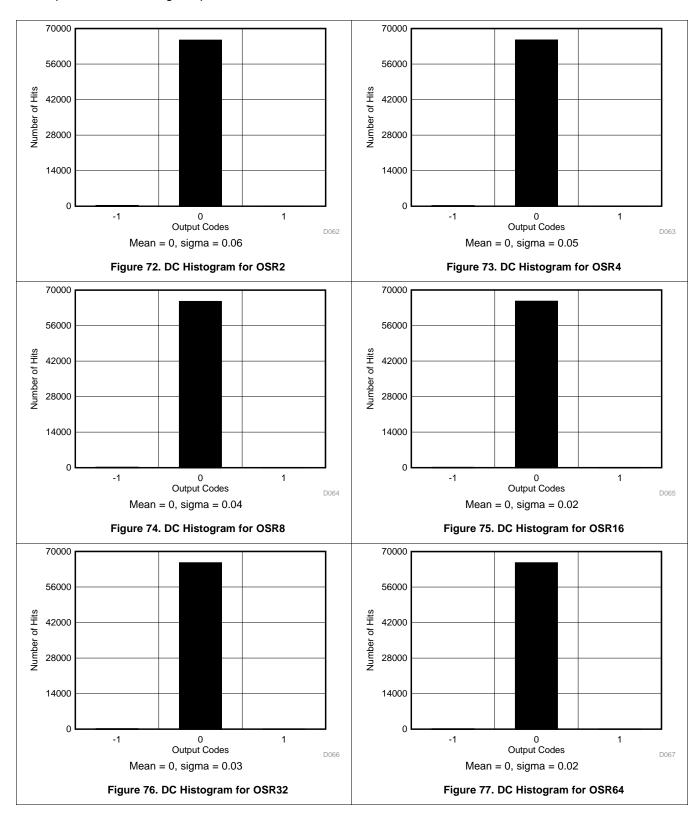

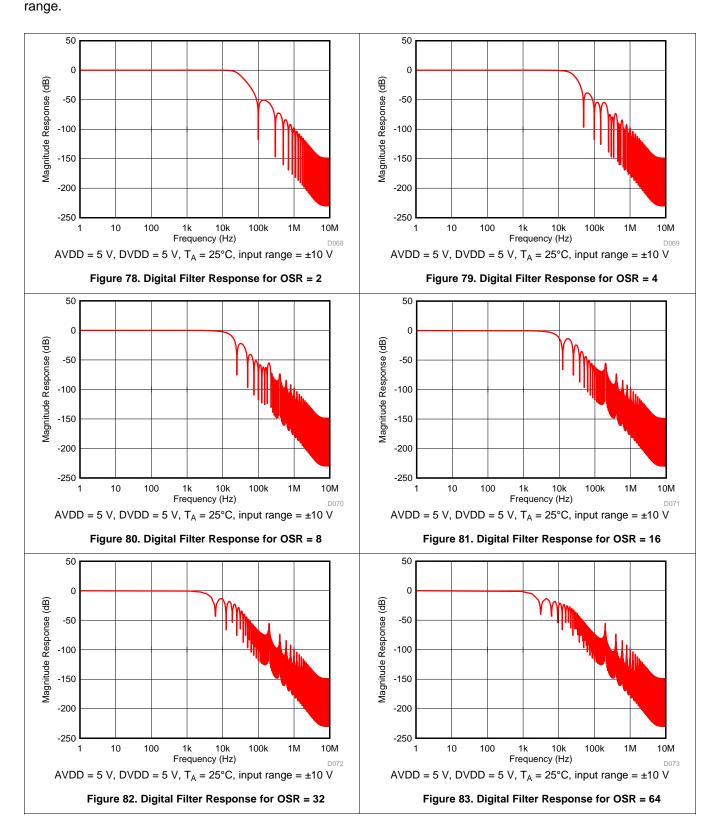

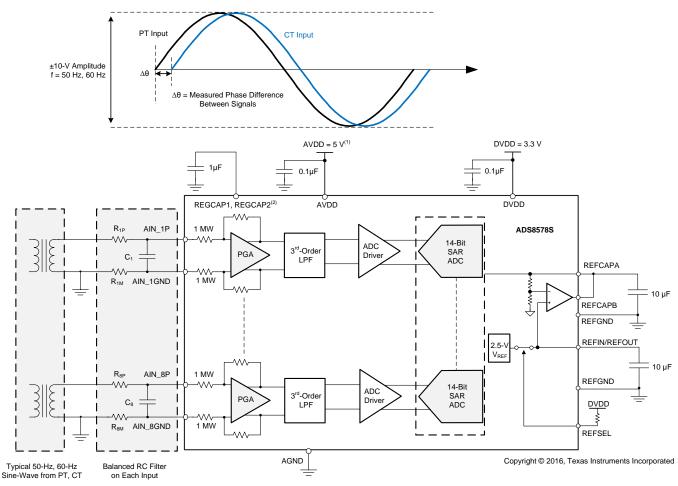

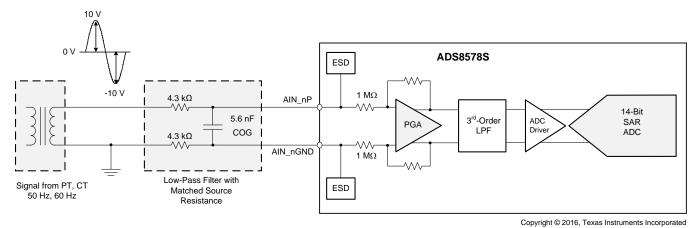

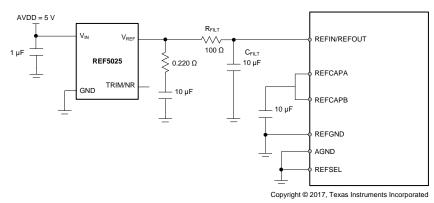

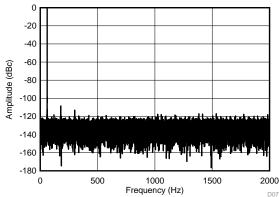

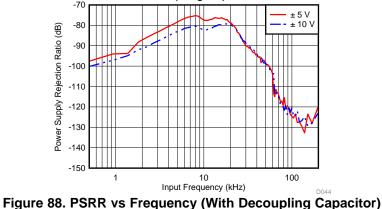

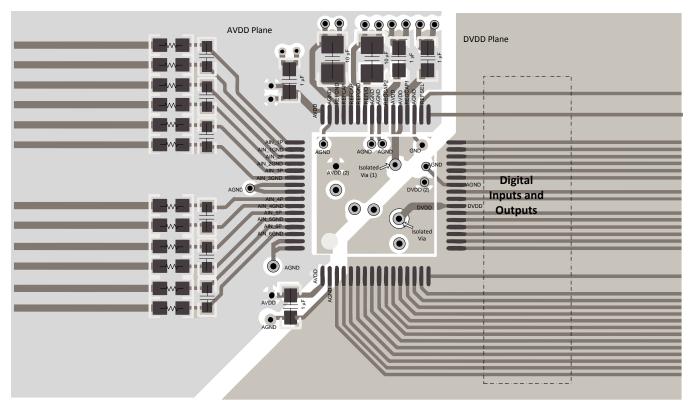

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|