Sample &

Buy

Support &

20

LP2950, LP2951

SLVS582I-APRIL 2006-REVISED NOVEMBER 2014

## LP295x Adjustable Micropower Voltage Regulators with Shutdown

Technical

Documents

## 1 Features

- Wide Input Range: Up to 30 V

- Rated Output Current of 100 mA

- Low Dropout: 380 mV (Typ) at 100 mA

- Low Quiescent Current: 75 μA (Typ)

- Tight Line Regulation: 0.03% (Typ)

- Tight Load Regulation: 0.04% (Typ)

- High V<sub>O</sub> Accuracy

- 1.4% at 25°C

- 2% Over Temperature

- Can Be Used as a Regulator or Reference

- Stable With Low ESR (>12 mΩ) Capacitors

- Current- and Thermal-Limiting Features

- LP2950 Only (3-Pin Package)

- Fixed-Output Voltages of 5 V, 3.3 V, and 3 V

- LP2951 Only (8-Pin Package)

- Fixed- or Adjustable-Output Voltages: 5 V/ADJ, 3.3 V/ADJ, and 3 V/ADJ

- Low-Voltage Error Signal on Falling Output

- Shutdown Capability

- Remote Sense Capability for Optimal Output Regulation and Accuracy

## 2 Applications

Tools &

Software

- Applications with High-Voltage Input

- Power Supplies

## **3 Description**

The LP2950 and LP2951 devices are bipolar, lowdropout voltage regulators that can accommodate a wide input supply-voltage range of up to 30 V. The easy-to-use, 3-pin LP2950 is available in fixed-output voltages of 5 V, 3.3 V, and 3 V. However, the 8-pin LP2951 is able to output either a fixed or adjustable output from the same device. By tying the OUTPUT and SENSE pins together, and the FEEDBACK and V<sub>TAP</sub> pins together, the LP2951 outputs a fixed 5 V, 3.3 V, or 3 V (depending on the version). Alternatively, by leaving the SENSE and V<sub>TAP</sub> pins open and connecting FEEDBACK to an external resistor divider, the output can be set to any value between 1.235 V to 30 V.

| Device Information |           |                   |  |  |  |  |  |  |  |  |

|--------------------|-----------|-------------------|--|--|--|--|--|--|--|--|

| PART NUMBER        | PACKAGE   | BODY SIZE (NOM)   |  |  |  |  |  |  |  |  |

| LP2950             | TO-92 (3) | 4.83 mm x 4.83 mm |  |  |  |  |  |  |  |  |

| 1 00054            | SOIC (8)  | 4.90 mm x 3.90 mm |  |  |  |  |  |  |  |  |

| LP2951             | SON (8)   | 3.00 mm x 3.00 mm |  |  |  |  |  |  |  |  |

## Device Information<sup>(1)</sup>

(1) For all available packages, see the orderable addendum at the end of the data sheet.

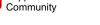

Dropout Voltage vs Temperature

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclosing a RECEIPTION DATA

Downloaded From Oneyac.com

Features ..... 1

Applications ..... 1

Description ..... 1

Revision History..... 2

Pin Configuration and Functions ...... 3

Specifications...... 4

Absolute Maximum Ratings ...... 4

Handling Ratings ...... 4

Recommended Operating Conditions ...... 4

Thermal Information ...... 4

Overview ..... 12

LP2950 Functional Block Diagram...... 12

6.6 Typical Characteristics ...... 7

Detailed Description ..... 12

1

2

3

4

5

6

7

6.1

6.2

6.3

6.4

6.5

7.1

7.2

2

#### 7.3 LP2951 Functional Block Diagram...... 13 7.4 Feature Description..... 14 Device Functional Modes......15 7.5 Application and Implementation ...... 16 8 8.1 Application Information...... 16

|    | 8.2  | Typical Application               | 16 |

|----|------|-----------------------------------|----|

| 9  | Pow  | er Supply Recommendations         | 19 |

| 10 | Lay  | out                               | 19 |

|    | 10.1 | Layout Guidelines                 | 19 |

|    | 10.2 | Layout Example                    | 19 |

| 11 | Dev  | ice and Documentation Support     | 19 |

|    | 11.1 | Trademarks                        | 19 |

|    | 11.2 | Electrostatic Discharge Caution   | 19 |

|    | 11.3 | Glossary                          | 19 |

| 12 | Mec  | hanical, Packaging, and Orderable |    |

|    | Info | mation                            | 19 |

## 4 Revision History

### Changes from Revision H (March 2012) to Revision I

| Added Applications, Device Information table, Handling Ratings table, Feature Description section, Device       |

|-----------------------------------------------------------------------------------------------------------------|

| Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout          |

| section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section |

|                                                                                                                 |

Table of Contents

Downloaded From Oneyac.com

www.ti.com

Page

1

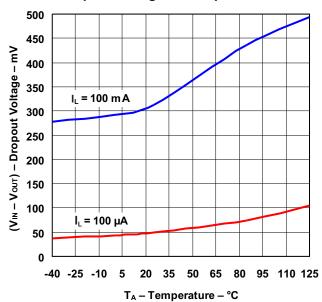

## 5 Pin Configuration and Functions

### **Pin Functions**

|                  | PIN    |        | TYPE | DESCRIPTION                                                                                                                                                                                                   |  |  |  |  |  |

|------------------|--------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME             | LP2950 | LP2951 | ITPE | DESCRIPTION                                                                                                                                                                                                   |  |  |  |  |  |

| ERROR            | _      | 5      | 0    | Active-low open-collector error output. Goes low when $V_{OUT}$ drops by 6% of its nominal value.                                                                                                             |  |  |  |  |  |

| FEEDBACK         | _      | 7      | I    | Determines the output voltage. Connect to $V_{TAP}$ (with OUTPUT tied to SENSE) to output the fixed voltage corresponding to the part version, or connect to a resistor divider to adjust the output voltage. |  |  |  |  |  |

| GND              | 2      | 4      | _    | Ground                                                                                                                                                                                                        |  |  |  |  |  |

| INPUT            | 3      | 8      | Ι    | Supply input                                                                                                                                                                                                  |  |  |  |  |  |

| OUTPUT           | 1      | 1      | 0    | Voltage output.                                                                                                                                                                                               |  |  |  |  |  |

| SENSE            |        | 2      | Ι    | Senses the output voltage. Connect to OUTPUT (with FEEDBACK tied to $V_{TAP}$ ) to output the voltage corresponding to the part version.                                                                      |  |  |  |  |  |

| SHUTDOWN         | _      | 3      | I    | Active-high input. Shuts down the device.                                                                                                                                                                     |  |  |  |  |  |

| V <sub>TAP</sub> | _      | 6      | 0    | Tie to FEEDBACK to output the fixed voltage corresponding to the part version.                                                                                                                                |  |  |  |  |  |

XAS STRUMENTS

www.ti.com

#### Specifications 6

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                   |                                                      | MIN  | MAX | UNIT |

|-------------------|------------------------------------------------------|------|-----|------|

| V <sub>IN</sub>   | Continuous input voltage range                       | -0.3 | 30  | V    |

| V <sub>SHDN</sub> | SHUTDOWN input voltage range                         | -1.5 | 30  | V    |

| VERROR            | ERROR comparator output voltage range <sup>(2)</sup> | -1.5 | 30  | V    |

| V <sub>FDBK</sub> | FEEDBACK input voltage range <sup>(2)</sup> (3)      | -1.5 | 30  | V    |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

May exceed input supply voltage

(3) If load is returned to a negative power supply, the output must be diode clamped to GND.

## 6.2 Handling Ratings

|                    |                          |                                                                                          | MIN | MAX  | UNIT |

|--------------------|--------------------------|------------------------------------------------------------------------------------------|-----|------|------|

| T <sub>stg</sub>   | Storage temperature rang | ge                                                                                       | -65 | 150  | °C   |

| N                  | Flastraatotia diasharga  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | 0   | 2500 | N/   |

| V <sub>(ESD)</sub> | Electrostatic discharge  | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | 0   | 1000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (2)

## 6.3 Recommended Operating Conditions

|   |                                          | MIN     | MAX | UNIT |

|---|------------------------------------------|---------|-----|------|

| ١ | V <sub>IN</sub> Supply input voltage     | See (1) | 30  | V    |

| Г | J Operating virtual junction temperature | -40     | 125 | °C   |

Minimum V<sub>IN</sub> is the greater of:

(a) 2 V (25°C), 2.3 V (over temperature), or

(b) V<sub>OUT(MAX)</sub> + Dropout (Max) at rated I<sub>L</sub>

## 6.4 Thermal Information

|                |                                        | LP2950 |    | LP2951 |       |      |

|----------------|----------------------------------------|--------|----|--------|-------|------|

|                | THERMAL METRIC <sup>(1)</sup>          | LP     | D  | Р      | DRG   | UNIT |

|                |                                        | 3 PINS |    | 8 PINS |       |      |

| $R_{\thetaJA}$ | Junction-to-ambient thermal resistance | 140    | 97 | 84.6   | 52.44 | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report (SPRA953).

## 6.5 Electrical Characteristics

$V_{\text{IN}} = V_{\text{OUT}} \text{ (nominal)} + 1 \text{ V}, \text{ I}_{\text{L}} = 100 \text{ }\mu\text{A}, \text{ }C_{\text{L}} = 1 \text{ }\mu\text{F} \text{ (5-V versions)} \text{ or } \text{ }C_{\text{L}} = 2.2 \text{ }\mu\text{F} \text{ (3-V and 3.3-V versions)}, \text{ 8-pin version: FEEDBACK tied to }V_{\text{TAP}}, \text{ OUTPUT tied to SENSE, }V_{\text{SHUTDOWN}} \leq 0.7 \text{ }V$

|                                    | PARAMETER                                             | TEST CONDITIONS                                                              | TJ             | MIN   | TYP   | MAX   | UNIT   |  |

|------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------|----------------|-------|-------|-------|--------|--|

| 3-V VERSI                          | ON (LP295x-30)                                        |                                                                              |                |       |       |       |        |  |

| M                                  |                                                       | 1 100 4                                                                      | 25°C           | 2.970 | 3     | 3.030 | V      |  |

| V <sub>OUT</sub>                   | Output voltage                                        | I <sub>L</sub> = 100 μA                                                      | -40°C to 125°C | 2.940 | 3     | 3.060 | v      |  |

| 3.3-V VERS                         | SION (LP295x-33)                                      | ·                                                                            |                |       |       |       |        |  |

| M                                  | Output voltage                                        | 1 100                                                                        | 25°C           | 3.267 | 3.3   | 3.333 | v      |  |

| V <sub>OUT</sub>                   | Output voltage                                        | I <sub>L</sub> = 100 μA                                                      | -40°C to 125°C | 3.234 | 3.3   | 3.366 | v      |  |

| 5-V VERSI                          | ON (LP295x-50)                                        |                                                                              |                |       |       |       |        |  |

| M                                  | Output voltage                                        | 1 100                                                                        | 25°C           | 4.950 | 5     | 5.050 | V      |  |

| V <sub>OUT</sub>                   | Output voltage                                        | I <sub>L</sub> = 100 μA                                                      | -40°C to 125°C | 4.900 | 5     | 5.100 | v      |  |

| ALL VOLT                           | AGE OPTIONS                                           |                                                                              |                |       |       |       |        |  |

|                                    | Output voltage temperature coefficient <sup>(1)</sup> | I <sub>L</sub> = 100 μA                                                      | -40°C to 125°C |       | 20    | 100   | ppm/°C |  |

|                                    | (2)                                                   |                                                                              | 25°C           |       | 0.03  | 0.2   | 0/ 0/  |  |

|                                    | Line regulation <sup>(2)</sup>                        | $V_{IN} = [V_{OUT(NOM)} + 1 V]$ to 30 V                                      | -40°C to 125°C |       |       | 0.4   | %/V    |  |

|                                    | 1 (2)                                                 |                                                                              | 25°C           |       | 0.04% | 0.2%  |        |  |

|                                    | Load regulation <sup>(2)</sup>                        | $I_{L} = 100 \ \mu A \text{ to } 100 \ m A$                                  | -40°C to 125°C |       |       | 0.3%  | _      |  |

|                                    | Dropout voltage <sup>(3)</sup>                        | 1 100                                                                        | 25°C           |       | 50    | 80    |        |  |

|                                    |                                                       | I <sub>L</sub> = 100 μA                                                      | -40°C to 125°C |       |       | 150   | mV     |  |

| V <sub>IN</sub> – V <sub>OUT</sub> |                                                       | 1                                                                            | 25°C           |       | 380   | 450   |        |  |

|                                    |                                                       | $I_L = 100 \text{ mA}$                                                       | -40°C to 125°C |       |       | 600   |        |  |

|                                    |                                                       | 1 100                                                                        | 25°C           |       | 75    | 120   |        |  |

|                                    |                                                       | I <sub>L</sub> = 100 μA                                                      | -40°C to 125°C |       |       | 140   | μA     |  |

| I <sub>GND</sub>                   | GND current                                           | 100                                                                          | 25°C           |       | 8     | 12    |        |  |

|                                    |                                                       | $I_L = 100 \text{ mA}$                                                       | -40°C to 125°C |       |       | 14    | mA     |  |

|                                    | Dropout ground ourropt                                | $V_{IN} = V_{OUT(NOM)} - 0.5 V,$                                             | 25°C           |       | 110   | 170   |        |  |

|                                    | Dropout ground current                                | $I_{L} = 100 \ \mu A$                                                        | -40°C to 125°C |       |       | 200   | μA     |  |

|                                    | Current lineit                                        | N 0.Y                                                                        | 25°C           |       | 160   | 200   |        |  |

|                                    | Current limit                                         | V <sub>OUT</sub> = 0 V                                                       | -40°C to 125°C |       |       | 220   | mA     |  |

|                                    | Thermal regulation <sup>(4)</sup>                     | I <sub>L</sub> = 100 μA                                                      | 25°C           |       | 0.05  | 0.2   | %/W    |  |

|                                    |                                                       | $C_L = 1 \ \mu F (5 \ V \text{ only})$                                       |                |       | 430   |       |        |  |

|                                    | Output noise (RMS),                                   | C <sub>L</sub> = 200 μF                                                      |                |       | 160   |       |        |  |

|                                    | 10 Hz to 100 kHz                                      | LP2951-50: $C_L$ = 3.3 µF,<br>$C_{Bypass}$ = 0.01 µF between<br>pins 1 and 7 | 25°C           |       | 100   |       | μV     |  |

(1) Output or reference voltage temperature coefficient is defined as the worst-case voltage change divided by the total temperature range.

(2) Regulation is measured at constant junction temperature, using pulse testing with a low duty cycle. Changes in output voltage due to heating effects are covered under the specification for thermal regulation.

(3) Dropout voltage is defined as the input-to-output differential at which the output voltage drops 100 mV, below the value measured at 1-V differential. The minimum input supply voltage of 2 V (2.3 V over temperature) must be observed.

(4) Thermal regulation is defined as the change in output voltage at a time (T) after a change in power dissipation is applied, excluding load or line regulation effects. Specifications are for a 50-mA load pulse at  $V_{IN} = 30 \text{ V}$ ,  $V_{OUT} = 5 \text{ V}$  (1.25-W pulse) for t = 10 ms.

### LP2950, LP2951

SLVS582I-APRIL 2006-REVISED NOVEMBER 2014

www.ti.com

STRUMENTS

XAS

## **Electrical Characteristics (continued)**

$V_{\text{IN}} = V_{\text{OUT}} \text{ (nominal)} + 1 \text{ V}, \text{ I}_{\text{L}} = 100 \text{ }\mu\text{A}, \text{ }C_{\text{L}} = 1 \text{ }\mu\text{F} \text{ (5-V versions)} \text{ or } \text{ }C_{\text{L}} = 2.2 \text{ }\mu\text{F} \text{ (3-V and 3.3-V versions)}, \text{ 8-pin version: FEEDBACK tied to }V_{\text{TAP}}, \text{ OUTPUT tied to SENSE, }V_{\text{SHUTDOWN}} \leq 0.7 \text{ }V$

| PARAMETER                                                | TEST CONDITIONS                                                       | TJ             | MIN   | TYP   | MAX   | UNIT   |

|----------------------------------------------------------|-----------------------------------------------------------------------|----------------|-------|-------|-------|--------|

| (LP2951-xx) 8-PIN VERSION ONLY AD                        | J                                                                     |                |       |       |       |        |

|                                                          |                                                                       | 25°C           | 1.218 | 1.235 | 1.252 |        |

|                                                          |                                                                       | -40°C to 125°C | 1.212 |       | 1.257 |        |

| Reference voltage                                        |                                                                       | -40°C to 125°C | 1.200 |       | 1.272 | V      |

| Reference voltage temperature coefficient <sup>(1)</sup> |                                                                       | 25°C           |       | 20    |       | ppm/°C |

| FEEDBACK bias current                                    |                                                                       | 25°C           |       | 20    | 40    | nA     |

| FEEDBACK bias current                                    |                                                                       | –40°C to 125°C |       |       | 60    | ПА     |

| FEEDBACK bias current<br>temperature coefficient         |                                                                       | 25°C           |       | 0.1   |       | nA/°C  |

| ERROR COMPARATOR                                         |                                                                       |                |       |       |       |        |

|                                                          | V = 20 V                                                              | 25°C           |       | 0.01  | 1     | μA     |

| Output leakage current                                   | V <sub>OUT</sub> = 30 V                                               | –40°C to 125°C |       |       | 2     | μΑ     |

|                                                          | $V_{IN} = V_{OUT(NOM)} - 0.5 \text{ V},$                              | 25°C           |       | 150   | 250   | mV     |

| Output low voltage                                       | $I_{OL} = 400 \ \mu A$                                                | -40°C to 125°C |       |       | 400   | IIIV   |

| Upper threshold voltage                                  |                                                                       | 25°C           | 40    | 60    |       | mV     |

| (ERROR output high) <sup>(5)</sup>                       |                                                                       | –40°C to 125°C | 25    |       |       | mv     |

| Lower threshold voltage                                  |                                                                       | 25°C           |       | 75    | 95    | mV     |

| (ERROR output low) <sup>(5)</sup>                        |                                                                       | -40°C to 125°C |       |       | 140   | mv     |

| Hysteresis <sup>(5)</sup>                                |                                                                       | 25°C           |       | 15    |       | mV     |

| SHUTDOWN INPUT                                           |                                                                       |                |       |       |       |        |

|                                                          | Low (regulator ON)                                                    | 40°C to 125°C  |       |       | 0.7   | V      |

| Input logic voltage                                      | High (regulator OFF)                                                  | -40°C to 125°C | 2     |       |       | v      |

|                                                          |                                                                       | 25°C           |       | 30    | 50    |        |

|                                                          | SHUTDOWN = 2.4 V                                                      | -40°C to 125°C |       |       | 100   |        |

| SHUTDOWN input current                                   |                                                                       | 25°C           |       | 450   | 600   | μA     |

|                                                          | SHUTDOWN = 30 V                                                       | -40°C to 125°C |       |       | 750   |        |

| Regulator output current                                 | V <sub>SHUTDOWN</sub> ≥ 2 V,                                          | 25°C           |       | 3     | 10    |        |

| in shutdown                                              | $V_{IN} \le 30 \text{ V}, V_{OUT} = 0,$<br>FEEDBACK tied to $V_{TAP}$ | -40°C to 125°C |       |       | 20    | μA     |

(5) Comparator thresholds are expressed in terms of a voltage differential equal to the nominal reference voltage (measured at V<sub>IN</sub> - V<sub>OUT</sub> = 1 V) minus FEEDBACK terminal voltage. To express these thresholds in terms of output voltage change, multiply by the error amplifier gain = V<sub>OUT</sub>/V<sub>REF</sub> = (R1 + R2)/R2. For example, at a programmed output voltage of 5 V, the ERROR output is specified to go low when the output drops by 95 mV x 5 V/1.235 V = 384 mV. Thresholds remain constant as a percentage of V<sub>OUT</sub> (as V<sub>OUT</sub> is varied), with the low-output warning occurring at 6% below nominal (typ) and 7.7% (max).

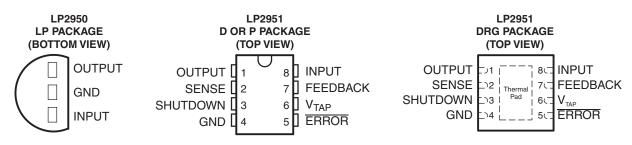

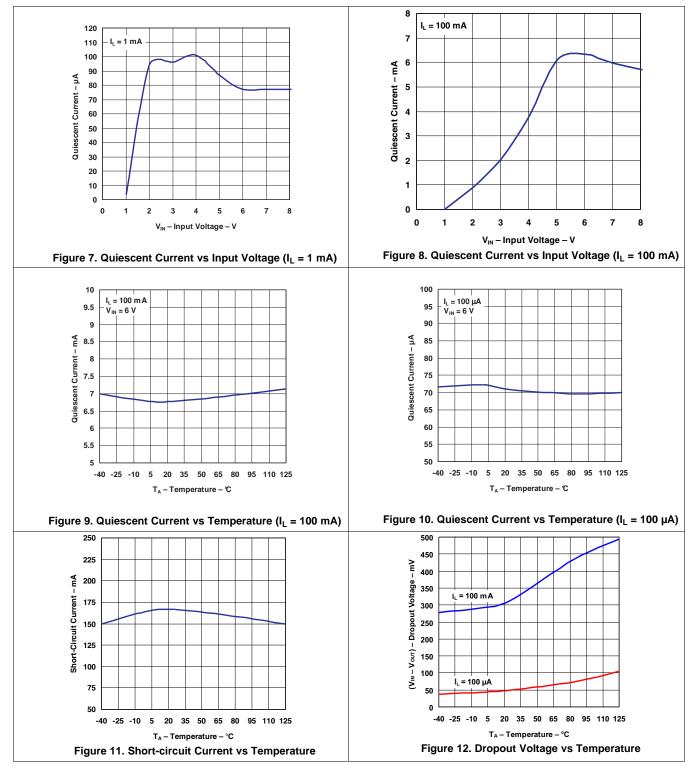

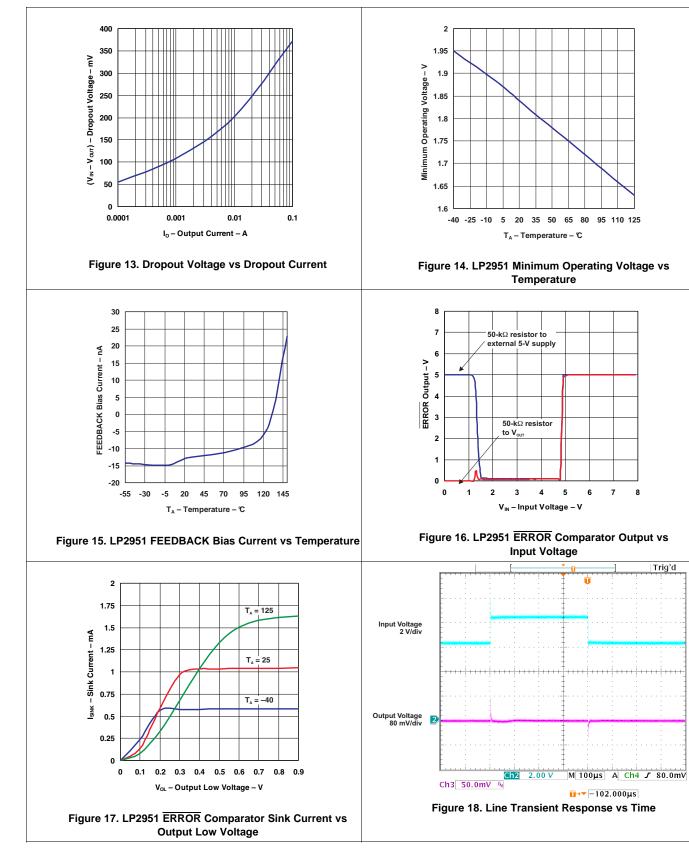

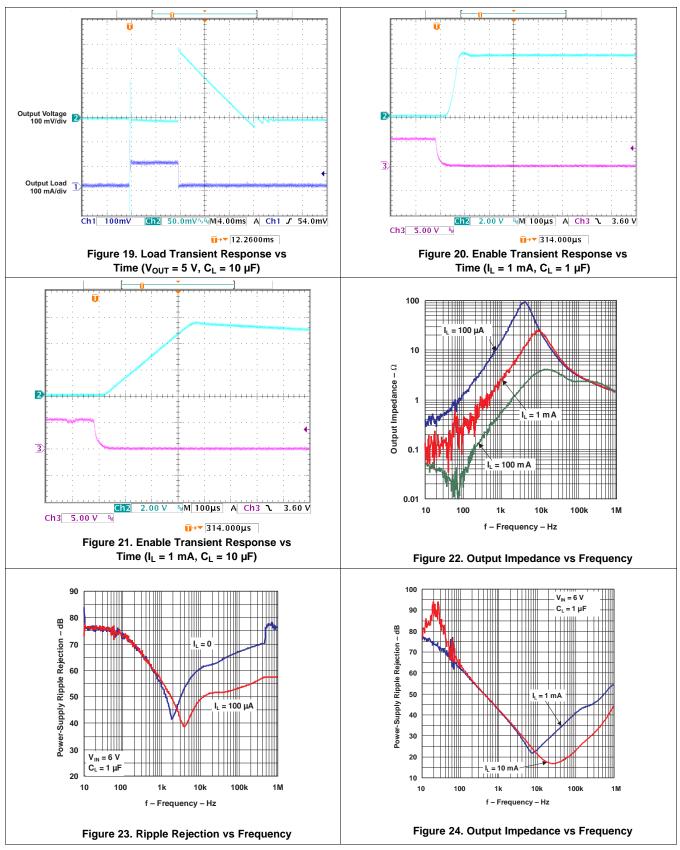

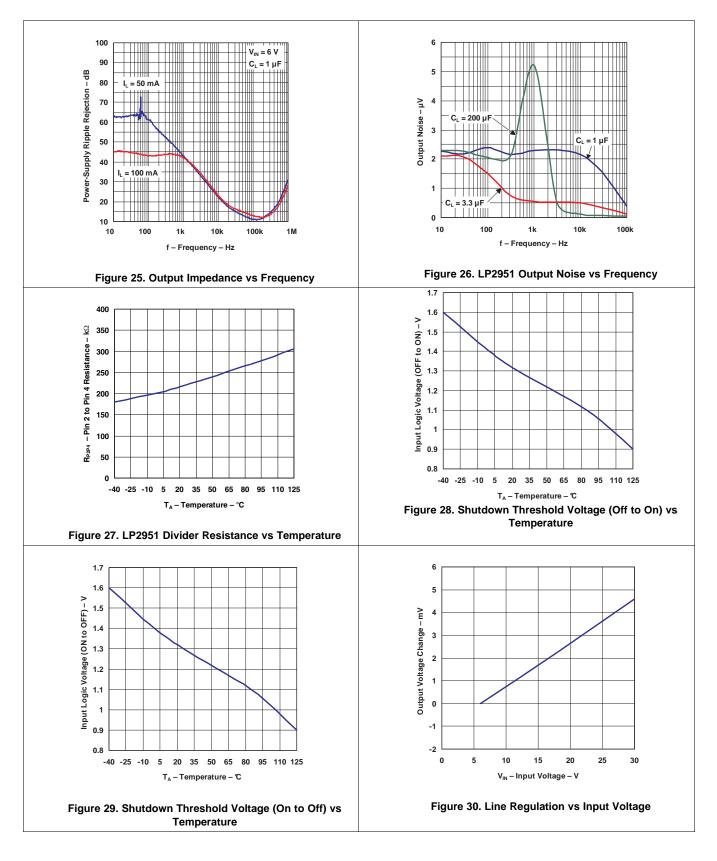

## 6.6 Typical Characteristics

### LP2950, LP2951 SLVS582I – APRIL 2006 – REVISED NOVEMBER 2014

www.ti.com

## **Typical Characteristics (continued)**

## **Typical Characteristics (continued)**

Copyright © 2006–2014, Texas Instruments Incorporated

LP2950, LP2951 SLVS582I – APRIL 2006 – REVISED NOVEMBER 2014

www.ti.com

## **Typical Characteristics (continued)**

10 Submit Documentation Feedback

Copyright © 2006–2014, Texas Instruments Incorporated

Product Folder Links: LP2950 LP2951

## **Typical Characteristics (continued)**

## 7 Detailed Description

## 7.1 Overview

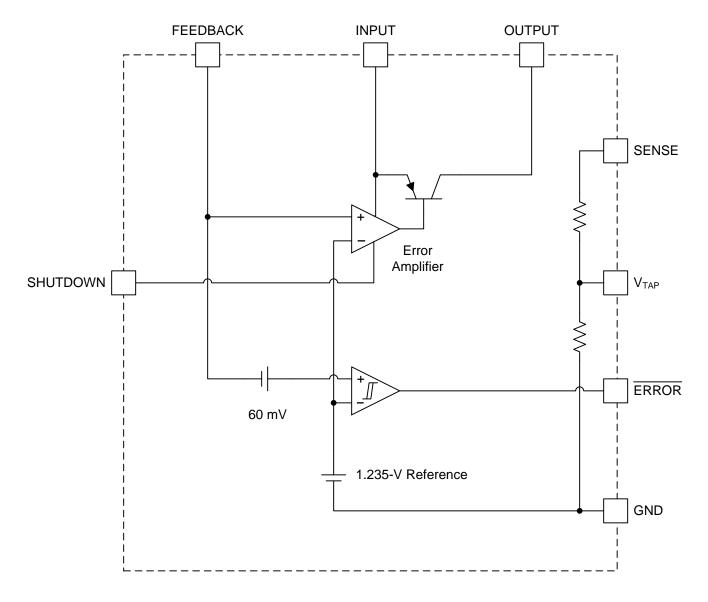

The LP2950 and LP2951 devices are bipolar, low-dropout voltage regulators that can accommodate a wide input supply-voltage range of up to 30 V. The easy-to-use, 3-pin LP2950 is available in fixed-output voltages of 5 V, 3.3 V, and 3 V. However, the 8-pin LP2951 device is able to output either a fixed or adjustable output from the same device. By tying the OUTPUT and SENSE pins together, and the FEEDBACK and V<sub>TAP</sub> pins together, the LP2951 device outputs a fixed 5 V, 3.3 V, or 3 V (depending on the version). Alternatively, by leaving the SENSE and V<sub>TAP</sub> pins open and connecting FEEDBACK to an external resistor divider, the output can be set to any value between 1.235 V to 30 V.

The 8-pin LP2951 device also offers additional functionality that makes it particularly suitable for battery-powered applications. For example, a logic-compatible shutdown feature allows the regulator to <u>be put</u> in standby mode for power savings. In addition, there is a built-in supervisor reset function in which the ERROR output goes low when  $V_{OUT}$  drops by 6% of its nominal value for whatever reasons – due to a drop in  $V_{IN}$ , current limiting, or thermal shutdown.

The LP2950 and LP2951 devices are designed to minimize all error contributions to the output voltage. With a tight output tolerance (0.5% at 25°C), a very low output voltage temperature coefficient (20 ppm typical), extremely good line and load regulation (0.3% and 0.4% typical), and remote sensing capability, the parts can be used as either low-power voltage references or 100-mA regulators.

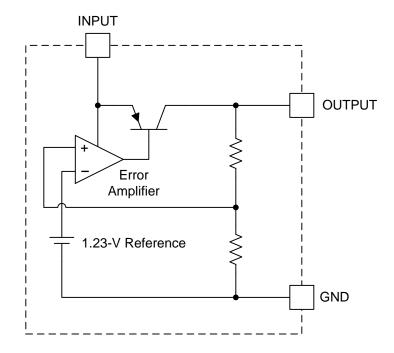

## 7.2 LP2950 Functional Block Diagram

## 7.3 LP2951 Functional Block Diagram

Copyright © 2006–2014, Texas Instruments Incorporated

INSTRUMENTS

www.ti.com

## 7.4 Feature Description

## 7.4.1 ERROR Function (LP2951 Only)

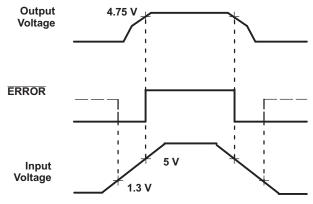

The LP2951 device has a low-voltage detection comparator that outputs a logic low when the output voltage drops by  $\approx$ 6% from its nominal value, and outputs a logic high when V<sub>OUT</sub> has reached  $\approx$ 95% of its nominal value. This 95% of nominal figure is obtained by dividing the built-in offset of  $\approx$ 60 mV by the 1.235-V bandgap reference, and remains independent of the programmed output voltage. For example, the trip-point threshold (ERROR output goes high) typically is 4.75 V for a 5-V output and 11.4 V for a 12-V output. Typically, there is a hysteresis of 15 mV between the thresholds for high and low ERROR output.

A timing diagram is shown in Figure 31 for ERROR vs  $V_{OUT}$  (5 V), as  $V_{IN}$  is ramped up and down. ERROR becomes valid (low) when  $V_{IN} \approx 1.3$  V. When  $V_{IN} \approx 5$  V,  $V_{OUT} = 4.75$  V, causing ERROR to go high. Because the dropout voltage is load dependent, the output trip-point threshold is reached at different values of  $V_{IN}$ , depending on the load current. For instance, at higher load current, ERROR goes high at a slightly higher value of  $V_{IN}$ , and vice versa for lower load current. The output-voltage trip point remains at ~4.75 V, regardless of the load. Note that when  $V_{IN} \leq 1.3$  V, the ERROR comparator output is turned off and pulled high to its pullup voltage. If  $V_{OUT}$  is used as the pullup voltage, rather than an external 5-V source, ERROR typically is ~1.2 V. In this condition, an equal resistor divider (10 k $\Omega$  is suitable) can be tied to ERROR to divide down the voltage to a valid logic low during any fault condition, while still enabling a logic high during normal operation.

Figure 31. ERROR Output Timing

Because the ERROR comparator has an open-collector output, an external pullup resistor is required to pull the output up to  $V_{OUT}$  or another supply voltage (up to 30 V). The output of the comparator is rated to sink up to 400  $\mu$ A. A suitable range of values for the pullup resistor is from 100 k $\Omega$  to 1 M $\Omega$ . If ERROR is not used, it can be left open.

### Feature Description (continued)

### 7.4.2 Programming Output Voltage (LP2951 Only)

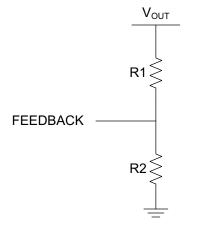

A unique feature of the LP2951 device is its ability to output either a fixed voltage or an adjustable voltage, depending on the external pin connections. To output the internally programmed fixed voltage, tie the SENSE pin to the OUTPUT pin and the FEEDBACK pin to the  $V_{TAP}$  pin. Alternatively, a user-programmable voltage ranging from the internal 1.235-V reference to a 30-V max can be set by using an external resistor divider pair. The resistor divider is tied to  $V_{OUT}$ , and the divided-down voltage is tied directly to FEEDBACK for comparison against the internal 1.235-V reference. To satisfy the steady-state condition in which its two inputs are equal, the error amplifier drives the output to equal Equation 1:

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R1}{R2}\right) - I_{FB}R_1$$

(1)

LP2950, LP2951

SLVS582I - APRIL 2006 - REVISED NOVEMBER 2014

Where:

V<sub>REF</sub> = 1.235 V applied across R2 (see Figure 32)

$I_{FB}$  = FEEDBACK bias current, typically 20 nA

A minimum regulator output current of 1  $\mu$ A must be maintained. Thus, in an application where a no-load condition is expected (for example, CMOS circuits in standby), this 1- $\mu$ A minimum current must be provided by the resistor pair, effectively imposing a maximum value of R2 = 1.2 M $\Omega$  (1.235 V/1.2 M $\Omega \neq$  1  $\mu$ A).

$I_{FB} = 20$  nA introduces an error of  $\neq 0.02\%$  in V<sub>OUT</sub>. This can be offset by trimming R1. Alternatively, increasing the divider current makes  $I_{FB}$  less significant, thus, reducing its error contribution. For instance, using R2 = 100 k $\Omega$  reduces the error contribution of  $I_{FB}$  to 0.17% by increasing the divider current to  $\neq 12 \mu$ A. This increase in the divider current still is small compared to the 600- $\mu$ A typical quiescent current of the LP2951 under no load.

Figure 32. Adjusting the Feedback on the LP2951

## 7.5 Device Functional Modes

### 7.5.1 Shutdown Mode

These devices can be placed in shutdown mode with a logic high at the SHUTDOWN pin. Return the logic level low to restore operation or tie SHUTDOWN to ground if the feature is not being used.

Downloaded From Oneyac.com

## 8 Application and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

The LP295x devices are used as low-dropout regulators with a wide range of input voltages.

### 8.2 Typical Application

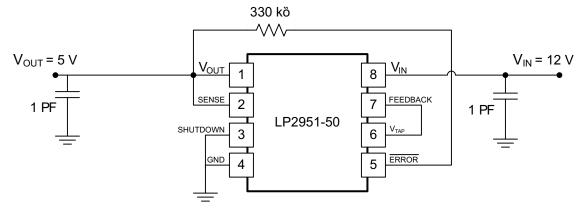

Figure 33. 12-V to 5-V Converter

### 8.2.1 Design Requirements

### 8.2.1.1 Input Capacitor (C<sub>IN</sub>)

A 1- $\mu$ F (tantalum, ceramic, or aluminum) electrolytic capacitor should be placed locally at the input of the LP2950 or LP2951 device if there is, or will be, significant impedance between the ac filter capacitor and the input; for example, if a battery is used as the input or if the ac filter capacitor is located more than 10 in away. There are no ESR requirements for this capacitor, and the capacitance can be increased without limit.

## 8.2.1.2 Output Capacitor (C<sub>OUT</sub>)

As with most PNP LDOs, stability conditions require the output capacitor to have a minimum capacitance and an ESR that falls within a certain range.

## **Typical Application (continued)**

## 8.2.2 Detailed Design Procedure

### 8.2.2.1 Capacitance Value

For  $V_{OUT} \ge 5$  V, a minimum of 1 µF is required. For lower  $V_{OUT}$ , the regulator's loop gain is running closer to unity gain and, thus, has lower phase margins. Consequently, a larger capacitance is needed for stability. For  $V_{OUT} = 3$  V or 3.3 V, a minimum of 2.2 µF is recommended. For worst case,  $V_{OUT} = 1.23$  V (using the ADJ version), a minimum of 3.3 µF is recommended. C<sub>OUT</sub> can be increased without limit and only improves the regulator stability and transient response. Regardless of its value, the output capacitor should have a resonant frequency greater than 500 kHz.

The minimum capacitance values given above are for maximum load current of 100 mA. If the maximum expected load current is less than 100 mA, then lower values of  $C_{OUT}$  can be used. For instance, if  $I_{OUT} < 10$  mA, then only 0.33 µF is required for  $C_{OUT}$ . For  $I_{OUT} < 1$  mA, 0.1 µF is sufficient for stability requirements. Thus, for a worst-case condition of 100-mA load and  $V_{OUT} = V_{REF} = 1.235$  V (representing the highest load current and lowest loop gain), a minimum  $C_{OUT}$  of 3.3 µF is recommended.

For the LP2950/51, no load stability is inherent in the design — a desirable feature in CMOS circuits that are put in standby (such as RAM keep-alive applications). If the LP2951 is used with external resistors to set the output voltage, a minimum load current of 1  $\mu$ A is recommended through the resistor divider.

### 8.2.2.2 Capacitor Types

Most tantalum or aluminum electrolytics are suitable for use at the input. Film-type capacitors also work but at higher cost. When operating at low temperature, care should be taken with aluminum electrolytics, as their electrolytes often freeze at  $-30^{\circ}$ C. For this reason, solid tantalum capacitors should be used at temperatures below  $-25^{\circ}$ C.

Ceramic capacitors can be used, but due to their low ESR (as low as 5 m $\Omega$  to 10 m $\Omega$ ), they may not meet the minimum ESR requirement previously discussed. If a ceramic capacitor is used, a series resistor between 0.1  $\Omega$  to 2  $\Omega$  must be added to meet the minimum ESR requirement. In addition, ceramic capacitors have one glaring disadvantage that must be taken into account — a poor temperature coefficient, where the capacitance can vary significantly with temperature. For instance, a large-value ceramic capacitor ( $\geq 2.2 \ \mu$ F) can lose more than half of its capacitance as temperature rises from 25°C to 85°C. Thus, a 2.2- $\mu$ F capacitor at 25°C drops well below the minimum C<sub>OUT</sub> required for stability as ambient temperature rises. For this reason, select an output capacitor that maintains the minimum 2.2  $\mu$ F required for stability for the entire operating temperature range.

## 8.2.2.3 C<sub>BYPASS</sub>: Noise and Stability Improvement

In the LP2951 device, an external FEEDBACK pin directly connected to the error amplifier noninverting input can allow stray capacitance to cause instability by shunting the error amplifier feedback to GND, especially at high frequencies. This is worsened if high-value external resistors are used to set the output voltage, because a high resistance allows the stray capacitance to play a more significant role; i.e., a larger RC time delay is introduced between the output of the error amplifier and its FEEDBACK input, leading to more phase shift and lower phase margin. A solution is to add a 100-pF bypass capacitor ( $C_{BYPASS}$ ) between OUTPUT and FEEDBACK; because  $C_{BYPASS}$  is in parallel with R1, it lowers the impedance seen at FEEDBACK at high frequencies, in effect offsetting the effect of the parasitic capacitance by providing more feedback at higher frequencies. More feedback forces the error amplifier to work at a lower loop gain, so  $C_{OUT}$  should be increased to a minimum of 3.3 µF to improve the regulator's phase margin.

$C_{BYPASS}$  can be also used to reduce output noise in the LP2951 device. This bypass capacitor reduces the closed loop gain of the error amplifier at the high frequency, so noise no longer scales with the output voltage. This improvement is more noticeable with higher output voltages, where loop gain reduction is greatest. A suitable  $C_{BYPASS}$  is calculated as shown in Equation 2:

$$f_{(CBYPASS)} \simeq 200 \text{ Hz} \rightarrow C_{(BYPASS)} = \frac{1}{2\pi \times \text{R1} \times 200 \text{ Hz}}$$

(2)

17

Submit Documentation Feedback

On the 3-pin LP2950 device, noise reduction can be achieved by increasing the output capacitor, which causes the regulator bandwidth to be reduced, thus eliminating high-frequency noise. However, this method is relatively inefficient, as increasing  $C_{OUT}$  from 1  $\mu$ F to 220  $\mu$ F only reduces the regulator's output noise from 430  $\mu$ V to 160  $\mu$ V (over a 100-kHz bandwidth).

Copyright © 2006–2014, Texas Instruments Incorporated

## Typical Application (continued)

### 8.2.2.4 ESR Range

The regulator control loop relies on the ESR of the output capacitor to provide a zero to add sufficient phase margin to ensure unconditional regulator stability; this requires the closed-loop gain to intersect the open-loop response in a region where the open-loop gain rolls off at 20 dB/decade. This ensures that the phase is always less than 180° (phase margin greater than 0°) at unity gain. Thus, a minimum-maximum range for the ESR must be observed.

The upper limit of this ESR range is established by the fact that an ESR that is too high could result in the zero occurring too soon, causing the gain to roll off too slowly. This, in turn, allows a third pole to appear before unity gain and introduces enough phase shift to cause instability. This typically limits the maximum ESR to approximately 5  $\Omega$ .

Conversely, the lower limit of the ESR range is tied to the fact that an ESR that is too low shifts the zero too far out, past unity gain, which allows the gain to roll off at 40 dB/decade at unity gain, resulting in a phase shift of greater than 180°. Typically, this limits the minimum ESR to approximately 20 m $\Omega$  to 30 m $\Omega$ .

For specific ESR requirements, see *Typical Characteristics*.

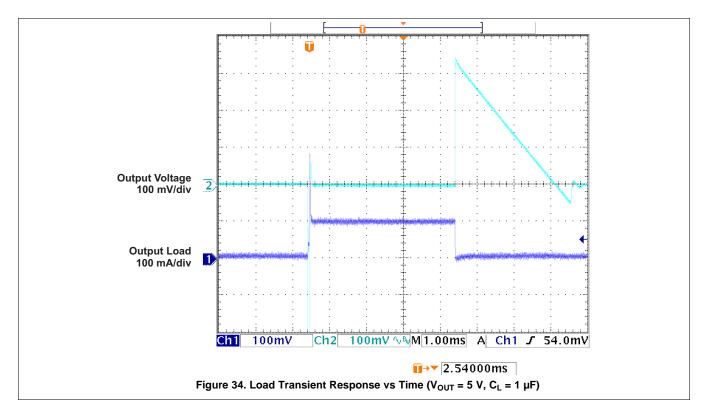

### 8.2.3 Application Curves

## 9 Power Supply Recommendations

Maximum input voltage should be limited to 30 V for proper operation. Place input and output capacitors as close to the device as possible to take advantage of their high frequency noise filtering properties.

## 10 Layout

### 10.1 Layout Guidelines

- Make sure that traces on the input and outputs of the device are wide enough to handle the desired currents. For this device, the output trace will need to be larger in order to accommodate the larger available current.

- Place input and output capacitors as close to the device as possible to take advantage of their high frequency noise filtering properties.

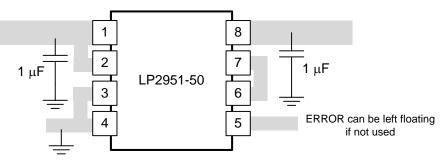

### 10.2 Layout Example

Figure 35. LP2951 Layout Example (D or P Package)

## **11** Device and Documentation Support

### 11.1 Trademarks

All trademarks are the property of their respective owners.

### **11.2 Electrostatic Discharge Caution**

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 11.3 Glossary

## SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## **PACKAGING INFORMATION**

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| LP2950-30LP      | LIFEBUY       | TO-92        | LP                 | 3    | 1000           | RoHS & Green    | SN                                   | N / A for Pkg Type   | -40 to 125   | KY5030                  |         |

| LP2950-30LPR     | LIFEBUY       | TO-92        | LP                 | 3    | 2000           | RoHS & Green    | SN                                   | N / A for Pkg Type   | -40 to 125   | KY5030                  |         |

| LP2950-30LPRE3   | LIFEBUY       | TO-92        | LP                 | 3    | 2000           | RoHS & Green    | SN                                   | N / A for Pkg Type   | -40 to 125   | KY5030                  |         |

| LP2950-33LPE3    | LIFEBUY       | TO-92        | LP                 | 3    | 1000           | RoHS & Green    | SN                                   | N / A for Pkg Type   | -40 to 125   | KY5033                  |         |

| LP2950-33LPRE3   | ACTIVE        | TO-92        | LP                 | 3    | 2000           | RoHS & Green    | SN                                   | N / A for Pkg Type   | -40 to 125   | KY5033                  | Samples |

| LP2950-50LPRE3   | ACTIVE        | TO-92        | LP                 | 3    | 2000           | RoHS & Green    | SN                                   | N / A for Pkg Type   | -40 to 125   | KY5050                  | Samples |

| LP2951-30D       | LIFEBUY       | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | KY5130                  |         |

| LP2951-30DR      | LIFEBUY       | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | KY5130                  |         |

| LP2951-30DRGR    | LIFEBUY       | SON          | DRG                | 8    | 3000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | ZUD                     |         |

| LP2951-33D       | LIFEBUY       | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | KY5133                  |         |

| LP2951-33DR      | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | KY5133                  | Samples |

| LP2951-33DRG4    | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | KY5133                  | Samples |

| LP2951-33DRGR    | ACTIVE        | SON          | DRG                | 8    | 3000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | ZUE                     | Samples |

| LP2951-50D       | LIFEBUY       | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | KY5150                  |         |

| LP2951-50DR      | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | KY5150                  | Samples |

| LP2951-50DRG4    | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | KY5150                  | Samples |

| LP2951-50DRGR    | ACTIVE        | SON          | DRG                | 8    | 3000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | ZUF                     | Samples |

| LP2951D          | LIFEBUY       | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | LP2951                  |         |

| LP2951DR         | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | LP2951                  | Samples |

| LP2951DRG4       | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 125   | LP2951                  | Samples |

<sup>(1)</sup> The marketing status values are defined as follows: **ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF LP2951 :

• Automotive : LP2951-Q1

NOTE: Qualified Version Definitions:

• Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

Texas

STRUMENTS

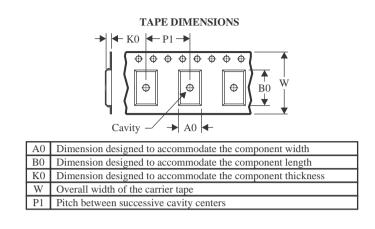

## TAPE AND REEL INFORMATION

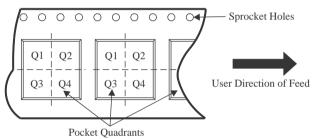

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LP2951-30DR                 | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| LP2951-30DRGR               | SON             | DRG                | 8 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| LP2951-33DRGR               | SON             | DRG                | 8 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| LP2951-50DR                 | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| LP2951-50DRGR               | SON             | DRG                | 8 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| LP2951DR                    | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

Pack Materials-Page 1

LP2951-50DR

LP2951-50DRGR

LP2951DR

www.ti.com

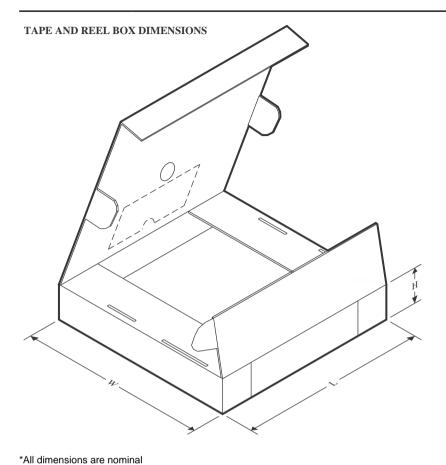

## PACKAGE MATERIALS INFORMATION

Width (mm)

338.1

367.0

367.0

338.1

367.0

338.1

340.5

367.0

340.5

Height (mm)

20.6

35.0

35.0

20.6

35.0

20.6

25-Oct-2023

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) |  |  |  |  |  |

|---------------|--------------|-----------------|------|------|-------------|--|--|--|--|--|

| LP2951-30DR   | SOIC         | D               | 8    | 2500 | 340.5       |  |  |  |  |  |

| LP2951-30DRGR | SON          | DRG             | 8    | 3000 | 367.0       |  |  |  |  |  |

| LP2951-33DRGR | SON          | DRG             | 8    | 3000 | 367.0       |  |  |  |  |  |

D

DRG

D

8

8

8

2500

3000

2500

SOIC

SON

SOIC

Pack Materials-Page 2

## TEXAS INSTRUMENTS

www.ti.com

25-Oct-2023

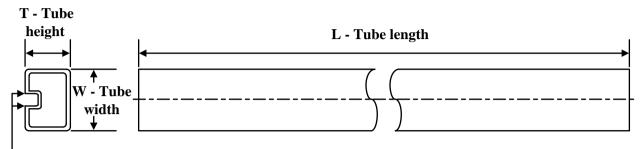

## TUBE

## - B - Alignment groove width

### \*All dimensions are nominal

| Device     | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| LP2951-30D | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| LP2951-33D | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| LP2951-50D | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| LP2951D    | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

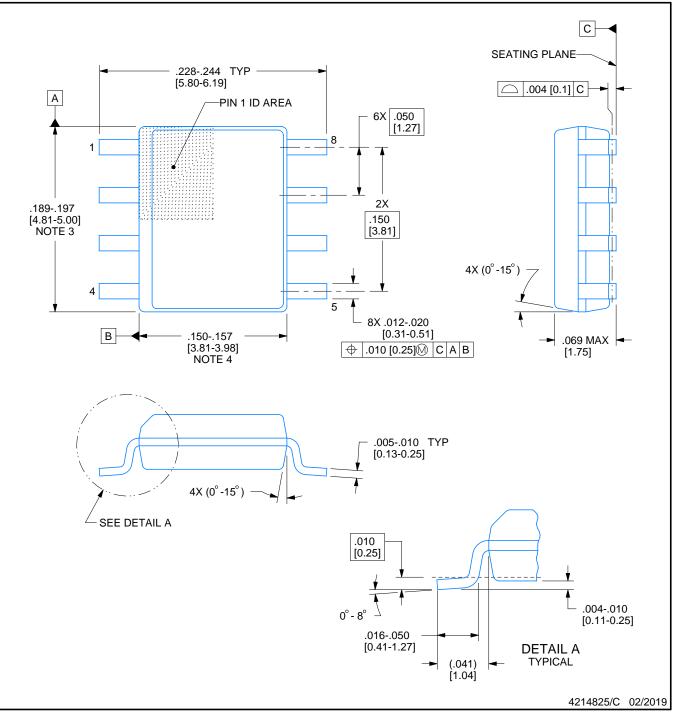

## D0008A

## **PACKAGE OUTLINE**

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

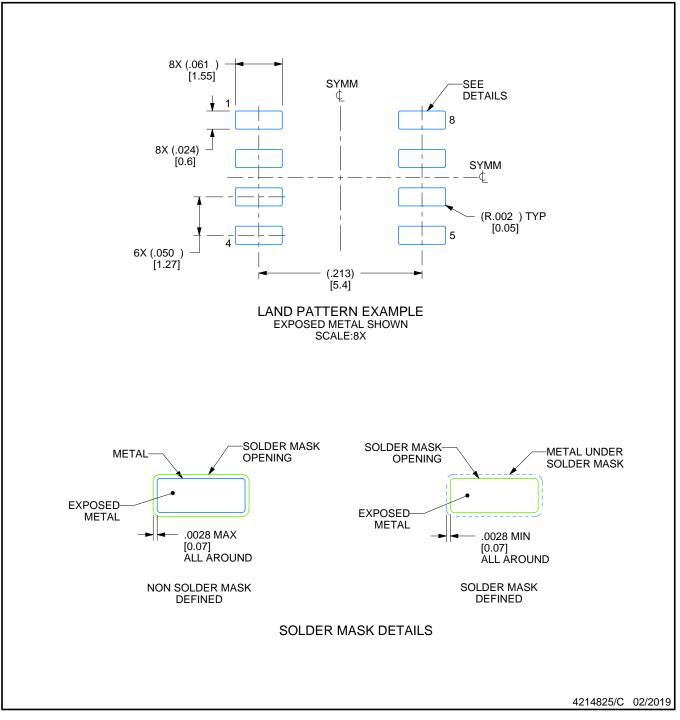

## D0008A

## **EXAMPLE BOARD LAYOUT**

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

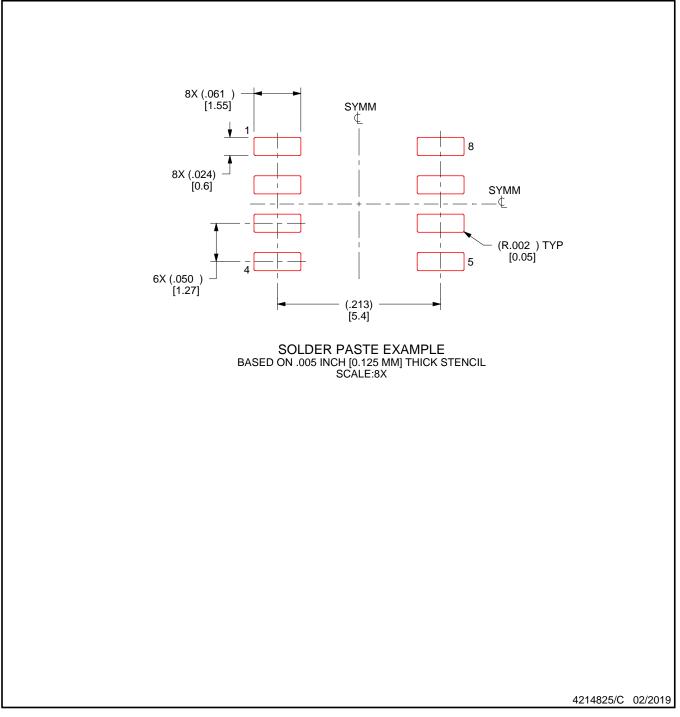

## D0008A

## **EXAMPLE STENCIL DESIGN**

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## **MECHANICAL DATA**

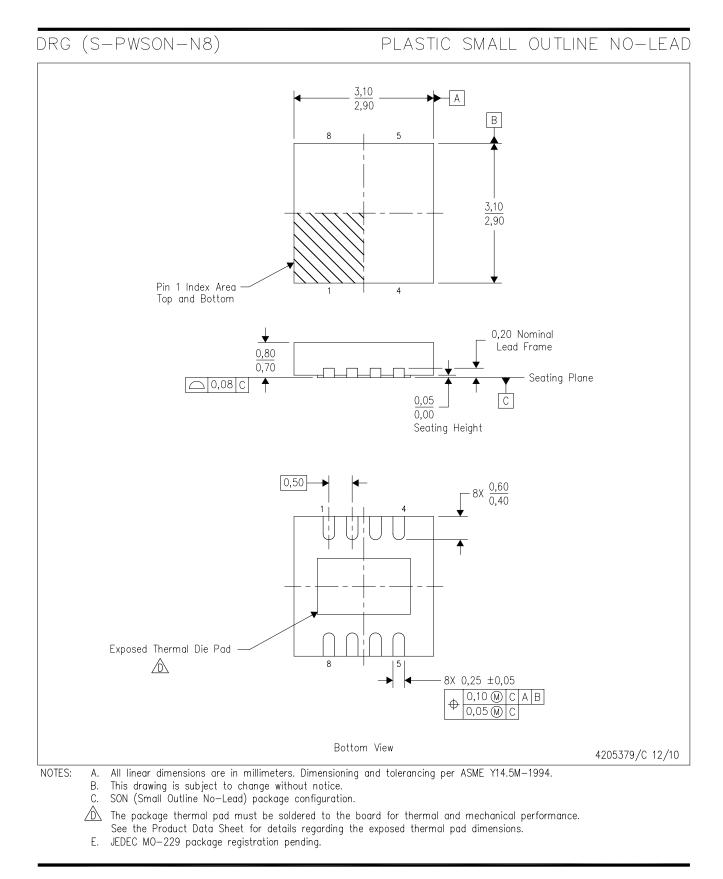

## **DRG0008A**

## **PACKAGE OUTLINE**

## WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

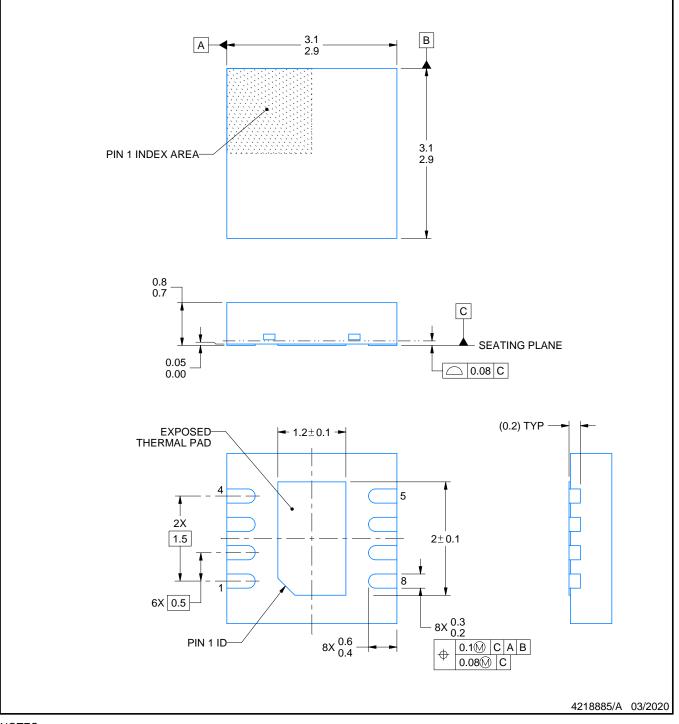

## DRG0008A

## **EXAMPLE BOARD LAYOUT**

## WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

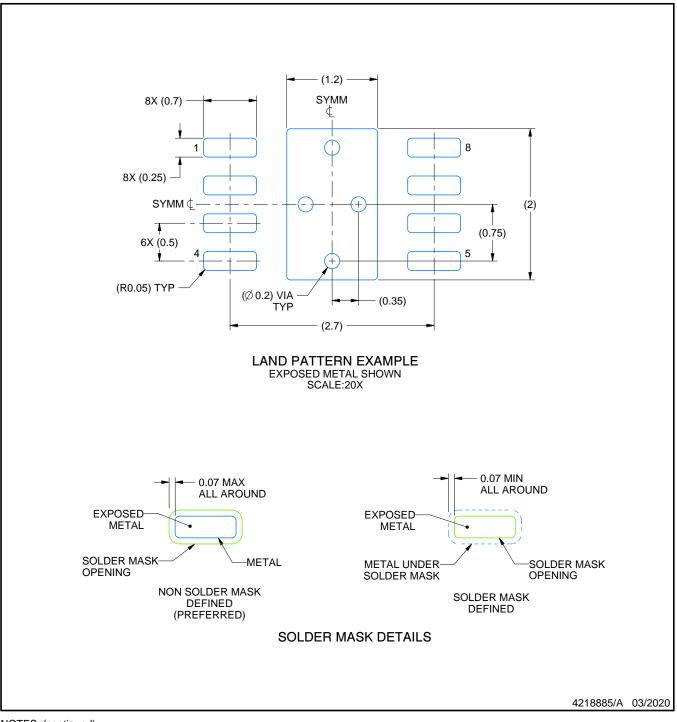

## DRG0008A

## **EXAMPLE STENCIL DESIGN**

## WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## **GENERIC PACKAGE VIEW**

# TO-92 - 5.34 mm max height TRANSISTOR OUTLINE

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4040001-2/F

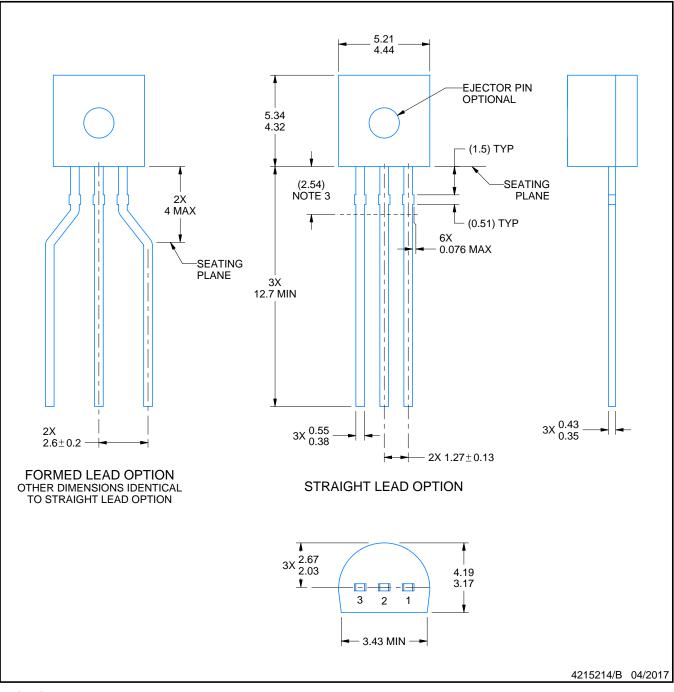

## LP0003A

## **PACKAGE OUTLINE**

## TO-92 - 5.34 mm max height

TO-92

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

- Lead dimensions are not controlled within this area.

Reference JEDEC TO-226, variation AA.

- 5. Shipping method:

- a. Straight lead option available in bulk pack only.b. Formed lead option available in tape and reel or ammo pack.

- c. Specific products can be offered in limited combinations of shipping medium and lead options.

- d. Consult product folder for more information on available options.

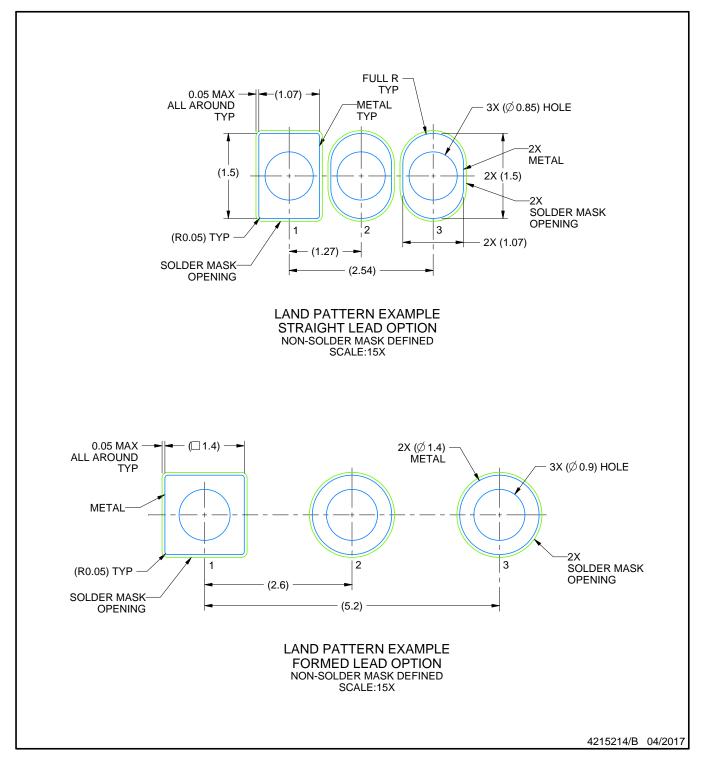

## LP0003A

## **EXAMPLE BOARD LAYOUT**

## TO-92 - 5.34 mm max height

TO-92

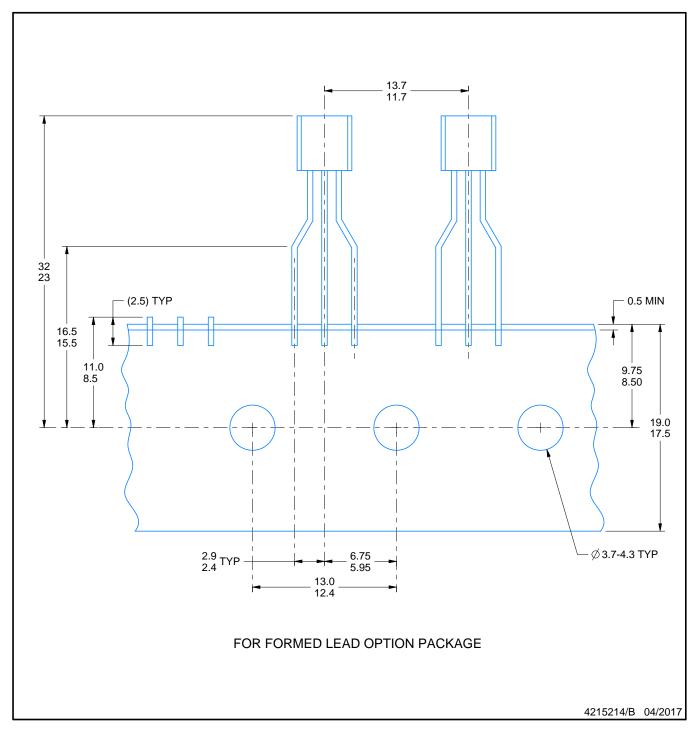

## LP0003A

## TAPE SPECIFICATIONS

## TO-92 - 5.34 mm max height

TO-92

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated 单击下面可查看定价,库存,交付和生命周期等信息

>>TI(德州仪器)