www.ti.com

#### SNOSBJ1E - MAY 1999 - REVISED MARCH 2013

### LM111-N/LM211-N/LM311-N Voltage Comparator

Check for Samples: LM111-N, LM211-N, LM311-N

### FEATURES

- Operates From Single 5V Supply

- Input Current: 150 nA Max. Over Temperature

- Offset Current: 20 nA Max. Over Temperature

- Differential Input Voltage Range: ±30V

- Power Consumption: 135 mW at ±15V

### DESCRIPTION

The LM111-N, LM211-N and LM311-N are voltage comparators that have input currents nearly a thousand times lower than devices like the LM106 or LM710. They are also designed to operate over a wider range of supply voltages: from standard  $\pm$ 15V op amp supplies down to the single 5V supply used for IC logic. Their output is compatible with RTL, DTL and TTL as well as MOS circuits. Further, they can drive lamps or relays, switching voltages up to 50V at currents as high as 50 mA.

Both the inputs and the outputs of the LM111-N, LM211-N or the LM311-N can be isolated from system ground, and the output can drive loads referred to ground, the positive supply or the negative supply. Offset balancing and strobe capability are provided and outputs can be wire OR'ed. Although slower than the LM106 and LM710 (200 ns response time vs 40 ns) the devices are also much less prone to spurious oscillations. The LM111-N has the same pin configuration as the LM106 and LM710.

The LM211-N is identical to the LM111-N, except that its performance is specified over a  $-25^{\circ}$ C to  $+85^{\circ}$ C temperature range instead of  $-55^{\circ}$ C to  $+125^{\circ}$ C. The LM311-N has a temperature range of 0°C to  $+70^{\circ}$ C.

### **Typical Applications**

NOTE

Pin connections shown in Schematic Diagram and Typical Applications are for the LMC TO-99 package.

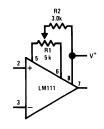

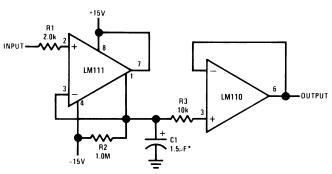

Figure 1. Offset Balancing

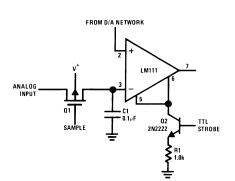

**Do Not** Ground Strobe Pin. Output is turned off when current is pulled from Strobe Pin.

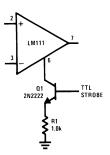

#### Figure 2. Strobing

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

www.ti.com

SNOSBJ1E-MAY 1999-REVISED MARCH 2013

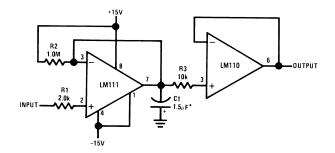

Increases typical common mode slew from 7.0V/µs to 18V/µs.

Figure 3. Increasing Input Stage Current

#### R1 4.5k 4.

Figure 4. Detector for Magnetic Transducer

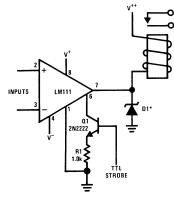

\*Absorbs inductive kickback of relay and protects IC from severe voltage transients on V<sup>++</sup> line. **Do Not** Ground Strobe Pin.

#### Figure 6. Relay Driver with Strobe

\*Solid tantalum

#### Figure 8. Positive Peak Detector

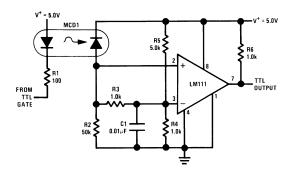

Figure 5. Digital Transmission Isolator

**Do Not** Ground Strobe Pin. Typical input current is 50 pA with inputs strobed off. Pin connections shown in Schematic Diagram and Typical Applications are for the LMC TO-99 package.

# Figure 7. Strobing off Both Input and Output Stages

www.ti.com

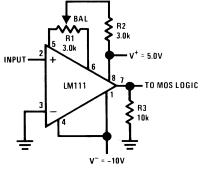

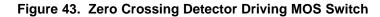

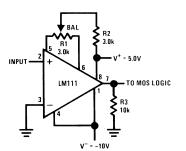

### Figure 9. Zero Crossing Detector Driving MOS Logic

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

SNOSBJ1E-MAY 1999-REVISED MARCH 2013

www.ti.com

STRUMENTS

EXAS

### Absolute Maximum Ratings for the LM111-N/LM211-N<sup>(1)(2)</sup>

| Total Supply Voltage (V <sub>84</sub> ) | 36V                   |                          |                |

|-----------------------------------------|-----------------------|--------------------------|----------------|

| Output to Negative Supply Voltage       | 50V                   |                          |                |

| Ground to Negative Supply Voltage       | (V <sub>14</sub> )    |                          | 30V            |

| Differential Input Voltage              | ±30V                  |                          |                |

| Input Voltage <sup>(3)</sup>            |                       |                          | ±15V           |

| Output Short Circuit Duration           |                       |                          | 10 sec         |

| Operating Temperature Range             |                       | LM111-N                  | -55°C to 125°C |

|                                         |                       | LM211-N                  | −25°C to 85°C  |

| Lead Temperature (Soldering, 10 se      | ec)                   |                          | 260°C          |

| Voltage at Strobe Pin                   |                       |                          | V*-5V          |

| Soldering Information                   | Dual-In-Line Package  | Soldering (10 seconds)   | 260°C          |

|                                         | Small Outline Package | Vapor Phase (60 seconds) | 215°C          |

|                                         |                       | Infrared (15 seconds)    | 220°C          |

| ESD Rating <sup>(4)</sup>               |                       |                          | 300V           |

(1) Refer to RETS111X for the LM111H, LM111J and LM111J-8 military specifications.

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

(3) This rating applies for ±15 supplies. The positive input voltage limit is 30V above the negative supply. The negative input voltage limit is equal to the negative supply voltage or 30V below the positive supply, whichever is less.

(4) Human body model,  $1.5 \text{ k}\Omega$  in series with 100 pF.

### Electrical Characteristics<sup>(1)</sup> for the LM111-N and LM211-N

| Parameter                           | Conditions                                                                                       | Min   | Тур       | Max  | Units |

|-------------------------------------|--------------------------------------------------------------------------------------------------|-------|-----------|------|-------|

| Input Offset Voltage <sup>(2)</sup> | T <sub>A</sub> =25°C, R <sub>S</sub> ≤50k                                                        |       | 0.7       | 3.0  | mV    |

| Input Offset Current                | T <sub>A</sub> =25°C                                                                             |       | 4.0       | 10   | nA    |

| Input Bias Current                  | T <sub>A</sub> =25°C                                                                             |       | 60        | 100  | nA    |

| Voltage Gain                        | T <sub>A</sub> =25°C                                                                             | 40    | 200       |      | V/mV  |

| Response Time <sup>(3)</sup>        | T <sub>A</sub> =25°C                                                                             |       | 200       |      | ns    |

| Saturation Voltage                  | V <sub>IN</sub> ≤−5 mV, I <sub>OUT</sub> =50 mA<br>T <sub>A</sub> =25°C                          |       | 0.75      | 1.5  | V     |

| Strobe ON Current <sup>(4)</sup>    | T <sub>A</sub> =25°C                                                                             |       | 2.0       | 5.0  | mA    |

| Output Leakage Current              | V <sub>IN</sub> ≥5 mV, V <sub>OUT</sub> =35V, T <sub>A</sub> =25°C,<br>I <sub>STROBE</sub> =3 mA |       | 0.2       | 10   | nA    |

| Input Offset Voltage <sup>(2)</sup> | R <sub>S</sub> ≤50 k                                                                             |       |           | 4.0  | mV    |

| Input Offset Current <sup>(2)</sup> |                                                                                                  |       |           | 20   | nA    |

| Input Bias Current                  |                                                                                                  |       |           | 150  | nA    |

| Input Voltage Range                 | V <sup>+</sup> =15V, V <sup>−</sup> =−15V, Pin 7 Pull-Up<br>May Go To 5V                         | -14.5 | 13.8-14.7 | 13.0 | V     |

| Saturation Voltage                  | V <sup>+</sup> ≥4.5V, V <sup>−</sup> =0, V <sub>IN</sub> ≤−6 mV,<br>I <sub>OUT</sub> ≤8 mA       | 0.23  |           | 0.4  | V     |

| Output Leakage Current              | V <sub>IN</sub> ≥5 mV, V <sub>OUT</sub> =35V                                                     |       | 0.1       | 0.5  | μA    |

| Positive Supply Current             | T <sub>A</sub> =25°C                                                                             |       | 5.1       | 6.0  | mA    |

| Negative Supply Current             | T <sub>A</sub> =25°C                                                                             |       | 4.1       | 5.0  | mA    |

(1) These specifications apply for V<sub>S</sub>=±15V and Ground pin at ground, and −55°C≤T<sub>A</sub>≤+125°C, unless otherwise stated. With the LM211-N, however, all temperature specifications are limited to −25°C≤T<sub>A</sub>≤+85°C. The offset voltage, offset current and bias current specifications apply for any supply voltage from a single 5V supply up to ±15V supplies.

(2) The offset voltages and offset currents given are the maximum values required to drive the output within a volt of either supply with a 1 mA load. Thus, these parameters define an error band and take into account the worst-case effects of voltage gain and R<sub>s</sub>.

(3) The response time specified (see definitions) is for a 100 mV input step with 5 mV overdrive.

(4) This specification gives the range of current which must be drawn from the strobe pin to ensure the output is properly disabled. Do not short the strobe pin to ground; it should be current driven at 3 to 5 mA.

SNOSBJ1E - MAY 1999 - REVISED MARCH 2013

#### www.ti.com

### Absolute Maximum Ratings for the LM311-N<sup>(1)(2)</sup>

| Total Supply Voltage (V <sub>84</sub> )              |                          |                                                    |  |  |  |  |  |

|------------------------------------------------------|--------------------------|----------------------------------------------------|--|--|--|--|--|

| Output to Negative Supply Voltage (V <sub>74</sub> ) |                          |                                                    |  |  |  |  |  |

| Ground to Negative Supply Voltage (V <sub>14</sub> ) |                          |                                                    |  |  |  |  |  |

|                                                      |                          | ±30V                                               |  |  |  |  |  |

|                                                      |                          | ±15V                                               |  |  |  |  |  |

| Power Dissipation <sup>(4)</sup>                     |                          |                                                    |  |  |  |  |  |

| ESD Rating <sup>(5)</sup>                            |                          |                                                    |  |  |  |  |  |

| Output Short Circuit Duration                        |                          |                                                    |  |  |  |  |  |

| perature Range                                       |                          | 0° to 70°C                                         |  |  |  |  |  |

|                                                      |                          | -65°C to 150°C                                     |  |  |  |  |  |

|                                                      |                          | 260°C                                              |  |  |  |  |  |

|                                                      |                          | V*-5V                                              |  |  |  |  |  |

| Dual-In-Line Package                                 | Soldering (10 seconds)   | 260°C                                              |  |  |  |  |  |

| Small Outline Package                                | Vapor Phase (60 seconds) | 215°C                                              |  |  |  |  |  |

|                                                      | Infrared (15 seconds)    | 220°C                                              |  |  |  |  |  |

|                                                      |                          | Small Outline Package     Vapor Phase (60 seconds) |  |  |  |  |  |

(1) "Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits."

(2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

(3) This rating applies for ±15V supplies. The positive input voltage limit is 30V above the negative supply. The negative input voltage limit is equal to the negative supply voltage or 30V below the positive supply, whichever is less.

(4) The maximum junction temperature of the LM311-N is 110°C. For operating at elevated temperature, devices in the LMC package must be derated based on a thermal resistance of 165°C/W, junction to ambient, or 20°C/W, junction to case. The thermal resistance of the dual-in-line package is 100°C/W, junction to ambient.

(5) Human body model,  $1.5 \text{ k}\Omega$  in series with 100 pF.

#### Electrical Characteristics <sup>(1)</sup> for the LM311-N

| Parameter                           | Conditions                                                                                                                    | Min   | Тур        | Max  | Units |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|------------|------|-------|--|

| Input Offset Voltage <sup>(2)</sup> | T <sub>A</sub> =25°C, R <sub>S</sub> ≤50k                                                                                     |       | 2.0        | 7.5  | mV    |  |

| Input Offset Current <sup>(2)</sup> | T <sub>A</sub> =25°C                                                                                                          |       | 6.0        | 50   | nA    |  |

| Input Bias Current                  | T <sub>A</sub> =25°C                                                                                                          |       | 100        | 250  | nA    |  |

| Voltage Gain                        | T <sub>A</sub> =25°C                                                                                                          | 40    | 200        |      | V/mV  |  |

| Response Time <sup>(3)</sup>        | T <sub>A</sub> =25°C                                                                                                          |       | 200        |      | ns    |  |

| Saturation Voltage                  | V <sub>IN</sub> ≤−10 mV, I <sub>OUT</sub> =50 mA ,<br>T <sub>A</sub> =25°C                                                    |       | 0.75       | 1.5  | V     |  |

| Strobe ON Current <sup>(4)</sup>    | T <sub>A</sub> =25°C                                                                                                          |       | 2.0        | 5.0  | mA    |  |

| Output Leakage Current              | V <sub>IN</sub> ≥10 mV, V <sub>OUT</sub> =35V T <sub>A</sub> =25°C,<br>I <sub>STROBE</sub> =3 mA V <sup>−</sup> = Pin 1 = −5V |       | 0.2        | 50   | nA    |  |

| Input Offset Voltage <sup>(2)</sup> | R <sub>S</sub> ≤50K                                                                                                           |       |            | 10   | mV    |  |

| Input Offset Current <sup>(2)</sup> |                                                                                                                               |       |            | 70   | nA    |  |

| Input Bias Current                  |                                                                                                                               |       |            | 300  | nA    |  |

| Input Voltage Range                 |                                                                                                                               | -14.5 | 13.8,-14.7 | 13.0 | V     |  |

| Saturation Voltage                  | v <sup>+</sup> ≥4.5V, V <sup>−</sup> =0, V <sub>IN</sub> ≤−10 mV,<br>I <sub>OUT</sub> ≤8 mA                                   |       | 0.23       | 0.4  | V     |  |

| Positive Supply Current             | T <sub>A</sub> =25°C                                                                                                          |       | 5.1        | 7.5  | mA    |  |

| Negative Supply Current             | T <sub>A</sub> =25°C                                                                                                          |       | 4.1        | 5.0  | mA    |  |

(1) These specifications apply for  $V_S=\pm 15V$  and Pin 1 at ground, and  $0^{\circ}C < T_A < +70^{\circ}C$ , unless otherwise specified. The offset voltage, offset current and bias current specifications apply for any supply voltage from a single 5V supply up to  $\pm 15V$  supplies.

(2) The offset voltages and offset currents given are the maximum values required to drive the output within a volt of either supply with 1 mA load. Thus, these parameters define an error band and take into account the worst-case effects of voltage gain and R<sub>S</sub>.

(2) The offset voltages and offset currents given are the maximum values required to drive the output within a volt of either supply with 1 mA load. Thus, these parameters define an error band and take into account the worst-case effects of voltage gain and R<sub>S</sub>.

(3) The response time specified (see definitions) is for a 100 mV input step with 5 mV overdrive.

(4) This specification gives the range of current which must be drawn from the strobe pin to ensure the output is properly disabled. Do not short the strobe pin to ground; it should be current driven at 3 to 5 mA.

Copyright © 1999-2013, Texas Instruments Incorporated

www.ti.com

#### SNOSBJ1E-MAY 1999-REVISED MARCH 2013

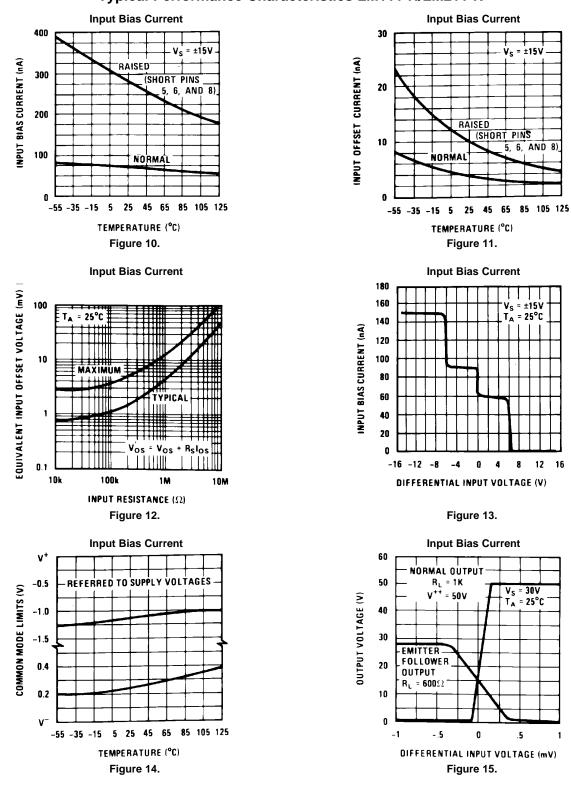

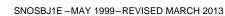

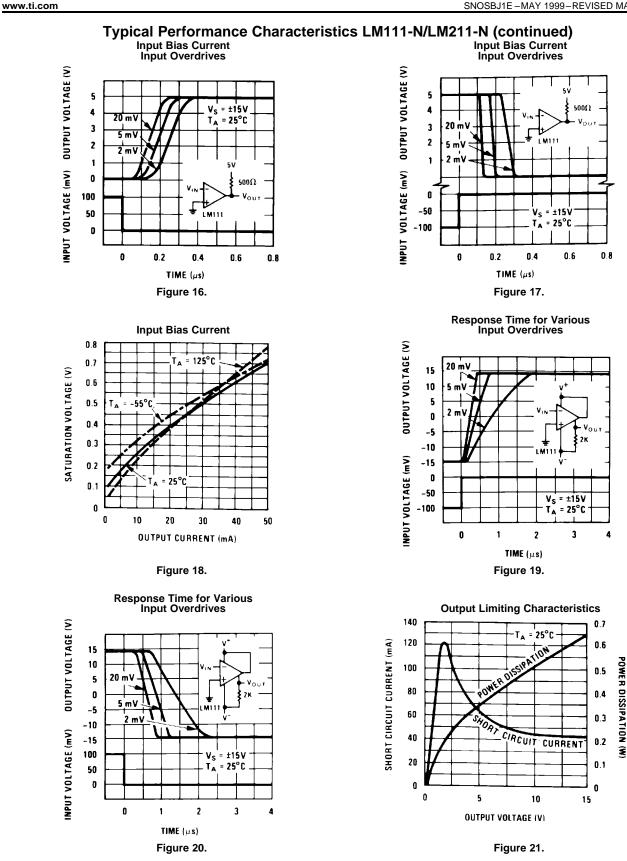

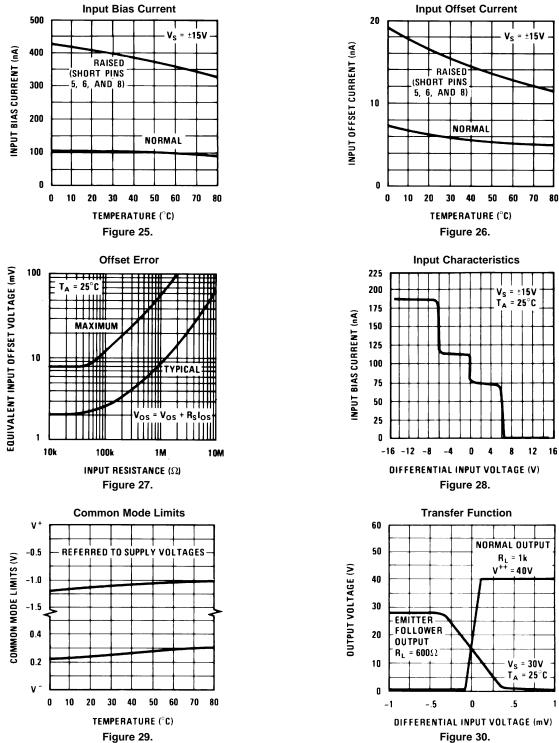

### Typical Performance Characteristics LM111-N/LM211-N

Texas

Instruments

SNOSBJ1E-MAY 1999-REVISED MARCH 2013

Product Folder Links: LM111-N LM211-N LM311-N

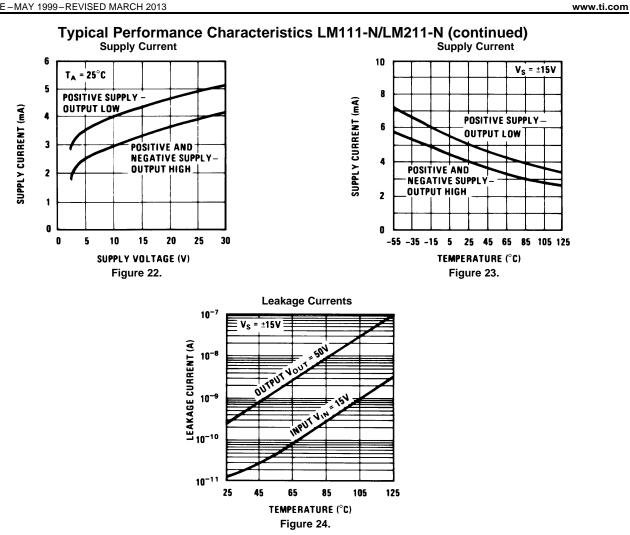

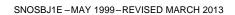

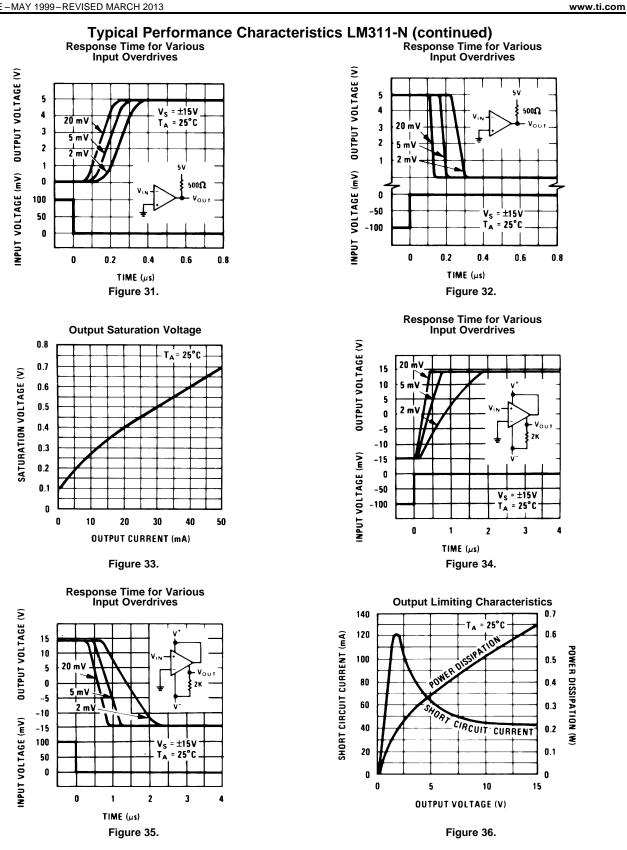

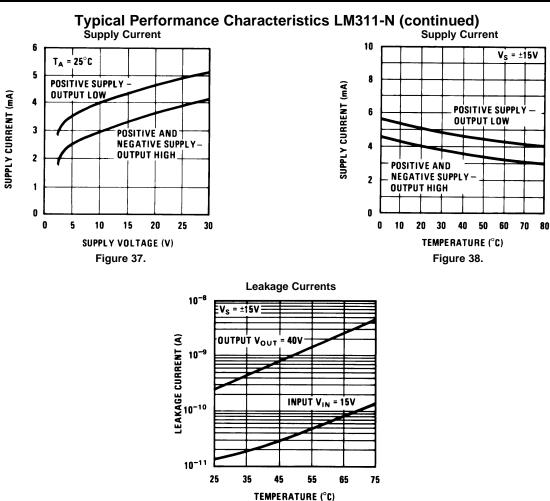

**Typical Performance Characteristics LM311-N**

#### SNOSBJ1E-MAY 1999-REVISED MARCH 2013

SNOSBJ1E - MAY 1999-REVISED MARCH 2013

Figure 39.

Texas

Instruments

Downloaded From Oneyac.com

www.ti.com

### **APPLICATION HINTS**

#### CIRCUIT TECHNIQUES FOR AVOIDING OSCILLATIONS IN COMPARATOR APPLICATIONS

When a high-speed comparator such as the LM111-N is used with fast input signals and low source impedances, the output response will normally be fast and stable, assuming that the power supplies have been bypassed (with 0.1  $\mu$ F disc capacitors), and that the output signal is routed well away from the inputs (pins 2 and 3) and also away from pins 5 and 6.

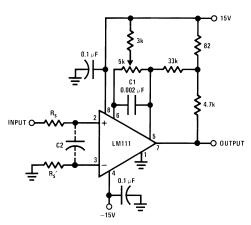

However, when the input signal is a voltage ramp or a slow sine wave, or if the signal source impedance is high (1 k $\Omega$  to 100 k $\Omega$ ), the comparator may burst into oscillation near the crossing-point. This is due to the high gain and wide bandwidth of comparators like the LM111-N. To avoid oscillation or instability in such a usage, several precautions are recommended, as shown in Figure 40 below.

- The trim pins (pins 5 and 6) act as unwanted auxiliary inputs. If these pins are not connected to a trim-pot, they should be shorted together. If they are connected to a trim-pot, a 0.01 µF capacitor C1 between pins 5 and 6 will minimize the susceptibility to AC coupling. A smaller capacitor is used if pin 5 is used for positive feedback as in Figure 40.

- 2. Certain sources will produce a cleaner comparator output waveform if a 100 pF to 1000 pF capacitor C2 is connected directly across the input pins.

- 3. When the signal source is applied through a resistive network, R<sub>S</sub>, it is usually advantageous to choose an R<sub>S</sub>' of substantially the same value, both for DC and for dynamic (AC) considerations. Carbon, tin-oxide, and metal-film resistors have all been used successfully in comparator input circuitry. Inductive wirewound resistors are not suitable.

- 4. When comparator circuits use input resistors (eg. summing resistors), their value and placement are particularly important. In all cases the body of the resistor should be close to the device or socket. In other words there should be very little lead length or printed-circuit foil run between comparator and resistor to radiate or pick up signals. The same applies to capacitors, pots, etc. For example, if R<sub>S</sub>=10 kΩ, as little as 5 inches of lead between the resistors and the input pins can result in oscillations that are very hard to damp. Twisting these input leads tightly is the only (second best) alternative to placing resistors close to the comparator.

- 5. Since feedback to almost any pin of a comparator can result in oscillation, the printed-circuit layout should be engineered thoughtfully. Preferably there should be a groundplane under the LM111-N circuitry, for example, one side of a double-layer circuit card. Ground foil (or, positive supply or negative supply foil) should extend between the output and the inputs, to act as a guard. The foil connections for the inputs should be as small and compact as possible, and should be essentially surrounded by ground foil on all sides, to guard against capacitive coupling from any high-level signals (such as the output). If pins 5 and 6 are not used, they should be shorted together. If they are connected to a trim-pot, the trim-pot should be located, at most, a few inches away from the LM111-N, and the 0.01 μF capacitor should be installed. If this capacitor cannot be used, a shielding printed-circuit foil may be advisable between pins 6 and 7. The power supply bypass capacitors should be located within a couple inches of the LM111-N. (Some other comparators require the power-supply bypass to be located immediately adjacent to the comparator.)

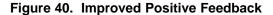

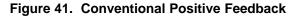

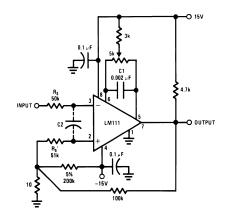

- 6. It is a standard procedure to use hysteresis (positive feedback) around a comparator, to prevent oscillation, and to avoid excessive noise on the output because the comparator is a good amplifier for its own noise. In the circuit of Figure 41, the feedback from the output to the positive input will cause about 3 mV of hysteresis. However, if  $R_S$  is larger than 100 $\Omega$ , such as 50 k $\Omega$ , it would not be reasonable to simply increase the value of the positive feedback resistor above 510 k $\Omega$ . The circuit of Figure 42 could be used, but it is rather awkward. See the notes in paragraph 7 below.

- 7. When both inputs of the LM111-N are connected to active signals, or if a high-impedance signal is driving the positive input of the LM111-N so that positive feedback would be disruptive, the circuit of Figure 40 is ideal. The positive feedback is to pin 5 (one of the offset adjustment pins). It is sufficient to cause 1 to 2 mV hysteresis and sharp transitions with input triangle waves from a few Hz to hundreds of kHz. The positive feedback signal across the 82 $\Omega$  resistor swings 240 mV below the positive supply. This signal is centered around the nominal voltage at pin 5, so this feedback does not add to the V<sub>OS</sub> of the comparator. As much as 8 mV of V<sub>OS</sub> can be trimmed out, using the 5 k $\Omega$  pot and 3 k $\Omega$  resistor as shown.

- 8. These application notes apply specifically to the LM111-N, LM211-N, LM311-N, and LF111 families of comparators, and are applicable to all high-speed comparators in general, (with the exception that not all comparators have trim pins).

www.ti.com

SNOSBJ1E - MAY 1999-REVISED MARCH 2013

Pin connections shown are for LM111H in the LMC hermetic package.

Pin connections shown are for LM111H in the LMC hermetic package.

www.ti.com

SNOSBJ1E-MAY 1999-REVISED MARCH 2013

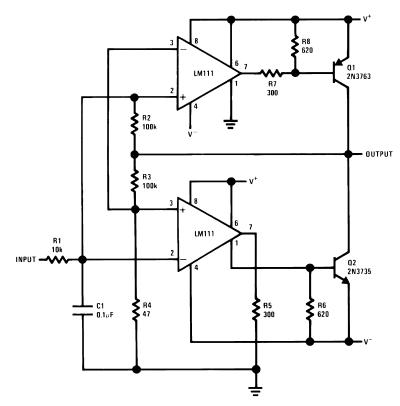

### **Typical Applications**

(Pin numbers refer to LMC package)

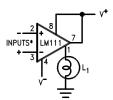

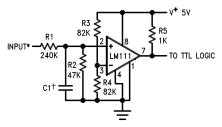

\*TTL or DTL fanout of two

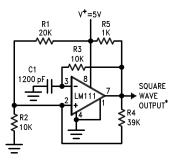

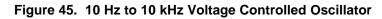

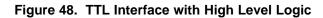

\*Adjust for symmetrical square wave time when  $V_{IN} = 5 \text{ mV}$ †Minimum capacitance 20 pF Maximum frequency 50 kHz

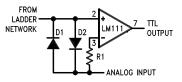

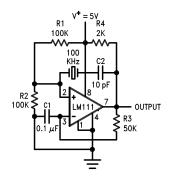

\*Input polarity is reversed when using pin 1 as output.

**XAS**

www.ti.com

STRUMENTS

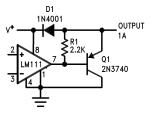

\*Values shown are for a 0 to 30V logic swing and a 15V threshold. †May be added to control speed and reduce susceptibility to noise spikes.

Figure 49. Crystal Oscillator

www.ti.com

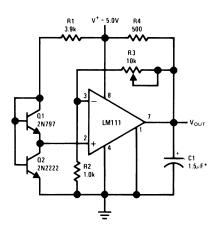

\*Solid tantalum †Adjust to set clamp level

\*Solid tantalum

\*Solid tantalum

Figure 53. Positive Peak Detector

SNOSBJ1E-MAY 1999-REVISED MARCH 2013

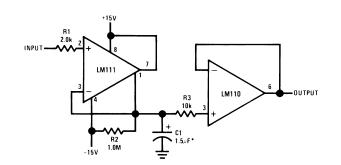

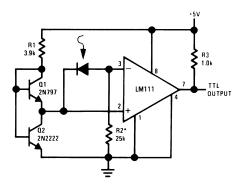

Figure 54. Zero Crossing Detector Driving MOS Logic

\*Solid tantalum

Figure 55. Negative Peak Detector

\*R2 sets the comparison level. At comparison, the photodiode has less than 5 mV across it, decreasing leakages by an order of magnitude.

Figure 56. Precision Photodiode Comparator

www.ti.com

RUMENTS

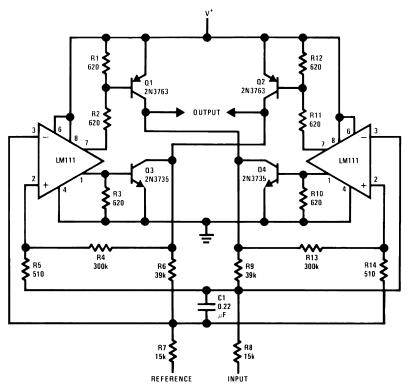

SNOSBJ1E-MAY 1999-REVISED MARCH 2013

www.ti.com

Copyright © 1999–2013, Texas Instruments Incorporated

Product Folder Links: LM111-N LM211-N LM311-N

SNOSBJ1E - MAY 1999-REVISED MARCH 2013

#### www.ti.com

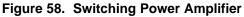

### **Schematic Diagram**

### NOTE

Pin connections shown in the schematic diagram are for the LMC package.

www.ti.com

SNOSBJ1E-MAY 1999-REVISED MARCH 2013

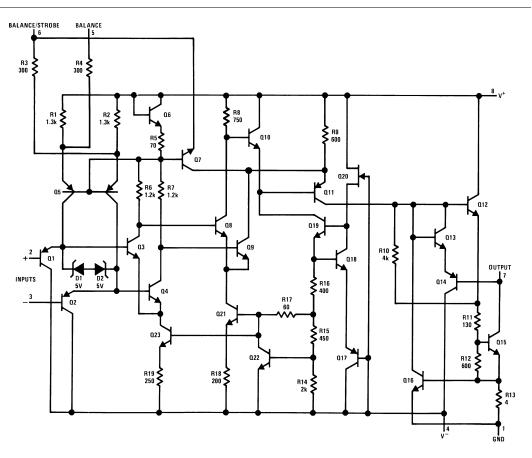

**Pin Diagrams**

INPUT+ OUTPUT INPUT-LM111W NC BALANCE STROBE NC BALANCE ٧-

> Figure 62. LM111W/883, LM111WG/883 10-Pin CLGA (See NAD Package) 10-Pin CLGA (See NAC Package)

SNOSBJ1E-MAY 1999-REVISED MARCH 2013

| REVISION | <b>HISIUKI</b> |

|----------|----------------|

|          |                |

|          |                |

|          |                |

| Cł | nanges from Revision D (March 2013) to Revision E  | Page |

|----|----------------------------------------------------|------|

| •  | Changed layout of National Data Sheet to TI format | 20   |

www.ti.com

### **PACKAGING INFORMATION**

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)     | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|---------------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| LM111 MW8        | ACTIVE        | WAFERSALE    | YS                 | 0    | 1              | RoHS & Green        | Call TI                              | Level-1-NA-UNLIM     | -55 to 125   |                         | Samples |

| LM111H           | ACTIVE        | TO-99        | LMC                | 8    | 500            | Non-RoHS<br>& Green | Call TI                              | Level-1-NA-UNLIM     | -55 to 125   | ( LM111H, LM111H)       | Samples |

| LM111H/NOPB      | ACTIVE        | TO-99        | LMC                | 8    | 500            | RoHS & Green        | Call TI                              | Level-1-NA-UNLIM     | -55 to 125   | ( LM111H, LM111H)       | Samples |

| LM111J-8         | ACTIVE        | CDIP         | NAB                | 8    | 40             | Non-RoHS<br>& Green | Call TI                              | Level-1-NA-UNLIM     | -55 to 125   | LM111J-8                | Samples |

| LM311-MWC        | ACTIVE        | WAFERSALE    | YS                 | 0    | 1              | RoHS & Green        | Call TI                              | Level-1-NA-UNLIM     | -40 to 85    |                         | Samples |

| LM311H           | ACTIVE        | TO-99        | LMC                | 8    | 500            | Non-RoHS<br>& Green | Call TI                              | Level-1-NA-UNLIM     | 0 to 70      | ( LM311H, LM311H)       | Samples |

| LM311H/NOPB      | ACTIVE        | TO-99        | LMC                | 8    | 500            | RoHS & Green        | Call TI                              | Level-1-NA-UNLIM     | 0 to 70      | ( LM311H, LM311H)       | Samples |

| LM311M           | LIFEBUY       | SOIC         | D                  | 8    | 95             | Non-RoHS<br>& Green | Call TI                              | Level-1-235C-UNLIM   | 0 to 70      | LM<br>311M              |         |

| LM311M/NOPB      | ACTIVE        | SOIC         | D                  | 8    | 95             | RoHS & Green        | SN                                   | Level-1-260C-UNLIM   | 0 to 70      | LM<br>311M              | Samples |

| LM311MX          | LIFEBUY       | SOIC         | D                  | 8    | 2500           | Non-RoHS<br>& Green | Call TI                              | Level-1-235C-UNLIM   | 0 to 70      | LM<br>311M              |         |

| LM311MX/NOPB     | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green        | SN                                   | Level-1-260C-UNLIM   | 0 to 70      | LM<br>311M              | Samples |

| LM311N/NOPB      | ACTIVE        | PDIP         | Р                  | 8    | 40             | RoHS & Green        | NIPDAU                               | Level-1-NA-UNLIM     | 0 to 70      | LM<br>311N              | Samples |

<sup>(1)</sup> The marketing status values are defined as follows: **ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

www.ti.com

# PACKAGE OPTION ADDENDUM

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

(3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

Texas Instruments

www.ti.com

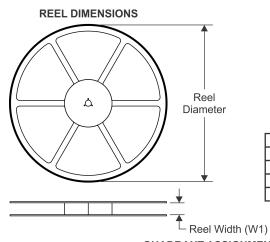

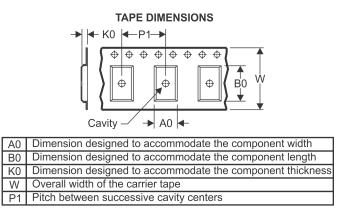

### TAPE AND REEL INFORMATION

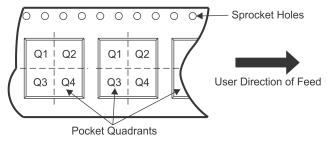

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LM311MX                     | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| LM311MX/NOPB                | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

Pack Materials-Page 1

www.ti.com

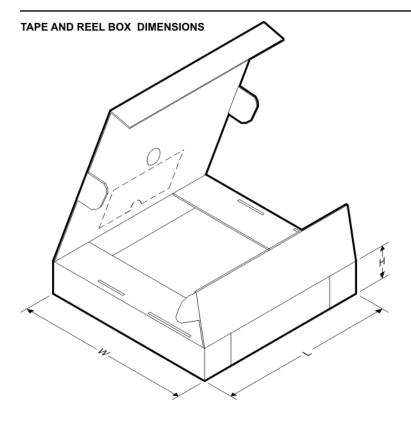

# PACKAGE MATERIALS INFORMATION

11-Feb-2022

\*All dimensions are nominal

| Device       | Package Type Package Drawing |   | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|------------------------------|---|------|------|-------------|------------|-------------|

| LM311MX      | SOIC                         | D | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| LM311MX/NOPB | SOIC                         | D | 8    | 2500 | 367.0       | 367.0      | 35.0        |

Pack Materials-Page 2

www.ti.com

11-Feb-2022

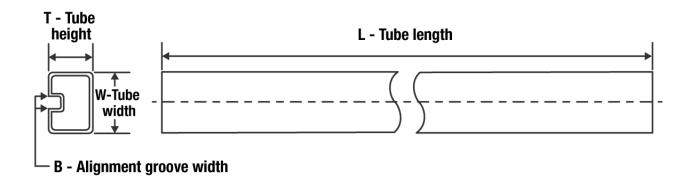

### TUBE

| *All | dimensions | are | nominal |

|------|------------|-----|---------|

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| LM111J-8    | NAB          | CDIP         | 8    | 40  | 502    | 14     | 11938  | 4.32   |

| LM311M      | D            | SOIC         | 8    | 95  | 495    | 8      | 4064   | 3.05   |

| LM311M      | D            | SOIC         | 8    | 95  | 495    | 8      | 4064   | 3.05   |

| LM311M/NOPB | D            | SOIC         | 8    | 95  | 495    | 8      | 4064   | 3.05   |

| LM311N/NOPB | Р            | PDIP         | 8    | 40  | 502    | 14     | 11938  | 4.32   |

Pack Materials-Page 3

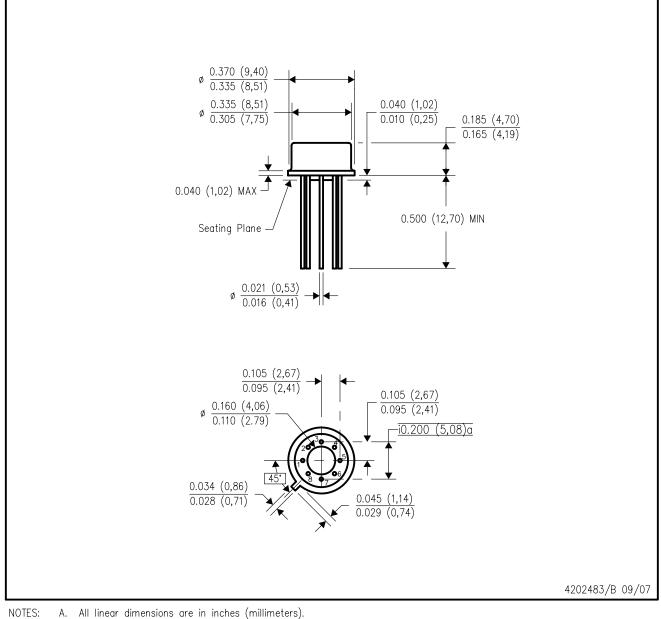

LMC (O-MBCY-W8)

### METAL CYLINDRICAL PACKAGE

- - Β. This drawing is subject to change without notice.

- Leads in true position within 0.010 (0,25) R @ MMC at seating plane. C.

- D. Pin numbers shown for reference only. Numbers may not be marked on package.

- E. Falls within JEDEC MO-002/TO-99.

# MECHANICAL DATA

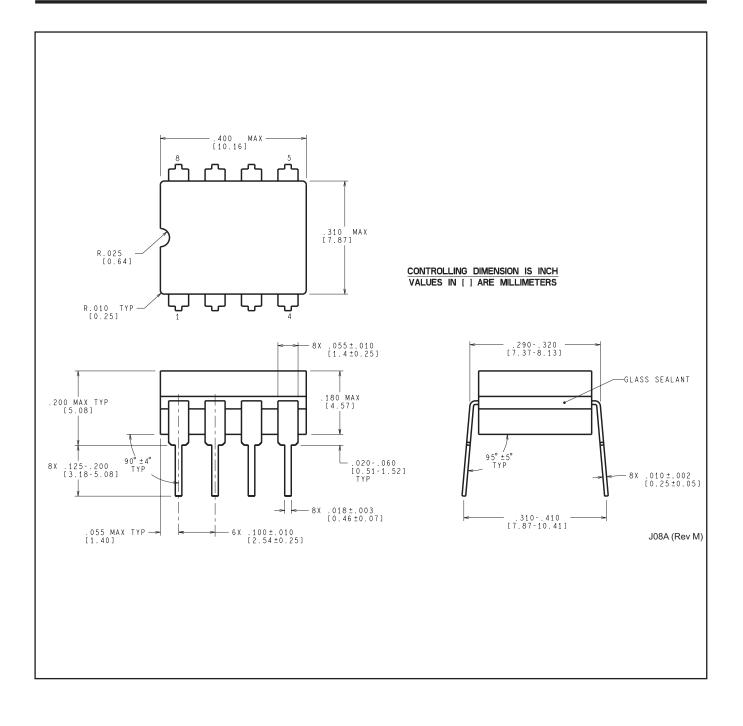

# NAB0008A

P (R-PDIP-T8)

PLASTIC DUAL-IN-LINE PACKAGE

- A. All linear dimensions are in inches (millimeters).B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001 variation BA.

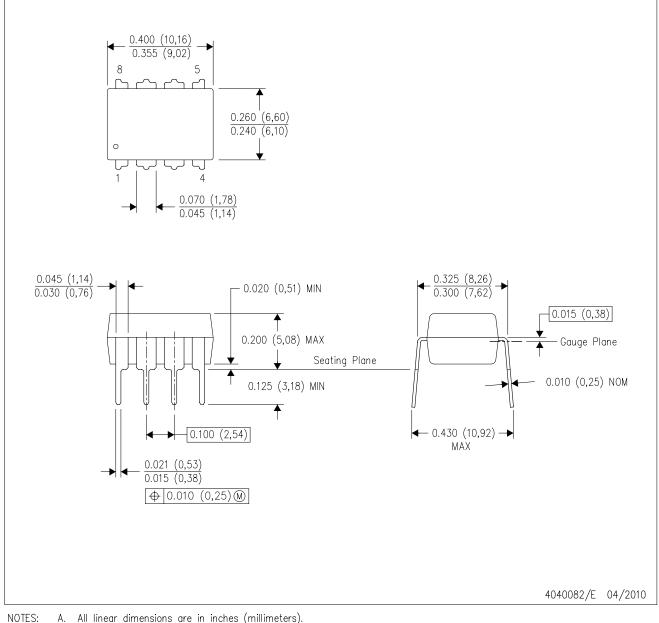

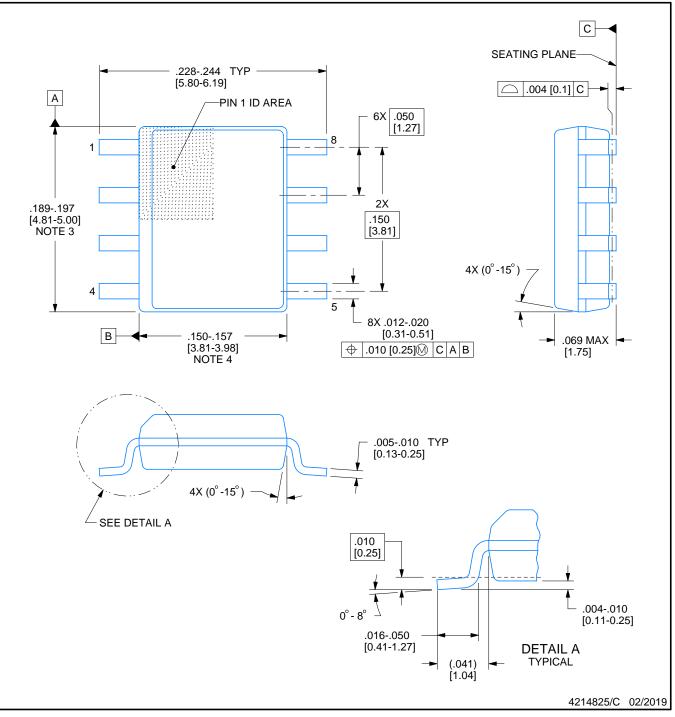

# D0008A

# **PACKAGE OUTLINE**

### SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

# D0008A

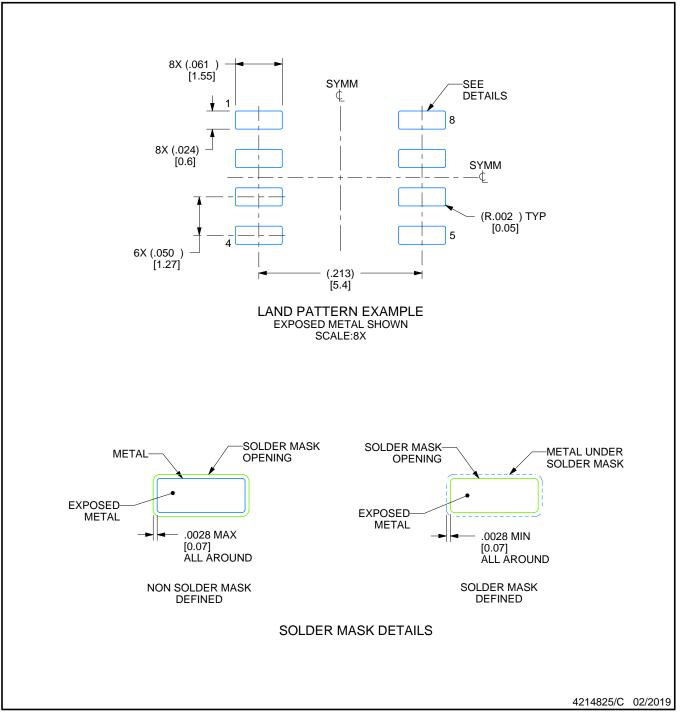

# **EXAMPLE BOARD LAYOUT**

### SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# D0008A

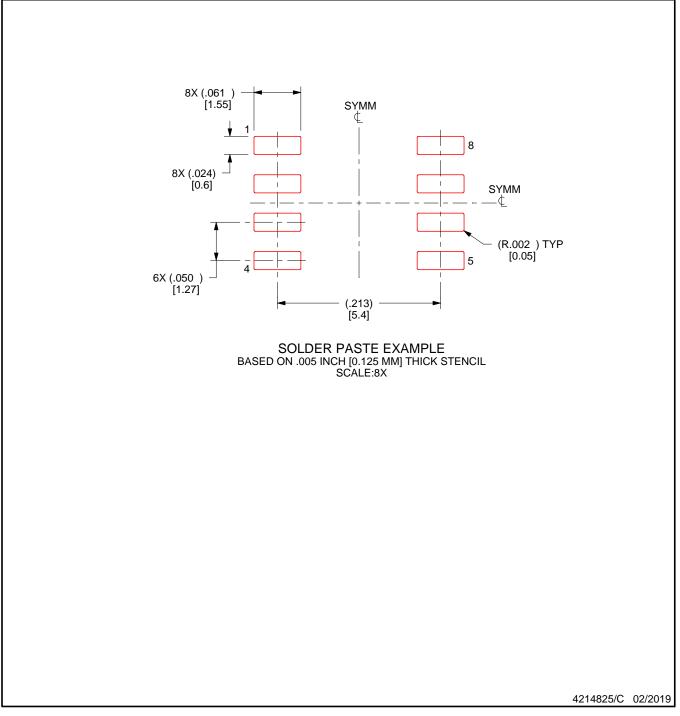

# **EXAMPLE STENCIL DESIGN**

### SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated 单击下面可查看定价,库存,交付和生命周期等信息

>>TI(德州仪器)