DS110DF111

SNLS461A -MAY 2013-REVISED JUNE 2015

# DS110DF111 Low-Power, Multirate, 2-Channel Retimer

### **Features**

- Pin-Compatible Retimer Family

- DS110DF111 With DFE: 8.5 to 11.3 Gbps

- DS125DF111 With DFE: 9.8 to 12.5 Gbps

- Adaptive CTLE Up to 34 dB Boost at 5.65 GHz

- Self-Tuning 5-Tap DFE

- Raw Equalized and Retimed Data Loopback

- Adjustable Transmit V<sub>OD</sub>: 600 to 1300 mVp-p

- Settable TX De-Emphasis Driver 0 to -12 dB

- Low Power Consumption: 200 mW/Channel

- Locks to Half, Quarter, and Eighth Data Rates for Legacy Support

- On-Chip Eye Monitor (EOM), PRBS Generator

- Input Signal Detection, CDR Lock Detection/Indicator

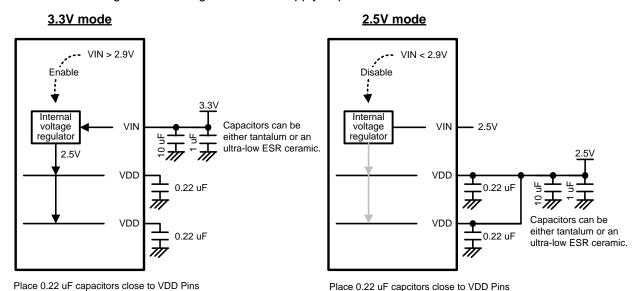

- Single 3.3-V or 2.5-V ±5% Power Supply

- SMBus, EEPROM, or Pin-Based Configuration

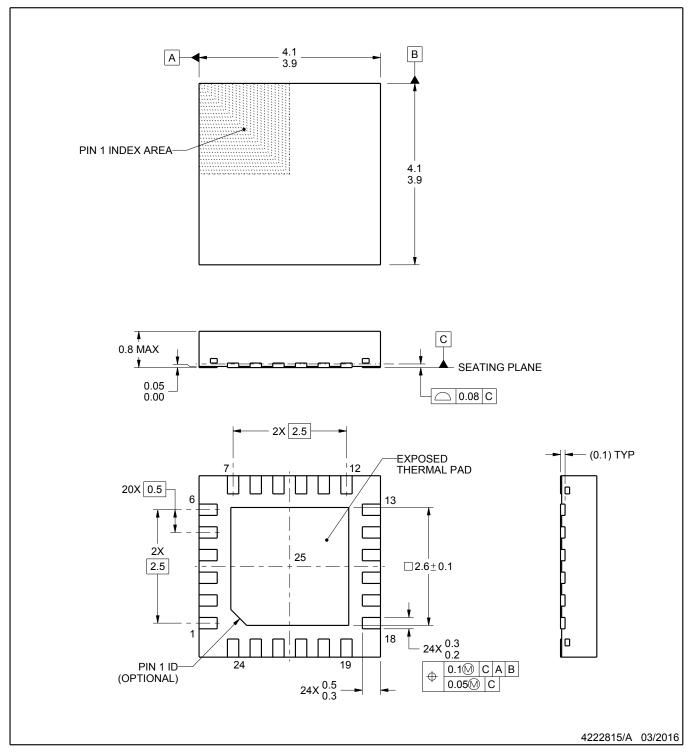

- 4.0-mm × 4.0-mm, 24-Pin QFN Package

- Operating Temp Range: -40°C to 85°C

# **Applications**

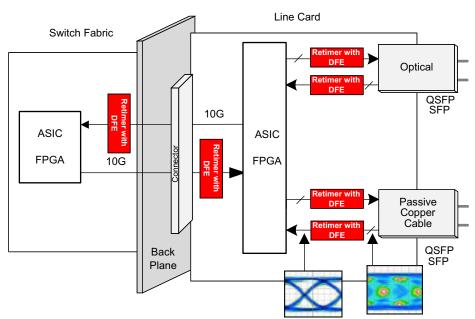

- Front Port Optical Interconnects

- SFF-8431

- 10G/1G Ethernet

- **CPRI**

# 3 Description

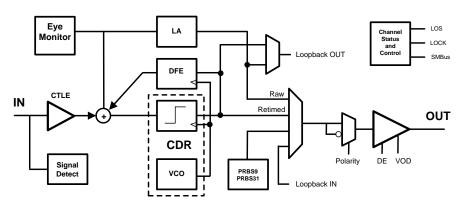

DS110DF111 is dual-channel а bidirectional) retimer with integrated signal conditioning. The DS110DF111 includes an input Continuous-Time Linear Equalizer (CTLE), clock and data recovery (CDR), and transmit driver on each channel.

The DS110DF111 with its on-chip Decision Feedback Equalizer (DFE) can enhance the reach and robustness of long, lossy, cross-talk-impaired high speed serial links to achieve BER < 1x10<sup>-15</sup>. For lessdemanding applications and interconnects, the DFE can be switched off and achieve the same BER performance. The DS125DF111 and DS110DF111 devices are pin-compatible.

Each channel of the DS110DF111 independently locks to serial data at data rates from 8.5 to 11.3 Gbps or to any supported subrate of these data rates. This simplifies system design and lowers overall cost.

Programmable transmit de-emphasis driver offers precise settings to meet the SFF-8431 output eye template. The fully adaptive receive equalization (CTLE and DFE) enables longer transmission in lossy copper interconnect and backplanes with multiple connectors. The CDR function is ideal for use in front port parallel optical module applications to reset the jitter budget and retime high-speed serial data.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM) |

|-------------|-----------|-----------------|

| DS110DF111  | WQFN (24) | 4.0 mm × 4.0 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

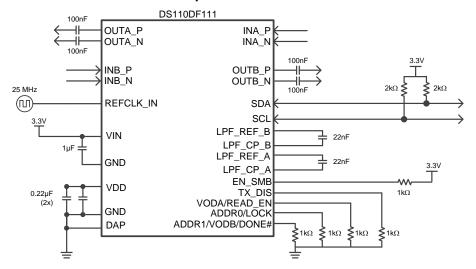

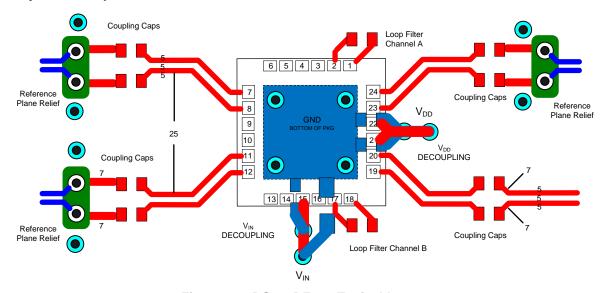

### Simplified Schematic

# **Table of Contents**

| 1 | Features 1                           |    | 7.5 Programming                      |    |

|---|--------------------------------------|----|--------------------------------------|----|

| 2 | Applications 1                       |    | 7.6 Register Maps                    |    |

| 3 | Description 1                        | 8  | Applications and Implementation      | 43 |

| 4 | Revision History2                    |    | 8.1 Application Information          | 43 |

| 5 | Pin Configuration and Functions3     |    | 8.2 Typical Application              | 4  |

| 6 | Specifications5                      | 9  | Power Supply Recommendations         | 4  |

| · | 6.1 Absolute Maximum Ratings 5       | 10 | Layout                               | 40 |

|   | 6.2 ESD Ratings                      |    | 10.1 Layout Guidelines               | 40 |

|   | 6.3 Recommended Operating Conditions |    | 10.2 Layout Example                  | 40 |

|   | 6.4 Thermal Information              | 11 | Device and Documentation Support     | 47 |

|   | 6.5 Electrical Characteristics       |    | 11.1 Documentation Support           | 4  |

|   | 6.6 Typical Characteristics9         |    | 11.2 Community Resources             | 4  |

| 7 | Detailed Description                 |    | 11.3 Trademarks                      | 4  |

| • | 7.1 Overview                         |    | 11.4 Electrostatic Discharge Caution | 4  |

|   | 7.2 Functional Block Diagram         |    | 11.5 Glossary                        | 4  |

|   | 7.3 Feature Description              | 12 | Mechanical, Packaging, and Orderable |    |

|   | 7.4 Device Functional Modes          |    | Information                          | 4  |

# 4 Revision History

## Changes from Original (May 2013) to Revision A

Page

Added Pin Configuration and Functions section, Handling Rating table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section \_\_\_\_\_\_1

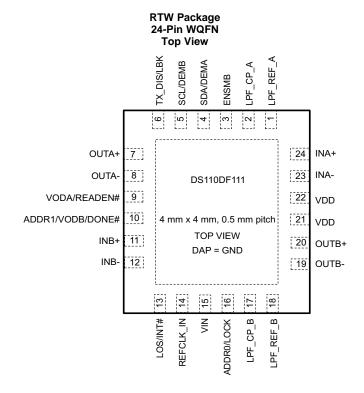

# 5 Pin Configuration and Functions

### **Pin Functions**

| PIN                          |        | TVDE        | DESCRIPTION                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|------------------------------|--------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME                         | NUMBER | TYPE        | DESCRIPTION                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| HIGH SPEED DIFFERENTIAL I/OS |        |             |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| OUTA±                        | 7, 8   | O, CML      | Inverting and noninverting CML-compatible differential outputs. Outputs require AC coupling                                                                                                                                                                                   |  |  |  |  |  |

| OUTB±                        | 20, 19 | O, CML      | Inverting and noninverting CML-compatible differential outputs. Outputs require AC coupling                                                                                                                                                                                   |  |  |  |  |  |

| INA±                         | 24, 23 | I, CML      | Inverting and noninverting CML-compatible differential inputs. An on-chip 100 Ohm terminating resistor connects INA+ to INA-Inputs require AC coupling. TI recommends 100 nF capacitors. Note that for SFP+ applications, AC coupling is included as part of the SFP+ module. |  |  |  |  |  |

| INB±                         | 11, 12 | I, CML      | Inverting and noninverting CML-compatible differential inputs. An on-chip 100 Ohm terminating resistor connects INB+ to INB-Inputs require AC coupling. TI recommends 100 nF capacitors. Note that for SFP+ applications, AC coupling is included as part of the SFP+ module. |  |  |  |  |  |

| LOOP FILTER CONNECTI         | ON PIN | •           |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| LPF_CP_A, LPF_REF_A          | 2, 1   | I/O, analog | Loop filter connection, place a 22 nF capacitor in series between LPF_CP_A and LPF_REF_A                                                                                                                                                                                      |  |  |  |  |  |

| LPF_CP_B, LPF_REF_B          | 17, 18 | I/O, analog | Loop filter connection, place a 22 nF capacitor in series between LPF_CP_B and LPF_REF_B                                                                                                                                                                                      |  |  |  |  |  |

| Reference Clock I/O          |        |             |                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| REFCLK_IN                    | 14     | I, LVCMOS   | 25 MHz ±100 ppm clock from external Oscillator                                                                                                                                                                                                                                |  |  |  |  |  |

# Pin Functions (continued)

| PIN                  |                     |                   |                                                                                                                                                                                                                                                                       |  |  |  |

|----------------------|---------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME NUMBER          |                     | TYPE              | DESCRIPTION                                                                                                                                                                                                                                                           |  |  |  |

| INDICATOR PINS       |                     |                   |                                                                                                                                                                                                                                                                       |  |  |  |

| LOCK                 | 16                  | O, LVCMOS         | Goes high when CDR lock is attained on the corresponding channel.  Note that this terminal is shared with strap input functions read at startup                                                                                                                       |  |  |  |

| LOS/INT#             | 13                  | O, OD             | Output is driven LOW when a valid signal is present on CH A. Output is released when signal on CH A is lost (LOS). This output can be redefined as an INT# signal which will be driven LOW if the EOM check returns a value below the HEO/VEO interrupt threshold (1) |  |  |  |

| SMBus MODE PINS      | !                   | *                 |                                                                                                                                                                                                                                                                       |  |  |  |

| ENSMB                | 3                   | I, 4-Level        | System Management Bus (SMBus) enable terminal HIGH = Register Access, SMBus Slave mode FLOAT = SMBus Master read from External EEPROM LOW = External Pin Control Mode                                                                                                 |  |  |  |

| SDA                  | 4                   | I, SMBus<br>O, OD | Data Input / Open Drain Output<br>External pull-up resistor is required. Terminal is 3.3 V LVCMOS<br>tolerant (2)                                                                                                                                                     |  |  |  |

| SCL                  | 5                   | I, SMBus<br>O, OD | Clock input in SMBus slave mode. Can also be an open drain output in SMBus master mode Pin is 3.3 V LVCMOS Tolerant (2)                                                                                                                                               |  |  |  |

| TX_DIS               | 6                   | I, 4-Level        | Disable the OUTB transmitter HIGH = OUTA Enabled/OUTB Disabled FLOAT = Reserved 20K to GND = Reserved LOW = OUTA/OUTB Enabled (normal operation)                                                                                                                      |  |  |  |

| ADDR0                | 16                  | I, LVCMOS         | This pin sets the SMBus address for the retimer. This pin is a strap input. The state is read on power-up to set the SMBus address in SMBus control mode <sup>(2)</sup>                                                                                               |  |  |  |

| ADDR1/DONE#          | 10                  | IO, LVCMOS        | This pin sets the SMBus address for the retimer in SMBus Slave Mode. Goes low to indicate that the SMBus master EEPROM read has been completed in SMBus Master Mode (2)                                                                                               |  |  |  |

| READEN#              | 9                   | I, 4-Level        | Initiates SMBus master EEPROM read. When multiple DS110DS111 are connected to a single EEPROM, the READEN# input can be daisy chained to the DONE# output. In SMBus Slave Mode, pull low to Logic 0 proper register operation (2)                                     |  |  |  |

| PIN CONTROL (ENSMB = | LOW) <sup>(3)</sup> |                   |                                                                                                                                                                                                                                                                       |  |  |  |

| DEMA                 | 4                   | I, 4-Level        | Set CHA output de-emphasis level in pin control mode (2)                                                                                                                                                                                                              |  |  |  |

| DEMB                 | 5                   | I, 4-Level        | Set CHB output de-emphasis level in pin control mode (2)                                                                                                                                                                                                              |  |  |  |

| LBK                  | 6                   | I, 4-Level        | HIGH = INA goes to OUTA, INB goes to OUTB<br>FLOAT = INB goes to OUTA and OUTB<br>20K to GND = INA goes to OUTA and OUTB<br>LOW = INA goes to OUTB, INB goes to OUTA <sup>(2)</sup>                                                                                   |  |  |  |

| VODA                 | 9                   | I, 4-Level        | Set CHA output launch amplitude in pin control mode <sup>(2)</sup>                                                                                                                                                                                                    |  |  |  |

| VODB                 | 10                  | I, 4-Level        | Set CHB output launch amplitude in pin control mode (2)                                                                                                                                                                                                               |  |  |  |

| POWER                |                     |                   |                                                                                                                                                                                                                                                                       |  |  |  |

| VDD                  | 21, 22              | Power             | VDD = 2.5 V ±5% 3.3 V Mode Operation: VDD Supply Output = 2.5 V ±5% 2.5 V Mode Operation: VDD Supply Input = 2.5 V ±5%                                                                                                                                                |  |  |  |

| VIN                  | 15                  | Power             | Regulator Input with Integrated Supply Mode Control 3.3 V Mode Operation: VIN Supply Input = 3.3 V ±10% 2.5 V Mode Operation: VIN Supply Input = 2.5 V ±5%                                                                                                            |  |  |  |

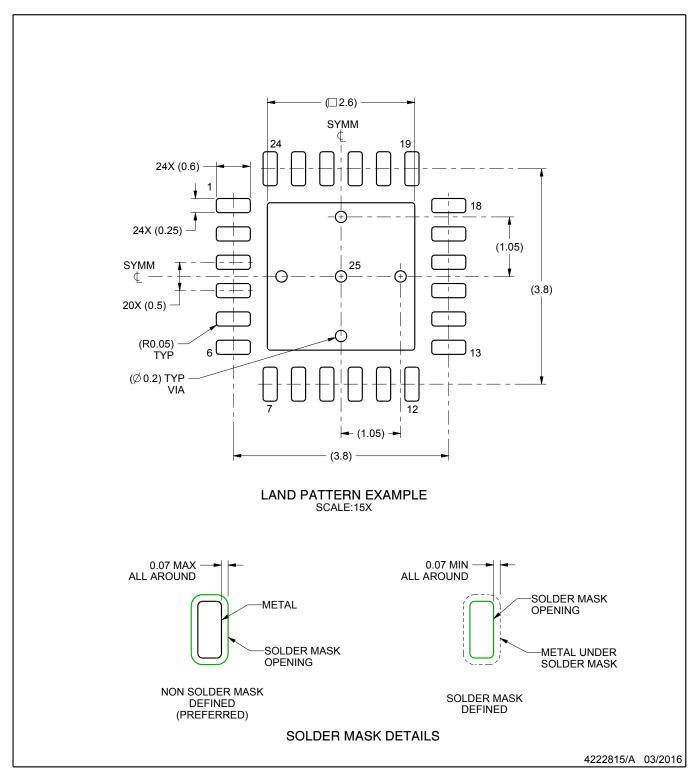

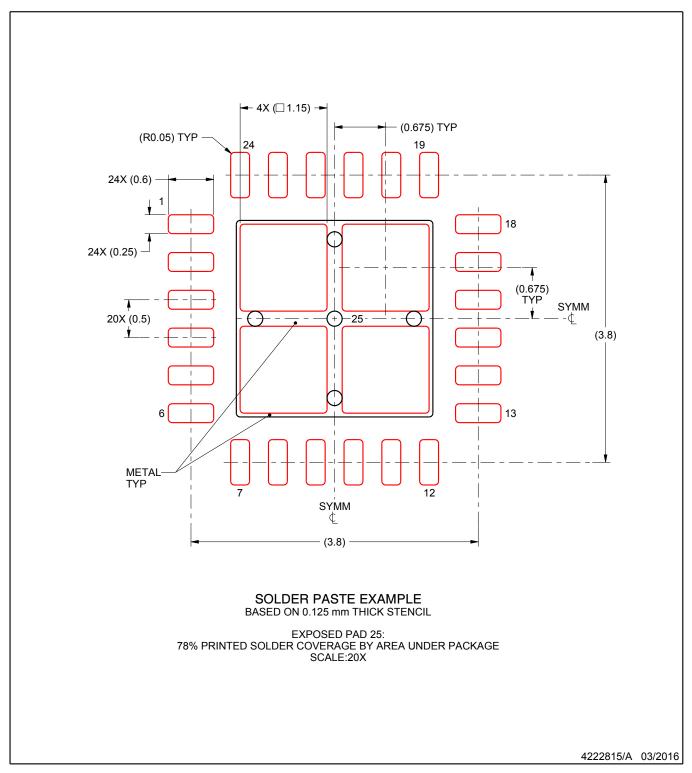

| DAP                  | PAD                 | Power             | Ground reference The exposed pad at the center of the package must be connected to ground plane of the board with at least 4 vias to lower the ground impedance and improve the thermal performance of the package                                                    |  |  |  |

- The LOS/INT# pin is an open drain output which requires external pull-up resistor to 3.3 V to achieve a HIGH level.

- (2)

- This terminal is shared with other functions.

When in pin control mode the DS110DF111 device operates at 1.25 and 10.3125 Gbps and has limited VOD and De-Emphasis control. (3)

## 6 Specifications

# 6.1 Absolute Maximum Ratings<sup>(1)</sup>

|                                      | MIN  | MAX                   | UNIT |

|--------------------------------------|------|-----------------------|------|

| Supply Voltage (V <sub>DD</sub> )    | -0.5 | +2.75                 | V    |

| Supply Voltage (V <sub>IN</sub> )    | -0.5 | +4.0                  | V    |

| LVCMOS Input/Output Voltage          | -0.5 | +4.0                  | V    |

| 4-Level Input Voltage (2.5 V mode)   | -0.5 | +2.75                 | V    |

| 4-Level Input Voltage (3.3 V mode)   | -0.5 | 4.0                   | V    |

| SMBus Input/Output Voltage           | -0.5 | 4.0                   | V    |

| CML Input Voltage                    | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| CML Input Current                    | -30  | +30                   | mA   |

| Storage Temperature T <sub>stg</sub> | -40  | +125                  | °C   |

<sup>(1)</sup> For soldering specifications, see product folder at www.ti.com

## 6.2 ESD Ratings

|                           |                                         | VALUE | UNIT |

|---------------------------|-----------------------------------------|-------|------|

| ESD Rating <sup>(1)</sup> | HBM, STD - JESD22-A114F <sup>(2)</sup>  | ±2500 | V    |

| ESD Raling (*)            | CDM, STD - JESD22-C101-D <sup>(3)</sup> | ±1000 | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges in to the device.

# 6.3 Recommended Operating Conditions

|                     |            | MIN   | NOM | MAX   | UNIT |

|---------------------|------------|-------|-----|-------|------|

| Complex Valtage     | 2.5 V Mode | 2.375 | 2.5 | 2.625 |      |

| Supply Voltage      | 3.3 V Mode | 3.0   | 3.3 | 3.6   | V    |

| Ambient Temperature |            | -40   | 25  | +85   | °C   |

| SMBus (SDA, SCL)    |            | 3.0   | 3.3 | 3.6   | V    |

### 6.4 Thermal Information

|                        |                                              | DS110DF111 |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | WQFN (RTW) | UNIT |

|                        |                                              | 24 PINS    |      |

| $\theta_{JA}$          | Junction-to-ambient thermal resistance       | 35.0       | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 34.0       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 13.4       | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.3        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 13.4       | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 3.3        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.5 Electrical Characteristics

| 6.5 EIE                          | PARAMETER                             | TEST CONDITIONS                                                                                                                | MIN  | TYP  | MAX             | UNIT  |

|----------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------|------|-----------------|-------|

| R_baud                           | Input baud rate                       | Full Rate: DS110DF111                                                                                                          | 8.5  |      | 11.3            | Gbps  |

|                                  | p. or some total                      | Slave Mode Clock Rate                                                                                                          | 100  |      | 400             | po    |

| F <sub>SDC</sub>                 | SMBus Clock Rate                      | Master Mode Clock Rate                                                                                                         | 280  | 400  | 520             | kHz   |

| REFCLK                           | Clock Rate                            | ± 100 ppm                                                                                                                      |      | 25.0 | 020             | MHz   |

|                                  | UPPLY CURRENT                         | _ 100 pp                                                                                                                       |      | 20.0 |                 |       |

|                                  |                                       | 11.3 Gbps : DS110DF111                                                                                                         |      | 170  |                 | mA    |

|                                  |                                       | 11.3 Gbps : DS110DF111                                                                                                         |      |      |                 |       |

|                                  | Current Consumption                   | DFE Disabled                                                                                                                   |      | 150  |                 | mA    |

| I <sub>DD</sub>                  | (Whole Device)                        | Maximum Transient Supply Current<br>Default Settings: CHA and CHB<br>valid input signal detected<br>CHA and CHB acquiring LOCK |      | 235  | 300             | mA    |

|                                  |                                       | 50 Hz to 100 Hz                                                                                                                |      | 100  |                 | mVp-p |

| NTps                             | Supply Noise Tolerance                | 100 Hz to 10 MHz                                                                                                               |      | 40   |                 | mVp-p |

|                                  |                                       | 10 MHz to 5.0 GHz                                                                                                              |      | 10   |                 | mVp-p |

| LVCMOS                           | (LBK, READEN#, DONE#, LOCK)           | ,                                                                                                                              |      |      | •               |       |

| V <sub>IH</sub>                  | High level input voltage              | 2.5 V or 3.3 V Supply Modes                                                                                                    | 1.7  |      | V <sub>IN</sub> | V     |

| $V_{IL}$                         | Low level input voltage               | 2.5 V or 3.3 V Supply Modes                                                                                                    |      |      | 0.7             | V     |

| V <sub>OH</sub>                  | High level output voltage             | $I_{OH} = -3 \text{ mA}$                                                                                                       | 2.0  |      | $V_{IN}$        | V     |

| V <sub>OL</sub>                  | Low level output voltage              | I <sub>OL</sub> = 3 mA                                                                                                         |      |      | 0.4             | V     |

| I <sub>IN</sub>                  | Input leakage current                 | $V_{INPUT} = GND \text{ or } V_{IN}$                                                                                           | -15  |      | +15             | μΑ    |

| 4-LEVEL I                        | NPUTS (ENSMB, DEMA, DEMB, TX_         | DIS, VODA, VODB)                                                                                                               |      |      |                 |       |

| I <sub>IN-R</sub>                | Input leakage current                 | $V_{INPUT} = GND \text{ or } V_{IN}$                                                                                           | -160 |      | +80             | μΑ    |

| OPEN DR                          | AIN (LOS/INT#)                        |                                                                                                                                |      |      |                 |       |

| V <sub>OL</sub>                  | Low level output voltage              | I <sub>OL</sub> = 3 mA                                                                                                         |      |      | 0.4             | V     |

| SIGNAL D                         | ETECT                                 |                                                                                                                                |      |      |                 |       |

| SDH                              | Signal Detect:<br>ON Threshold Level  | Default level to assert<br>Signal Detect, 10.3125 Gbps                                                                         |      | 20   |                 | mVp-p |

| SDL                              | Signal Detect:<br>OFF Threshold Level | Default level to de-assert<br>Signal Detect, 10.3125 Gbps                                                                      |      | 15   |                 | mVp-p |

| CML RX II                        | NPUTS                                 |                                                                                                                                |      |      |                 |       |

| R_Rd                             | DC Input differential Resistance      |                                                                                                                                |      | 100  |                 | Ω     |

|                                  |                                       | SDD11 10 MHz                                                                                                                   |      | -19  |                 |       |

| $RL_{RX-IN}$                     | Input Return-Loss                     | SDD11 2.0 GHz                                                                                                                  |      | -14  |                 | dB    |

|                                  |                                       | SDD11 6.0 - 11.1 GHz                                                                                                           |      | -8   |                 |       |

| V <sub>RX</sub> -                | Source Transmit Signal Level          |                                                                                                                                | 600  |      | 1600            | mVp-p |

| CML TX O                         | UTPUTS                                |                                                                                                                                |      |      |                 |       |

| T_V <sub>DIFF0</sub>             | Output differential voltage           | Default setting, PRBS31                                                                                                        | 400  | 550  | 675             | mVp-p |

| T_V <sub>DIFF7</sub>             | Output differential voltage           | Maximum setting, PRBS31<br>Requires SMBus Control                                                                              | 1000 | 1250 |                 | mVp-p |

| V <sub>OD_DE</sub>               | De-emphasis Level                     | Maximum setting, VOD and DE<br>Requires SMBus Control<br>Input: 10.3125Gbps, 64T pattern                                       |      | -12  |                 | dB    |

| T_Rd                             | DC Output Differential Resistance     |                                                                                                                                |      | 100  |                 | Ω     |

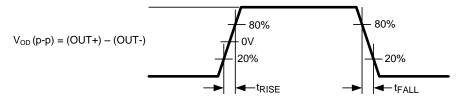

| T <sub>R</sub> /T <sub>F</sub>   | Output Rise/Fall Time                 | Full Slew Rate<br>20% - 80%<br>Input: 10.3125 Gbps, 8T Pattern                                                                 |      | 36   |                 | ps    |

| T <sub>RS</sub> /T <sub>FS</sub> | Output Rise/Fall Time                 | Limited Slew Rate (Reg 0x18)<br>20% - 80%<br>Input: 10.3125 Gbps, 8T Pattern                                                   |      | 50   |                 | ps    |

# **Electrical Characteristics (continued)**

|                     | PARAMETER                                    | TEST CONDITIONS                                                             | MIN TYP    | MAX  | UNIT     |

|---------------------|----------------------------------------------|-----------------------------------------------------------------------------|------------|------|----------|

|                     |                                              | SDD22 10 MHz - 2 GHz                                                        | -19        |      |          |

| T <sub>SDD22</sub>  | Output differential mode return loss         | SDD22 5.5GHz                                                                | -15        |      | dB       |

|                     |                                              | SDD22 11.1GHz                                                               | -11        |      |          |

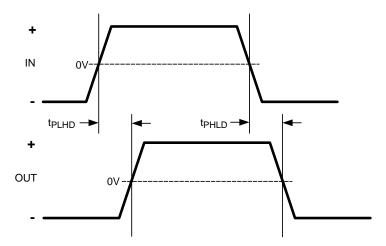

| T <sub>PD</sub>     | Propagation Delay                            | Retimed Data 10.3125 Gbps                                                   | 350        |      | ps       |

| T <sub>PD-RAW</sub> | Propagation Delay                            | Raw Data                                                                    | 200        |      | ps       |

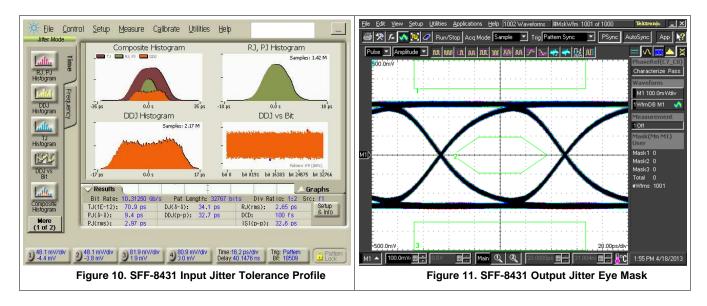

|                     | JITTER SPECS (1)                             |                                                                             |            |      |          |

| T <sub>TJ</sub>     | Total Jitter (1E-12)                         | PRBS7, 10.3125 Gbps                                                         | 7.5        |      | ps       |

| T <sub>RJ</sub>     | Random Jitter                                | PRBS7, 10.3125 Gbps                                                         | 0.33       |      | ps (RMS) |

| T <sub>DJ</sub>     | Deterministic Jitter                         | PRBS7, 10.3125 Gbps                                                         | 3.6        |      | ps       |

|                     | ND DATA RECOVERY                             |                                                                             |            |      |          |

| BW <sub>P LL</sub>  | PLL Bandwidth –3 dB                          | Measured at 10.3125 Gbps                                                    | 5          |      | MHz      |

| J <sub>TOL</sub>    | Total jitter tolerance                       | Jitter per SFF-8431 Appendix D.11<br>Combination of Dj, Pj, and Rj          | > 0.70     |      | UI       |

| T <sub>LOCK1</sub>  | CDR Lock Time                                | Standards Based <sup>(2)</sup>                                              | 10 - 30    |      | ms       |

|                     | CDR Lock                                     | Lock Temperature Range –40°C to 85°C operating range                        | 125        |      | °C       |

| SERIAL B            | JS INTERFACE CHARACTERISTICS                 | 1 0 0                                                                       |            |      |          |

| V <sub>IL</sub>     | Data, Clock Input Low Voltage<br>(SDA / SCL) |                                                                             |            | 0.8  | V        |

| V <sub>IH</sub>     | Data, Clock Input High Voltage (SDA / SCL)   |                                                                             | 2.1        | 3.6  | V        |

| V <sub>HY</sub>     | Input Hystersis                              |                                                                             | >50        |      | mV       |

| V <sub>OL</sub>     | Output Low Voltage                           | SDA or SCL, IOL = 1.25 mA                                                   | 0          | 0.36 | V        |

| I <sub>IN</sub>     | Input Current                                | SDA or SCL, V <sub>INPUT</sub> = V <sub>IN</sub> , V <sub>DD</sub> ,<br>GND | <b>–15</b> | +15  | μΑ       |

| T <sub>R</sub>      | SDA Rise Time, Read Operation                | SDA, RPU = 10K, Cb < 400 pF                                                 | 430        |      | ns       |

| T <sub>F</sub>      | SDA Fall Time, Read Operation                | SDA, RPU = 10K, Cb < 400 pF                                                 | 20         |      | ns       |

| T <sub>SU:DAT</sub> | Setup Time, Read Operation                   | -                                                                           | 560        |      | ns       |

| T <sub>HD;DAT</sub> | Hold Time, Read Operation                    |                                                                             | 615        |      | ns       |

| T <sub>SP</sub>     | Input Filter                                 |                                                                             | 50         |      | ns       |

| C <sub>IN</sub>     | Input Capacitance                            | SDA or SCL                                                                  | < 5        |      | pF       |

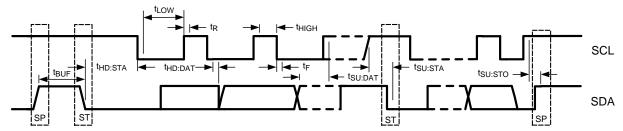

|                     | ENDED TIMING FOR THE SERIAL BU               | S INTERFACE                                                                 |            |      | -        |

| F <sub>SCL</sub>    | SCL Clock Frequency                          |                                                                             |            | 400  | kHz      |

| T <sub>LOW</sub>    | SCL Low Period                               |                                                                             | 1300       |      | ns       |

| T <sub>HIGH</sub>   | SCL High Period                              |                                                                             | 600        |      | ns       |

| T <sub>HD;STA</sub> | Hold Time, Start Operation                   |                                                                             | 600        |      | ns       |

| T <sub>SU;STA</sub> | Setup Time, Start Operation                  |                                                                             | 600        |      | ns       |

| T <sub>HD;DAT</sub> | Data Hold Time                               |                                                                             | 0          | 900  | ns       |

| T <sub>SU;DAT</sub> | Data Set Up Time                             |                                                                             | 100        |      | ns       |

| T <sub>SU;STO</sub> | Set Up Time, Stop Condition                  |                                                                             | 600        |      | ns       |

| T <sub>BUF</sub>    | Bus Free Time<br>Between Stop - Start        |                                                                             | 1300       |      | ns       |

| T <sub>F</sub>      | SCL and SDA, Fall Time                       |                                                                             |            | 300  | ns       |

| T <sub>R</sub>      | SCL and SDA, Rise Time                       |                                                                             |            | 1000 | ns       |

Rj and Dj Jitter decomposition as reported by TEK DSA8200 Sampling scope using a 80E09 Electrical sampling module, 80A06 Pattern trigger, and 82A04 Phase Reference Module.

The typical LOCK time can vary based on data-rate, input channel, and specific DS110DF111 settings.

EEPROM interface requires 520 kHz capable (1 MHz Recommended) EEPROM device.

Figure 1. Output Edge Rate

Figure 2. Propagation Delay

Figure 3. SMBus Timing Diagram

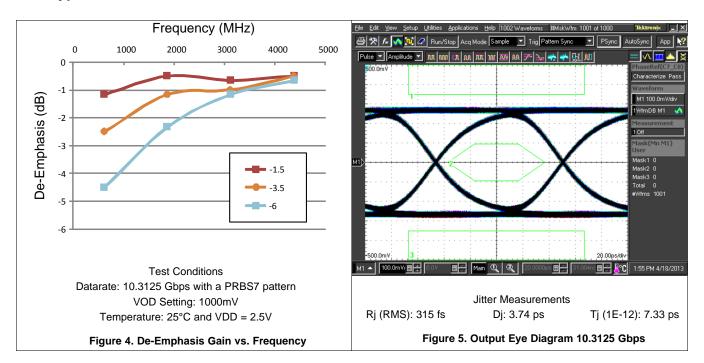

# 6.6 Typical Characteristics

## 7 Detailed Description

#### 7.1 Overview

The DS110DF111 is a low-power, multirate, 2-channel retimer. Both channels operate independently. Each channel includes a Continuous Time Linear Equalizer (CTLE) which compensates for the presence of a dispersive transmission channel between the source and the input of the DS110DF111. Each channel includes an independent Voltage-Controlled Oscillator (VCO) and Phase-Locked Loop (PLL) which produce a clean clock. The clean clock produced by the VCO and the PLL is phase-locked to the incoming data clock, but the high-frequency jitter on the incoming data is attenuated by the PLL, producing a clean clock with substantially reduced jitter. This clean clock is used to retime the incoming data, removing high-frequency jitter from the data stream and producing a data output signal with reduced jitter. This provides the Clock and Data Recovery (CDR) function of the retimer.

Each channel of the DS110DF111 features an output driver with settable differential output voltage and settable output de-emphasis. The output de-emphasis compensates for dispersion in the transmission channel at the output of the DS110DF111.

### 7.2 Functional Block Diagram

Figure 6. DS110DF111 Data Path Block Diagram

### 7.3 Feature Description

### 7.3.1 Device Data Path Operation

The data path operation of the DS110DF111 is shown Figure 6. The functional sections are as follows.

- Input Channel Equalization

- · Clock and Data Recovery

- PRBS Pattern Generator

- Datapath Multiplexer and Output Driver

- Reference Clock

- Control Pins

- Eye Opening Monitor

### 7.3.1.1 Input Channel Equalization

Physical transmission media comprising traces on printed circuit boards (PCBs) or copper cables exhibit a low-pass frequency response characteristic. The magnitude of the high frequency loss varies with the length of the transmission medium and with the loss of the materials which comprise it. This differential high frequency loss and the frequency-dependent group delay of the transmission medium introduce inter-symbol interference in the high-speed broadband signals propagating through the transmission medium.

### **Feature Description (continued)**

To make configuration of these settings easier, the DS110DF111 is designed to determine the correct settings for the CTLE autonomously by automatically adapting these equalizations to the input transmission medium. The automatic adaptation takes place when a signal is first detected at the input to the DS110DF111, immediately after the DS110DF111 acquires phase lock.

The automatic adaptation is also triggered whenever the CDR circuitry is reset. The DS110DF111 uses its internal eye monitor to generate a figure of merit for the adaptation. The DS110DF111 adjusts its CTLE boost settings in a systematic way to optimize this figure of merit. When 8b/10b encoding is used and the input channels has more than 15 dB of loss, the CTLE table and or adaption algorithm needs to be modified so as to prevent CTLE mal-adaption. This scenario occurs when the CTLE boost is insufficient at lower settings to cause regeneration of the high-frequency content of the K28.5 pattern. As boost is increased, the adaption Figure of Merit (FOM) temporarily observes eye closure as the EQ boost begins to restore the high-frequency content. If the FOM does not improve within the look-beyond counter depth, the CTLE will settle at a lower boost, which is insufficient to equalize the signal and provide good BER.

The 5-tap DFE discriminates against input noise and random jitter as well as against crosstalk at the input to the DS110DF111. The DFE tap weights and polarities are adaptive and operate in conjunction with the CTLE to achieve an acceptable BER with more severe channel impairments.

### 7.3.1.2 Clock And Data Recovery

The DS110DF111 performs its clock and data recovery function by detecting the bit transitions in the incoming data stream and locking its internal VCO to the clock represented by the mean arrival times of these bit transitions. This process produces a recovered clock with greatly reduced jitter at jitter frequencies outside the bandwidth of the CDR Phase-Locked Loop (PLL). This is the primary benefit of using the DS110DF111 in a system. It significantly reduces the jitter present in the data stream, in effect resetting the jitter budget for the system.

#### 7.3.1.3 PRBS Pattern Generator

Each channel in the DS110DF111 can be configured to generate and output its own pseudo random bit sequence (PRBS). The DS110DF111 pattern generators support the following PRBS sequences:

- PRBS-9, 2<sup>9</sup> 1

- PRBS-31, 2<sup>31</sup> 1

### 7.3.1.4 Datapath Multiplexer and Output Driver

The DS110DF111 datapath multiplexer is used to control which internal signal will be presented to the output driver block. Inputs to this multiplexer include raw equalized data without clock recovery, retimed data, PRBS patterns, and Loopback data from the other datapath.

The DS110DF111 output driver is used to control specific signal characteristics to enhance transmission quality. The output driver is used to control the following signal features

- Amplitude

- De-Emphasis

- Edge Rate

- Polarity

The DS110DF111 is commonly used in applications where lossy transmission media exist both at the input and the output of the DS110DF111. The CTLE compensates for lossy transmission media at the input to the DS110DF111. The output de-emphasis compensates for the lossy transmission medium at the output of the DS110DF111.

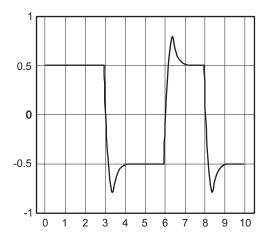

When there is a transition in the output data stream, the output differential voltage reaches its configured maximum value within the configured rise/fall time of the output driver. Following this, the differential voltage rapidly falls off until it reaches the configured VOD level minus the configured de-emphasis level. This accentuates the high-frequency components of the output driver signal at the expense of the low frequency components. The pre-distorted DS110DF111 output signal, with high-frequency components emphasized relative to its low frequency components, exhibits less inter-symbol interference after traveling down a dispersive transmission medium than an undistorted output signal.

## **Feature Description (continued)**

An idealized transmit waveform with analog de-emphasis applied is shown in Figure 7.

Figure 7. Idealized De-Emphasis Waveform

The output driver is capable of driving variable output voltages with variable amounts of analog de-emphasis. The output voltage and de-emphasis level can be configured by writing registers over the SMBus. The DS110DF111 cannot determine independently the appropriate output voltage or de-emphasis setting, so the user is responsible for configuring these parameters. They can be set for each channel independently.

### 7.3.1.5 Reference Clock

A 25 MHz ±100-ppm reference clock is required for proper device operation. The DS110DF111 uses the reference clock to determine when its VCO is properly phase-locked to the incoming data-rate. The DS110DF111 does not include a crystal driver, so a stand-alone external oscillator is required.

The DS110DF111 is set to phase lock to a constrained set of data-rates, the digital circuitry in the device preconfigures the VCO frequency. This enables the DS110DF111 to detect very quickly that a loss of lock has occurred.

The phase noise of the reference clock is not critical. Any commercially-available 25 MHz oscillator (±100 ppm maximum) can provide an acceptable reference clock. The 25-MHz clock high level input voltage must match the VIN level used on the DS110DF111.

# **Feature Description (continued)**

### 7.3.1.6 Control Pins

The 4-level input pins use a resistor divider to help set the 4 valid levels and provide a wider range of control settings when ENSMB=0. There is an internal 30K pull-up and a 60K pull-down connected to the package pin. These resistors, together with the external resistor connection combine to achieve the desired voltage level. Using the 1K pull-up, 1K pull-down, no connect, and 20K pull-down provide the optimal voltage levels for each of the four input states.

Table 1. 4-Level Inputs

| LEVEL | SETTING                | VOLTAGE                 |

|-------|------------------------|-------------------------|

| 0     | 1 K to GND             | 0.1 V                   |

| R     | 20 K to GND            | 0.33 * V <sub>IN</sub>  |

| Float | No connection          | 0.67 * V <sub>IN</sub>  |

| 1     | 1 K to V <sub>IN</sub> | V <sub>IN</sub> - 0.05V |

To minimize the startup current associated with the integrated 2.5-V regulator, the 1 K pull-up and pull-down resistors are recommended. If several 4-level inputs require the same setting, it is possible to combine two or more 1 K resistors into a single lower value resistor. As an example; combining two inputs with a single  $500-\Omega$  resistor is a good way to save board space.

#### 7.3.1.6.1 Pin Mode Limitation

Using the control pins directly does limit the ability of the DS110DF111 CTLE to correctly adapt to high frequency datarates in high loss input channel scenarios. For input channels with more than 15 dB of loss the CTLE Adaption table and or adaption algorithm needs to be modified in the SMBus channel register so as to prevent CTLE mal-adaption. This scenario occurs when the CTLE boost is insufficient at the lowest settings to cause regeneration of the high-frequency content of the K28.5 pattern. As boost is increased, the adaption Figure of Merit (FOM) temporarily observes eye closure as the EQ boost begins to restore the high-frequency content. If the FOM does not improve within the look-beyond counter depth, the CTLE will settle at a lower boost, which is insufficient to equalize the signal and provide good BER. See Table 23 for additional information on CTLE settings and gain levels.

### 7.3.1.7 Eye Opening Monitor

The DS110DF111's Eye Opening Monitor (EOM) measures the internal data eye at the input of the CDR and can be used for 2 functions:

- 1. Horizontal Eye Opening (HEO) and Vertical Eye Opening (VEO) measurement

- 2. Full Eye Diagram Capture

The HEO measurement is made at the 0V crossing and is read in channel register 0x27. The VEO measurement is made at the 0.5 UI mark and is read in channel register 0x28. The HEO and VEO registers can be read from channel registers 0x27 and 0x28 at any time while the CDR is locked. The following equations are used to convert the contents of channel registers 0x27 and 0x28 into their appropriate units:

- HEO [UI] = ch reg 0x27 ÷ 64

- VEO [mV] = ch reg 0x28 x 3.125

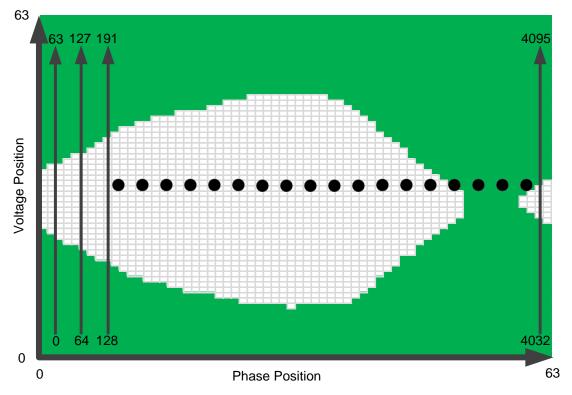

A full eye diagram capture can be performed when the CDR is locked. The eye diagram is constructed within a 64 x 64 array, where each cell in the matrix consists of an 16-bit word. Users can manually adjust the vertical scaling of the EOM or allow the state machine to control the scaling which is the default option. The horizontal scaling controlled by the state machine and is always directly proportional to the data rate.

When a full eye diagram plot is captured, the retimer will shift out 4 16-bit words of junk data that should be discarded followed by 4096 16-bit words that make up the 64 x 64 eye plot. The first actual word of the eye plot from the retimer is for (X, Y) position (0,0). Each time the eye plot data is read out the voltage position is incremented. Once the voltage position has incremented to position 63, the next read will cause the voltage position to reset to 0 and the phase position to increment. This process will continue until the entire 64 x 64 matrix is read out. Figure 8 shows the EOM read out sequence overlaid on top of a simple eye opening plot. In this plot any hits are shown in green. This type of plot is helpful for quickly visualizing the HEO and VEO. Users can apply different algorithms to the output data to plot density or color gradients to the output data.

Figure 8. EOM Full Eye Capture Readout

To manually control the EOM vertical range, remove scaling control from the state machine then select the desired range:

- 1. Channel Reg  $0x2C[6] \rightarrow 0$

- 2. See Table 2

**Table 2. Eye Opening Monitor Vertical Range Settings**

| CHANNEL REG 0x11[7:6] VALUE | EOM VERTICAL RANGE [mV] |

|-----------------------------|-------------------------|

| 2'b00                       | ±100                    |

| 2'b01                       | ±200                    |

| 2'b10                       | ±300                    |

| 2'b11                       | ±400                    |

The EOM operates as an under-sampled circuit. This allows the EOM to be useful in identifying over equalization, ringing and other gross signal conditioning issues. However, the EOM cannot be correlated to a bit error rate.

The EOM can be accessed in two ways to read out the entire eye plot:

- Multi-byte reads can be used such that data is repeatedly latched out from channel register 0x25.

- Or single byte reads. With single byte reads, the MSB are located in register 0x25 and the LSB are located in register 0x26. In this mode, the device must be addressed each time a new byte is read.

To perform a full eye capture with the EOM, follow these steps within the desired channel register set:

**Table 3. Eye Opening Monitor Full Eye Capture Instructions**

| STEP | REGISTER [bits]                            | VALUE            | DESCRIPTION                                                                                                                                                       |  |

|------|--------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1    | 0x3E[7]                                    | 0                | Disable lock EOM lock monitoring                                                                                                                                  |  |

| 2    | 0x2C[6]<br>0x11[7:6]                       | 0<br>2'b         | Set the desired EOM vertical range                                                                                                                                |  |

| 3    | 0x11[5]                                    | 0                | Power on the EOM                                                                                                                                                  |  |

| 4    | 0x24[7]                                    | 1                | Enable fast EOM                                                                                                                                                   |  |

| 5    | 0x24[0]<br>0x25<br>0x26                    | 1                | Begin read out of the 64 x 64 array, discard first 4 words Ch reg 0x24[0] is self clearing. 0x25 is the MSB of the 16-bit word 0x26 is the LSB of the 16-bit word |  |

| 6    | 0x25<br>0x26                               |                  | Continue reading information until the 64 x 64 array is complete.                                                                                                 |  |

| 7    | 0x3E[7]<br>0x2C[6]<br>0x11[5]<br>0x24[7,1] | 1<br>1<br>1<br>0 | Return the EOM to its original state. Undo steps 1-4                                                                                                              |  |

### 7.4 Device Functional Modes

To select different programming device, the ENSMB pin selects the control modes. The DS110DF111device can be programmed using external pin control, a SMBus controller, or through an EEPROM configuration load.

**Table 4. ENSMB Control Description**

| ENSMB PIN | DESCRIPTION       | READEN# Terminal                                                |

|-----------|-------------------|-----------------------------------------------------------------|

| High      | SMBus Slave Mode  | Pull Low to initiate reading configuration data from the EEPROM |

| Float     | SMBus Master Mode | Tie Low to enable proper address strapping on power up          |

| R         | N/A               |                                                                 |

| Low       | Pin Mode Control  | Shared with VODA terminal control function                      |

#### 7.4.1 Control Pin Mode

The 4-level input pins utilize a resistor divider to help set the 4 valid levels and provide a wider range of control settings when ENSMB=0. There is an internal 30K pull-up and a 60K pull-down connected to the package pin. These resistors, together with the external resistor connection combine to achieve the desired voltage level. Using the 1K pull-up, 1K pull-down, no connect, and 20K pull-down provide the optimal voltage levels for each of the four input states.

Table 5. 4-Level Inputs

| LEVEL | SETTING       | VOLTAGE     |

|-------|---------------|-------------|

| 0     | 1K to GND     | 0.1 V       |

| R     | 20K to GND    | 0.33 * VIN  |

| Float | No connection | 0.67 * VIN  |

| 1     | 1K to VIN     | VIN - 0.05V |

Note:  $V_{IN} = 2.5V$  in 2.5V Mode and  $V_{IN} = 3.3V$  in 3.3V Mode

In order to minimize the startup current associated with the integrated 2.5-V regulator the 1K pull-up / pull-down resistors are recommended. If several 4 level inputs require the same setting, it is possible to combine two or more 1K resistors into a single lower value resistor. As an example; combining two inputs with a single 500 Ohm resistor is a good way to save board space.

### 7.4.2 SMBus Master Mode and SMBus Slave Mode

In SMBus master mode the DS110DF111 reads its initial configuration from an external EEPROM upon powerup. The serial EEPROM must support a minimum frequency of 520 KHz. Once the DS110DF111 has finished reading its initial configuration from the external EEPROM in SMBus master mode it reverts to SMBus slave mode and can be further configured by an external controller over the SMBus. Two device pins initiate reading the configuration from the external EEPROM and indicate when the configuration read is complete.

- DONE#

- READEN#

These pins are meant to work together. When the DS110DF111 is powered up in SMBus master mode, it reads its configuration from the external EEPROM. This is triggered when the READEN# pin goes low. When the DS110DF111 is finished reading its configuration from the external EEPROM, it drives its DONE# pin low. In this mode, as the name suggests, the DS110DF111 acts as an SMBus master during the time it is reading its configuration from the external EEPROM. After the DS110DF111 has finished reading its configuration from the EEPROM, it releases control of the SMBus and becomes a SMBus slave. In applications where there is more than one DS110DF111 on the same SMBus, bus contention can result if more than one DS110DF111 tries to take command of the SMBus as the SMBus master at the same time. The READEN# and DONE# pins prevent this bus contention.

In a system where the DS110DF111s are meant to operate in SMBus master mode, the READEN# pin of one retimer should be wired to the DONE# pin of the next. The system should be designed so that the READEN# pin of one (and only one) of the DS110DF111s in the system is driven low on power-up. This DS110DF111 will take command of the SMBus on power-up and will read its initial configuration from the external EEPROM. When it is finished reading its configuration, it will set its DONE# pin low. This pin should be connected to the READEN# pin of another DS110DF111. When this DS110DF111 senses its READEN# pin driven low, it will take command of the SMBus and read its initial configuration from the external EEPROM, after which it will set its DONE# pin low. By connecting the DONE# pin of each DS110DF111 to the READEN# pin of the next DS110DF111, each DS110DF111 can read its initial configuration from the EEPROM without causing bus contention.

For SMBus slave mode, the READEN# pin must be tied LOW. Do not leave it Floating or tie it HIGH.

### 7.5 Programming

#### 7.5.1 SMBus Interface

### 7.5.1.1 Address Lines

In either SMBus mode the DS110DF111 must be assigned a SMBus address. A unique address should be assigned to each device on the SMBus.

The SMBus address is latched into the DS110DF111 on power-up. The address is read in from the state of the ADR[1:0] lines upon power-up. A floating address line input will be interpreted as a logic 0.

The DS110DF111 can be configured with any of 4 SMBus addresses. The SMBus addressing scheme uses the least significant bit of the SMBus address as the Write/Read\_N address bit. When an SMBus device is addressed for writing, this bit is set to 0; for reading, to 1. Table 6 shows the write address setting for the DS110DF111versus the values latched in on the address line at power-up.

## 7.5.1.2 Device Configuration in SMBus Slave Mode

The configurable settings of the DS110DF111 may be set independently for each channel at any time after power up using the SMBus. A register write is accomplished when the controller sends a START condition on the SMBus followed by the Write address of the DS110DF111 to be configured. See Table 6 for the mapping of the address lines to the SMBus Write addresses. After sending the Write address of the DS110DF111, the controller sends the register address byte followed by the register data byte. The DS110DF111 acknowledges each byte written to the controller according to the data link protocol of the SMBus Version 2.0 Specification. See this specification for additional information on the operation of the SMBus.

There are two types of device registers in the DS110DF111. These are the control/shared registers and the channel registers. The control/shared registers control or allow observation of settings which affect the operation of all channels of the DS110DF111. They are also used to select which channel of the device is to be the target channel for reads from and writes to the channel registers.

## **Programming (continued)**

The channel registers are used to set all the configuration settings of the DS110DF111. They provide independent control for each channel of the DS110DF111 for all the settable device characteristics. Any registers not described in the tables that follow should be treated as reserved. The user should not try to write new values to these registers. The user-accessible registers described in the tables that follow provide a complete capability for customizing the operation of the DS110DF111 on a channel-by-channel basis.

### 7.5.1.3 Bit Fields in the Register Set

Many of the registers in the DS110DF111 are divided into bit fields. This allows a single register to serve multiple purposes, which may be unrelated. Often configuring the DS110DF111 requires writing a bit field that makes up only part of a register value while leaving the remainder of the register value unchanged.

## 7.5.1.4 Writing to and Reading From the Control/Shared Registers

Any write operation targeting register 0xff writes to the control/shared register 0xff. This is the only register in the DS110DF111 with an address of 0xff. Bit 2 of register 0xff is used to select either the control/shared register set or a channel register set. If bit 2 of register 0xff is cleared (written with a 0), then all subsequent read and write operations over the SMBus are directed to the control/shared register set. This situation persists until bit 2 of register 0xff is set (written with a 1). There is a register with address 0x00 in the control/shared register set, and there is also a register with address 0x00 in each channel register set. If you read the value in register 0x00 when bit 2 of register 0xff is cleared to 0, then the value returned by the DS110DF111 is the value in register 0x00 when bit 2 of register 0xff is set to 1, then the value returned by the DS110DF111 is the value in register 0x00 of the selected channel register set. The channel register set is selected by bits 1:0 of register 0xff. If bit 3 of register 0xff is set to 1 and bit 2 of register 0xff is also set to 1, then any write operation to any register address will write all the channel register sets in the DS110DF111 simultaneously. This situation will persist until either bit 3 of register 0xff or bit 2 of register 0xff is cleared.

Note that when you write to register 0xff, independent of the current settings in register 0xff, the write operation ALWAYS targets the control/shared register 0xff. This channel select register, register 0xff, is unique in this regard. Table 7 shows the control/shared register set.

# Table 6. SMBus Write Address Assignment<sup>(1)</sup>

| ADDR1 | ADDR0 | SMBus WRITE ADDRESS | SMBus READ ADDRESS |

|-------|-------|---------------------|--------------------|

| 0     | 0     | 0x30                | 0x31               |

| 0     | 1     | 0x32                | 0x33               |

| 1     | 0     | 0x34                | 0x35               |

| 1     | 1     | 0x36                | 0x37               |

<sup>(1)</sup> A floating ADDR[1:0] terminal at power-up will be interpreted as a logic 0.

# **Table 7. Control and Shared Register Space**

| ADDRESS<br>(HEX) | DEFAULT<br>VALUE (HEX) | BITS | DEFAULT<br>VALUE<br>(BINARY) | MODE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|------------------------|------|------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00             | 00                     | 7:4  | 0000                         | R      | SMBus Address Strap Observation <3:0>                                                                                                                                                                                                                                                                                                                                                                                          |

| 0x01             | 60                     | 7:5  | 011                          | R      | Device Revision                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  | 60                     | 4:0  | 0 0000                       | R      | Device ID                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0x04             |                        | 6    | 0                            | R/W/SC | Self-Clearing Reset for Control/Shared Registers                                                                                                                                                                                                                                                                                                                                                                               |

|                  | 01                     | 5    | 0                            | R/W    | Reset for SMBus Master Mode                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  |                        | 4    | 0                            | R/W    | Force EEPROM Configuration                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x05             |                        | 4    | 0                            | R      | Indicates EEPROM read complete                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  | 00                     | 3    | 0                            | R      | Indicates Channel A has interrupted                                                                                                                                                                                                                                                                                                                                                                                            |

|                  |                        | 2    | 0                            | R      | Indicates Channel B has interrupted                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x06             | 00                     | 3:0  | 0000                         | R/W    | Write to 0xA'h to observe SMBus Address strap in Reg 0x00[7:4]                                                                                                                                                                                                                                                                                                                                                                 |

| 0x07             | 04                     | 1    | 0                            | R/W    | Loopback:<br>Loopback Input of Channel B to Output of Channel A                                                                                                                                                                                                                                                                                                                                                                |

|                  | 04                     | 0    | 0                            | R/W    | Loopback:<br>Loopback Input of Channel A to Output of Channel B                                                                                                                                                                                                                                                                                                                                                                |

| 0xff             |                        | 7:6  | 00                           | R/W    | Controls LOCK pin output (ADDR0 = 0 or Float) 00: Logical OR of Lock Status from CH A and CH B 01: Lock Status from Channel A 10: Lock Status from Channel B 11: Logical AND of Lock Status from CH A and CH B Controls LOCK pin output (ADDR0 = 1) 00: Logical NOR of Lock Status from CH A and CH B 01: NOT Lock Status from Channel A 10: NOT Lock Status from Channel B 11: Logical NAND of Lock Status from CH A and CH B |

|                  | 00                     | 5    | 0                            | R/W    | Loss of Signal / Interrupt (LOS/INT) terminal output 0: LOS 1: Interrupt                                                                                                                                                                                                                                                                                                                                                       |

|                  |                        |      | 0                            | R/W    | Selects Both Channels for Register Write. Register read from one channel based on the selected channel in register 0xff bits 1:0. See Table 8                                                                                                                                                                                                                                                                                  |

|                  |                        |      | 0                            | R/W    | 0 = reads/writes directed to shared registers 1 = reads/writes directed to channel registers based on target channel defined by register 0xff bits 1:0. See Table 8                                                                                                                                                                                                                                                            |

|                  |                        | 1:0  | 0                            | R/W    | Selects Target Channel for Register Reads and Writes. See Table 8                                                                                                                                                                                                                                                                                                                                                              |

### 7.5.1.5 SMBus Strap Observation

Register 0x00, bits 7:4

In order to communicate with the DS110DF111 over the SMBus, it is necessary for the SMBus controller to know the address of the DS110DF111. The address strap observation bits in control/shared register 0x00 are primarily useful as a test of SMBus operation. In order to use the address strap observation bits of control/shared register 0x00, it is necessary first to set the diagnostic test control bits of control/shared register 0x06. This four bit field should be written with a value of 0xa. When this value is written to bits 3:0 of control/shared register 0x06, then the value of the SMBus address straps can be read in register 0x00, bits 7:4. The value read will be the same as the value present on the ADDR line when the DS110DF111 powers up. For example, if a value of 0x0 is read from control/shared register 0x00, bits 7:4, then at power-up the ADDR line was set to 0. The DS110DF111 is set to a SMBus Write address of 0x30.

### 7.5.1.6 Interrupt Channel Flag Bits

Register 0x05, bits 3:2

The operation of these bits is described in the section on interrupt handling later in this data sheet.

### 7.5.1.7 Control/Shared Register Reset

Register 0x04, bit 6

Register 0x04, bit 6, clears all the control/shared registers back to their factory defaults. This bit is self clearing, so it is cleared after it is written and the control/shared registers are reset to their factory default values.

### 7.5.1.8 Device Revision and Device ID

Register 0x01

Control/shared register 0x01 contains the device revision and device ID. The device ID will be different for the different devices in the retimer family. This register is useful because it can be interrogated by software to determine the device variant and revision installed in a particular system. The software might then configure the device with appropriate settings depending upon the device variant and revision.

Table 8. Channel Select Register Values Mapped to Register Set Target

| REGISTER 0xFF<br>VALUE (HEX) | SHARED/CHANNEL<br>REGISTER<br>SELECTION | BROADCAST<br>CHANNEL<br>REGISTER<br>SELECTION | TARGETED<br>CHANNEL<br>REGISTER<br>SELECTION | COMMENTS                                                                             |

|------------------------------|-----------------------------------------|-----------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------|

| 0x00                         | Shared                                  | N/A                                           | N/A                                          | All reads and writes target shared register set                                      |

| 0x04                         | Channel                                 | No                                            | Α                                            | All reads and writes target channel register set                                     |

| 0x05                         | Channel                                 | No                                            | В                                            | All reads and writes target channel register set                                     |

| 0x0c                         | Channel                                 | Yes                                           | А                                            | All writes target all channel register sets, all reads target Channel A register set |

| 0x0d                         | Channel                                 | Yes                                           | В                                            | All writes target all channel register sets, all reads target Channel B register set |

#### 7.5.1.9 Channel Select Register

Register 0xff, bits 3:0