Sample &

Buv

SLOS816A – MARCH 2015–REVISED MARCH 2015

# AFE5812 Fully Integrated, 8-Channel Ultrasound Analog Front End with Passive CW Mixer, and Digital I/Q Demodulator, 0.75 nV/rtHz, 14/12-Bit, 65 MSPS, 180 mW/CH

Technical

Documents

# 1 Features

- 8-Channel Complete Analog Front-End

LNA, VCAT, PGA, LPF, ADC, and CW Mixer

- Programmable Gain Low-Noise Amplifier (LNA)

- 24, 18, 15 dB Gain

- 0.25, 0.5, 0.7 V<sub>PP</sub> Linear Input Range

- 0.63, 0.7, 0.9 nV/rtHz Input Referred NoiseProgrammable Active Termination

- 40 dB Low Noise Voltage Controlled Attenuator (VCAT)

- 24/30 dB Programmable Gain Amplifier (PGA)

- 3<sup>rd</sup> Order Linear Phase Low-Pass Filter (LPF)

10, 15, 20, 30, 35, 50 MHz

- 14-bit Analog to Digital Converter w/ LVDS output

77 dBFS SNR at 65 MSPS

- Noise/Power Optimizations (Without Digital Demodulator)

- 180 mW/CH at 0.75 nV/rtHz, 65 MSPS

- 109 mW/CH at 1.1 nV/rtHz, 40 MSPS

- 107 mW/CH at CW Mode

- Excellent Device-to-Device Gain Matching

±0.5 dB(typical) and ±1.1 dB(max)

- Programmable Digital I/Q Demodulator after ADC

- Wide Range Demodulation Frequency

- <1KHz Frequency Resolution

- Decimation Filter Factor M = 1 to 32

- 16xM tap FIR Decimation Filter

- LVDS Rate Reduction after Demodulation

- On-chip RAM with 32 preset Profiles

- Low Harmonic Distortion

- Low Frequency Sonar Signal Processing

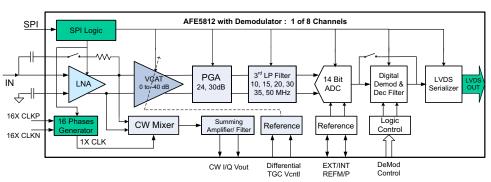

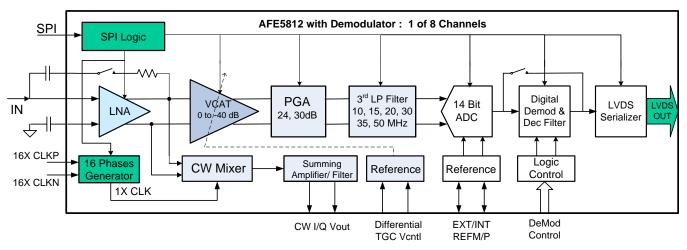

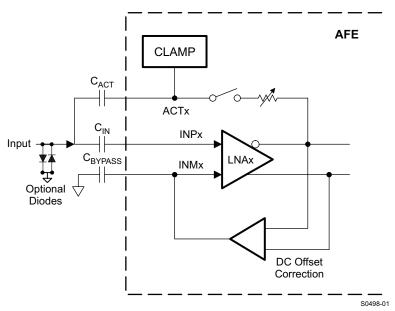

# 4 Simplified Diagram

Fast and Consistent Overload Recovery

**.**...

- Passive Mixer for Continuous Wave Doppler(CWD)

- Low Close-in Phase Noise –156 dBc/Hz at 1 KHz off 2.5 MHz Carrier

Support &

Community

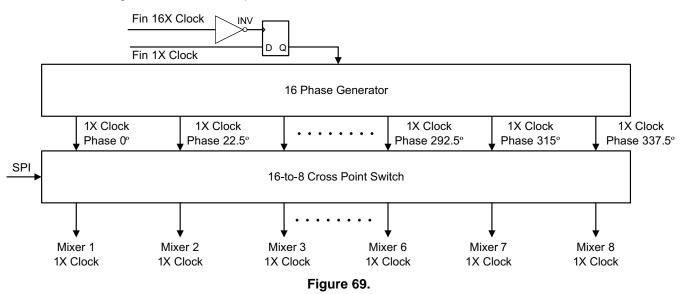

Phase Resolution of 1/16λ

Tools &

Software

- Support 16X, 8X, 4X and 1X CW Clocks

- 12dB Suppression on 3<sup>rd</sup> and 5<sup>th</sup> Harmonics

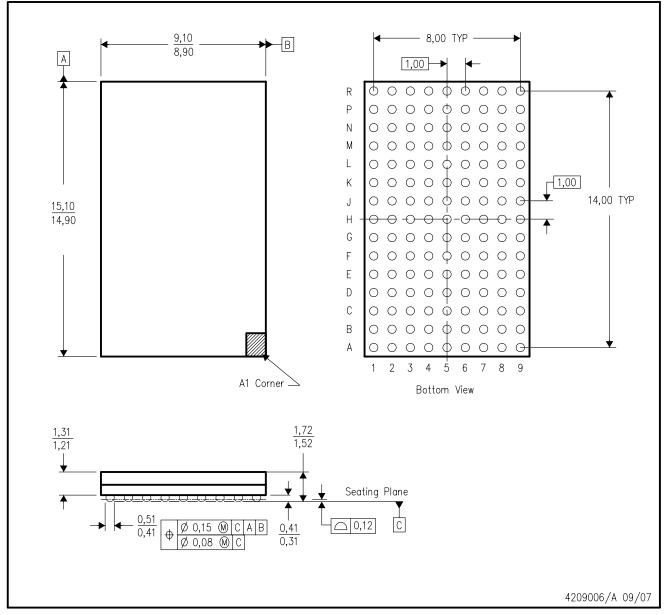

- Small Package: 15 mm x 9 mm, 135-BGA

- Operation Temperature: -40°C to 85°C

# 2 Applications

- Medical Ultrasound Imaging

- Nondestructive Evaluation Equipments

- Sonar applications

- Multichannel, High-Speed Data Acquisition

# 3 Description

The AFE5812 is a highly-integrated analog front-end (AFE) solution specifically designed for ultrasound systems in which high performance and small size are required. The AFE5812 integrates a complete time-gain-control (TGC) imaging path and a CWD path. It also enables users to select one of various power/noise combinations to optimize system performance. Therefore, the AFE5812 is a suitable ultrasound AFE solution not only for high-end systems, but also for portable ones.

## **Device Information**<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)    |

|-------------|-------------|--------------------|

| AFE5812     | NFBGA (135) | 15.00 mm × 9.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimore PROPLETION DATA

2

| me | 113  |                                       |                 |

|----|------|---------------------------------------|-----------------|

|    | 10.3 | Feature Description                   | 29              |

|    | 10.4 | Device Functional Modes               | 45              |

|    | 10.5 | Programming                           | 47              |

|    | 10.6 | Register Maps                         | <mark>52</mark> |

| 11 | Appl | ication and Implementation            | 80              |

|    | 11.1 | Application Information               | 80              |

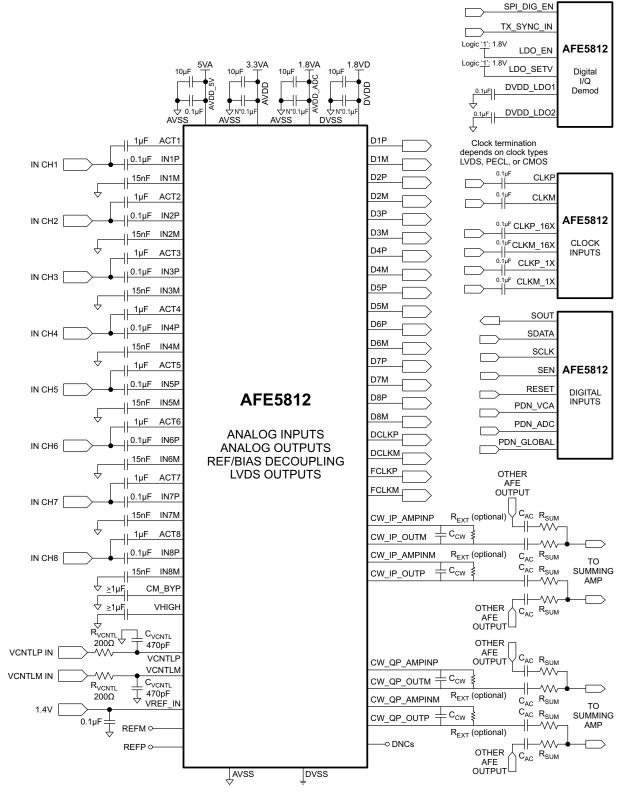

|    | 11.2 | Typical Application                   | <mark>81</mark> |

|    | 11.3 | Do's and Don'ts                       | 97              |

| 12 | Pow  | er Supply Recommendations             | <mark>98</mark> |

|    | 12.1 | Power/Performance Optimization        |                 |

|    | 12.2 | Power Management Priority             |                 |

|    | 12.3 | Partial Power-Up and Power-Down Mode. | <mark>98</mark> |

|    | 12.4 | Complete Power-Down Mode              | 99              |

|    | 12.5 | Power Saving in CW Mode               | 99              |

| 13 | Layo | out                                   | 100             |

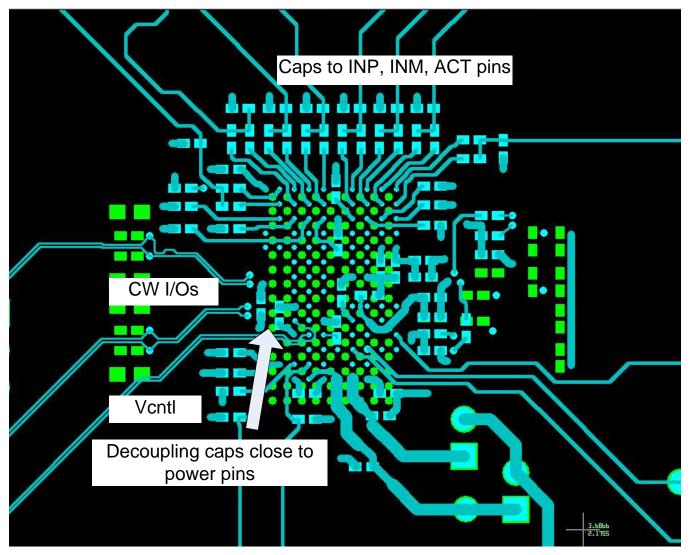

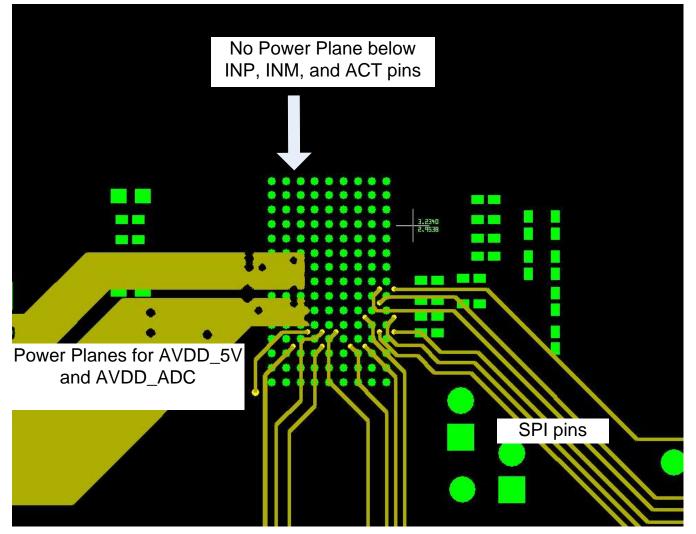

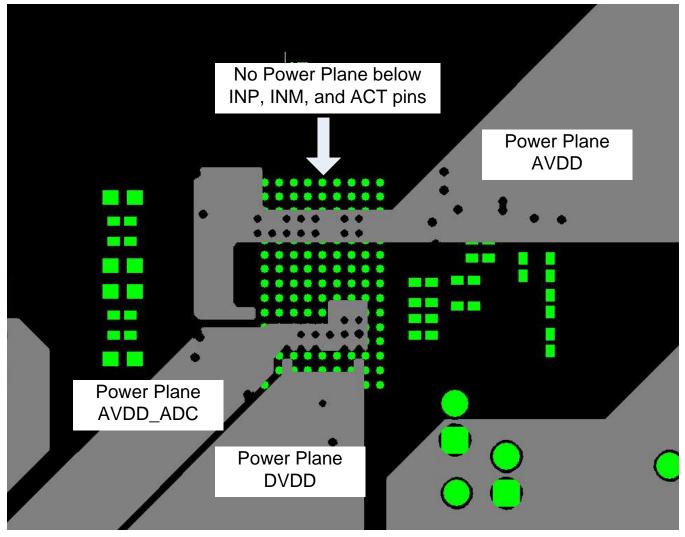

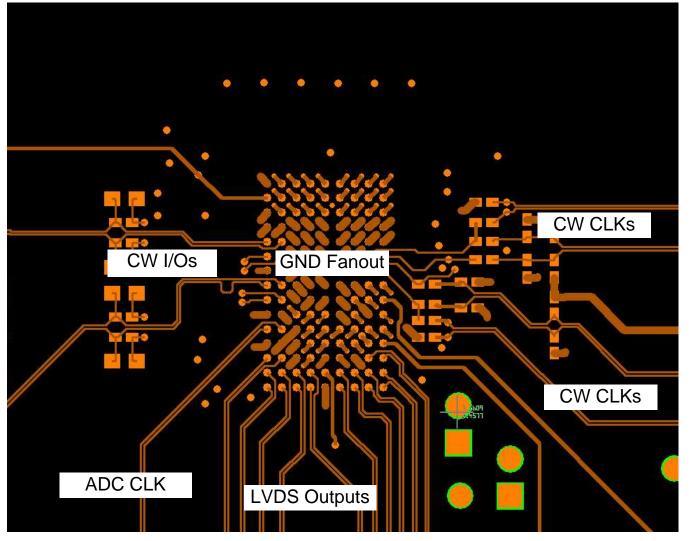

|    | 13.1 | Layout Guidelines                     | 100             |

|    | 13.2 | Layout Example                        | 101             |

| 14 | Devi | ce and Documentation Support          | 105             |

|    | 14.1 | Documentation Support                 | 105             |

Mechanical, Packaging, and Orderable

Trademarks ..... 105

Electrostatic Discharge Caution ...... 105

Glossary ...... 105

Copyright © 2015, Texas Instruments Incorporated

Information ..... 105

| 5 Revision | History |

|------------|---------|

|------------|---------|

| Changes from Original (March 2015) to Revision A |                                                              |     |  |

|--------------------------------------------------|--------------------------------------------------------------|-----|--|

| •                                                | Changed the device From: Product Preview To: Production Data | . 1 |  |

14.2

14.3

14.4

15

#### 1 Features ..... 1 2 Applications ..... 1 3 Description ..... 1 4 Simplified Diagram ..... 1 5 Revision History..... 2 6 Device Comparison Table...... 3 7 Description (continued)..... 4 Pin Configuration and Functions ...... 5 8 9 Specifications......8 9.1 Absolute Maximum Ratings ...... 8 9.2 9.3 9.4 Electrical Characteristics...... 10 9.5 9.6 Digital Demodulator Electrical Characteristics ...... 14 9.7 Digital Characteristics ..... 15 9.9 Output Interface Timing (14-bit) ...... 16 9.10 SPI Timing Characteristics...... 18 9.11 Typical Characteristics ...... 18 10.1 10.2 Functional Block Diagram ...... 28

www.ti.com

# 6 Device Comparison Table

| Part Number       | Part Description                                                                                                                                 | Package     | Body Size (NOM)     |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------|

| AFE5818, SBAS687  | 16-Channel, Ultrasound, Analog Front-End with 124-mW/Channel, 0.75-nV/√Hz<br>Noise, 14-Bit, 65-MSPS or 12-Bit, 80-MSPS ADC, and Passive CW Mixer | NFBGA (289) | 15.00 mm × 15.00 mm |

| AFE5816, SBAS688  | 16-Channel, Ultrasound, Analog Front-End with 54-mW/Channel, 1.3-nV/√Hz<br>Noise, 14-Bit, 65-MSPS or 12-Bit, 80-MSPS ADC, and Passive CW Mixer   | NFBGA (289) | 15.00 mm × 15.00 mm |

| AFE5809, SLOS738  | 8-Channel Ultrasound Analog Front End With Passive CW Mixer, and Digital I/Q<br>Demodulator, 0.75 nV/rtHz, 14, 12-Bit, 65 MSPS, 158 mW/CH        | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5808A,SLOS729  | 8-Channel Ultrasound Analog Front End With Passive CW Mixer, 0.75 nV/rtHz,<br>14/12-Bit, 65 MSPS, 158 mW/CH                                      | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5807, SLOS703  | 8-Channel Ultrasound Analog Front End with Passive CW Mixer, 1.05 nV/rtHz, 12-<br>Bit, 80 MSPS, 117 mW/CH                                        | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5803, SLOS763  | 8-Channel Ultrasound Analog Front End, 0.75 nV/rtHz, 14/12-Bit, 65 MSPS, 158 mW/CH                                                               | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5805, SBOS421  | 8-Channel Ultrasound Analog Front End, 0.85 nV/rtHz, 12-Bit, 50 MSPS, 122 mW/CH                                                                  | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5804, SBOS442  | 8-Channel Ultrasound Analog Front End, 1.23 nV/rtHz, 12-Bit, 50 MSPS, 101 mW/CH                                                                  | NFBGA (135) | 15.00 mm × 9.00 mm  |

| AFE5801, SLOS591  | 8-Channel Variable-Gain Amplifier (VGA) With Octal High-Speed ADC, 5.5 nV/rtHz, 12-Bit, 65MSPS, 65 mW/CH                                         | QFN (64)    | 9.00 mm × 9.00 mm   |

| AFE5851, SLOS574  | 16-Channel Variable-Gain Amplifier (VGA) With High-Speed ADC, 5.5 nV/rtHz, 12-<br>Bit, 32.5 MSPS, 39 mW/CH                                       | QFN (64)    | 9.00 mm × 9.00 mm   |

| VCA5807, SLOS727  | 8-Channel Voltage Controlled Amplifier for Ultrasound with Passive CW Mixer, 0.75 nV/rtHz, 99 mW/CH                                              | TQFP (80)   | 14.00 mm × 14.00 mm |

| VCA8500, SBOS390  | 8-Channel, Ultralow-Power, Variable Gain Amplifier with Low-Noise Pre-Amp, 0.8 nV/rtHz, 65 mW/CH                                                 | QFN (64)    | 9.00 mm × 9.00 mm   |

| ADS5294, SLAS776  | Octal-Channel 14-Bit 80-MSPS ADC, 75 dBFS SNR, 77 mW/CH                                                                                          | TQFP (80)   | 14.00 mm × 14.00 mm |

| ADS5292, SLAS788  | Octal-Channel 12-Bit 80-MSPS ADC, 70 dBFS SNR, 66 mW/CH                                                                                          | TQFP (80)   | 14.00 mm × 14.00 mm |

| ADS5295, SBAS595  | Octal-Channel 12-Bit 100-MSPS ADC, 70.6 dBFS SNR, 80 mW/CH                                                                                       | TQFP (80)   | 14.00 mm × 14.00 mm |

| ADS5296A, SBAS631 | 10-Bit, 200-MSPS, 4-Channel, 61dBFS SNR, 150 mW/CH and 12-Bit, 80-MSPS, 8-<br>Channel, 70dBFS SNR, 65 mW/CH ADC                                  | QFN (64)    | 9.00 mm × 9.00 mm   |

## 7 Description (continued)

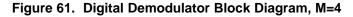

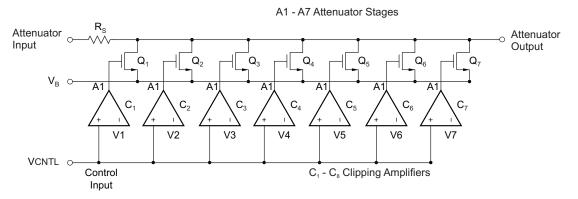

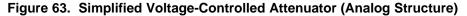

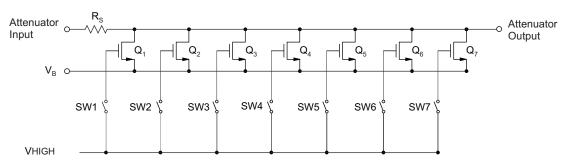

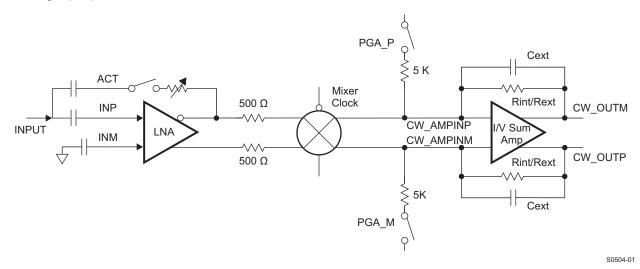

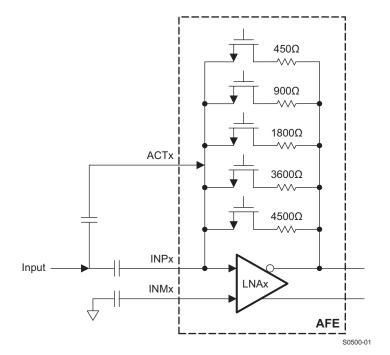

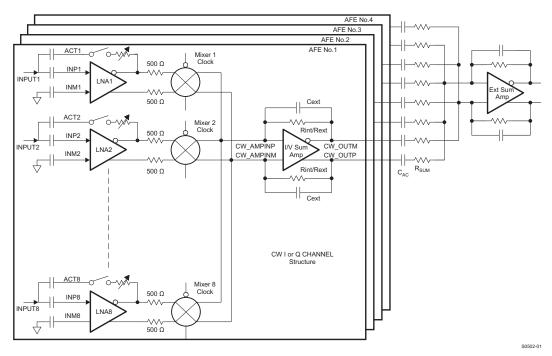

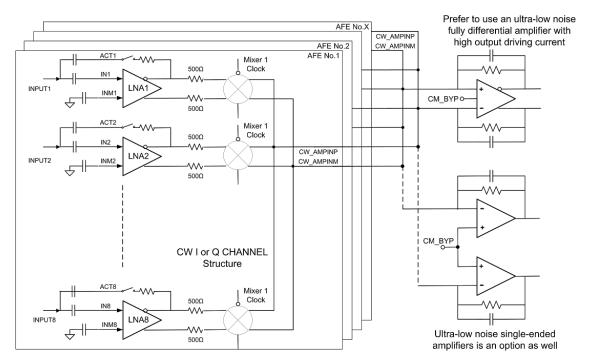

The AFE5812 contains eight channels of voltage controlled amplifier (VCA), 14, and 12-bit ADC, and CW mixer. The VCA includes LNA, VCAT, PGA, and LPF. The LNA gain is programmable to support 250 mV<sub>PP</sub> to 0.75 V<sub>PP</sub> input signals. Programmable active termination is also supported by the LNA. The ultra-low noise VCAT provides an attenuation control range of 40 dB and improves overall low-gain SNR, which benefits harmonic imaging and near-field imaging. The PGA provides gain options of 24 and 30 dB. Before the ADC, a LPF can be configured as 10, 15, 20, 30, 35 or 50 MHz to support ultrasound applications with different frequencies. In addition, the signal chain of the AFE5812 can handle signal frequency lower than 100 kHz, which enables the AFE5812 to be used in both sonar and medical applications. The high-performance 14-bit/65-MSPS ADC in the AFE5812 achieves 77 dBFS SNR. It ensures excellent SNR at low chain gain. The ADC's LVDS outputs enable flexible system integration desired for miniaturized systems.

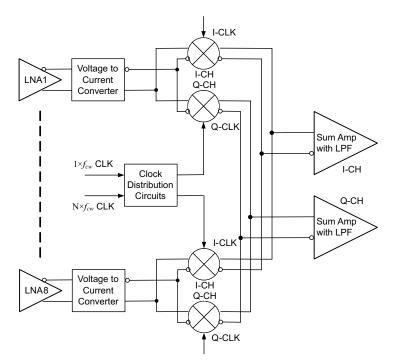

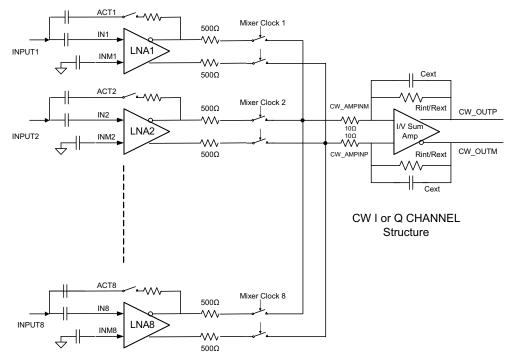

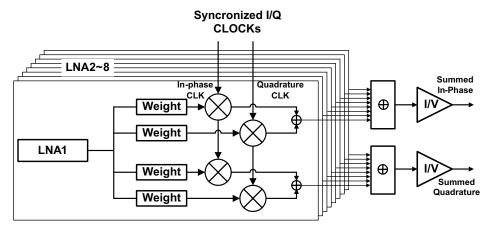

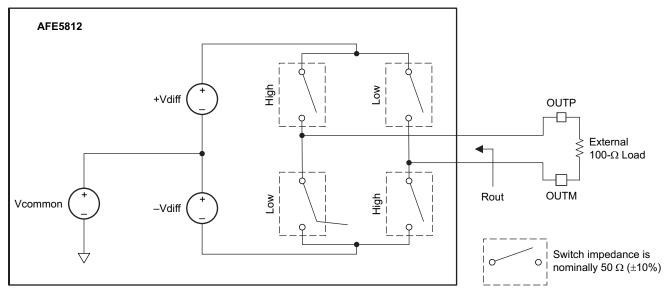

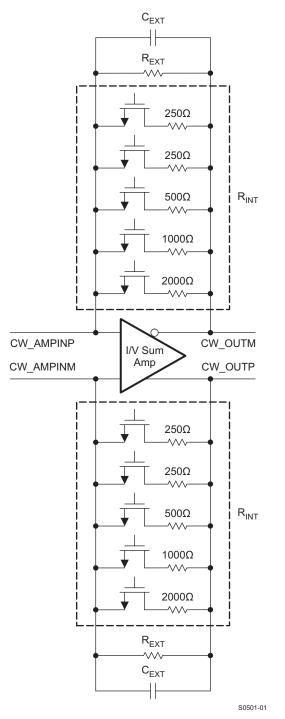

The AFE5812 integrates a low-power passive mixer and a low-noise summing amplifier to accomplish on-chip CWD beamformer. 16 selectable phase-delays can be applied to each analog input signal. Meanwhile, a unique third- and fifth-order harmonic suppression filter is implemented to enhance CW sensitivity.

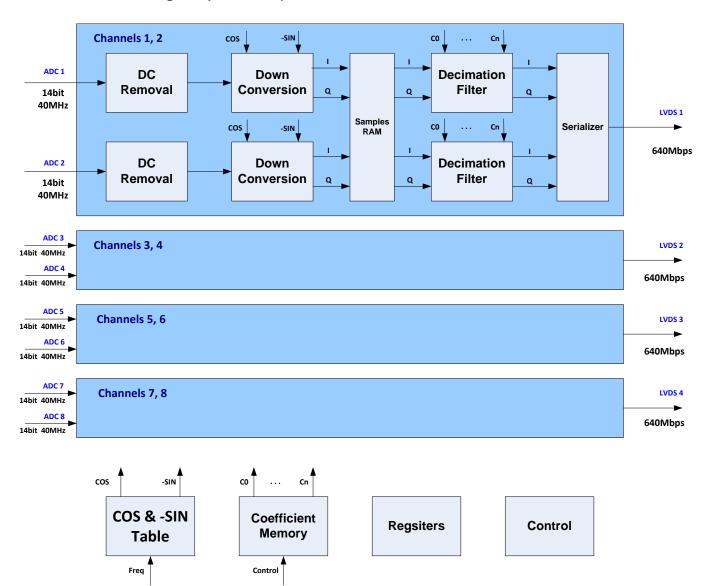

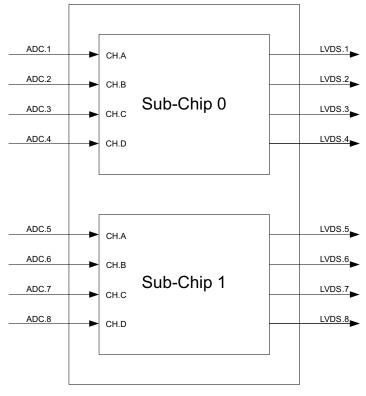

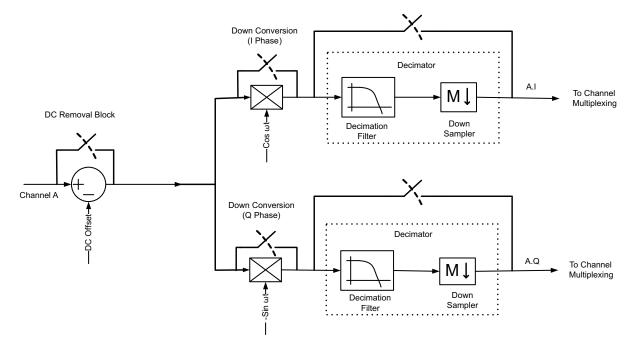

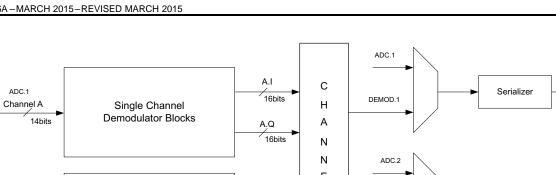

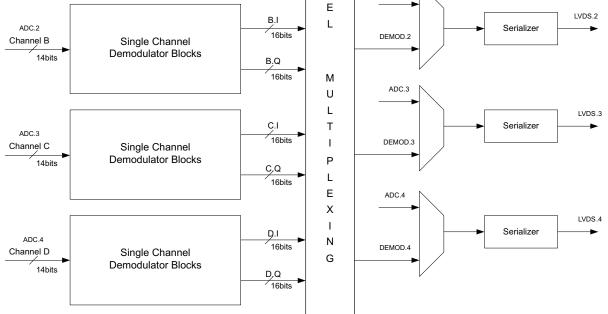

AFE5812 also includes a digital in-phase and quadrature (I/Q) demodulator and a low-pass decimation filter. The main purpose of the demodulation block is to reduce the LVDS data rate and improve overall system power efficiency. The I/Q demodulator can accept ADC output with up to 65 MSPS sampling rate and 14-bit resolution. For example, after digital demodulation and 4x decimation filtering, the data rate for either in-phase or quadrature output is reduced to 16.25 MSPS and the data resolution is improved to 16 bits, consequently. Hence, the overall LVDS trace reduction can be a factor of 2. This demodulator can be bypassed and powered down completely if it is not needed.

The AFE5812 is available in a 15-mm × 9-mm, 135-pin BGA package, and it is specified for operation from -40°C to 85°C.

# 8 Pin Configuration and Functions

|   | 1            | 2            | 3                |           | 5     | 6         | 7          | 8          | 9        |

|---|--------------|--------------|------------------|-----------|-------|-----------|------------|------------|----------|

|   | 1            | Z            | 3                | 4         | 5     | 6         | 1          | 8          | 9        |

| Α | AVDD         | INP8         | INP7             | INP6      | INP5  | INP4      | INP3       | INP2       | INP1     |

| В | CM_BYP       | ACT8         | ACT7             | ACT6      | ACT5  | ACT4      | ACT3       | ACT2       | ACT1     |

| С | AVSS         | INM8         | INM7             | INM6      | INM5  | INM4      | INM3       | INM2       | INM1     |

| D | AVSS         | AVSS         | AVSS             | AVSS      | AVSS  | AVSS      | AVSS       | AVDD       | AVDD     |

| Е | CW_IP_AMPINP | CW_IP_AMPINM | AVSS             | AVSS      | AVSS  | AVSS      | AVSS       | AVDD       | AVDD     |

| F | CW_IP_OUTM   | CW_IP_OUTP   | AVSS             | AVSS      | AVSS  | AVSS      | AVSS       | CLKP_16X   | CLKM_16X |

| G | AVSS         | AVSS         | AVSS/DTGC_S<br>W | AVSS      | AVSS  | AVSS      | AVSS       | CLKP_1X    | CLKM_1X  |

| н | CW_QP_OUTM   | CW_QP_OUTP   | AVSS             | AVSS      | AVSS  | AVSS      | AVSS       | PDN_GLOBAL | RESET    |

| J | CW_QP_AMPINP | CW_QP_AMPINM | AVSS             | AVSS      | AVSS  | AVDD_ADC  | AVDD_ADC   | PDN_VCA    | SCLK     |

| к | AVDD         | AVDD_5V      | VCNTLP           | VCNTLM    | VHIGH | AVSS      | DNC        | AVDD_ADC   | SDATA    |

| L | CLKP_ADC     | CLKM_ADC     | AVDD_ADC         | REFM      | DNC   | LDO_EN    | TX_SYNC_IN | PDN_ADC    | SEN      |

| м | AVDD_ADC     | AVDD_ADC     | VREF_IN          | REFP      | DNC   | LDO_SETV  | SPI_DIG_EN | DNC        | SDOUT    |

| N | D8P          | D8M          | DVDD             | DVDD_LDO1 | DVSS  | DVDD_LDO2 | DVDD       | D1M        | D1P      |

| Р | D7M          | D6M          | D5M              | FCLKM     | DVSS  | DCLKM     | D4M        | D3M        | D2M      |

| R | D7P          | D6P          | D5P              | FCLKP     | DVSS  | DCLKP     | D4P        | D3P        | D2P      |

## Table 1. ZCF (BGA-135) Top View

## **Pin Functions**

| PIN          |          | DESCRIPTION                                                                                                                                                                                                                                                                                                                        |  |

|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME         | NO.      | DESCRIPTION                                                                                                                                                                                                                                                                                                                        |  |

| ACT1 to ACT8 | B9 to B2 | Active termination input pins for CH1 to CH8. Bias voltage = 1.5 V                                                                                                                                                                                                                                                                 |  |

|              | A1       |                                                                                                                                                                                                                                                                                                                                    |  |

|              | D8       |                                                                                                                                                                                                                                                                                                                                    |  |

| AVDD         | D9       | 3.3-V analog supply for LNA, VCAT, PGA, LPF, and CWD blocks                                                                                                                                                                                                                                                                        |  |

| AVDD         | E8       | S.S.V analog supply for LIVA, VCAT, FGA, LFF, and CVVD blocks                                                                                                                                                                                                                                                                      |  |

|              | E9       |                                                                                                                                                                                                                                                                                                                                    |  |

|              | K1       |                                                                                                                                                                                                                                                                                                                                    |  |

| AVDD_5V      | K2       | 5-V analog supply for LNA, VCAT, PGA, LPF, and CWD blocks                                                                                                                                                                                                                                                                          |  |

|              | J6       |                                                                                                                                                                                                                                                                                                                                    |  |

|              | J7       |                                                                                                                                                                                                                                                                                                                                    |  |

| AVDD ADC     | K8       | 1.8-V analog power supply for ADC                                                                                                                                                                                                                                                                                                  |  |

| AVDD_ADC     | L3       | T.o-V analog power supply for ADC                                                                                                                                                                                                                                                                                                  |  |

|              | M1       |                                                                                                                                                                                                                                                                                                                                    |  |

|              | M2       |                                                                                                                                                                                                                                                                                                                                    |  |

|              | C1       |                                                                                                                                                                                                                                                                                                                                    |  |

|              | D1 to D7 |                                                                                                                                                                                                                                                                                                                                    |  |

|              | E3 to E7 |                                                                                                                                                                                                                                                                                                                                    |  |

|              | F3 to F7 |                                                                                                                                                                                                                                                                                                                                    |  |

| AVSS         | G1 to G2 | Analog ground                                                                                                                                                                                                                                                                                                                      |  |

|              | G4 to G7 |                                                                                                                                                                                                                                                                                                                                    |  |

|              | H3 to H7 |                                                                                                                                                                                                                                                                                                                                    |  |

|              | J3 to J5 |                                                                                                                                                                                                                                                                                                                                    |  |

|              | K6       |                                                                                                                                                                                                                                                                                                                                    |  |

| AVSS/DTGC_SW | G3       | Analog ground; or external control pin to switch from ATGC to DTGC. Active high to enable the DTGC mode. Pull down to GND with 20 k $\Omega$ . This pin is equivalent to VCA Reg 0x3B[7], DIG_TGC_ATT and Figure 64. Tie to AVSS if not used. Note: this feature is ensured by design and characterization; NOT production tested. |  |

| CLKM_ADC     | L2       | Negative input of differential ADC clock. In the single-end clock mode, it can be tied to GND directly or through a $0.1$ - $\mu$ F capacitor. Bias voltage = 1V                                                                                                                                                                   |  |

Copyright © 2015, Texas Instruments Incorporated

AFE5812 SLOS816A – MARCH 2015 – REVISED MARCH 2015

www.ti.com

Texas Instruments

# Pin Functions (continued)

| PIN          |          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME         | NO.      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| CLKP_ADC     | L1       | Positive input of differential ADC clock. In the single-end clock mode, it can be tied to clock signal directly or through a $0.1$ - $\mu$ F capacitor. Bias voltage = 1V                                                                                                                                                                        |  |  |  |

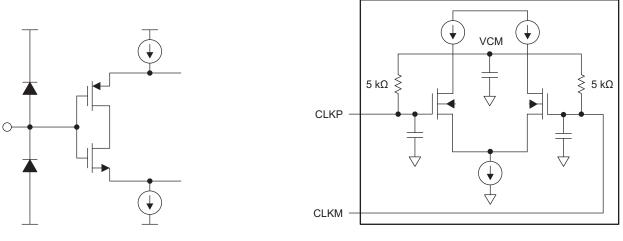

| CLKM_16X     | F9       | Negative input of differential CW 16× clock. Tie to GND when the CMOS clock mode is enabled. In the 4× and 8× CW clock modes, this pin becomes the 4× or 8× CLKM input. In the 1× CW clock mode, this pin becomes the in-phase 1× CLKM for the CW mixer. Can be floated if CW mode is not used. See register 0x36[11:10]. Bias voltage = $2.5$ V |  |  |  |

| CLKP_16X     | F8       | Positive input of differential CW 16x clock. In 4x and 8x clock modes, this pin becomes the 4x and 8x CLKP input. In the 1x CW clock mode, this pin becomes the in-phase 1x CLKP for the CW mixer. Can be floated if CW mode is not used.See register 0x36[11:10]. Bias voltage = 2.5 V                                                          |  |  |  |

| CLKM_1X      | G9       | Negative input of differential CW 1× clock. Tie to GND when the CMOS clock mode is enabled (refer to Figure 107 for details). In the 1× clock mode, this pin is the quadrature-phase 1× CLKM for the CW mixer. Can be floated if CW mode is not used. Bias voltage = $2.5 \text{ V}$                                                             |  |  |  |

| CLKP_1X      | G8       | Positive input of differential CW 1x clock. In the 1x clock mode, this pin is the quadrature-phase 1x CLKP for the CW mixer. Can be floated if CW mode is not used. Bias voltage = 2.5 V                                                                                                                                                         |  |  |  |

| CM_BYP       | B1       | Bias voltage and bypass to ground. TI recommends 1 $\mu F.$ To suppress the ultra-low frequency noise, the designer can use 10 $\mu F.$ Bias voltage = 1.5 V                                                                                                                                                                                     |  |  |  |

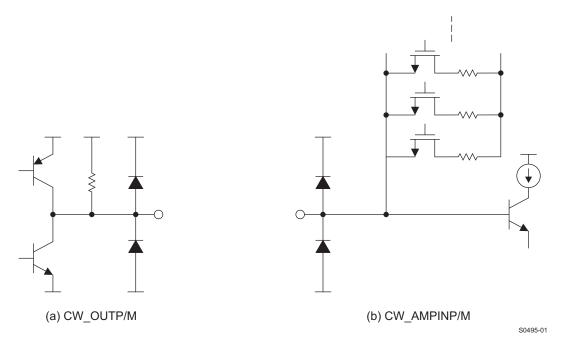

| CW_IP_AMPINM | E2       | Negative differential input of the in-phase summing amplifier. External LPF capacitor must be connected between CW_IP_AMPINM and CW_IP_OUTP. This pin provides the current output for the CW mixer. This pin becomes the CH7 PGA negative output when PGA test mode is enabled. Can be floated if not used. Bias voltage = 1.5 V                 |  |  |  |

| CW_IP_AMPINP | E1       | Positive differential input of the in-phase summing amplifier. External LPF capacitor must be connected between CW_IP_AMPINP and CW_IP_OUTM. This pin provides the current output for the CW mixer. This pin becomes the CH7 PGA positive output when PGA test mode is enabled. Can be floated if not used. Bias voltage = 1.5 V                 |  |  |  |

| CW_IP_OUTM   | F1       | Negative differential output for the in-phase summing amplifier. External LPF capacitor must be connected between CW_IP_AMPINP and CW_IP_OUTPM. Can be floated if not used. Bias voltage = 1.5 V                                                                                                                                                 |  |  |  |

| CW_IP_OUTP   | F2       | Positive differential output for the in-phase summing amplifier. External LPF capacitor must be connected between CW_IP_AMPINM and CW_IP_OUTP. Can be floated if not used. Bias voltage = 1.5 V                                                                                                                                                  |  |  |  |

| CW_QP_AMPINM | J2       | Negative differential input of the quadrature-phase summing amplifier. External LPF capacitor must be connected between CW_QP_AMPINM and CW_QP_OUTP. This pin provides the current output for the CW mixer. This pin becomes CH8 PGA negative output when PGA test mode is enabled. Can be floated if not used. Bias voltage = 1.5 V             |  |  |  |

| CW_QP_AMPINP | J1       | Positive differential input of the quadrature-phase summing amplifier. External LPF capacitor must be connected between CW_QP_AMPINP and CW_QP_OUTM. This pin provides the current output for the CW mixer. This pin becomes CH8 PGA positive output when PGA test mode is enabled. Can be floated if not used. Bias voltage = 1.5 V             |  |  |  |

| CW_QP_OUTM   | H1       | Negative differential output for the quadrature-phase summing amplifier. External LPF capacitor must be connected between CW_QP_AMPINP and CW_QP_OUTM. Can be floated if not used. Bias voltage = 1.5 V                                                                                                                                          |  |  |  |

| CW_QP_OUTP   | H2       | Positive differential output for the quadrature-phase summing amplifier. External LPF capacitor must be connected between CW_QP_AMPINM and CW_QP_OUTP. Can be floated if not used. Bias voltage = 1.5 V                                                                                                                                          |  |  |  |

|              | N8       |                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|              | P9 to P7 |                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| D1M to D8M   | P3 to P1 | ADC CH1 to CH8 LVDS negative data outputs                                                                                                                                                                                                                                                                                                        |  |  |  |

|              | N2       |                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|              | N9       |                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| D1P to D8P   | R9 to R7 | ADC CH1 to 8 LVDS positive data outputs                                                                                                                                                                                                                                                                                                          |  |  |  |

|              | R3 to R1 |                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|              | N1       |                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| DCLKM        | P6       | LVDS bit clock (7x in 14bit resolution) negative output                                                                                                                                                                                                                                                                                          |  |  |  |

| DCLKP        | R6       | LVDS bit clock (7x in 14bit resolution) positive output                                                                                                                                                                                                                                                                                          |  |  |  |

| DVDD         | N3<br>N7 | ADC digital and I/O power supply, 1.8 V                                                                                                                                                                                                                                                                                                          |  |  |  |

## Pin Functions (continued)

| PIN                     |          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                    | NO.      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                         | N5       |                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| DVSS                    | P5       | ADC digital ground                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                         | R5       |                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                         | N4       | In the internal LDO mode, i.e. LDO_EN=1, these two pins should be separated on PCB and                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| DVDD_LDO1,<br>DVDD_LDO2 | N6       | <b>decoupled respectively.</b> Internal LDO output will drive this PIN to 1.2V or 1.4V depending on LDO_SETV. In the external LDO mode, i.e. LDO_EN=0 or floating, lower demod power is achieved than the internal LDO mode. 1.4V~1.5V should be applied when ADC sampling rate is high, e.g. 50~65MSPS. <b>Demod SPI requires DVDD_LDO1/2.</b>                                                                                       |  |  |  |

| FCLKM                   | P4       | LVDS frame clock (1x) negative output                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| FCLKP                   | R4       | LVDS frame clock (1x) positive output                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| INM1 to INM8            | C9 to C2 | CH1 to CH8 complementary analog inputs. Bypass to ground with ≥0.015-µF capacitors. The HPF response of the LNA depends on the capacitors. Bias voltage = 2.2 V                                                                                                                                                                                                                                                                       |  |  |  |

| INP1 to INP8            | A9 to A2 | CH1 to CH8 analog inputs. AC couple to inputs with ≥0.1-µF capacitors. Bias voltage = 2.2 V                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| LDO_EN                  | L6       | Enable/Disable AFE's internal LDO regulators. When it is tied to 1.8-V DVDD or Logic "1", AFE's internal LDO is enabled. When it is tied to DVSS or Logic "0", AFE's internal LDO is disabled and external 1.4V supply can be applied at N4 and N6 pins, i.e. DVDD_LDO1, DVDD_LDO2. Default is pulled down internally through a 150 K $\Omega$ resistor with input capacitance of 5 pF.Either 1.8V or 3.3V logic level can be used.   |  |  |  |

| LDO_SETV                | M6       | Sets the internal LDO voltage. '0' is 1.2V; '1' is 1.4V. Default is pulled down internally through a 150 K $\Omega$ resistor with input capacitance of 5 pF. Either 1.8V or 3.3V logic level can be used. Please note: some voltage drop exists on chip; therefore the measured DVDD_LDO voltage is slightly lower than the sepcified ones.                                                                                           |  |  |  |

| PDN_ADC                 | L8       | ADC partial (fast) power-down control pin with an internal pulldown resistor of 100 k $\Omega$ . Active high. Either 1.8-V or 3.3-V logic level can be used.                                                                                                                                                                                                                                                                          |  |  |  |

| PDN_VCA                 | J8       | VCA partial (fast) power-down control pin with an internal pulldown resistor of 20 k $\Omega$ . Active high. 3.3-V logic level should be used.                                                                                                                                                                                                                                                                                        |  |  |  |

| PDN_GLOBAL              | H8       | Global (complete) power-down control pin for the entire chip with an internal pulldown resistor of 20 k $\Omega$ .<br>Active high. 3.3-V logic level should be used. When the complete power-down mode is enabled, the digital demodulator may lose register settings. Therefore, it is required to reconfigure the demodulator registers, filter coefficient memory, and profile memory after existing the complete power-down mode. |  |  |  |

| REFM                    | L4       | 0.5-V reference output in the internal reference mode. Must leave floated in the internal reference mode. TI recommends adding a test point on the PCB for monitoring the reference output                                                                                                                                                                                                                                            |  |  |  |

| REFP                    | M4       | 1.5-V reference output in the internal reference mode. Must leave floated in the internal reference mode. TI recommends adding a test point on the PCB for monitoring the reference output                                                                                                                                                                                                                                            |  |  |  |

| RESET                   | H9       | Hardware reset pin with an internal pulldown resistor of 20 k $\Omega$ . Active high. The designer can use 3.3-V logic level.                                                                                                                                                                                                                                                                                                         |  |  |  |

| SCLK                    | J9       | Serial interface clock input with an internal pulldown resistor of 20 k $\Omega$ . This pin is connected to both ADC and VCA. The designer should use 3.3-V logic.                                                                                                                                                                                                                                                                    |  |  |  |

| SDATA                   | К9       | Serial interface data input with an internal pulldown resistor of 20 k $\Omega$ . This pin is connected to both ADC and VCA. The designer should use 3.3-V logic.                                                                                                                                                                                                                                                                     |  |  |  |

| SDOUT                   | M9       | Serial interface data readout. High impedance when readout is disabled. This pin is connected to ADC only. The designer can use 1.8-V logic.                                                                                                                                                                                                                                                                                          |  |  |  |

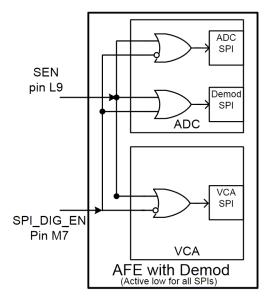

| SEN                     | L9       | Serial interface enable with an internal pullup resistor of 20 k $\Omega$ . Active low. This pin is connected to both ADC and VCA. The designer should use 3.3-V logic.                                                                                                                                                                                                                                                               |  |  |  |

| SPI_DIG_EN              | M7       | Serial interface enable for the digital demodulator memory space. SPI_DIG_EN pin is required to be set to 0 during SPI transactions to demodulator registers. Each transaction starts by setting SEN as 0 and terminates by setting it back to 1 (similar to other register transactions). Pull up internally through a 20- $k\Omega$ resistor. This pin is connected to both ADC and VCA. The designer should use 3.3-V logic.       |  |  |  |

| TX_SYNC_IN              | L7       | System trig signal input. It indicates the start of signal transmission. Either 3.3-V or 1.8-V logic level can be used. Note: TX_SYNC signal must be synchronized with ADC CLK. Typically, pulse repetition frequency (PRF) signal can be used for TX_SYNC_IN.                                                                                                                                                                        |  |  |  |

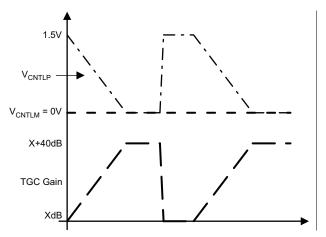

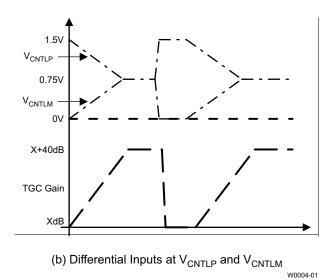

| VCNTLM                  | K4       | Negative differential attenuation control pin                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| VCNTLP                  | K3       | Positive differential attenuation control pin                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| VHIGH                   | K5       | Bias voltage; bypass to ground with ≥1 µF. Bias voltage = 1 V                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

STRUMENTS

EXAS

## Pin Functions (continued)

| PIN     |     | DESCRIPTION                                                                                 |  |  |  |

|---------|-----|---------------------------------------------------------------------------------------------|--|--|--|

| NAME    | NO. | DESCRIPTION                                                                                 |  |  |  |

| VREF_IN | M3  | DC 1.4-V reference input in the external reference mode; bypass to ground with 0.1 $\mu$ F. |  |  |  |

| DNC     | L5  |                                                                                             |  |  |  |

|         | K7  | Do not connect. Must leave floated                                                          |  |  |  |

|         | M5  |                                                                                             |  |  |  |

|         | M8  |                                                                                             |  |  |  |

## 9 Specifications

## 9.1 Absolute Maximum Ratings

over operating free-air temperature (unless otherwise noted)<sup>(1)</sup>

|                                                                    |          | MIN  | MAX                    | UNIT |

|--------------------------------------------------------------------|----------|------|------------------------|------|

|                                                                    | AVDD     | -0.3 | 3.9                    | V    |

|                                                                    | AVDD_ADC | -0.3 | 2.2                    | V    |

| Supply voltage                                                     | AVDD_5V  | -0.3 | 6                      | V    |

|                                                                    | DVDD     | -0.3 | 2.2                    | V    |

|                                                                    | DVDD_LDO | -0.3 | 1.6                    | V    |

| Voltage between AVSS and LVSS                                      |          | -0.3 | 0.3                    | V    |

| Voltage at CLKM_ADC, CLKP_ADC <sup>(2)</sup>                       |          | -0.3 | min[2.2, AVDD_ADC+0.3] | V    |

| Voltage at CLKM_16X, CLKP_16X, CLKM_1X, and CLKP_1X <sup>(2)</sup> |          | -0.3 | min[5.5V, AVDD_5V+0.3] | V    |

| Voltage at analog inputs and digital inputs                        |          | -0.3 | min [3.6, AVDD + 0.3]  | V    |

| Voltage at digital ou                                              | tputs    | -0.3 | min[2.2, DVDD+0.3]     | V    |

| Peak solder temperature <sup>(3)</sup>                             |          |      | 260                    | °C   |

| Maximum junction temperature (T <sub>J</sub> ), any condition      |          |      | 105                    | °C   |

| Operating temperature                                              |          | -40  | 85                     | °C   |

| Storage temperature, T <sub>stg</sub>                              |          | -55  | 150                    | °C   |

(1) Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied Exposure to absolute maximum rated conditions for extended periods may degrade device reliability.

(2) When AVDD\_ADC or AVDD\_5V is turned off, TI recommends to switch off the input clock (or ensure the voltage on CLKP\_ADC, CLKM\_ADC is < |0.3V|). This prevents the ESD protection diodes at the clock input pins from turning on. CLKM/P\_16X and CLKM/P\_1X CLKs should follow the similar recommendations as well.</p>

(3) Device complies with JSTD-020D.

## 9.2 ESD Ratings

|                    |        |                                                                                | VALUE | UNIT |

|--------------------|--------|--------------------------------------------------------------------------------|-------|------|

| V                  | V(FSD) | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±1000 | V    |

| V <sub>(ESD)</sub> |        | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 9.3 Recommended Operating Conditions

|                                    | MIN  | MAX | UNIT |

|------------------------------------|------|-----|------|

| AVDD                               | 3.15 | 3.6 | V    |

| AVDD_ADC                           | 1.7  | 1.9 | V    |

| DVDD                               | 1.7  | 1.9 | V    |

| DVDD_LDO1/2 (External LDO mode)    | 1.4  | 1.5 | V    |

| AVDD_5V                            | 4.75 | 5.5 | V    |

| T <sub>A</sub> Ambient temperature | -40  | 85  | °C   |

## 9.4 Thermal Information

|                       |                                              | AFE5812  |      |

|-----------------------|----------------------------------------------|----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | BGA      | UNIT |

|                       |                                              | 135 PINS |      |

| $R_{	extsf{	heta}JA}$ | Junction-to-ambient thermal resistance       | 34.1     |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 5        |      |

| $R_{	extsf{	heta}JB}$ | Junction-to-board thermal resistance         | 11.5     | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.2      | C/VV |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 10.8     |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A      |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

AFE5812

SLOS816A-MARCH 2015-REVISED MARCH 2015

www.ti.com

## 9.5 Electrical Characteristics

AVDD\_5V = 5 V, AVDD = 3.3 V, AVDD\_ADC = 1.8 V, DVDD = 1.8 V, AC-coupled with 0.1  $\mu$ F at INP and bypassed to ground with 15 nF at INM, No active termination, V<sub>CNTL</sub> = 0 V,  $f_{IN}$  = 5 MHz, LNA = 18 dB, PGA = 24 dB, 14 bit, sample rate = 65 MSPS, LPF Filter = 15 MHz, low-noise mode, V<sub>OUT</sub> = -1 dBFS, Single-ended V<sub>CNTL</sub> mode, VCNTLM = GND, ADC configured in internal reference mode, internal 500- $\Omega$  CW feedback resistor, CMOS CW clocks, at ambient temperature, T<sub>A</sub> = 25°C, Digital demodulator is disabled unless otherwise noted. Min and max values are specified across full-temperature range with AVDD\_5 V = 5 V, AVDD = 3.3 V, AVDD\_ADC = 1.8 V.

|          | PARAMETER                                                    | TEST CONDITIONS                                                                          | MIN  | TYP                   | MAX | UNIT    |

|----------|--------------------------------------------------------------|------------------------------------------------------------------------------------------|------|-----------------------|-----|---------|

| GC FULL  | SIGNAL CHANNEL (LNA + VCAT + LPF                             | + ADC)                                                                                   |      |                       |     |         |

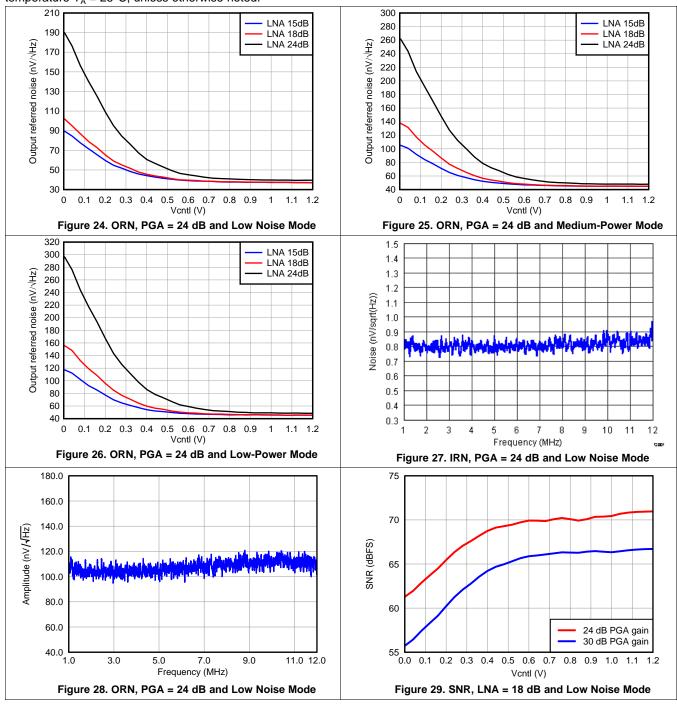

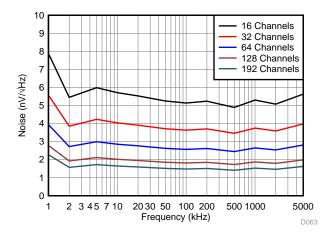

|          | Input voltage noise over LNA gain (low-                      | Rs = 0 Ω, <i>f</i> = 2 MHz, LNA = 24, 18, 15 dB, PGA = 24 dB                             | 0.76 | , 0.83, 1.16          |     | nV/rtHz |

|          | noise mode)                                                  | Rs = 0 Ω, <i>f</i> = 2 MHz, LNA = 24, 18, 15 dB, PGA = 30 dB                             | 0.75 | , 0.86, 1.12          |     |         |

|          | Input voltage noise over LNA gain (low-                      | Rs = 0 Ω, <i>f</i> = 2 MHz, LNA = 24, 18, 15 dB, PGA = 24 dB                             | 1.   | 1, 1.2, 1.45          |     |         |

| en (RTI) | power mode)                                                  | Rs = 0 Ω, <i>f</i> = 2 MHz, LNA = 24, 18, 15 dB, PGA = 30 dB                             | 1.   | 1, 1.2, 1.45          |     | nV/rtHz |

|          | Input voltage noise over LNA gain                            | Rs = 0 Ω, <i>f</i> = 2 MHz, LNA = 24, 18, 15 dB, PGA = 24 dB                             | 1    | , 1.05, 1.25          |     | nV/rtHz |

|          | (medium-power mode)                                          | Rs = 0 Ω, <i>f</i> = 2 MHz, LNA = 24, 18, 15 dB, PGA = 30 dB                             |      | 0.95, 1, 1.2          |     |         |

| en (RTI) | Input voltage noise at low frequency                         | f = 100 kHz, INM capacitor = 1 µF, PGA integrator disabled                               |      | 0.9                   |     | nV/rtHz |

|          | Input referred current noise                                 | Low-noise mode/medium-power mode/low-power mode                                          |      | 2.7, 2.1, 2           |     | pA/rtHz |

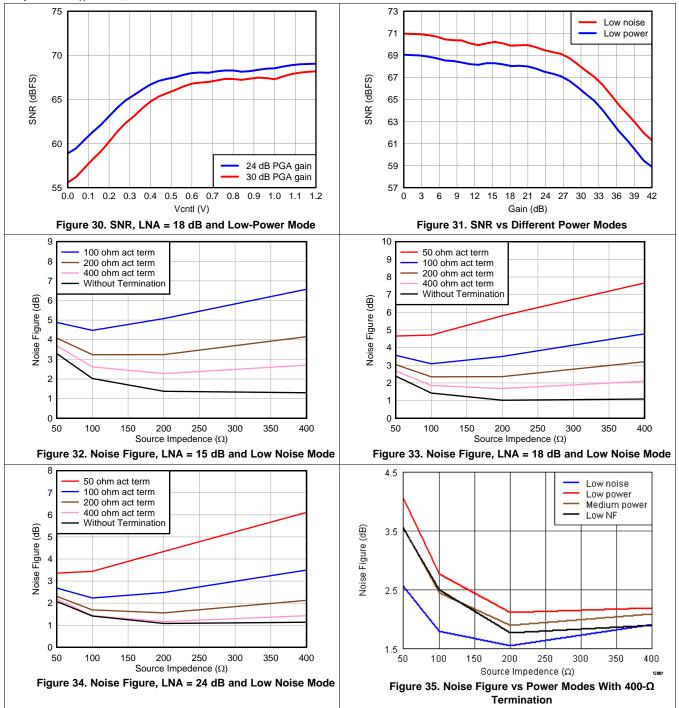

| ١F       | Noice figure                                                 | $Rs$ = 200 $\Omega,$ 200- $\Omega$ active termination, PGA = 24 dB, LNA = 15, 18, 24 dB  | 3.   | 85, 2.4, 1.8          |     | dB      |

| JF.      | Noise figure                                                 | Rs = 100 $\Omega$ , 100- $\Omega$ active termination, PGA = 24 dB, LNA = 15, 18, 24 dB   | 5    | 5.3, 3.1, 2.3         |     | dB      |

| IF       | Noise figure                                                 | Rs = 500 $\Omega$ , 1 k $\Omega$ , no termination, low-NF mode is enabled (Reg53[9] = 1) |      | 1.08, 0.94            |     | dB      |

| IF       | Noise figure                                                 | Rs = 50 $\Omega$ / 200 $\Omega$ , no termination, low-noise mode (Reg53[9] = 0)          |      | 2.35, 1.05            |     | dB      |

| мах      | Maximum linear input voltage                                 | LNA gain = 24, 18, 15 dB                                                                 | 25   | 0, 500, 700           |     |         |

| CLAMP    | Clamp voltage                                                | Reg52[10:9] = 0, LNA = 24, 18, 15 dB                                                     | 35   | 0, 600, 825           |     | mVpp    |

|          |                                                              | Low-noise mode                                                                           |      | 24, 30                |     | ٩Ŀ      |

|          | PGA gain                                                     | Medium-power/low-power mode                                                              |      | 24, 28.5              |     | dB      |

|          |                                                              | LNA = 24 dB, PGA = 30 dB, low-noise mode                                                 |      | 54                    |     |         |

|          | Total gain                                                   | LNA = 24 dB, PGA = 30 dB, medium-power mode                                              |      | 52.5                  |     | dB      |

|          |                                                              | LNA = 24 dB, PGA = 30 dB, low-power mode                                                 |      | 52.5                  |     |         |

|          | Ch-CH noise correlation factor without signal <sup>(1)</sup> | Summing of 8 channels                                                                    |      | 0                     |     |         |

|          | Ch-CH noise correlation factor with                          | Full band (V <sub>CNTL</sub> = 0, 0.8)                                                   |      | 0.15, 0.17            |     |         |

|          | signal <sup>(1)</sup>                                        | 1-MHz band over carrier (V <sub>CNTL</sub> = 0, 0.8)                                     |      | 0.18, 0.75            |     |         |

|          |                                                              | V <sub>CNTL</sub> = 0.6 V (22-dB total channel gain)                                     | 68   | 70                    |     |         |

|          | Signal-to-noise ratio (SNR)                                  | $V_{CNTL}$ = 0, LNA = 18 dB, PGA = 24 dB                                                 | 58.3 | 63                    |     | dBFS    |

|          |                                                              | V <sub>CNTL</sub> = 0, LNA = 24 dB, PGA = 24 dB                                          |      | 58                    |     |         |

|          | Narrow-band SNR                                              | SNR over 2-MHz band around carrier at V <sub>CNTL</sub> = 0.6 V (22-dB total gain)       | 75   | 77                    |     | dBFS    |

|          | Input common-mode voltage                                    | At INP and INM pins                                                                      |      | 2.2                   |     | V       |

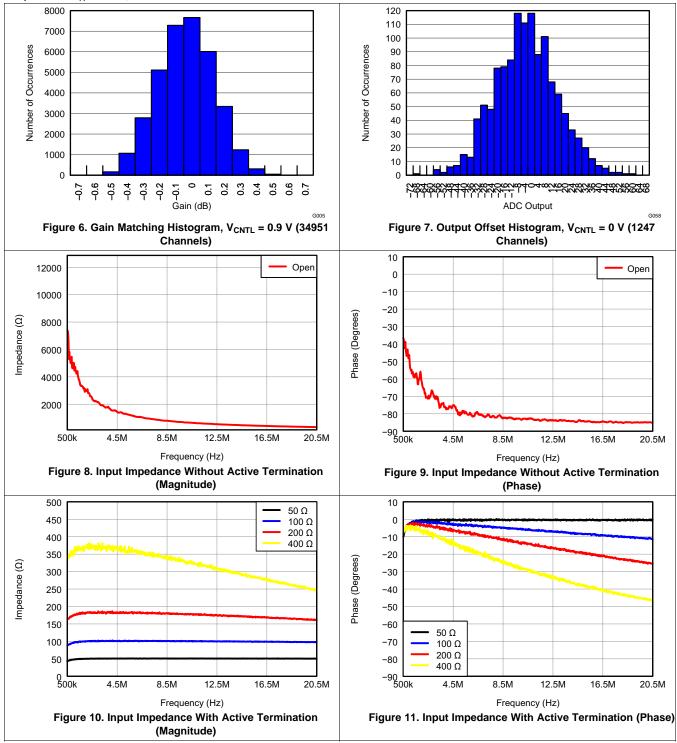

|          |                                                              |                                                                                          |      | 8                     |     | kΩ      |

|          | Input resistance                                             | Preset active termination enabled                                                        | 50,1 | 00,200,400            |     | Ω       |

|          | Input capacitance                                            |                                                                                          |      | 20                    |     | pF      |

|          | Input control voltage                                        | V <sub>CNTLP</sub> - V <sub>CNTLM</sub>                                                  | 0    |                       | 1.5 | V       |

|          | Common-mode voltage                                          | V <sub>CNTLP</sub> and V <sub>CNTLM</sub>                                                |      | 0.75                  |     | V       |

|          | Gain range                                                   |                                                                                          |      | -40                   |     | dB      |

|          | Gain slope                                                   | V <sub>CNTL</sub> = 0.1 to 1.1 V                                                         |      | 35                    |     | dB/V    |

|          | Input resistance                                             | Between V <sub>CNTLP</sub> and V <sub>CNTLM</sub>                                        |      | 200                   |     | kΩ      |

|          | Input capacitance                                            | Between V <sub>CNTLP</sub> and V <sub>CNTLM</sub>                                        |      | 1                     |     | pF      |

| _        | TGC response time                                            | V <sub>CNTL</sub> = 0- to 1.5-V step function                                            |      | 1.5                   |     | μs      |

|          | Third-order LPF                                              |                                                                                          | 10,  | 15, 20, 30,<br>35, 50 |     | MHz     |

|          | Settling time for change in LNA gain                         |                                                                                          |      | 14                    |     | μs      |

|          | Settling time for change in active termination setting       |                                                                                          |      | 1                     |     | μs      |

(1) Noise correlation factor is defined as Nc / (Nu + Nc), where Nc is the correlated noise power in single channel; and Nu is the uncorrelated noise power in single channel. Its measurement follows the below equation, in which the SNR of single-channel signal and the SNR of summed eight-channel signal are measured.

$$\frac{N_{C}}{N_{u} + N_{C}} = \frac{10^{-\frac{8CH_{SNR}}{10}}}{\frac{10^{-\frac{1}{10}}}{10}} \times \frac{1}{\frac{1}{56}} - \frac{1}{7}$$

10 Submit Documentation Feedback

## **Electrical Characteristics (continued)**

AVDD\_5V = 5 V, AVDD = 3.3 V, AVDD\_ADC = 1.8 V, DVDD = 1.8 V, AC-coupled with 0.1  $\mu$ F at INP and bypassed to ground with 15 nF at INM, No active termination, V<sub>CNTL</sub> = 0 V,  $f_{IN}$  = 5 MHz, LNA = 18 dB, PGA = 24 dB, 14 bit, sample rate = 65 MSPS, LPF Filter = 15 MHz, low-noise mode, V<sub>OUT</sub> = -1 dBFS, Single-ended V<sub>CNTL</sub> mode, VCNTLM = GND, ADC configured in internal reference mode, internal 500- $\Omega$  CW feedback resistor, CMOS CW clocks, at ambient temperature, T<sub>A</sub> = 25°C, Digital demodulator is disabled unless otherwise noted. Min and max values are specified across full-temperature range with AVDD\_5 V = 5 V, AVDD = 3.3 V, AVDD\_ADC = 1.8 V, DVDD = 1.8 V.

|         | PARAMETER                    | TEST CONDITIONS                                                                                                                                                                                    | MIN  | TYP                 | MAX | UNIT    |

|---------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|-----|---------|

| AC ACCI | JRACY                        |                                                                                                                                                                                                    |      |                     |     |         |

|         | LPF bandwidth tolerance      |                                                                                                                                                                                                    |      | ±5%                 |     |         |

|         | CH-CH group delay variation  | 2 to 15 MHz                                                                                                                                                                                        |      | 2                   |     | ns      |

|         | CH-CH phase variation        | 15-MHz signal                                                                                                                                                                                      |      | 11                  |     | ۰       |

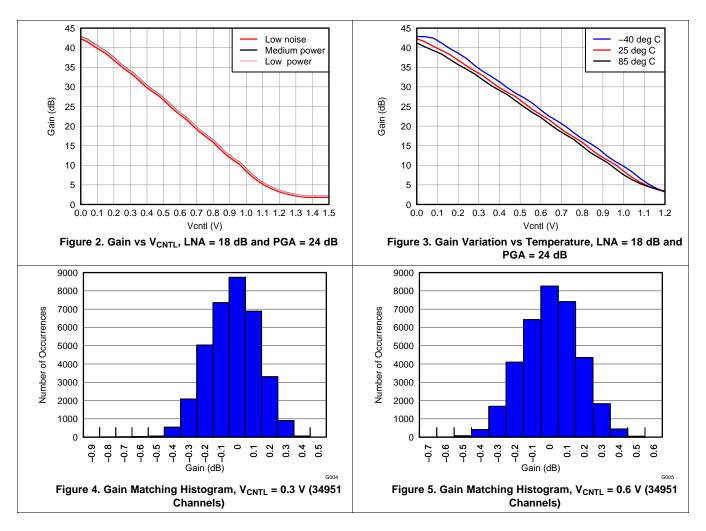

|         |                              | 0 V < V <sub>CNTL</sub> < 0.1 V (Dev-to-Dev)                                                                                                                                                       |      | ±0.5                |     |         |

|         | Gain matching                | 0.1 V < V <sub>CNTL</sub> < 1.1 V(Dev-to-Dev)                                                                                                                                                      | -1.1 | ±0.5                | 1.1 | dB      |

|         |                              | 1.1 V < V <sub>CNTL</sub> < 1.5 V (Dev-to-Dev)                                                                                                                                                     |      | ±0.5                |     | 1       |

|         | Gain matching                | Channel-to-channel                                                                                                                                                                                 |      | ±0.25               |     | dB      |

|         | Output offset                | V <sub>CNTL</sub> = 0, PGA = 24 dB, LNA = 18 dB                                                                                                                                                    | -100 |                     | 100 | LSB     |

| AC PERF | ORMANCE                      |                                                                                                                                                                                                    |      |                     |     |         |

|         |                              | $F_{IN} = 2 \text{ MHz}; V_{OUT} = -1 \text{ dBFS}$                                                                                                                                                |      | -60                 |     |         |

|         |                              | $F_{IN} = 5 \text{ MHz}; V_{OUT} = -1 \text{ dBFS}$                                                                                                                                                |      | -60                 |     | I       |

| HD2     | Second-harmonic distortion   | $\begin{array}{l} F_{IN}=5\ MHz;\ V_{IN}{=}\ 500\ mV_{PP},\\ V_{OUT}=-1\ dBFS,\ LNA=18\ dB,\ V_{CNTL}{=}\ 0.88\ V \end{array}$                                                                     |      | -55                 |     | dBc     |

|         |                              | $\label{eq:Final} \begin{array}{l} F_{IN}=5\mbox{ MHz; }V_{IN}=250\mbox{ mV}_{PP},\\ V_{OUT}=-1\mbox{ dBFS, LNA}=24\mbox{ dB, }V_{CNTL}=0.88\mbox{ V} \end{array}$                                 |      | -55                 |     |         |

|         |                              | F <sub>IN</sub> = 2 MHz; V <sub>OUT</sub> = -1 dBFS                                                                                                                                                |      | -50                 |     |         |

|         |                              | F <sub>IN</sub> = 5 MHz; V <sub>OUT</sub> = -1 dBFS                                                                                                                                                |      | -50                 |     | 1       |

| HD3     | Third-harmonic distortion    | $\label{eq:Final} \begin{array}{l} F_{iN}=5~MHz;~V_{iN}=500~mV_{PP},\\ V_{OUT}=-1~dBFS,~LNA=18~dB,~V_{CNTL}=0.88~V \end{array}$                                                                    |      | -50                 |     | dBc     |

|         |                              | $\label{eq:Final} \begin{split} F_{IN} &= 5 \ \text{MHz}; \ V_{IN} = 250 \ \text{mV}_{PP}, \\ V_{OUT} &= -1 \text{dBFS}, \ \text{LNA} = 2 \ \text{ddB}, \ V_{CNTL} &= 0.88 \ \text{V} \end{split}$ |      | -50                 |     |         |

| THD     | Total bases aris distantian  | F <sub>IN</sub> = 2 MHz; V <sub>OUT</sub> = -1 dBFS                                                                                                                                                |      | -50                 |     | -10-    |

| THD     | Total harmonic distortion    | F <sub>IN</sub> = 5 MHz; V <sub>OUT</sub> = - 1dBFS                                                                                                                                                |      | -50                 |     | dBc     |

| IMD3    | Intermodulation distortion   | $f_1 = 5 \text{ MHz at} -1 \text{ dBFS},$<br>$f_2 = 5.01 \text{ MHz at} -27 \text{ dBFS}$                                                                                                          |      | -60                 |     | dBc     |

| XTALK   | Cross-talk                   | F <sub>IN</sub> = 5 MHz; V <sub>OUT</sub> = -1 dBFS                                                                                                                                                |      | -65                 |     | dB      |

|         | Phase noise                  | kHz off 5 MHz (V <sub>CNTL</sub> = 0 V)                                                                                                                                                            |      | -132                |     | dBc/Hz  |

| LNA     |                              |                                                                                                                                                                                                    |      |                     |     |         |

|         | Input referred voltage noise | Rs = 0 $\Omega$ , $f$ = 2 MHz, Rin = High Z, Gain = 24, 18, 15 dB                                                                                                                                  | 0.6  | 3, 0.70, 0.9        |     | nV/rtHz |

|         | High-pass filter (HPF)       | -3 dB cut-off frequency                                                                                                                                                                            | 5    | 0, 100, 150,<br>200 |     | kHz     |

|         | LNA linear output            |                                                                                                                                                                                                    |      | 4                   |     | Vpp     |

| VCAT+ P | GA                           |                                                                                                                                                                                                    |      |                     |     |         |

|         | VCAT input noise             | 0-dB, -40-dB attenuation                                                                                                                                                                           |      | 2, 10.5             |     | nV/rtHz |

|         | PGA input noise              | 24 dB, 30 dB                                                                                                                                                                                       |      | 1.75                |     | nV/rtH  |

|         | -3 dB HPF cut-off frequency  |                                                                                                                                                                                                    |      | 80                  |     | kHz     |

## **Electrical Characteristics (continued)**

AVDD\_5V = 5 V, AVDD = 3.3 V, AVDD\_ADC = 1.8 V, DVDD = 1.8 V, AC-coupled with 0.1  $\mu$ F at INP and bypassed to ground with 15 nF at INM, No active termination, V<sub>CNTL</sub> = 0 V,  $f_{IN}$  = 5 MHz, LNA = 18 dB, PGA = 24 dB, 14 bit, sample rate = 65 MSPS, LPF Filter = 15 MHz, low-noise mode, V<sub>OUT</sub> = -1 dBFS, Single-ended V<sub>CNTL</sub> mode, VCNTLM = GND, ADC configured in internal reference mode, internal 500- $\Omega$  CW feedback resistor, CMOS CW clocks, at ambient temperature, T<sub>A</sub> = 25°C, Digital demodulator is disabled unless otherwise noted. Min and max values are specified across full-temperature range with AVDD\_5 V = 5 V, AVDD = 3.3 V, AVDD\_ADC = 1.8 V.

|                   | PARAMETER                                              | TEST CONDITIONS                                                                                                                             | MIN TYP       | MAX | UNIT    |

|-------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----|---------|

| CW DOP            | PLER                                                   | <u> </u>                                                                                                                                    |               |     |         |

|                   |                                                        | 1-channel mixer, LNA = 24 dB, 500- $\Omega$ feedback resistor                                                                               | 0.8           |     |         |

| en (RTI)          | Input voltage noise (CW)                               | 8-channel mixer, LNA = 24 dB, 62.5- $\Omega$ feedback resistor                                                                              | 0.33          |     | nV/rtHz |

| (                 |                                                        | 1-channel mixer, LNA = 24 dB, 500-Ω feedback resistor                                                                                       | 12            |     |         |

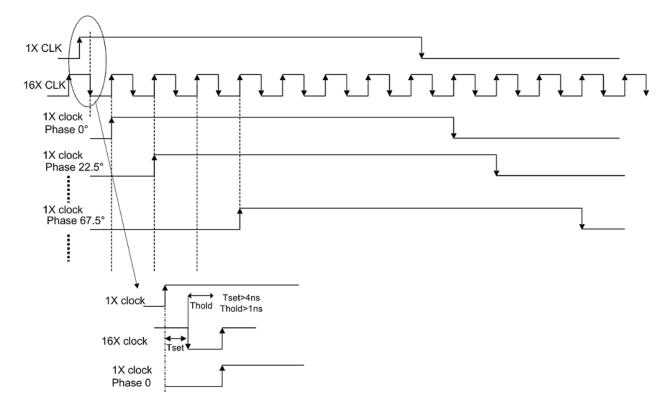

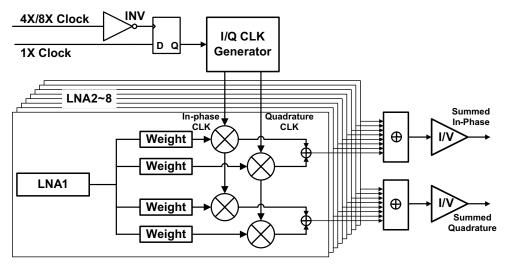

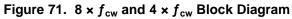

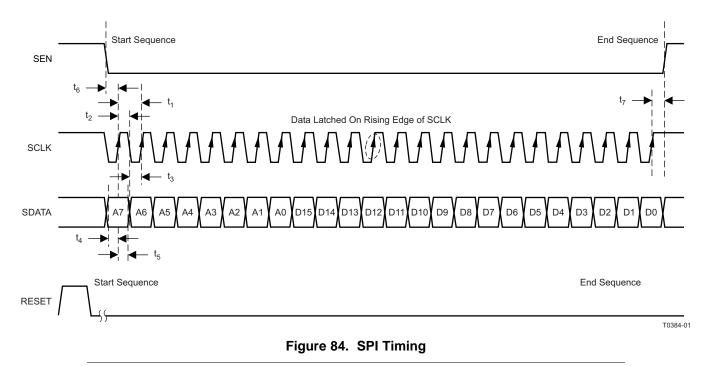

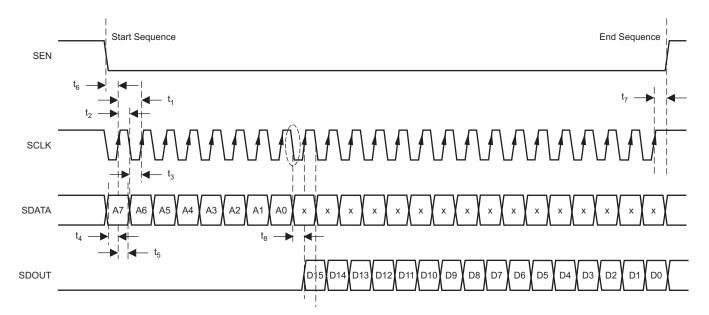

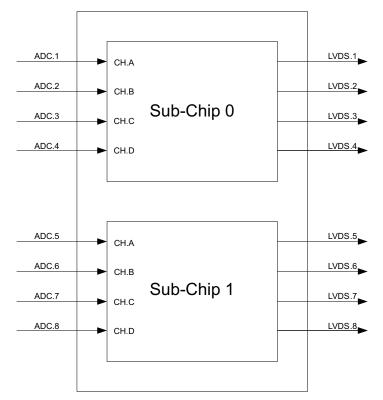

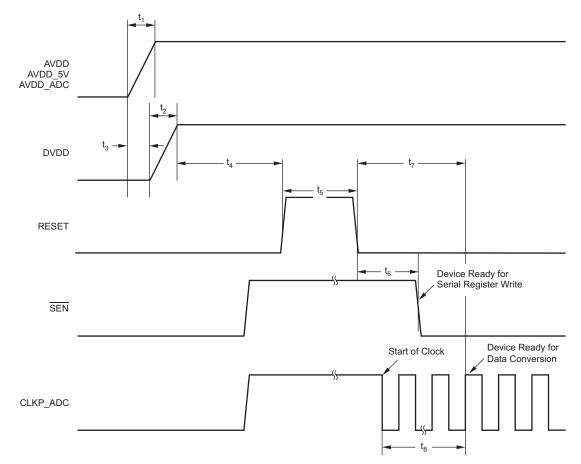

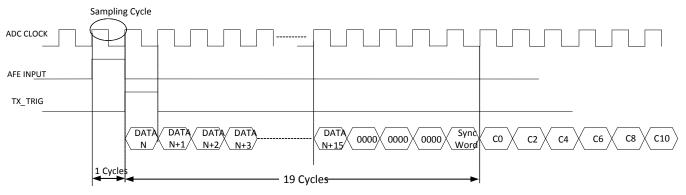

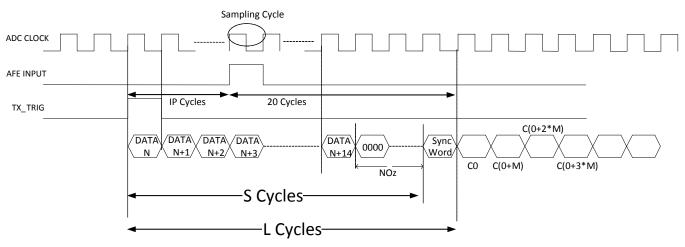

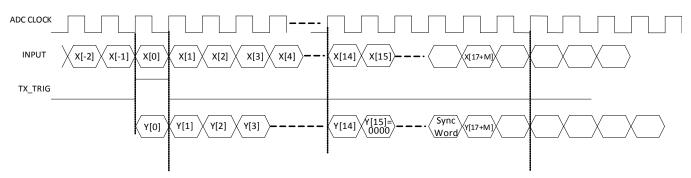

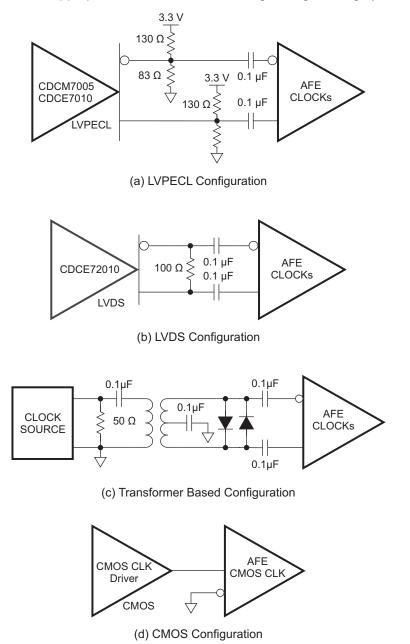

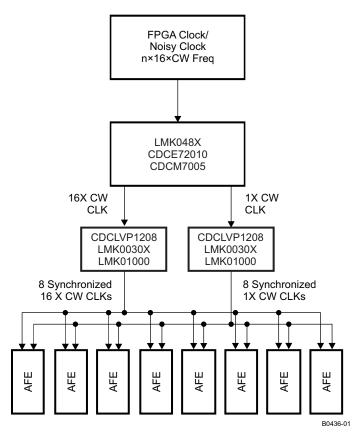

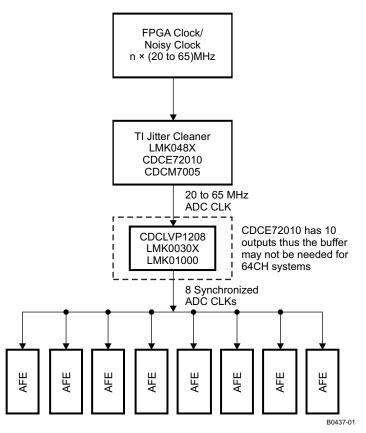

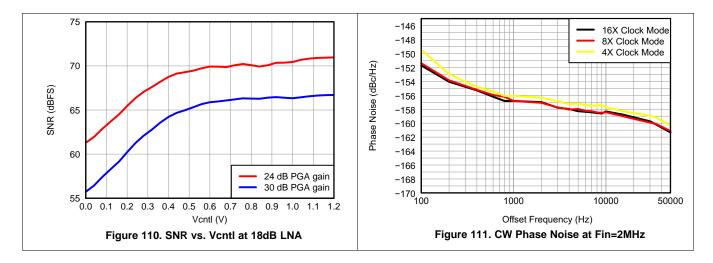

| en (RTO)          | Output voltage noise (CW)                              | 8-channel mixer, LNA = 24 dB, 62.5- $\Omega$ feedback resistor                                                                              | 5             |     | nV/rtHz |