Sample &

Buv

# UCC28050, UCC28051, UCC38050, UCC38051

SLUS515G - SEPTEMBER 2002 - REVISED DECEMBER 2015

# UCC2805x, UCC3805x Transition Mode PFC Controller

# **1** Features

**Fexas**

Instruments

- Transition Mode PFC Controller for Low Implementation Cost

- Industry Pin Compatibility With Improved Feature

Set

- Improved Transient Response With Slew-Rate

Comparator

- Zero Power Detect to Prevent Overvoltage Protection (OVP) During Light Load Conditions

- Accurate Internal VREF for Tight Output Regulation

- Two UVLO Options

- OVP, Open-Feedback Protection, and Enable Circuits

- ±750-mA Peak Gate Drive Current

- Low Start-Up and Operating Currents

- Lead (Pb)-Free Packages

# 2 Applications

- Single-Stage PFC Flyback Converters for Lighting and Motor Drives

- Switch-Mode Power Supplies for Desktops, Monitors, TVs, and Set Top Boxes (STBs)

- AC Adapter Front-End Power Supplies

- Electronic Ballasts

# 3 Description

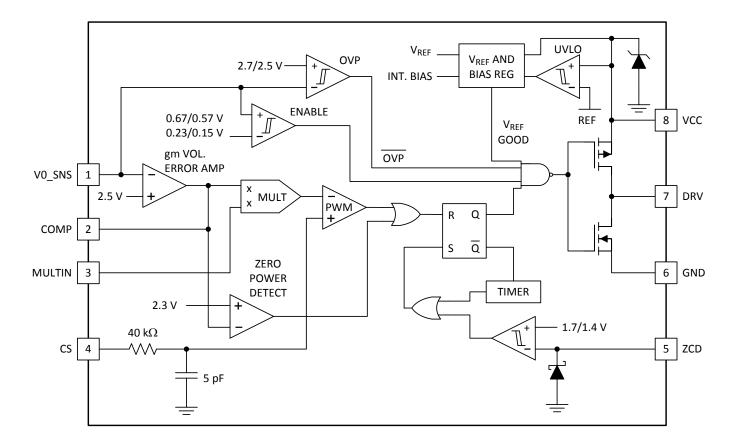

The UCC38050 and UCC38051 are PFC controllers for low-to-medium power applications requiring compliance with IEC 1000-3-2 harmonic reduction standard. The controllers are designed for a boost preregulator operating in transition mode (also referred to as boundary-conduction mode or critical conduction-mode operation). They feature а transconductance voltage amplifier for feedback error processing, a simple multiplier for generating a current command proportional to the input voltage, a current-sense (PWM) comparator, PWM logic, and a totem-pole driver for driving an external FET.

In the transition mode operation, the PWM circuit is self-oscillating, with the turnon being governed by an inductor zero-current detector (ZCD pin), and the turnoff being governed by the current-sense comparator. Additionally, the controller provides features such as peak current limit, default timer, overvoltage protection (OVP) and enable.

# Device Information<sup>(1)</sup>

| PART NUMBER                        | PACKAGE  | BODY SIZE (NOM)   |

|------------------------------------|----------|-------------------|

| UCC28050,                          | SOIC (8) | 3.91 mm × 4.90 mm |

| UCC28051,<br>UCC38050,<br>UCC38051 | PDIP (8) | 6.35 mm × 9.81 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

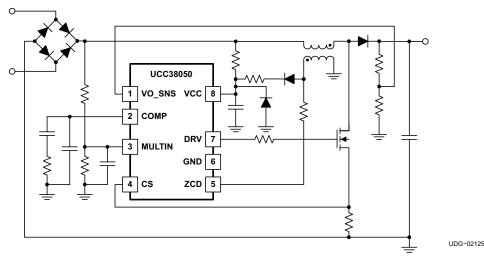

# **Simplified Application Diagram**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

**Table of Contents**

| Fea  | tures 1                            |    |

|------|------------------------------------|----|

| Арр  | lications 1                        | 8  |

| Des  | cription 1                         |    |

| Rev  | ision History 2                    |    |

| Pin  | Configuration and Functions 3      | 9  |

| Spe  | cifications 4                      | 1  |

| 6.1  | Absolute Maximum Ratings 4         |    |

| 6.2  | ESD Ratings 4                      |    |

| 6.3  | Recommended Operating Conditions 4 | 1  |

| 6.4  |                                    |    |

| 6.5  | Electrical Characteristics5        |    |

| 6.6  | Typical Characteristics 7          |    |

| Deta | ailed Description 10               |    |

| 7.1  | Overview 10                        |    |

|      | Functional Block Diagram 11        |    |

| 7.3  | Feature Description 12             | 1. |

#### **Revision History** 4

1

2 3 4

5

6

7

# Changes from Revision F (March 2009) to Revision G

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section. ..... 1

|    | 7.4   | Device Functional Modes 14         |

|----|-------|------------------------------------|

| 8  | App   | lication and Implementation 16     |

|    | 8.1   | Application Information 16         |

|    | 8.2   | Typical Application 16             |

| 9  | Pow   | er Supply Recommendations          |

| 10 | Laye  | out                                |

|    | 10.1  | Layout Guidelines 22               |

|    | 10.2  | Layout Example 22                  |

| 11 | Dev   | ice and Documentation Support      |

|    | 11.1  | Device Support 23                  |

|    | 11.2  | Related Links 23                   |

|    | 11.3  | Community Resources 23             |

|    | 11.4  | Trademarks 23                      |

|    | 11.5  | Electrostatic Discharge Caution 23 |

|    | 11.6  | Glossary 23                        |

| 12 | Mec   | hanical, Packaging, and Orderable  |

|    | Infor | mation 24                          |

Copyright © 2002–2015, Texas Instruments Incorporated

www.ti.com

Page

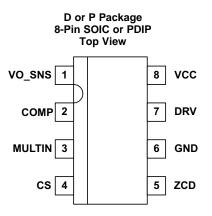

# 5 Pin Configuration and Functions

# **Pin Functions**

| Р      | IN  |     | DECODIDION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| СОМР   | 2   | 0   | Output of the transconductance error amplifier. Loop compensation components are connected between this pin and ground. The output current capability of this pin is $10-\mu$ A under normal conditions, but increases to approximately 1-mA when the differential input is greater than the specified values in the specifications table. This voltage is one of the inputs to the multiplier, with a dynamic input range of 2.5 V to 3.8 V. During zero power or overvoltage conditions, this pin goes below 2.5 V nominal. When it goes below 2.3 V, the zero power comparator is activated, which prevents the gate drive from switching.                               |

| CS     | 4   | 1   | This pin senses the instantaneous switch current in the boost switch and uses it as the internal ramp for PWM comparator. The internal circuitry filters out switching noise spikes without requiring external components. In addition, an external R-C filter may be required to suppress the noise spikes. An internal clamp on the multiplier output terminates the switching cycle if this pin voltage exceeds 1.7 V. Additional external filtering may be required. CS threshold is approximately equal to:<br>$L = \frac{\left(V_{AC(min)}\right)^2 \times \left(V_{OUT} - \sqrt{2} \times V_{AC(min)}\right)}{2 \times F_{s(min)} \times V_{OUT} \times P_{IN}}$ (1) |

|        |     |     | V <sub>OFFSET</sub> is approximately 75 mV to improve the zero crossing distortion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DRV    | 7   | о   | The gate drive output for an external boost switch. This output is capable of delivering up to 750-<br>mA peak currents during turn-on and turn-off. An external gate drive resistor may be needed to<br>limit the peak current depending on the $V_{CC}$ voltage being used. Below the UVLO threshold, the<br>output is held low.                                                                                                                                                                                                                                                                                                                                          |

| GND    | 6   | -   | The chip reference ground. All bypassing elements are connected to ground pin with shortest loops feasible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MULTIN | 3   | I   | This pin senses the instantaneous boost regulator input voltage through a voltage divider. The voltage acts as one of the inputs to the internal multiplier. Recommended operating range is 0 V to 2.5 V at high line.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VCC    | 8   | _   | The supply voltage for the chip. This pin should be bypassed with a high-frequency capacitor (greater than $0.1-\mu F$ ) and tied to GND. The UCC38050 has a wide UVLO hysteresis of approximately 6.3 V that allows use of a lower value supply capacitor on this pin for quicker and easier start-up. The UCC38051 has a narrow UVLO hysteresis with of about 2.8 V, and a start-up voltage of about 12.5 V for applications where the operation of the PFC device must be controlled by a downstream PWM controller.                                                                                                                                                     |

| VO_SNS | 1   | I   | This pin senses the boost regulator output voltage through a voltage divider. Internally, this pin is the inverting input to the transconductance amplifier (with a nominal value of 2.5 V) and also is input to the OVP comparator. Additionally, pulling this pin below the ENABLE threshold turns off the output switching, ensuring that the gate drive is held off while the boost output is pre-charging, and also ensuring no runaway if the feedback path is open.                                                                                                                                                                                                  |

| ZCD    | 5   | 1   | Input for the zero current detect comparator. The boost inductor current is indirectly sensed through the bias winding on the boost inductor. The ZCD pin input goes low when the inductor current reaches zero and that transition is detected. Internal active voltage clamps are provided to prevent this pin from going below ground or too high. If zero current is not detected within 400 $\mu$ s, a reset timer sets the latch and gate drive.                                                                                                                                                                                                                      |

Copyright © 2002–2015, Texas Instruments Incorporated

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                              |                         | MIN | MAX  | UNIT |

|--------------------------------------------------------------|-------------------------|-----|------|------|

| Supply voltage, V <sub>CC</sub>                              | (Internally clamped)    |     | 20   | V    |

| Input current into V <sub>CC</sub> clamp                     | I <sub>DD</sub>         |     | 30   | mA   |

| Input current                                                | ZCD                     |     | ±10  | mA   |

| Gate drive current (peak), I <sub>DRV</sub>                  | DRV                     |     | ±750 | mA   |

| Input voltage, V <sub>CC</sub>                               | VO_SNS, MULTIN, CS      |     | 5    | V    |

| Maximum negative voltage                                     | VO_SNS, MULTIN, DRV, CS |     | -0.5 | V    |

| Device disciplation of T                                     | D package               |     | 650  | mW   |

| Power dissipation at $T_A = 50^{\circ}C$                     | P package               |     | 1    | W    |

| Operating junction temperature range                         | e, T <sub>J</sub>       | -55 | 150  | °C   |

| Storage temperature, T <sub>stg</sub>                        |                         | -65 | 150  | °C   |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | )                       |     | 300  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                                                                   |                                                                          | VALUE | UNIT |

|--------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------|-------|------|

| SOIC P             | ACKAGE                                                            |                                                                          |       |      |

|                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000                                                                    | V     |      |

| V <sub>(ESD)</sub> | Electrostatic discharge                                           | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{(2)}$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                | MIN                      | NOM MAX | UNIT |

|------------------------------------------------|--------------------------|---------|------|

| VCC input voltage from a low-impedance source  | VCC <sub>OFF</sub> + 1 V | 18      | V    |

| Operating junction temperature, T <sub>J</sub> | -40                      | 125     | °C   |

# 6.4 Thermal Information

|                       |                                              |          | UCC2805x, UCC3805x |      |  |

|-----------------------|----------------------------------------------|----------|--------------------|------|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | P (PDIP)           | UNIT |  |

|                       |                                              | 8 PINS   | 8 PINS             |      |  |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 113.6    | 55.6               | °C/W |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 60.3     | 45.5               | °C/W |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 54.3     | 32.7               | °C/W |  |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 14       | 23.1               | °C/W |  |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 53.8     | 32.6               | °C/W |  |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

Submit Documentation Feedback

4

Product Folder Links: UCC28050 UCC28051 UCC38050 UCC38051

# 6.5 Electrical Characteristics

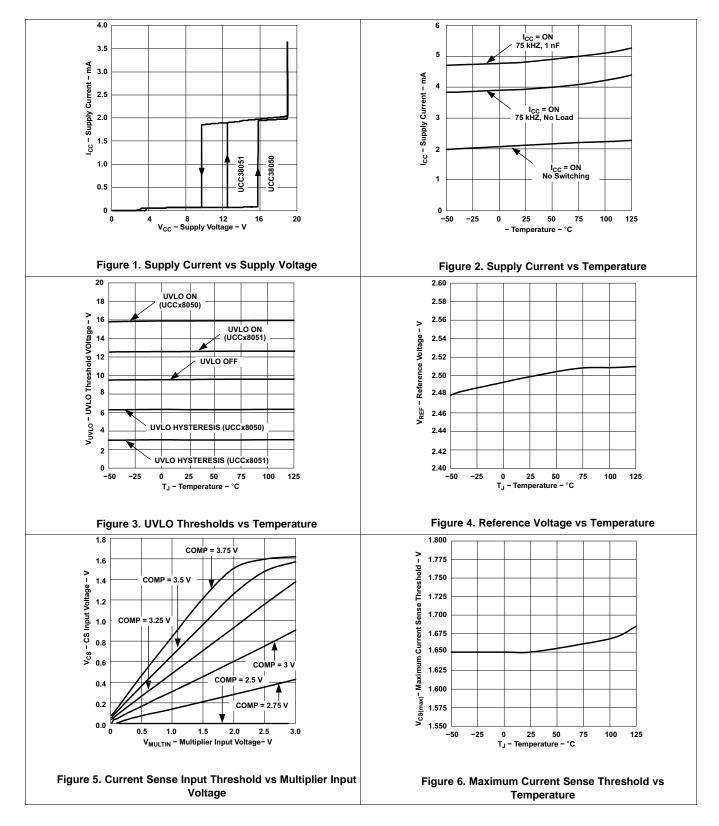

$T_A = 0^{\circ}C$  to 70°C for the UCC3805x, -40°C to +105°C for the UCC2805x,  $T_A = T_J$ ,  $V_{CC} = 12$  V.

| PARAMETER                                |                     | TEST CONDITIONS                                   | MIN          | ТҮР         | MAX         | UNIT |

|------------------------------------------|---------------------|---------------------------------------------------|--------------|-------------|-------------|------|

| SUPPLY                                   |                     |                                                   |              |             |             |      |

| V <sub>CC</sub> operating voltage        |                     |                                                   |              |             | 18          | V    |

| Shunt voltage                            |                     | I <sub>VCC</sub> = 25 mA                          | 18           | 19          | 20          | V    |

| Supply current, off                      |                     | $V_{CC} = V_{CC}$ turnon threshold -300 mV        |              | 75          | 125         | μA   |

| Supply current, disabled                 |                     | VO_SNS = 0.5 V                                    |              | 2           | 4           | mA   |

| Supply current, on                       |                     | 75 kHz, C <sub>L</sub> = 0 nF                     |              | 4           | 6           | mA   |

| Supply current, dynamic oper             | ating               | 75 kHz, C <sub>L</sub> = 1 nF                     |              | 5           | 7           | mA   |

| UVLO                                     |                     |                                                   |              |             |             |      |

|                                          | UCCx8050            |                                                   | 15.4         | 15.8        | 16.4        |      |

| $V_{CC}$ turnon threshold                | UCCx8051            |                                                   | 12           | 12.5        | 13          | V    |

| V <sub>CC</sub> turnoff threshold        |                     |                                                   | 9.4          | 9.7         | 10          | V    |

| IIV/I O hystore                          | UCCx8050            |                                                   | 5.8          | 6.3         | 6.8         |      |

| UVLO hysteresis                          | UCCx8051            |                                                   | 2.3          | 2.8         | 3.3         | V    |

| VOLTAGE AMPLIFIER (VO_SNS                | )                   | · · · · · · · · · · · · · · · · · · ·             |              |             | 1           |      |

|                                          | UCC3805x            |                                                   | 2.46         | 2.5         | 2.54        |      |

| Input voltage (V <sub>REF</sub> )        | UCC2805x            |                                                   | 2.45         | 2.5         | 2.55        | V    |

| Input bias current                       |                     |                                                   |              |             | 0.5         | μA   |

| V <sub>COMP</sub> high                   |                     | VO_SNS = 2.1 V                                    | 4.5          |             | 5.5         | V    |

| V <sub>COMP</sub> low                    |                     | VO_SNS = 2.55 V                                   |              | 1.8         | 2.45        | V    |

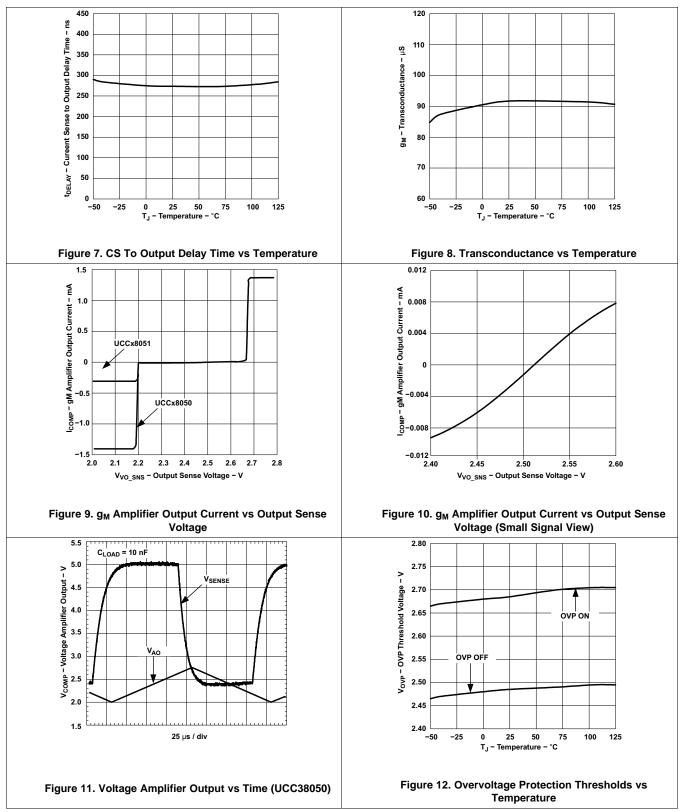

| gM                                       |                     | T <sub>J</sub> = 25 °C, V <sub>COMP</sub> = 3.5 V | 60           | 90          | 130         | μS   |

| 0                                        | UCCx8050            | VO_SNS = 2.1 V, V <sub>COMP</sub> = 3.5 V         | -0.2         | -0.1        |             | mA   |

| Source current                           | UCCx8051            | VO_SNS = 2.1 V, V <sub>COMP</sub> = 2.5 V         | -200         | -300        | -400        | μA   |

| Sink current                             |                     | VO_SNS = 2.7 V, $V_{COMP}$ = 3.5 V                | 0.2          | 1           |             | mA   |

| OVER VOLTAGE PROTECTION                  | ENABLE              |                                                   |              |             |             |      |

| 0                                        | UCCx8050            |                                                   | VREF + 0.165 | VREF + 0.19 | VREF + 0.21 |      |

| Overvoltage reference                    | UCCx8051            |                                                   | VREF + 0.15  | VREF + 0.18 | VREF + 0.21 | V    |

| 1 hastene ele                            | UCCx8050            |                                                   | 175          | 200         | 225         |      |

| Hysteresis                               | UCCx8051            |                                                   | 150          | 180         | 210         | mV   |

| <b>F</b> . 1 . 4                         | UCCx8050            |                                                   | 0.62         | 0.67        | 0.72        |      |

| Enable threshold                         | UCCx8051            |                                                   | 0.18         | 0.23        | 0.28        | V    |

| Enable hysteresis                        | ·                   |                                                   | 0.05         | 0.1         | 0.2         | V    |

| MULTIPLIER                               |                     |                                                   |              |             |             |      |

| Multiplier gain constant (k)             |                     | V <sub>MULTIN</sub> = 0.5 V, COMP = 3.5 V         | 0.43         | 0.65        | 0.87        | 1/V  |

| Dynamic input range, V <sub>MULTIN</sub> | INPUT               |                                                   | 0 to 2.5     | 0 to 3.5    |             | V    |

| Dynamic input range, COMP                | INPUT               |                                                   | 2.5 to 3.8   | 2.5 to 4    |             | V    |

| Input bias current, MULTIN               |                     |                                                   |              | 0.1         | 1           | μA   |

| ZERO POWER                               |                     | L                                                 |              |             | 1           |      |

| Zero power comparator thres              | hold <sup>(1)</sup> | Measured on V <sub>COMP</sub>                     | 2.1          | 2.3         | 2.5         | V    |

(1) Ensured by design. Not production tested.

# **Electrical Characteristics (continued)**

## $T_A = 0^{\circ}C$ to 70°C for the UCC3805x, -40°C to +105°C for the UCC2805x, $T_A = T_J$ , $V_{CC} = 12$ V.

| PARAMETER                                    | TEST CONDITIONS                                 | MIN  | TYP  | MAX | UNIT |

|----------------------------------------------|-------------------------------------------------|------|------|-----|------|

| ZERO CURRENT DETECT                          |                                                 |      |      |     |      |

| Input threshold (rising edge) <sup>(1)</sup> |                                                 | 1.5  | 1.7  | 2   | V    |

| Hysteresis <sup>(1)</sup>                    |                                                 | 250  | 350  | 450 | mV   |

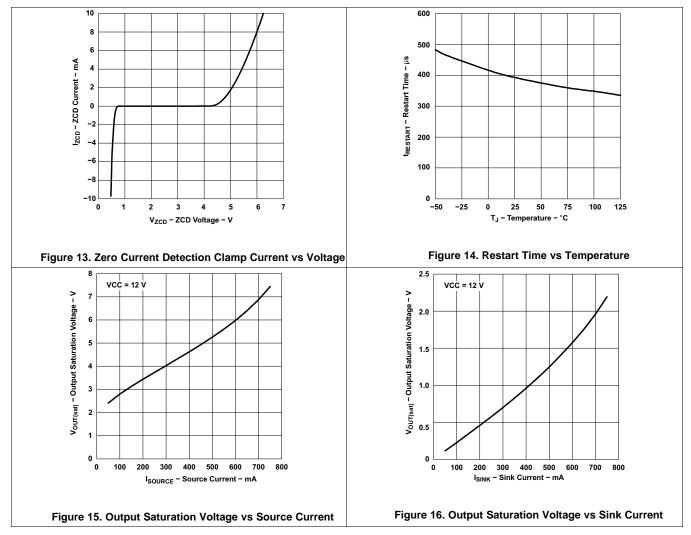

| Input high clamp                             | I = 3 mA                                        |      | 5    | 6   | V    |

| Input low clamp                              | I = -3 mA                                       | 0.3  | 0.65 | 0.9 | V    |

| Restart time delay                           |                                                 | 200  | 400  |     | μs   |

| CURRENT SENSE COMPARATOR                     |                                                 |      |      |     |      |

| Input bias current                           | CS = 0 V                                        |      | 0.1  | 1   | μA   |

| Input offset voltage <sup>(1)</sup>          |                                                 | -10  |      | 10  | mV   |

| Delay to output                              | CS to DRV                                       |      | 300  | 450 | ns   |

| Maximum current sense threshold voltage      |                                                 | 1.55 | 1.7  | 1.8 | V    |

| PFC GATE DRIVER                              |                                                 |      |      |     |      |

| GT1 pull-up resistance                       | $I_{OUT} = -125 \text{ mA}$                     |      | 5    | 12  | Ω    |

| GT1 pull-down resistance                     | I <sub>OUT</sub> = 125 mA                       |      | 2    | 10  | Ω    |

| GT1 output rise time                         | $C_{LOAD} = 1 \text{ nF}, R_{LOAD} = 10 \Omega$ |      | 25   | 75  | ns   |

| GT1 output fall time                         | $C_{LOAD} = 1 \text{ nF}, R_{LOAD} = 10 \Omega$ |      | 10   | 50  | ns   |

# 6.6 **Typical Characteristics**

# **Typical Characteristics (continued)**

8

Product Folder Links: UCC28050 UCC28051 UCC38050 UCC38051

### **Typical Characteristics (continued)**

Product Folder Links: UCC28050 UCC28051 UCC38050 UCC38051

# 7 Detailed Description

# 7.1 Overview

The UCC38050 and UCC38051 are PFC controllers for low-to-medium power applications requiring compliance with IEC 1000-3-2 harmonic reduction. The controller is designed for a boost preregulator operating in transition mode (also referred to as boundary-conduction mode or critical conduction-mode operation). It features a transconductance voltage amplifier for feedback error processing, a simple multiplier for generating a current command proportional to the input voltage, a current-sense (PWM) comparator, PWM logic, and a totem-pole driver for driving an external FET.

The UCC38050 and UCC38051, while being pin-compatible with other industry controllers providing similar functionality, offer many feature enhancements and tighter specifications, leading to an overall reduction in system implementation cost. The system performance is enhanced by incorporation of a zero-power detect function, which allows the controller output to shut down at light load conditions without running into overvoltage. The device also features innovative slew rate enhancement circuits, which improve the large signal transient performance of the voltage error amplifier. The low start-up and operating currents of the device result in low power consumption and ease of start-up. Highly accurate internal bandgap reference leads to tight regulation of output voltage in normal and OVP conditions, resulting in higher system reliability. The enable comparator ensures that the controller is off if the feedback sense path is broken or if the input voltage is very low.

There are two key parameteric differences between UCC38050 and UCC38051. The UVLO turn-on threshold of UCC38050 is 15.8 V, while for UCC38051 it is 12.5 V. Secondly, the gM amplifier source current for UCC38050 is typically 1.3 mA, while for UCC38051 it is 300  $\mu$ A. The higher UVLO turn-on threshold of the UCC38050 allows quicker and easier start-up with a smaller V<sub>CC</sub> capacitance, while the lower UVLO turn-on threshold of UCC38051 allows the operation of the PFC chip to be easily controlled by the downsteam PWM controller in two-stage power converters. The UCC38050 gM amplifier also provides a full 1.3-mA typical source current for faster start-up and improved transient response when output is low, either at start-up or during transient conditions. The UCC38051 scales this source current back down to 300- $\mu$ A typical source current to gradually increase the error voltage, preventing a step increase in line currents at start-up, but still providing good transient response. The UCC38051 is suitable for multiple applications, including AC adapters, where a two-stage power conversion is needed. The UCC38050 is suitable for applications such as electronic ballasts, where there is no down-stream PWM conversion and the advantages of a smaller V<sub>CC</sub> capacitor and improved transient response can be realized.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

### 7.3.1 UVLO and Reference Block

This block generates a precision reference voltage used to obtain tightly controlled UVLO threshold. In addition to generating a 2.5-V reference for the non-inverting terminal of the gM amplifier, it generates the reference voltages for blocks such as OVP, enable, zero power, and multiplier. An internal rail of 7.5 V is also generated, to drive all the internal blocks.

### 7.3.2 Error Amplifier

The voltage error amplifier in UCC3805x is a transcoductance amplifier, with a typical transconductance value of 90  $\mu$ S. A transconductance amplifier is advantageous in that the inverting input of the amplifier is solely determined by the external resistive-divider from the output voltage, and not the transient behavior of the amplifier itself. This allows the VO\_SNS pin to be used for sensing overvoltage conditions.

The sink and source capability of the error amplifier is approximately 10  $\mu$ A during normal operation of the amplifier. However, when the VO\_SNS pin voltage is beyond the normal operating conditions (VO\_SNS > 1.05 × V<sub>REF</sub>, VO\_SNS < 0.88 × V<sub>REF</sub>), additional circuitry to enhance the slew-rate of the amplifier is activated. Enhanced slew-rate of the compensation capacitor results in a faster start-up and transient response. This prevents the output voltage from drifting too high or too low, which can happen if the compensation capacitor were to be slewed by the normal slewing current of 10  $\mu$ A. When VO\_SNS falls below the normal range, the enhanced sink current capability is in excess of 1 mA. When VO\_SNS falls below the normal range, the UCC38050 can source more than 1 mA, and the UCC38051 sources approximately 300  $\mu$ A. The limited source current in the UCC38051 helps to gradually increase the error voltage on the COMP pin preventing a step increase in line current. The actual rate of increase of V<sub>COMP</sub> depends on the compensation network connected to the COMP pin.

## 7.3.3 Zero Current Detection and Re-Start Timer Blocks

When the boost inductor current becomes zero, the voltage at the power MOSFET drain end falls. This is indirectly sensed with a secondary winding connected to the ZCD pin. The internal active clamp circuitry prevents the voltage from going to a negative or a high positive value. The clamp has the sink and source capability of 10 mA. The resistor value in series with the secondary winding should be chosen to limit the ZCD current to less than 10 mA. The rising edge threshold of the ZCD comparator can be as high as 2 V. The auxiliary winding should be chosen such that the positive voltage (when the power MOSFET is off) at the ZCD pin is in excess of 2 V.

The restart timer attempts to set the gate drive high in case the gate drive remains off for more than 400  $\mu$ s nominally. The minimum guaranteed time period of the timer is 200  $\mu$ s. This translates to a minimum switching frequency of 5 kHz. In other words, the boost inductor value should be chosen for switching frequencies greater than 5 kHz.

### Feature Description (continued)

### 7.3.4 Enable Block

The gate drive signal is held low if the voltage at the VO\_SNS pin is less than the ENABLE threshold. This feature can disable the converter by pulling VO\_SNS low. If the output feedback path is broken, VO\_SNS is pulled to ground, and the output is disabled to protect the power stage.

## 7.3.5 Zero Power Block

When the output of the  $g_M$  amplifier goes below 2.3 V, the zero power comparator latches the gate drive signal low. The slew rate enhancement circuitry of the gM amplifier activated during overvoltage conditions slews the COMP pin to approximately 2.4 V. This ensures that the zero power comparator is not activated during transient behavior, when the slew rate enhancement circuitry is enhanced.

### 7.3.6 Multiplier Block

The multiplier block has two inputs. One is the error amplifier output voltage ( $V_{COMP}$ ), and the other is  $V_{MULTIN}$ , which is obtained by a resistive divider from the rectified line. The multiplier output is approximately 0.67 ×  $V_{MULTIN} \times (V_{COMP} - 2.5 \text{ V})$ . There is a positive offset of about 75 mV to the  $V_{MULTIN}$  signal because this improves the zero-crossing distortion and thus the THD performance of the controller in the application. The dynamic range of the inputs can be found in *Electrical Characteristics*.

## 7.3.7 Overvoltage Protection (OVP) Block

The OVP feature in the part is not activated under most operating conditions because of the presence of the slew rate enhancement circuitry present in the error amplifier. As soon as the output voltage reaches to approximately 5% to 7% above the nominal value, the slew rate enhancement circuit is activated, and the error amplifier output voltage is pulled below the dynamic range of the multiplier block. This prevents further rise in output voltage.

If the COMP pin is not pulled low fast enough and the voltage rises further, the OVP circuit acts as a second line of protection. When the voltage at the VO\_SNS pin is more than 7.5% of the nominal value (> ( $V_{REF}$  + 0.19)), the OVP feature is activated. It stops the gate drive from switching as long as the voltage at the VO\_SNS pin is above the nominal value ( $V_{REF}$ ). This prevents the output DC voltage from going above 7.5% of the nominal value designed for, and protects the switch and other components of the system such as the boost capacitor.

### 7.4 Device Functional Modes

### 7.4.1 Transition Mode Control

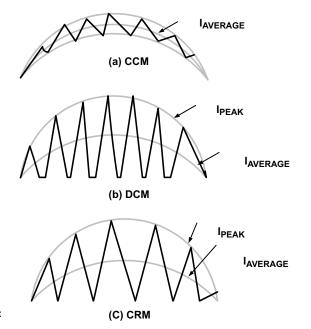

The boost converter, the most common topology used for power factor correction, can operate in two modes: continuous conduction code (CCM) and discontinuous conduction mode (DCM). Transition mode control, also referred to as critical conduction mode (CRM) or boundary conduction mode, maintains the converter at the boundary between CCM and DCM by adjusting the switching frequency.

The CRM converter typically uses a variation of hysteretic control, with the lower boundary equal to zero current. It is a variable frequency control technique that has inherently stable input current control while eliminating reverse recovery rectifier losses. As shown in Figure 17, the switch current is compared to the reference signal (output of the multiplier) directly. This control method has the advantage of simple implementation and good power factor correction.

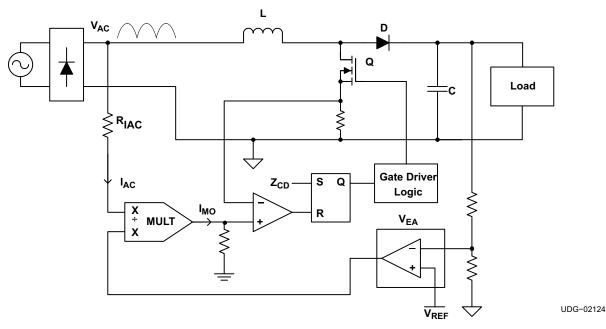

Figure 17. Basic Block Diagram of CRM Boost PFC

The power stage equations and the transfer functions of the CRM are the same as the CCM. However, implementations of the control functions are different. Transition mode forces the inductor current to operate just at the border of CCM and DCM. The current profile is also different, and affects the component power loss and filtering requirements. The peak current in the CRM boost is twice the amplitude of CCM, leading to higher conduction losses. The peak-to-peak ripple is twice the average current, which affects MOSFET switching losses and magnetics ac losses.

### UCC28050, UCC28051, UCC38050, UCC38051 SLUS515G-SEPTEMBER 2002-REVISED DECEMBER 2015

# **Device Functional Modes (continued)**

Note: Operating Frequency >> 120 Hz

UDG-02123

Figure 18. PFC Inductor Current Profiles

For low to medium power applications up to approximately 300 W, the CRM boost has an advantage in losses. The filtering requirement is not severe, and therefore is not a disadvantage. For medium to higher power applications, where the input filter requirements dominate the size of the magnetics, the CCM boost is a good choice due to lower peak currents (which reduces conduction losses) and lower ripple current (which reduces filter requirements). The main tradeoff in using CRM boost is lower losses due to no reverse recovery in the boost diode vs. higher ripple and peak currents.

# 8 Application and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 8.1 Application Information

The UCC38050 and UCC38051 are switch-mode controllers used in boost converters for power factor correction operating in transition mode. In the transition mode operation, the PWM circuit is self-oscillating, with the turnon being governed by an inductor zero-current detector (ZCD pin), and the turnoff being governed by the current-sense comparator. Additionally, the controller provides features such as peak current limit, default timer, OVP, and enable.

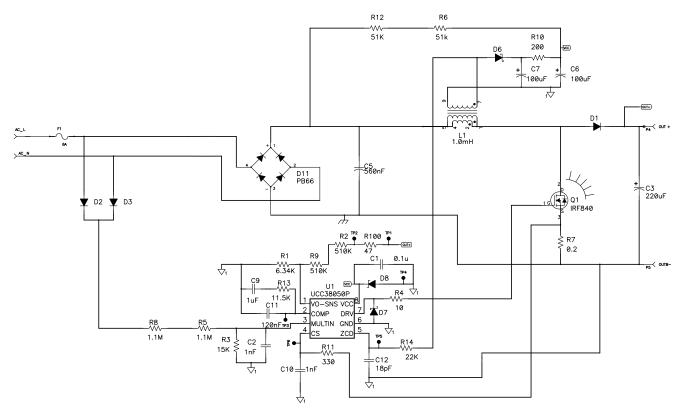

There are two key parametric differences between UCC38050 and UCC38051. The UVLO turnon threshold of UCC38050 is 15.8 V, while for UCC38051 it is 12.5 V. Secondly, the gM amplifier source current for UCC38050 is typically 1.3 mA, while for UCC38051 it is 300  $\mu$ A. The UCC38051 is suitable for multiple applications, including AC adapters, where a two-stage power conversion is needed. The UCC38050 is suitable for applications such as electronic ballasts, where there is no down-stream PWM conversion and the advantages of a smaller VCC capacitor and improved transient response can be realized. Figure 19 is an example of a critical conduction mode power factor correction boost converter utilizing the UCC38050.

# 8.2 Typical Application

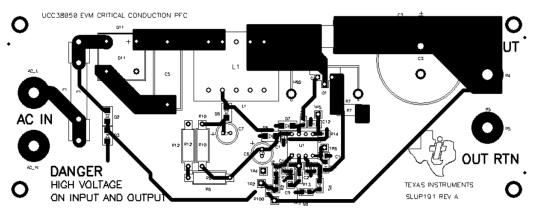

The UCC38050 is used for the off-line power factor corrected pre-regulator with operation over a universal input range of 85 V to 265 V with a 400-V<sub>DC</sub> regulated output. The schematic is shown in Figure 19, and the board layout for the reference design is shown in Figure 24.

Figure 19. Universal Line Input 100-W Boost Converter

Product Folder Links: UCC28050 UCC28051 UCC38050 UCC38051

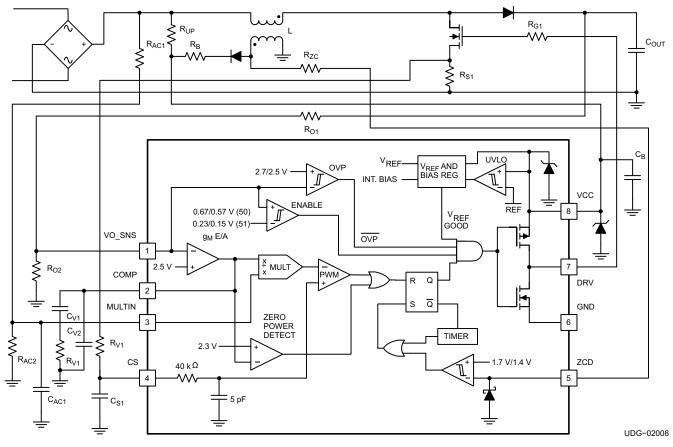

# **Typical Application (continued)**

Figure 20. Typical Application Diagram

# 8.2.1 Design Requirements

Table 1 shows the design requirements for a CCM, PFC boost converter utilizing the UCC38050.

|                  | PARAMETER                       | TEST CONDITION                                                    | MIN  | TYP | MAX | UNIT             |

|------------------|---------------------------------|-------------------------------------------------------------------|------|-----|-----|------------------|

| V <sub>IN</sub>  | Input voltage                   |                                                                   | 85   |     | 265 | V <sub>RMS</sub> |

|                  | Input frequency                 |                                                                   |      | 60  |     | Hz               |

| V <sub>OUT</sub> | Output voltage DC               | V <sub>IN</sub> = 85 V <sub>RMS</sub>                             | 370  | 400 | 425 | V                |

| V <sub>OUT</sub> | Output voltage DC               | V <sub>IN</sub> = 265 V <sub>RMS</sub>                            | 370  | 390 | 410 | V                |

| P <sub>OUT</sub> | Output power                    |                                                                   | 0    |     | 100 | W                |

|                  | Output voltage ripple           | V <sub>IN</sub> = 85 V <sub>RMS</sub>                             |      |     | 3%  |                  |

|                  | Efficiency                      | P <sub>OUT</sub> = 100 W                                          | 90%  |     |     |                  |

|                  | Total harmonic distortion (THD) | $V_{IN} = 85 V_{RMS}, P_{OUT} = 100 W$                            |      | 5%  |     |                  |

|                  | Total harmonic distortion (THD) | V <sub>IN</sub> = 265 V <sub>RMS</sub> , P <sub>OUT</sub> = 100 W |      | 15% |     |                  |

|                  | Hold-up time                    |                                                                   | 16.7 |     |     | ms               |

Copyright © 2002–2015, Texas Instruments Incorporated

#### 8.2.2 Detailed Design Procedure

For a selected  $V_{OUT}$  and minimum switching frequency, the following equations outline the design guidelines for power stage component selection, using a universal input, 100-W PFC converter with an output voltage of 390 V. Refer to Figure 20 for reference designators.

#### 8.2.2.1 Inductor Selection

In the transition mode control, the inductor value must be calculated to start the next switching cycle at zero current. The time it takes to reach zero depends on line voltage and inductance and as shown in Equation 2. L determines the frequency range of the converter.

$$L = \frac{\left(V_{AC(min)}\right)^{2} \times \left(V_{OUT} - \sqrt{2} \times V_{AC(min)}\right)}{2 \times F_{s(min)} \times V_{OUT} \times P_{IN}}$$

where

• V<sub>AC</sub> = RMS line voltage

2

• V<sub>AC(min)</sub> = minimum AC line voltage

| <ul> <li>P<sub>IN</sub> = maximum input power averaged over the ac line period</li> </ul> | (2) |

|-------------------------------------------------------------------------------------------|-----|

| $I_{L(peak)} = 2 \times \sqrt{2} \times (P_{IN}/V_{AC(min)})$                             | (3) |

| $I_{L(rms)} = I_{L(peak)} / \sqrt{6}$                                                     | (4) |

$$I_{L(rms)} = I_{L(peak)} / VO$$

# 8.2.2.2 MOSFET Selection

The main switch selection is driven by the amount of power dissipation allowable. Choose a device that minimizes gate charge and capacitance, and minimizes the sum of switching and conduction losses at a given frequency.

$$I_{Q(rms\_crm)} = \sqrt{\frac{1}{6} - (4 \times \sqrt{2}) \times (\frac{V_{AC(min)}}{9\pi \times V_{OUT}})} \times IL_{PEAK(crm)}$$

(5)

$$V_{Q(max)} = V_{OUT}$$

(6)

#### 8.2.2.3 Diode Selection

The effects of the reverse recovery current in the diode can be eliminated with relatively little negative impact to the system. The diode selection is based on reverse voltage, forward current, and switching speed.

$$I_{D(avg)} = I_{OUT(avg)}$$

(7)

$$I_{D(rms)} = I_{L(peak)} \sqrt{\frac{\sqrt{2} \times V_{AC}}{\pi \times V_{OUT}}}$$

(8)

$V_{D(peak)} = V_{OUT}$

### 8.2.2.4 Capacitor Selection

The hold-up time is the main requirement in determining the output capacitance. ESR and the maximum RMS ripple current rating can also be important, especially at higher power levels.

$C_{OUT(min)} = (2 \times P_{OUT} \times t_{HOLDUP}) / ((V_{OUT})^2 - (V_{OUT(min)})^2)$

where

$$I_{C(rms)} = \sqrt{\left(I_{L(peak)}\right)^{2} \times \frac{\sqrt{2} \times V_{AC(max)}}{\pi \times V_{OUT}} - \left(\frac{P_{OUT}}{V_{OUT}}\right)^{2} + (ac rms load currents)^{2}}$$

(11)

(9)

#### 8.2.2.5 Multiplier Set-Up

Select  $R_{AC1}$  and  $R_{AC2}$  so that their ratio uses the full dynamic range of the multiplier input at the peak line voltage, and yet with values small enough to negate the effects of the multiplier bias current. To use the maximum range of the multiplier, select the divider ratio so that  $V_{MULTIN}$ , evaluated at the peak of the maximum ac line voltage, is the maximum of the minimum dynamic input range of MULTIN, which is 2.5 V. Choose  $R_{AC1}$  so that it has at least 100 µA at the peak of the minimum AC operating line voltage.

$$\frac{R_{AC1}}{R_{AC2}} = \left(\frac{\sqrt{2}}{2.5} V_{AC(max)}\right) - 1$$

(12)

In extreme cases, switching transients can contaminate the MULTIN signal, so it can be beneficial to add capacitor  $C_{AC1}$ . Select the value of  $C_{AC1}$  so that the corner frequency of the resulting filter is greater than the lowest switching frequency. The low corner frequency of this filter may compromise the overall power factor.

### 8.2.2.6 Sense Resistor Selection

The current sense resistor value must be chosen to limit the output power, and it must also use the full dynamic range of the multiplier during normal steady state operation. The value of  $R_{S1}$  is thus selected for maximum power operation at low ac line voltage conditions. To use the full dynamic range, set the  $V_{SENSE}$  threshold as a function of the dynamic input range of  $V_{COMP}$  and the peak of the minimum MULTIN voltage.

$$R_{S1} = \frac{0.67 \times (COMP_{(MAX)} - COMP_{(MIN)}) \times (MULTIN_{(PEAK)@VAC(min)} - 0.075)}{2 \times \sqrt{2} \times \frac{P_{IN(max)}}{V_{AC(min)}}}$$

where

- COMP<sub>(MAX)</sub> = 3.8 V

- COMP<sub>(MIN)</sub> = 2.5 V

- $MULTIN_{(PEAK)@VAC(min)} = \sqrt{2} \times V_{AC(min)}(R_{AC2} / (R_{AC2} + R_{AC1}))$ (13)

If the exact value  $R_{S1}$  is not available,  $R_{S2}$  and  $R_{S3}$  can be added for further scaling. The CS pin already has an internal filter for noise due to switching transients. Additional filtering at switching transient frequencies can be achieved by adding CS1.

### 8.2.2.7 Output Voltage Sense Design

Select the divider ratio of  $R_{O1}$  and  $R_{O2}$  to set the VO\_SNS voltage to 2.5 V at the desired output voltage. The current through the divider should be at least 200  $\mu$ A.

### 8.2.2.8 Voltage Loop Design

How well the voltage control loop is designed directly impacts line current distortion. UCC38050 employs a transconductance amplifier ( $g_M$  amp) with gain scheduling for improved transient response (refer to Figure 9). Integral type control at low frequencies is preferred, because the loop gain varies considerably with line conditions. The largest gain occurs at maximum line voltage. If the power factor corrector load is dc-to-dc switching converter, the small signal model of the controller and the power factor corrector, from COMP to PFC output voltage is given by:

$$\frac{\hat{V}_{OUT}(s)}{\hat{V}_{COMP}(s)} = \frac{k_1 \times (V_{AC})^2}{V_{OUT(avg)} \times R_{S1} \times k_{CRM} \times C_{OUT}} \times \frac{1}{S}$$

where

- $V_{OUT}$  = small signal variations in  $V_{OUT}$

- $V_{COMP}$  = small signal variations in  $V_{COMP}$

- $k_1$  = multiplier gain = 0.65

- k<sub>CRM</sub> = peak to average factor = 2

(14)

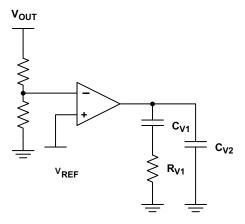

A controller that has integral control at low frequencies requires a zero near the crossover frequency to be stable. The resulting gM amplifier configuration is shown in Figure 21.

Figure 21. gM Amplifier Configuration

The compensator transfer function is:

$$A_{V} = \frac{gM}{C_{V1} + C_{V2}} \times \frac{1 + (R_{V1} \times C_{V1} \times s)}{s \left(1 + \left(R_{V1} \times \frac{\left[C_{V1} \times C_{V2}\right]}{\left[C_{V1} \times C_{V2}\right]}\right) \times s\right)}$$

where

The limiting factor of the gain is usually the allowable third harmonic distortion, although other harmonics can dominate. The crossover frequency of the control loop will be much lower than twice the AC line voltage. To choose the compensator dynamics, determine the maximum allowable loop gain at twice the line frequency, and solve for capacitor  $C_{V2}$ . This also determines the crossover frequency.

$$C_{V2} = \left(\frac{V_{AC(max)}}{4\pi f_{AC}}\right) 2 \times \left(\frac{gM \times k_{1}}{V_{OUT(avg)} \times R_{S1} \times k_{(crm)} \times C_{OUT(max loop gain at 2f_{AC})}}\right)$$

(16)

$$f_{CO} = \frac{V_{AC}}{\pi} \sqrt{\frac{gM \times k_{1}}{C_{V2} \times V_{OUT} \times R_{S1} \times k_{(crm)} \times C_{OUT}}}$$

(17)

Select  $C_{V1}$  so that the low frequency zero is one-tenth of the crossover frequency.

$$C_{V1} = 9 C_{V2}$$

(18)

Select  $R_{V1}$  so that the pole is at the crossover frequency.

/

(15)

(19)

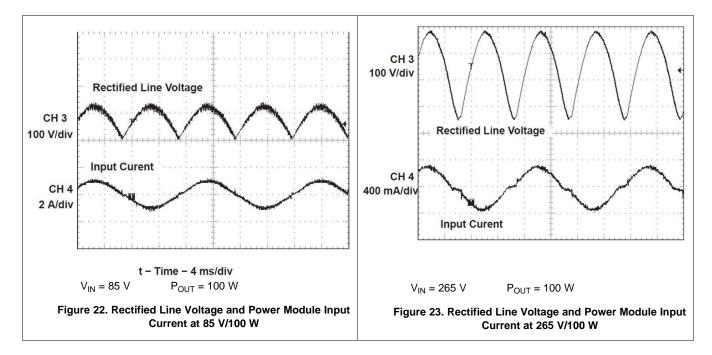

## 8.2.3 Application Curves

Figure 22 and Figure 23 show the input current and rectified line for the power module.

- Channel 3 = Rectified Line Voltage

- Channel 4 = Power Module Input Current

# 9 Power Supply Recommendations

The supply voltage for the device comes from VCC pin. This pin must be bypassed with a high-frequency capacitor (greater than 0.1  $\mu$ F) and tied to GND. The UCC38050 has a wide UVLO hysteresis of approximately 6.3 V that allows use of a lower value supply capacitor on this pin for quicker and easier start-up. The UCC38051 has a narrow UVLO hysteresis with of about 2.8 V, and a start-up voltage of about 12.5 V for applications where the operation of the PFC device must be controlled by a downstream PWM controller.

# 10 Layout

# 10.1 Layout Guidelines

### 10.1.1 Bias Current

The bias voltage is supplied by a bias winding on the inductor. Select the turns ratio so that sufficient bias voltage can be achieved at low AC line voltage. The bias capacitor must be large enough to maintain sufficient voltage with AC line variations. Connect a 0.1- $\mu$ F bypass capacitor between the VCC pin and the GND pin as close to the integrated circuit as possible. For wide line variations, a resistor, R<sub>B</sub>, is necessary to permit clamping action. The bias voltage should also be clamped with an external zener diode to a maximum of 18 V.

## 10.1.2 Zero Current Detection

The zero current detection activates when the ZCD voltage falls below 1.4 V. The bias winding can provide the necessary voltage. This pin has a clamp at approximately 5 V. Add a current limiting resistor,  $R_{ZC}$ , to keep the maximum current below 1 mA.

# 10.2 Layout Example

Figure 24. UCC38050 Layout Example

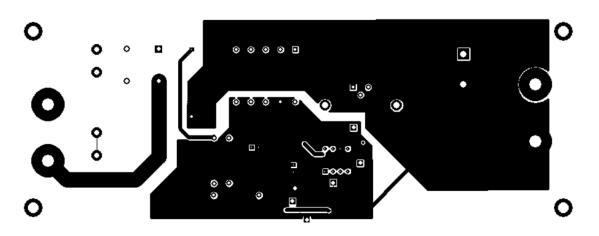

Figure 25. UCC38050 Bottom-Layer Layout Example

# **11** Device and Documentation Support

# **11.1 Device Support**

## 11.1.1 Development Support

Reference Design, 100-W Universal Line Input PFC Boost Converter Using the UCC38050 (SLUU134)

# 11.2 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

| PARTS    | PRODUCT FOLDER | SAMPLE & BUY | TECHNICAL<br>DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT &<br>COMMUNITY |  |  |  |  |  |

|----------|----------------|--------------|------------------------|---------------------|------------------------|--|--|--|--|--|

| UCC28050 | Click here     | Click here   | Click here             | Click here          | Click here             |  |  |  |  |  |

| UCC28051 | Click here     | Click here   | Click here             | Click here          | Click here             |  |  |  |  |  |

| UCC38050 | Click here     | Click here   | Click here             | Click here          | Click here             |  |  |  |  |  |

| UCC38051 | Click here     | Click here   | Click here             | Click here          | Click here             |  |  |  |  |  |

### Table 2. Related Links

# **11.3 Community Resources**

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

# 11.4 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

### 11.5 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

# PACKAGING INFORMATION

| Orderable Device | Status  | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|------------------|---------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------|---------|

|                  | (1)     |              | Drawing            |      | QLY            | (2)          | (6)                           | (3)                |              | (4/5)          |         |

| UCC28050D        | LIFEBUY | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 105   | 28050          |         |

| UCC28050DR       | LIFEBUY | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 105   | 28050          |         |

| UCC28050P        | LIFEBUY | PDIP         | Р                  | 8    | 50             | RoHS & Green | NIPDAU                        | N / A for Pkg Type | -40 to 105   | 28050          |         |

| UCC28051D        | ACTIVE  | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 105   | 28051          | Samples |

| UCC28051DG4      | ACTIVE  | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 105   | 28051          | Samples |

| UCC28051DR       | ACTIVE  | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 105   | 28051          | Samples |

| UCC28051DRG4     | ACTIVE  | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 105   | 28051          | Samples |

| UCC28051P        | LIFEBUY | PDIP         | Р                  | 8    | 50             | RoHS & Green | NIPDAU                        | N / A for Pkg Type | -40 to 105   | 28051          |         |

| UCC38050D        | LIFEBUY | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | 0 to 70      | 38050          |         |

| UCC38050DR       | LIFEBUY | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | 0 to 70      | 38050          |         |

| UCC38050P        | LIFEBUY | PDIP         | Р                  | 8    | 50             | RoHS & Green | NIPDAU                        | N / A for Pkg Type | 0 to 70      | 38050          |         |

| UCC38051D        | LIFEBUY | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | 0 to 70      | 38051          |         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

# PACKAGE OPTION ADDENDUM

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

STRUMENTS

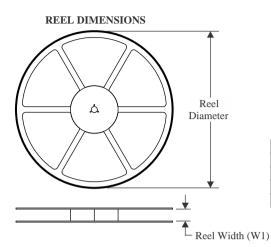

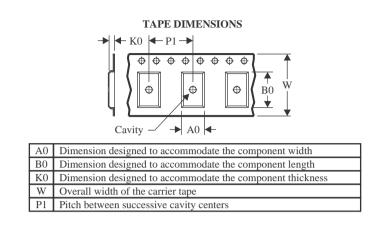

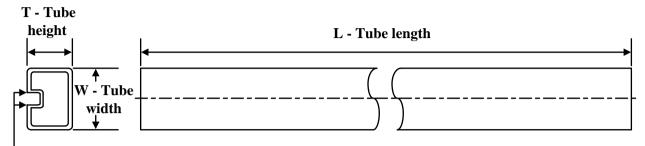

# TAPE AND REEL INFORMATION

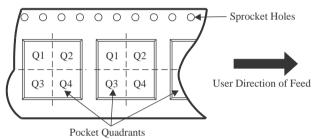

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| UCC28050DR                  | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| UCC28051DR                  | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| UCC38050DR                  | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

Pack Materials-Page 1

# PACKAGE MATERIALS INFORMATION

31-Oct-2023

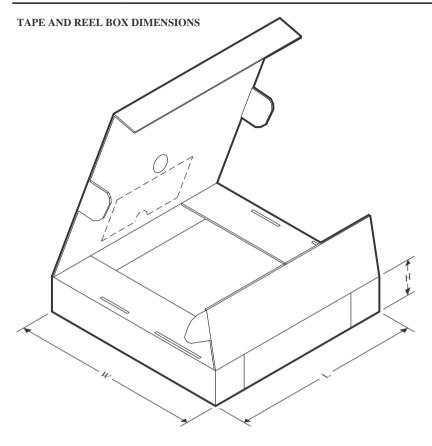

\*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UCC28050DR | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

| UCC28051DR | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

| UCC38050DR | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

Pack Materials-Page 2

# TEXAS INSTRUMENTS

www.ti.com

31-Oct-2023

# TUBE

# - B - Alignment groove width

## \*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| UCC28050D   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| UCC28050P   | Р            | PDIP         | 8    | 50  | 506    | 13.97  | 11230  | 4.32   |

| UCC28051D   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| UCC28051DG4 | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| UCC28051P   | Р            | PDIP         | 8    | 50  | 506    | 13.97  | 11230  | 4.32   |

| UCC38050D   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| UCC38050P   | Р            | PDIP         | 8    | 50  | 506    | 13.97  | 11230  | 4.32   |

| UCC38051D   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

Pack Materials-Page 3

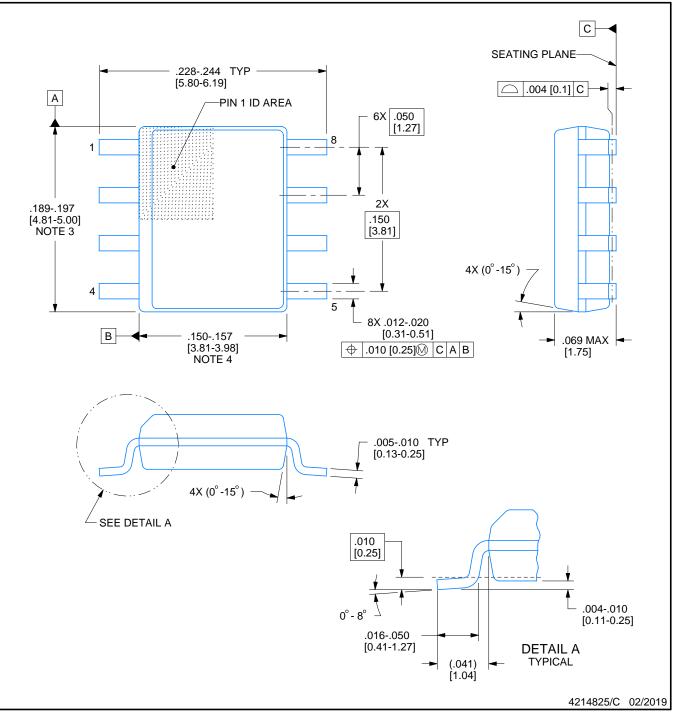

# D0008A

# **PACKAGE OUTLINE**

# SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

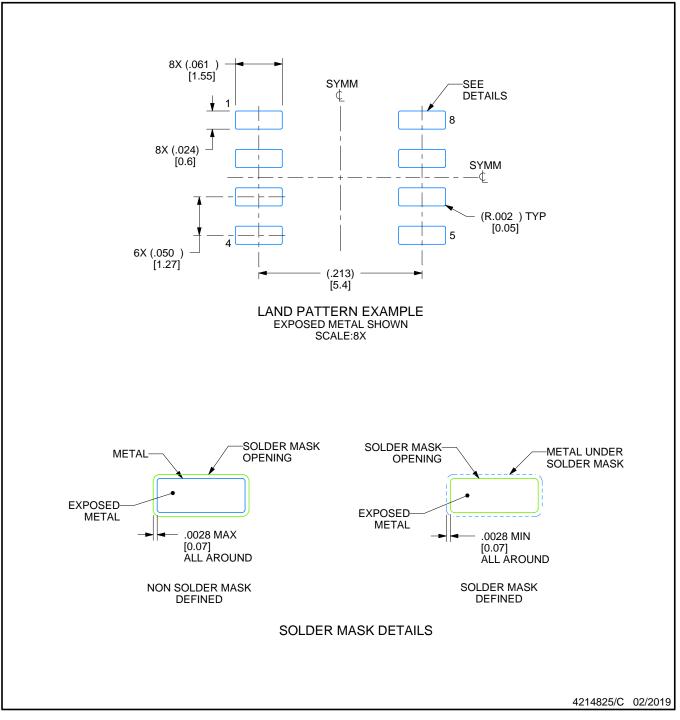

# D0008A

# **EXAMPLE BOARD LAYOUT**

# SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

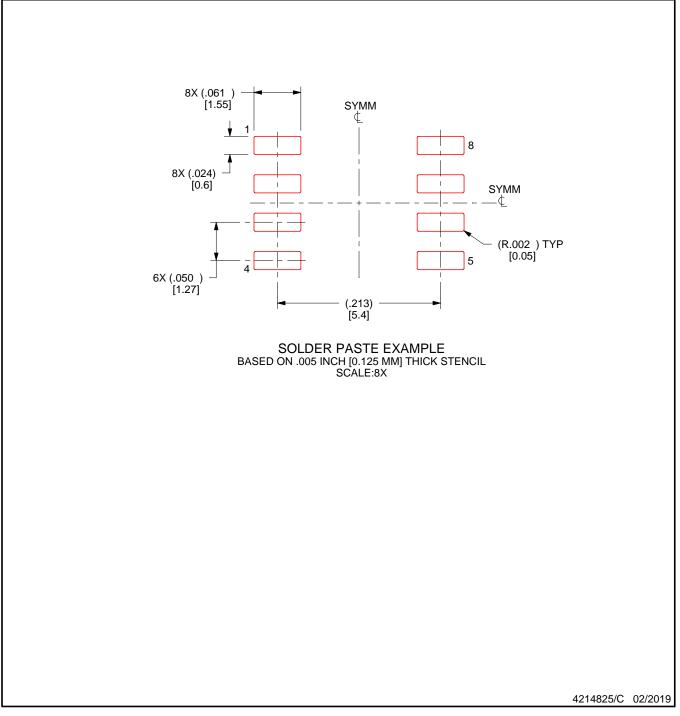

# D0008A

# **EXAMPLE STENCIL DESIGN**

# SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

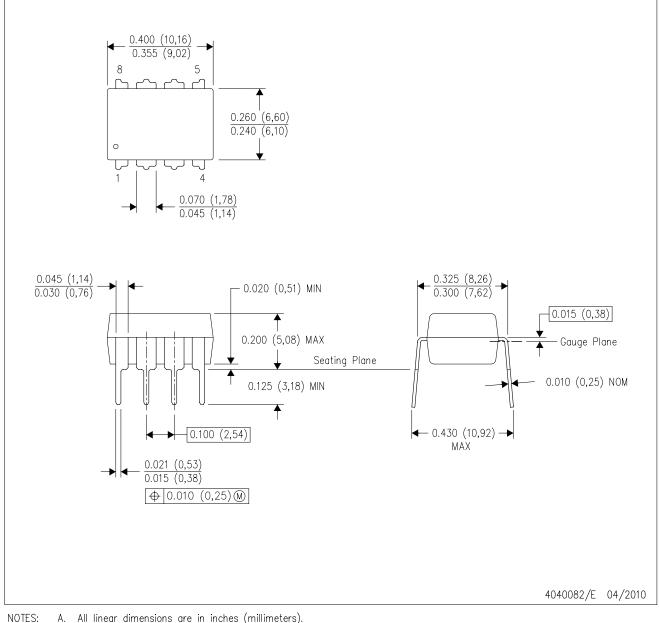

P (R-PDIP-T8)

PLASTIC DUAL-IN-LINE PACKAGE

- A. All linear dimensions are in inches (millimeters).B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001 variation BA.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated 单击下面可查看定价,库存,交付和生命周期等信息

>>TI(德州仪器)