ETR02032-002

Delay capacitor adjustable voltage detectors with sense pin isolation, surge voltage protection and HYS external adjustment

### ■GENERAL DESCRIPTION

The XC6132 series are ultra-small delay capacitor adjustable type voltage detectors that have high accuracy and sense pin isolation. High accuracy and a low supply current are achieved by means of a CMOS process, a highly accurate reference power supply, and laser trimming technology.

The sense pin is isolated from the power input pin to enable monitoring of the voltage of another power supply. Output can be maintained in the detection state even if the voltage of the power supply that is monitored drops to 0V. The sense pin is also suitable for detecting high voltages, and the detection and release voltage can be set as desired using external resistors. An internal surge voltage protection circuit and an internal delay circuit are also provided.

By connecting a capacitor to the Cd/MRB pin, any release delay time and detect delay time can be set and the pin can also be used as a manual reset pin.

The HYS external adjustment pin can be used to establish a sufficient hysteresis width.

### APPLICATIONS

Microcontroller reset and malfunction monitoring

Battery voltage monitoring

System power-on reset

Power failure detection

### ■FEATURES

| Operating Ambient Temperature       | : -40°C~+125°C                                  |

|-------------------------------------|-------------------------------------------------|

| Operating voltage range             | : 1.6V~6.0V                                     |

| Detect voltage range                | : 0.8V~2.0V                                     |

| Detect voltage accuracy             | : ±18mV(V <sub>DF</sub> <1.5V)                  |

| (Ta=25°C)                           | : ±1.2%(1.5V≦V <sub>DF</sub> ≦2.0V)             |

| Detect voltage accuracy             | : ±36mV(V <sub>DF</sub> <1.5V)                  |

| (Ta=-40∼125°C)                      | : ±2.7%(1.5V≦V <sub>DF</sub> ≦2.0V)             |

| Temperature Characteristics         | : ±50ppm/°C(TYP.)                               |

| Hysteresis width                    | : V <sub>DF</sub> ×0.1%(TYP.)                   |

| Adjustable Pin for Hysteresis Width | : Yes                                           |

| Low supply current                  | : 1.28µA(TYP.)                                  |

|                                     | V <sub>IN</sub> =1.6V(At detection)             |

|                                     | : 1.65µA(TYP.)                                  |

|                                     | V <sub>IN</sub> =6.0V(At release)               |

| Manual reset function               | : Yes (For details, refer to<br>FUNCTION CHART) |

| Output type                         | : CMOS or Nch open drain                        |

| Output logic                        | : H level or L level at detection               |

|                                     | : Release delay / detection delay               |

| Delay capacitance pin               | can be set in 5 time ratio options              |

|                                     | (For details, refer to Selection Guide).        |

| Sense pin                           | : Includes a surge voltage protection           |

|                                     | function                                        |

| Packages                            | : USP-6C,SOT-26                                 |

| Environment friendly                | : EU RoHS compliant, Pb free                    |

|                                     |                                                 |

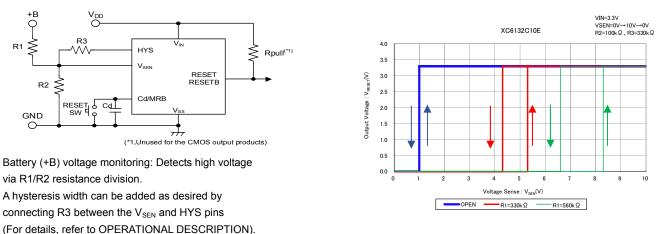

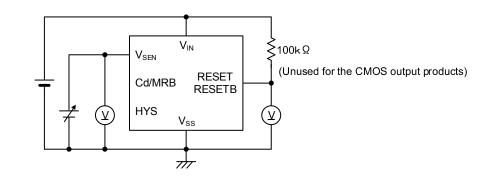

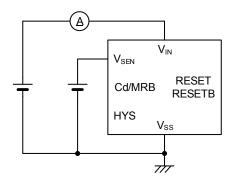

### ■ TYPICAL APPLICATION CIRCUIT ■ TYPICAL PERFORMANCE CHARACTERISTICS

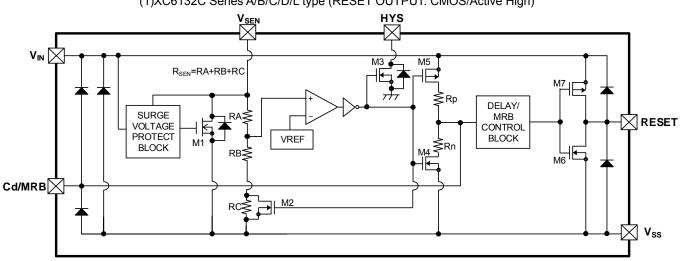

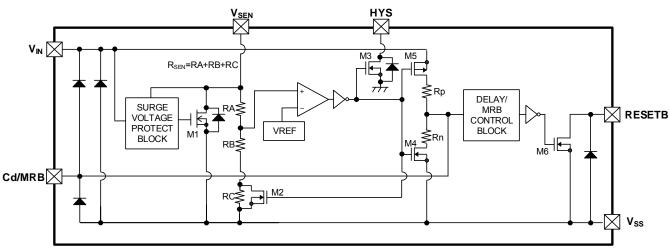

### ■BLOCK DIAGRAMS

(1)XC6132C Series A/B/C/D/L type (RESET OUTPUT: CMOS/Active High)

\* Diodes inside the circuit are an ESD protection diode and a parasitic diode.

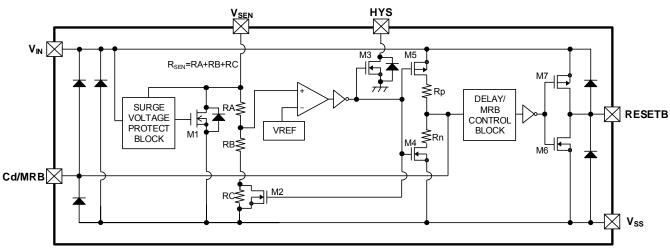

(2)XC6132C Series E/F/H/K/M type (RESETB OUTPUT: CMOS/Active Low)

\* Diodes inside the circuit are an ESD protection diode and a parasitic diode.

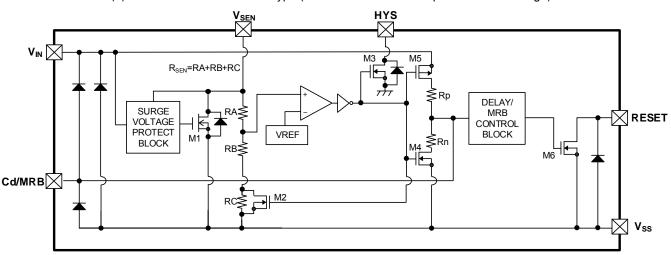

### ■BLOCK DIAGRAMS (Continued)

(3)XC6132N Series A/B/C/D/L type (RESET OUTPUT: Nch open drain/Active High)

\* Diodes inside the circuit are an ESD protection diode and a parasitic diode.

(4)XC6132N Series E/F/H/K/M type (RESETB OUTPUT: Nch open drain/Active Low)

\* Diodes inside the circuit are an ESD protection diode and a parasitic diode.

### ■ PRODUCT CLASSIFICATION

#### Ordering Information

XC6132123456-7(\*1)

| DESIGNATOR  | ITEM                   | SYMBOL | DESCRIPTION              |

|-------------|------------------------|--------|--------------------------|

|             | Output Configuration   | С      | CMOS output              |

| 1           | Output Configuration   | N      | Nch open drain output    |

| 23          | Detect Voltage         | 08~20  | e.g. 1.0V → ②=1, ③=0     |

| 4           | TYPE                   | A~M    | Refer to Selection Guide |

| (5)6-7)(*1) | Dookogoo (Ordor Linit) | MR-G   | SOT-26 (3,000pcs/Reel)   |

| 30-0, "     | Packages (Order Unit)  | ER-G   | USP-6C (3,000pcs/Reel)   |

<sup>(\*1)</sup> The "-G" suffix denotes Halogen and Antimony free as well as being fully EU RoHS compliant.

#### Selection Guide

| TYPE | RESET/RESETB OUTPUT         | DEL     | AY(Rp:Rn)                  | HYSTERESIS |

|------|-----------------------------|---------|----------------------------|------------|

| А    | Active High <sup>(*2)</sup> | 1:0     | 144kΩ:0Ω                   | 0.1%(TYP)  |

| В    | ↑                           | 1:0.125 | 144kΩ : 18kΩ               | 1          |

| С    | 1                           | 1:1     | 144kΩ:144kΩ                | ↑          |

| D    | ↑                           | 2:1     | 288kΩ:144kΩ                | ↑ (        |

| L    | 1                           | 0.076:1 | 11kΩ:144kΩ                 | ↑ (        |

| E    | Active Low <sup>(*2)</sup>  | 1:0     | 144kΩ:0Ω                   | ↑ (        |

| F    | ↑                           | 1:0.125 | 144kΩ : 18kΩ               | ↑ (        |

| Н    | 1                           | 1:1     | 144kΩ:144kΩ                | ↑ (        |

| к    | ↑                           | 2:1     | 288kΩ:144kΩ                | ↑ (        |

| М    | 1                           | 0.076:1 | $11k\Omega$ : $144k\Omega$ | 1          |

(\*2) "Active High" is H level when detection occurs, and "Active Low" is L level when detection occurs.

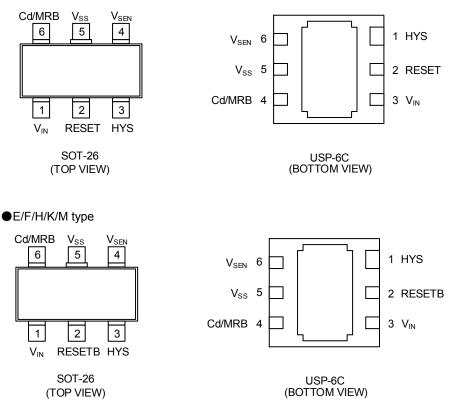

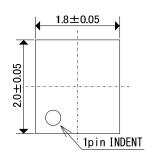

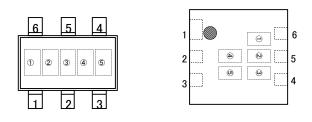

### ■ PIN CONFIGURATION

#### ●A/B/C/D/L type

\*The dissipation pad for the USP-6C package should be solder-plated in reference mount pattern and metal masking so as to enhance mounting strength and heat release. If the pad needs to be connected to other pins, it should be connected to  $V_{SS}$  (No. 5) pin.

### ■ PIN ASSIGNMENT

| PIN NUMBER |        | PIN NAME         | FUNCTION                                       |  |  |  |  |

|------------|--------|------------------|------------------------------------------------|--|--|--|--|

| SOT-26     | USP-6C |                  | FUNCTION                                       |  |  |  |  |

| 1          | 3      | VIN              | Power Input                                    |  |  |  |  |

| 2          | 2      | RESETB           | Reset Output (Active Low) <sup>(*1)</sup>      |  |  |  |  |

| 2          | 2      | RESET            | Reset Output (Active High)(*1)                 |  |  |  |  |

| 3          | 1      | HYS              | Adjustable Pin for Hysteresis Width            |  |  |  |  |

| 4          | 6      | V <sub>SEN</sub> | Voltage Sense                                  |  |  |  |  |

| 5          | 5      | Vss              | Ground                                         |  |  |  |  |

| 6          | 4      | Cd/MRB           | Adjustable Pin for Delay Time/<br>Manual Reset |  |  |  |  |

$^{(^{\star}1)}$  Refer to the 4 in Ordering Information table.

### ■FUNCTION CHART

| PIN SIGNAL STATUS |      |                                          |  |  |  |  |  |  |

|-------------------|------|------------------------------------------|--|--|--|--|--|--|

|                   | L    | Forced Reset                             |  |  |  |  |  |  |

| Cd/MRB            | Н    | For details, refer to " Function Chart " |  |  |  |  |  |  |

|                   | OPEN | Normal Operation                         |  |  |  |  |  |  |

#### Function Chart

1.6V≦V<sub>IN</sub>≦6.0V

| Marin                                               | V                                     | Transition of VRESETB Condition     | Transition of VRESET Condition       |  |

|-----------------------------------------------------|---------------------------------------|-------------------------------------|--------------------------------------|--|

| Vsen                                                | VCd/MRB                               | TYPE:A/B/C/D/L                      | TYPE:E/F/H/K/M                       |  |

|                                                     | V <sub>Cd/MRB</sub> ≦V <sub>MRL</sub> | Reset (High Level) <sup>(*2)</sup>  | Reset (Low Level)(*1)                |  |

| V <sub>SEN</sub> ≧V <sub>DF</sub> +V <sub>HYS</sub> | V <sub>Cd/MRB</sub> ≧V <sub>MRH</sub> | Release (Low Level) <sup>(*1)</sup> | Release (High Level) <sup>(*2)</sup> |  |

| VSEN≦VDF                                            | V <sub>Cd/MRB</sub> ≦V <sub>MRL</sub> | Reset (High Level) <sup>(*2)</sup>  | Reset (Low Level)(*1)                |  |

| V SEN ≧ V DF                                        | V <sub>Cd/MRB</sub> ≧V <sub>MRH</sub> | Undefined <sup>(*3)</sup>           | Undefined <sup>(*3)</sup>            |  |

$^{(^{\star}1)}$  CMOS output:  $V_{IN}\times 0.1$  or less, N-ch open drain output, pull-up voltage  $\times$  0.1 or less.

$^{(*2)}$  CMOS output:  $V_{IN}$  × 0.9 or higher, N-ch open drain output, pull-up voltage × 0.9 or higher.

$^{(*3)}$  For details, refer to page 17 < Manual reset function >.

Note: If used with  $V_{IN} < V_{SEN}$ , the surge protection circuit will activate. Use with  $V_{IN} \ge V_{SEN}$ .

### ■ABSOLUTE MAXIMUM RATINGS

|                            |                         |                      |                    |                                                    | Ta=25°C |

|----------------------------|-------------------------|----------------------|--------------------|----------------------------------------------------|---------|

| PARAME                     | TER                     | SYM                  | BOL                | RATINGS                                            | UNITS   |

| Input Voltage              |                         | V <sub>IN</sub>      |                    | -0.3~+7.0                                          | V       |

| V <sub>SEN</sub> Pin V     | oltage                  | Vs                   | EN                 | -0.3~+V <sub>IN</sub> +0.3 or +7.0 <sup>(*1)</sup> | V       |

| HYS Pin Ve                 | oltage                  | VH                   | IYS                | -0.3~+7.0                                          | V       |

| Cd/MRB Pin                 | Voltage                 | Vcd                  | /MRB               | -0.3~+V <sub>IN</sub> +0.3 or +7.0 <sup>(*1)</sup> | V       |

|                            | XC6132C <sup>(*2)</sup> | V                    | V                  | -0.3~+V <sub>IN</sub> +0.3 or +7.0 <sup>(*1)</sup> | V       |

| Output Voltage             | XC6132N <sup>(*3)</sup> | V <sub>RESETB</sub>  | V <sub>RESET</sub> | -0.3~+7.0                                          | V       |

| Cd/MRB Pin                 | Current                 | ICd/                 | MRB                | ±5.0                                               | mA      |

| Output Current             | XC6132C <sup>(*2)</sup> |                      |                    | ±50                                                | mA      |

| Output Current             | XC6132N <sup>(*3)</sup> | - I <sub>RBOUT</sub> | IROUT              | +50                                                | mA      |

| HYS Pin C                  | urrent                  | IHYS                 |                    | +50                                                | mA      |

| V <sub>SEN</sub> Pin Surge | Current(+)              | ISENSU               | IRGE(+)            | +2.5(*4)                                           | mA      |

| V <sub>SEN</sub> Pin Surge | Current(-)              | I <sub>SENSU</sub>   | JRGE(-)            | -2.5(*5)                                           | mA      |

| VSEN Pin Surge             | Voltage(+)              | VSENS                | JRGE(+)            | +7.0 <sup>(*4)</sup>                               | V       |

| VSEN Pin Surge             | Voltage(-)              | VSENS                | URGE(-)            | -0.9 (*5)                                          | V       |

|                            | SOT-26                  |                      |                    | 250                                                |         |

| Power Dissipation          | 301-20                  | - P                  | d                  | 600 (40mm x 40mm Standard board) (*6)              | mW      |

| Fower Dissipation          |                         |                      | u                  | 100                                                |         |

|                            | USP-6C                  |                      |                    | 1250 (JEDEC board) (*6)                            | -       |

| Operating Ambient          | Temperature             | Тс                   | pr                 | -40~+125                                           | °C      |

| Storage Tem                | perature                | Ts                   | stg                | -55~+125                                           | °C      |

$^{\ast}$  All voltages are described based on the V $_{\text{SS}}$

$^{(^{\star}1)}$  The maximum value should be either  $V_{IN}\text{+}0.3$  or +7.0 in the lowest.

(\*2) CMOS Output

(\*3) N-ch Open Drain Output

$^{(*4)}$  Transient  $\leq$  200ms.

$^{(*5)}$  Transient  $\leq$  20ms.

(\*6) This is a reference data taken by using the test board. Please see the power dissipation page for the mounting condition.

### ■ ELECTRICAL CHARACTERISTICS

|                                                   |                                                | CONDITIONO                                                                 |                              | Ta=25°C                   | ;                            | -40°C≦                       | ≦Ta≦1                     | 25°C <sup>(*7)</sup>         |        |         |

|---------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------|------------------------------|---------------------------|------------------------------|------------------------------|---------------------------|------------------------------|--------|---------|

| PARAMETER                                         | SYMBOL                                         | CONDITIONS                                                                 | MIN.                         | TYP.                      | MAX.                         | MIN.                         | TYP.                      | MAX.                         | UNITS  | CIRCUIT |

| Operating Voltage                                 | V <sub>IN</sub>                                |                                                                            | 1.6                          |                           | 6.0                          | 1.6                          |                           | 6.0                          | V      |         |

| V <sub>SEN</sub> Input Voltage                    | $V_{\text{SEN}}$                               |                                                                            | 0                            |                           | 6.0                          | 0                            |                           | 6.0                          | V      |         |

| Datast Valtage                                    | V <sub>DF</sub>                                | $V_{DF(T)}^{(*1)}=0.8V\sim1.4V$                                            | V <sub>DF(T)</sub><br>-18mV  | V <sub>DF(T)</sub>        | V <sub>DF(T)</sub><br>+18mV  | V <sub>DF(T)</sub><br>-36mV  | V <sub>DF(T)</sub>        | V <sub>DF(T)</sub><br>+36mV  | V      | 1       |

| Detect Voltage                                    | V DF                                           | $V_{DF(T)}^{(*1)}=1.5V\sim2.0V$                                            | V <sub>DF(T)</sub><br>×0.988 | V <sub>DF(T)</sub>        | V <sub>DF(T)</sub><br>×1.012 | V <sub>DF(T)</sub><br>×0.973 | V <sub>DF(T)</sub>        | V <sub>DF(T)</sub><br>×1.027 | V      |         |

| Temperature<br>Characteristics                    | ΔV <sub>DF</sub> /<br>(ΔTopr∙V <sub>DF</sub> ) | -40°C≦Topr≦125°C                                                           | -                            | ±50                       | -                            | -                            | ±50                       | -                            | ppm/°C |         |

| Hysteresis Width                                  | V <sub>HYS</sub>                               |                                                                            | -                            | V <sub>DF</sub><br>×0.001 | V <sub>DF</sub><br>×0.007    | -                            | V <sub>DF</sub><br>×0.001 | V <sub>DF</sub><br>×0.01     | V      |         |

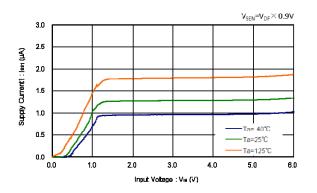

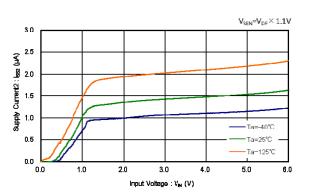

| Supply Current 1                                  | I <sub>ss1</sub>                               | $V_{SEN} = V_{DF} \times 0.9V,$<br>$V_{IN} : \text{ Refer to } V-1^{(*2)}$ | -                            | E-′                       | <b> </b> (*3)                | -                            | E-2                       | 2 <sup>(*3)</sup>            |        |         |

| Supply Surrent 1                                  | ISS1                                           | V <sub>SEN</sub> =V <sub>DF</sub> ×0.9V,<br>V <sub>IN</sub> =6.0V          | -                            | 1.36                      | 2.80                         | -                            | 1.36                      | 4.22                         | μA     | 2       |

| Supply Current 2                                  |                                                | $V_{SEN}$ = $V_{DF}$ ×1.1V,<br>$V_{IN}$ : Refer to V-1 <sup>(*2)</sup>     | -                            | E-3                       | <b>3</b> (*3)                | -                            | E-4 <sup>(*3)</sup>       |                              | μΛ     | Ľ       |

| Supply Current 2                                  | I <sub>ss2</sub>                               | V <sub>SEN</sub> =V <sub>DF</sub> ×1.1V,<br>V <sub>IN</sub> =6.0V          | -                            | 1.65                      | 3.25                         | -                            | 1.65                      | 4.97                         |        |         |

| SENSE Resistance                                  | R <sub>SEN</sub>                               | V <sub>IN</sub> =6.0V,V <sub>SEN</sub> =6.0V                               | E-{                          | 5 <sup>(*4)</sup>         | -                            | E-6                          | ð <sup>(*4)</sup>         | -                            | MΩ     | 3       |

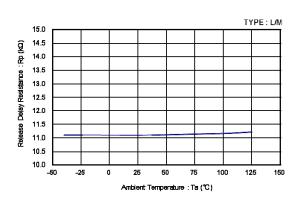

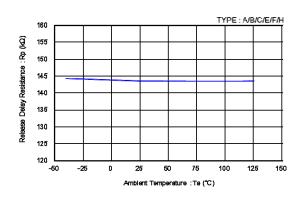

| Release Delay<br>Resistance<br>(TYPE:A/B/C/E/F/H) |                                                | V <sub>IN</sub> =6.0V,V <sub>SEN</sub> =6.0V,<br>V <sub>Cd/MRB</sub> =0V   | 130                          | 144                       | 158                          | 122                          | 144                       | 166                          |        |         |

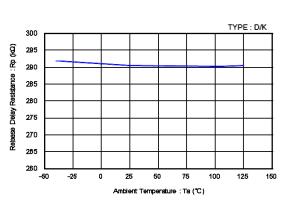

| Release Delay<br>Resistance<br>(TYPE:D/K)         | Rp                                             | V <sub>IN</sub> =6.0V,V <sub>SEN</sub> =6.0V,<br>V <sub>Cd/MRB</sub> =0V   | 259                          | 288                       | 317                          | 245                          | 288                       | 331                          |        |         |

| Release Delay<br>Resistance<br>(TYPE:L/M)         |                                                | $V_{IN}$ =6.0V, $V_{SEN}$ =6.0V,<br>$V_{Cd/MRB}$ =0V                       | 8.3                          | 11                        | 18.4                         | 7.6                          | 11                        | 20.0                         | kΩ     | 4       |

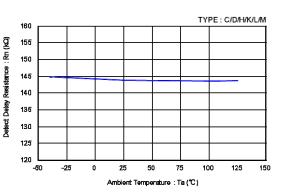

| Detect Delay<br>Resistance<br>(TYPE:C/D/H/K/L/M)  | Rn                                             | V <sub>IN</sub> =6.0V,V <sub>SEN</sub> =0V,<br>V <sub>Cd/MRB</sub> =6.0V   | 130                          | 144                       | 158                          | 122                          | 144                       | 166                          |        |         |

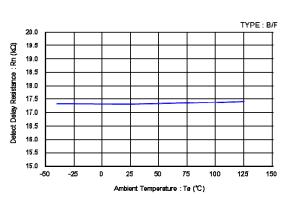

| Detect Delay<br>Resistance<br>(TYPE:B/F)          |                                                | V <sub>IN</sub> =6.0V,V <sub>SEN</sub> =0V,<br>V <sub>Cd/MRB</sub> =6.0V   | 16.8                         | 18                        | 19.1                         | 16.2                         | 18                        | 19.8                         |        |         |

| Release Delay<br>Time <sup>(*5)</sup>             | t <sub>DR0</sub>                               | $V_{IN}$ =6.0V,<br>$V_{SEN}$ = $V_{DF}$ ×0.9V $\rightarrow$ $V_{DF}$ ×1.1V | -                            | 20                        | 102                          | -                            | 20                        | 136                          |        | Ē       |

| Detect Delay<br>Time <sup>(*6)</sup>              | t <sub>DF0</sub>                               | $V_{IN}$ =6.0V,<br>$V_{SEN}$ = $V_{DF}$ ×1.1V $\rightarrow$ $V_{DF}$ ×0.9V | -                            | 20                        | 82                           | -                            | 20                        | 116                          | μs     | 5       |

Unless otherwise specified in measurement conditions, Cd/MRB pin and HYS pin are open.

(\*1) V<sub>DF(T)</sub>: Nominal detect voltage

<sup>(\*2)</sup> For V<sub>IN</sub> conditions, refer to SPEC TABLE (p.10).

<sup>(\*3)</sup> Refer to SPEC TABLE (p.10). <sup>(\*4)</sup> Refer to SPEC TABLE (p.11).

(\*5) RESETB product: Time from when the V<sub>SEN</sub> pin voltage reaches the release voltage until the reset output pin reaches 5.4V (V<sub>IN</sub>×90%).

RESET product: Time from when the V<sub>SEN</sub> pin voltage reaches the release voltage until the reset output pin reaches 0.6V(V<sub>IN</sub>×10%) Release voltage (V<sub>DR</sub>)=Detect voltage (V<sub>DF</sub>)+Hysteresis width (V<sub>HYS</sub>).

(\*6) RESETB product: Time from when the V<sub>SEN</sub> pin voltage reaches the detect voltage until the reset output pin reaches 0.6V(V<sub>IN</sub>×10%). RESET product: Time from when the  $V_{SEN}$  pin voltage reaches the detect voltage until the reset output pin reaches 5.4V( $V_{IN}$ ×90%).

$^{(`7)}$  The ambient temperature range (-40°C  $\leq$  Ta  $\leq$  125°C) is a design Value.

### ■ ELECTRICAL CHARACTERISTICS (Continued)

|                                      |                                    |                                                                                                |      | Ta=25°C | >    | -40°C≦ | ≦Ta≦12 | 25°C <sup>(*12)</sup> |       |                          |  |

|--------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------|------|---------|------|--------|--------|-----------------------|-------|--------------------------|--|

| PARAMETER                            | SYMBOL                             | CONDITIONS                                                                                     | MIN. | TYP.    | MAX. | MIN.   | TYP.   | MAX.                  | UNITS | CIRCUIT                  |  |

| Hysteresis Output<br>Current         | I <sub>HYSOUT</sub>                | V <sub>IN</sub> =1.6V,<br>V <sub>SEN</sub> =0V,V <sub>HYS</sub> =0.3V                          | 1.9  | 3.4     | -    | 0.7    | 3.4    | -                     | mA    | 6                        |  |

| Hysteresis Output<br>Leakage Current | I <sub>HYSLEAK</sub>               | V <sub>IN</sub> =6.0V,V <sub>SEN</sub> =6.0V,<br>V <sub>HYS</sub> =6.0V                        | -    | 0.01    | 0.1  | -      | 0.01   | 1.0                   | μA    | <b>O</b>                 |  |

|                                      |                                    | V <sub>SEN</sub> =V <sub>DF</sub> ×0.9V,<br>Nch. V <sub>RESETB</sub> =0.3V                     |      |         |      |        |        |                       |       |                          |  |

|                                      |                                    | V <sub>IN</sub> =1.6V <sup>(*9)</sup>                                                          | 1.9  | 3.4     | -    | 0.7    | 3.4    | -                     |       |                          |  |

|                                      |                                    | V <sub>IN</sub> =2.0V                                                                          | 4.2  | 6.0     | -    | 2.0    | 6.0    | -                     |       |                          |  |

|                                      | IRBOUTN                            | V <sub>IN</sub> =3.0V                                                                          | 8.6  | 10.5    | -    | 4.3    | 10.5   | -                     |       |                          |  |

|                                      |                                    | V <sub>IN</sub> =4.0V                                                                          | 12.7 | 14.1    | -    | 6.2    | 14.1   | -                     |       |                          |  |

| RESETB                               |                                    | V <sub>IN</sub> =5.0V                                                                          | 15.6 | 17.0    | -    | 7.3    | 17.0   | -                     | mA    |                          |  |

| Output Current                       |                                    | V <sub>IN</sub> =6.0V                                                                          | 17.8 | 19.2    | -    | 8.1    | 19.2   | -                     |       |                          |  |

|                                      |                                    | V <sub>SEN</sub> =V <sub>DF</sub> ×1.1V,<br>Pch.<br>V <sub>RESETB</sub> =V <sub>IN</sub> -0.3V |      |         |      |        |        |                       |       |                          |  |

|                                      | IRBOUTP                            | V <sub>IN</sub> =1.6V <sup>(*10)</sup>                                                         | -    | -1.2    | -0.7 | -      | -1.2   | -0.48                 |       |                          |  |

|                                      |                                    | V <sub>IN</sub> =3.0V                                                                          | -    | -3.0    | -2.5 | -      | -3.0   | -1.1                  |       |                          |  |

|                                      |                                    | V <sub>IN</sub> =6.0V                                                                          | -    | -4.9    | -4.4 | -      | -4.9   | -2.5                  |       |                          |  |

|                                      |                                    | V <sub>SEN</sub> =V <sub>DF</sub> ×1.1V,<br>Nch. V <sub>RESET</sub> =0.3V                      |      |         |      |        |        |                       |       |                          |  |

|                                      |                                    | V <sub>IN</sub> =1.6V <sup>(*10)</sup>                                                         | 1.9  | 3.4     | -    | 0.7    | 3.4    | -                     | -     |                          |  |

|                                      |                                    | V <sub>IN</sub> =2.0V <sup>(*11)</sup>                                                         | 4.2  | 6.0     | -    | 2.0    | 6.0    | -                     |       | $\overline{\mathcal{O}}$ |  |

|                                      | I <sub>ROUTN</sub>                 | V <sub>IN</sub> =3.0V                                                                          | 8.6  | 10.5    | -    | 4.3    | 10.5   | -                     |       |                          |  |

|                                      |                                    | V <sub>IN</sub> =4.0V                                                                          | 12.7 | 14.1    | -    | 6.2    | 14.1   | -                     |       |                          |  |

| RESET<br>Output Current              |                                    | V <sub>IN</sub> =5.0V                                                                          | 15.6 | 17.0    | -    | 7.3    | 17.0   | -                     | mA    |                          |  |

| Output Current                       |                                    | V <sub>IN</sub> =6.0V                                                                          | 17.8 | 19.2    | -    | 8.1    | 19.2   | -                     |       |                          |  |

|                                      |                                    | V <sub>SEN</sub> =V <sub>DF</sub> ×0.9V,                                                       |      |         |      |        |        |                       |       |                          |  |

|                                      |                                    | Pch. V <sub>RESET</sub> =V <sub>IN</sub> -0.3V                                                 |      |         |      |        |        |                       |       |                          |  |

|                                      | I <sub>ROUTP</sub>                 | V <sub>IN</sub> =1.6V <sup>(*9)</sup>                                                          | -    | -1.2    | -0.7 | -      | -1.2   | -0.48                 |       |                          |  |

|                                      |                                    | V <sub>IN</sub> =3.0V                                                                          | -    | -3.0    | -2.5 | -      | -3.0   | -1.1                  |       |                          |  |

|                                      |                                    | V <sub>IN</sub> =6.0V                                                                          | -    | -4.9    | -4.4 | -      | -4.9   | -2.5                  |       |                          |  |

| RESETB Output                        | I <sub>leakn</sub> (*8)            | $V_{IN}$ =6.0V, $V_{SEN}$ =6.0V,<br>Nch. $V_{RESETB}$ =6.0V                                    | -    | 0.01    | 0.1  | -      | 0.01   | 1.0                   |       |                          |  |

| Leakage Current                      | I <sub>LEAKP</sub>                 | $V_{IN}$ =6.0V, $V_{SEN}$ =0V,<br>Pch. $V_{RESETB}$ =0V                                        | -    | -0.01   | -    | -      | -0.01  | -                     | μA    |                          |  |

| RESET Output                         | I <sub>LEAKN</sub> <sup>(*8)</sup> | V <sub>IN</sub> =6.0V,V <sub>SEN</sub> =0V,<br>Nch. V <sub>RESET</sub> =6.0V                   | -    | 0.01    | 0.1  | -      | 0.01   | 1.0                   | μ. ι  |                          |  |

| Leakage Current                      | I <sub>LEAKP</sub>                 | $V_{IN}$ =6.0V, $V_{SEN}$ =6.0V,<br>Pch. $V_{RESET}$ =0V                                       | -    | -0.01   | -    | -      | -0.01  | -                     |       |                          |  |

Unless otherwise specified in measurement conditions, Cd/MRB pin and HYS pin are open.

(\*8) Max. value is for XC6132N (Nch open drain).

$^{(*9)}\,For\,0.8V{\leqq}V_{DF(T)}{\leqq}1.7V$  only.

$^{(*12)}$  The ambient temperature range (-40°C $\leq$ Ta $\leq$ 125°C) is a design Value.

### ■ ELECTRICAL CHARACTERISTICS (Continued)

| PARAMETER                            | SYMBOL                                                                                       | CONDITIONS                                                                                                    |                       | Ta=25°C |                       | -40°C≦Ta≦125°C <sup>(*16)</sup> |         |                       | UNITS |        |

|--------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------|---------|-----------------------|---------------------------------|---------|-----------------------|-------|--------|

| PARAIVIETER                          | STINDUL                                                                                      | CONDITIONS                                                                                                    | MIN.                  | TYP.    | MAX.                  | MIN.                            | TYP.    | MAX.                  |       | CINCOT |

| Cd Pin Sink Current<br>(TYPE:A/E)    | I <sub>Cd</sub>                                                                              | V <sub>IN</sub> =1.6V,<br>V <sub>Cd/MRB</sub> =0.5V,<br>V <sub>SEN</sub> =0V                                  | 0.92                  | 1.2     |                       | 0.66                            | 1.2     |                       | mA    | 8      |

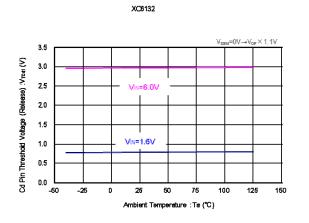

| Cd Pin Threshold<br>Voltage(Release) | $V_{TCd1}$                                                                                   | V <sub>IN</sub> :Refer to V-1 <sup>(*13)</sup> ,<br>V <sub>SEN</sub> =0V→V <sub>DF</sub> ×1.1V                | V×0.46                | Vx0 5   | V <sub>IN</sub> ×0.54 | Vx0 46                          | Vx0 5   | V×0 54                | V     | 9      |

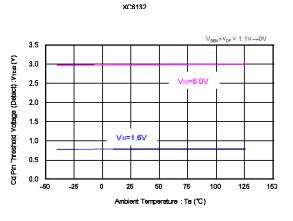

| Cd Pin Threshold<br>Voltage(Detect)  | $V_{\text{TCd2}}$                                                                            | V <sub>IN</sub> :Refer to V-1 <sup>(*13)</sup> ,<br>V <sub>SEN</sub> =V <sub>DF</sub> ×1.1V→0V                | VINAU.40              | VINA0.5 | VIN-0.04              | VINAU.+U                        | VINA0.5 | VIN^0.04              | v     | 9      |

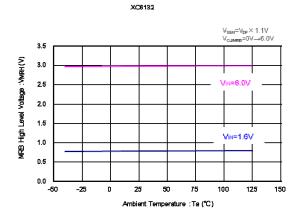

| MRB High Level<br>Voltage            | V <sub>MRH</sub>                                                                             | V <sub>IN</sub> :1.6V~6.0V,<br>V <sub>SEN</sub> = V <sub>DF</sub> ×1.1V,<br>V <sub>IN</sub> >V <sub>SEN</sub> | V <sub>IN</sub> ×0.55 |         | V <sub>IN</sub>       | V <sub>IN</sub> ×0.55           |         | V <sub>IN</sub>       | V     |        |

| MRB Low Level<br>Voltage             | V <sub>MRL</sub>                                                                             | V <sub>IN</sub> :1.6V~6.0V,<br>V <sub>SEN</sub> = V <sub>DF</sub> ×1.1V,<br>V <sub>IN</sub> >V <sub>SEN</sub> | 0                     |         | V <sub>IN</sub> ×0.18 | 0                               |         | V <sub>IN</sub> ×0.18 | V     | 10     |

| MRB Minimum                          | t <sub>MRIN</sub> <sup>(*14)</sup>                                                           | V <sub>IN</sub> :Refer to V-1 <sup>(*13)</sup> ,<br>V <sub>SEN</sub> =V <sub>DF</sub> ×1.1V,                  | 5.0                   | -       | -                     | 5.0                             | -       | -                     |       | 1      |

| Pulse Width                          | Apply pulse from   t <sub>MRIN</sub> (*15) V <sub>DF</sub> ×1.1V to 0V 1   MRB pin. MRB pin. | $V_{DF}$ ×1.1V to 0V to the                                                                                   | 32.0                  | -       | -                     | 32.0                            | -       | -                     | µs (1 | W      |

Unless otherwise specified in measurement conditions, Cd/MRB pin and HYS pin are open.

$^{(^{\ast}13)}$  For  $V_{IN}$  conditions, refer to SPEC TABLE (p.10).

(\*14) Specification is guaranteed for types A/B/C/D/L/E/F/H/K/M of the CMOS output product and types E/F/H/K/M of the Nch open drain product.

$^{(^{*}15)}$  Specification is guaranteed for types A/B/C/D/L of the Nch open drain output product.

$^{(*16)}$  The ambient temperature range (-40°C $\leq$ Ta $\leq$ 125°C) is a design Value.

### ■ELECTRICAL CHARACTERISTICS (SPEC TABLE)

Table of Characteristics by Voltage Setting

| NOMINAL            | V-1                  | E    | -1        | E           | -2      | E    | -3        | E           | -4      |

|--------------------|----------------------|------|-----------|-------------|---------|------|-----------|-------------|---------|

| DETECT             | V-1                  | Ta=  | 25°C      | -40°C≦Ta    | a≦125°C | Ta=  | 25°C      | -40°C≦Ta    | a≦125°C |

| VOLTAGE(V)         | INPUT                |      | Supply Cu | rrent 1(µA) |         |      | Supply Cu | rrent 2(µA) |         |

| V <sub>DF(T)</sub> | VOLTAGE<br>(V)       | TYP. | MAX.      | TYP.        | MAX.    | TYP. | MAX.      | TYP.        | MAX.    |

| 0.8                | 1.6                  |      |           |             |         |      |           |             |         |

| 0.9                | ↑                    |      |           |             |         |      |           |             |         |

| 1.0                | ↑                    |      |           |             |         |      |           |             |         |

| 1.1                | ↑                    |      |           |             |         |      |           |             |         |

| 1.2                | ↑                    | 1.28 | 2.65      | 1.28        | 3.92    | 1.32 | 2.75      | 1.32        | 4.26    |

| 1.3                | ↑                    | 1.20 | 2.05      | 1.20        | 3.92    | 1.52 | 2.75      | 1.52        | 4.20    |

| 1.4                | ↑                    |      |           |             |         |      |           |             |         |

| 1.5                | V <sub>DF</sub> ×1.1 |      |           |             |         |      |           |             |         |

| 1.6                | ↑                    |      |           |             |         |      |           |             |         |

| 1.7                | ↑                    |      |           |             |         |      |           |             |         |

| 1.8                | ↑                    |      |           |             |         |      |           |             |         |

| 1.9                | 1                    | 1.30 | 2.70      | 1.30        | 4.02    | 1.43 | 2.91      | 1.43        | 4.49    |

| 2.0                | ↑                    |      |           |             |         |      |           |             |         |

### ■ELECTRICAL CHARACTERISTICS (SPEC TABLE) (Continued)

| lable of Characteristics by Voltage Setting |           |              |                     |              |  |  |  |  |  |  |

|---------------------------------------------|-----------|--------------|---------------------|--------------|--|--|--|--|--|--|

| NOMINAL<br>DETECT                           | E-5(Ta    | a=25°C)      | E-6(-40°C≦Ta≦125°C) |              |  |  |  |  |  |  |

| VOLTAGE(V)                                  | SENSE Res | sistance(MΩ) | SENSE Res           | sistance(MΩ) |  |  |  |  |  |  |

| V <sub>DF(T)</sub>                          | MIN.      | TYP.         | MIN.                | TYP.         |  |  |  |  |  |  |

| 0.8                                         | 7.5       | 20.7         | 5.9                 | 20.7         |  |  |  |  |  |  |

| 0.9                                         | 8.6       | 23.3         | 6.8                 | 23.3         |  |  |  |  |  |  |

| 1.0                                         | 10.0      | 26.1         | 7.6                 | 26.1         |  |  |  |  |  |  |

| 1.1                                         | 11.0      | 28.6         | 8.5                 | 28.6         |  |  |  |  |  |  |

| 1.2                                         | 12.2      | 31.3         | 9.3                 | 31.3         |  |  |  |  |  |  |

| 1.3                                         | 13.4      | 33.9         | 10.2                | 33.9         |  |  |  |  |  |  |

| 1.4                                         | 14.5      | 36.6         | 11.1                | 36.6         |  |  |  |  |  |  |

| 1.5                                         | 15.7      | 38.6         | 11.9                | 38.6         |  |  |  |  |  |  |

| 1.6                                         | 16.9      | 39.2         | 12.8                | 39.2         |  |  |  |  |  |  |

| 1.7                                         | 18.1      | 39.8         | 13.6                | 39.8         |  |  |  |  |  |  |

| 1.8                                         | 19.3      | 40.4         | 14.5                | 40.4         |  |  |  |  |  |  |

| 1.9                                         | 19.0      | 40.2         | 14.3                | 40.2         |  |  |  |  |  |  |

| 2.0                                         | 18.6      | 39.9         | 14.0                | 39.9         |  |  |  |  |  |  |

Table of Characteristics by Voltage Setting

### ■TEST CIRCUITS

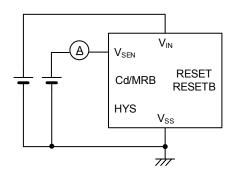

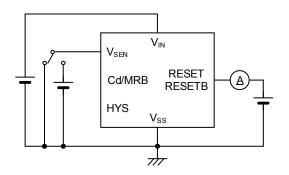

CIRCUIT(1)

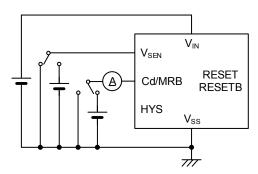

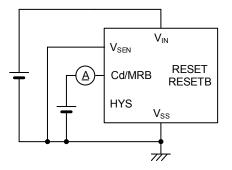

#### CIRCUIT(2)

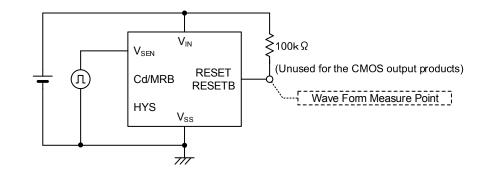

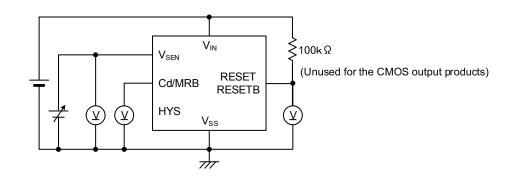

#### CIRCUIT(3)

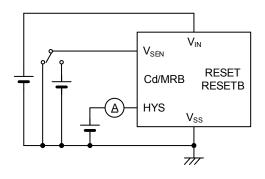

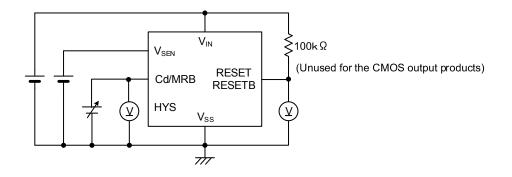

#### CIRCUIT(4)

\*"RESET" is A/B/C/D/L type, and "RESETB" is E/F/H/K/M type.

### ■TEST CIRCUITS (Continued)

CIRCUIT(5)

#### CIRCUIT<sup>®</sup>

CIRCUIT 7

CIRCUIT®

\*"RESET" is A/B/C/D/L type, and "RESETB" is E/F/H/K/M type.

TOIREX 13/30

### ■TEST CIRCUITS (Continued)

#### CIRCUIT(9)

#### CIRCUIT<sup>1</sup>

#### CIRCUIT

\*"RESET" is A/B/C/D/L type, and "RESETB" is E/F/H/K/M type.

TOREX 15/30

### ■ OPERATIONAL DESCRIPTION

#### <Basic Operation>

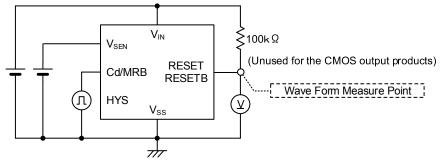

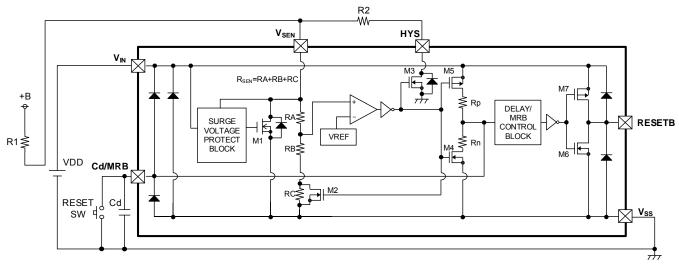

Fig. 1 shows a typical block diagram. Fig. 2 shows the timing chart of Fig. 1.

\* The XC6132N series (N-ch open drain output) requires a resistor to pull up the output.

Fig. 1: Typical block diagram (Active Low product)

①In the initial state, a voltage that is sufficiently high (MAX.:6.0V) with respect to the release voltage is applied to the  $V_{SEN}$  pin, and the delay capacitance Cd is charged up to the power input pin voltage. The  $V_{SEN}$  pin voltage starts to fall, and during the time until it reaches the detect voltage ( $V_{SEN} > V_{DF}$ ),

$V_{\text{RESETB}}$  is High level (=V<sub>IN</sub>).

Note: If the pull-up resistor is connected to a power supply other than the power input pin V<sub>IN</sub> when using the Nch open drain output (XC6132N), High level will be the voltage of the power supply to which the pull-up resistor is connected.

### ■OPERATIONAL DESCRIPTION (Continued)

(2)The V<sub>SEN</sub> pin voltage continues to drop, and when it reaches the detect voltage (V<sub>SEN</sub>=V<sub>DF</sub>), the Nch transistor for delay capacitance discharge turns ON, and discharge of the delay capacitance Cd starts through the delay resistor Rn.

The time from  $V_{SEN}=V_{DF}$  until  $V_{RESETB}$  reaches Low level is the detect delay time  $t_{DF}$  (the detect time when the capacitor is not connected to the Cd/MRB pin is  $t_{DF0}$ ). The delay capacitance Cd is discharged through the delay resistor Rn when it is above the threshold voltage of  $V_{TCD2}$ . When it is below the threshold voltage of  $V_{TCD2}$ , the delay capacitance Cd is discharged faster through the internal built-in low impedance switch.

(3) During the time that the  $V_{SEN}$  pin voltage is below the detect voltage  $V_{DF}$ , the delay capacitance Cd discharges to ground level. The  $V_{SEN}$  pin starts rising again, and during the time until it reaches the release voltage ( $V_{SEN}$ <br/>V $_{DF}$ + $V_{HYS}$ ),  $V_{RESETB}$  holds Low level.

(4) The V<sub>SEN</sub> pin voltage continues to rise, and when it reaches the release voltage (V<sub>DF</sub>+V<sub>HYS</sub>), the Nch transistor for delay capacitance discharge turns OFF, and charging of the delay capacitance Cd through the delay resistor Rp starts. The delay capacitance Cd is discharged through the delay resistor Rp when it is below the threshold voltage of V<sub>TCD1</sub>. When it is above the threshold voltage of V<sub>TCD1</sub>, the delay capacitance Cd is discharged faster through the internal built-in low impedance switch.

(5) When the delay capacitance pin voltage reaches  $V_{TCd1}$ ,  $V_{RESETB}$  changes to High level. The time from  $V_{SEN}=V_{DF}+V_{HYS}$  until the  $V_{RESETB}$  logic changes is the release delay time  $t_{DR}$  (the release time when the capacitor is not connected to the Cd/MRB pin is  $t_{DR0}$ ).

<sup>(6)</sup>During the time that the V<sub>SEN</sub> pin voltage is higher than the detect voltage (V<sub>SEN</sub>>V<sub>DF</sub>), V<sub>RESETB</sub> holds High level.

The above operation description is for an Active Low detection product.

For an Active High product, reverse the logic of the reset pin.

In the factory shipping state, internal hysteresis is not added ( $V_{HYS} = V_{DF}x0.001V(TYP.)$ ), so please add a hysteresis of 1% or more with an external resistor. For the calculation method, refer to <Hysteresis external adjustment function> below. Also please refer to "Notes on use 5 & 6" on page 19.

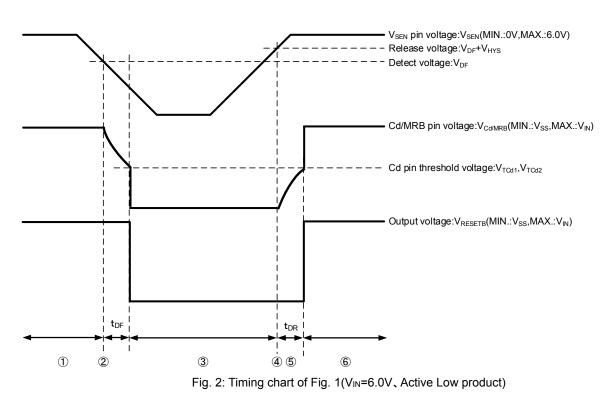

#### <Hysteresis external adjustment function>

Hysteresis can be added as desired by inserting a resistor between the node to monitor and V<sub>SEN</sub> pin, and between the V<sub>SEN</sub> pin and HYS pin.

The calculation method for adding hysteresis by increasing only the release voltage and leaving the detect voltage unchanged is given below.

For the circuit schematic, refer to Fig. 3: Hysteresis Augmentation Circuit 1.  $V_{DR}(H)=V_{DR}(T)\times\{1+(RD/RE)\}$ Hysteresis width= $V_{DR}(H)-V_{DF}(T)$ Example 1: RD=200k $\Omega$ , RE=200k $\Omega$ , V<sub>DF</sub>(T)=1.000V, V<sub>DR</sub>(T)=1.001V.  $V_{DR}(H)=2.002V$ Hysteresis width=2.002-1.000 =1.002V

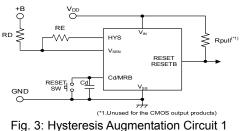

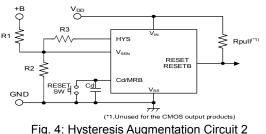

The calculation method for detecting high voltage and adding hysteresis is shown below. For the circuit schematic, refer to Fig. 4: Hysteresis Augmentation Circuit 2.  $V_{DF}(H)=V_{DF}(T)\times\{1+(R1/R2)\}$   $V_{DR}(H)=V_{DR}(T)\times\{1+(R1/R2)+(R1/R3)\}$ Hysteresis width= $V_{DR}(H)-V_{DF}(H)$ Example 2: R1=R3=500k $\Omega$ , R2=200k $\Omega$ , V<sub>DF</sub>(T)=2.000V, V<sub>DR</sub>(T)=2.002V.  $V_{DF}(H)=7.0V$

V<sub>DR</sub>(H)=9.009V Hysteresis width=9.009-7.0=2.009V

(Note 1)  $V_{DF}(H)$  is the detect voltage after external adjustment.

(Note 2) V<sub>DR</sub>(H) is the release voltage after external adjustment.

(Note 3)  $V_{DR}(T)$  is the release voltage.

(Note 4)  $V_{DF}(T)$  is the detect voltage.

(Note 5) The R2 resistance is in parallel with the internal  $R_{SEN}$  resistance, and thus to increase the accuracy of the detect voltage and release voltage after external adjustment, select an R2 resistance that is sufficiently small with respect to the  $R_{SEN}$  resistance. For  $R_{SEN}$  resistance values, refer to SPEC TABLE (p.11).

(Note 6) If high voltage is to be detected, divide the voltage with resistors R1 and R2 so that  $V_{SEN}$  pin  $\leq 6V$ . The battery voltage (+B) assumes up to 12V in this case.

### ■ OPERATIONAL DESCRIPTION (Continued)

#### <Release delay time / detect delay time>

The release delay time and detect delay time are determined by the delay resistors (Rp and Rn) and the delay capacitance Cd. The ratio of the delay resistances (Rp and Rn) is selectable from 5 options. The delay time is adjustable using the combination of delay resistance and delay capacitance value. (Refer to "Selection Guide") The release delay time (t<sub>DR</sub>) is calculated using Equation (1).  $t_{DR}=Rp \times Cd \times \{-ln(1 - V_{TCd1}/V_{IN})\} + t_{DR0} \dots (1)$ \* In is the natural logarithm. The delay capacitance pin threshold voltage is V<sub>TCd1</sub>=V<sub>IN</sub>/2(TYP.), and thus when t<sub>DR0</sub> can be neglected, the release delay time can be calculated simply using Equation (2).

t<sub>DR</sub>=Rp×Cd×[-In{1-(V<sub>IN</sub>/2)/V<sub>IN</sub>}]=Rp×Cd×0.693 ...(2)

The detect delay time (t<sub>DF</sub>) is calculated using Equation (3).

$t_{DF}=Rn \times Cd \times \{-ln(V_{TCd2}/V_{IN})\} + t_{DF0} \dots (3)$ \* In is the natural logarithm.

The delay capacitance pin threshold voltage is  $V_{TCd2}=V_{IN}/2$  (TYP.), and thus when

$t_{DF0}$  can be neglected, the detect delay can be calculated simply using Equation (4).

$t_{DF}=Rn \times Cd \times \{-ln(V_{IN}/2)/V_{IN}\}=Rn \times Cd \times 0.693 \dots (4)$

Example 3: When type A is selected (Rp:Rn=144k $\Omega$ :0 $\Omega$ ), the delay times are as follows: If Cd is set to 0.1uF. tpg=144×10<sup>3</sup>×0.1×10<sup>-6</sup>×0.693=10ms t<sub>DF</sub> is the detect delay time (t<sub>DFO</sub>) when the delay capacitance Cd is not connected.

Example 4: When type B is selected (Rp:Rn=144k $\Omega$ : 18k $\Omega$ ), the delay times are as follows: If Cd is set to 0.1uF. tpg=144×10<sup>3</sup>×0.1×10<sup>-6</sup>×0.693=10ms t<sub>DF</sub> =18×10<sup>3</sup>×0.1×10<sup>-6</sup>×0.693=1.25ms

(Note 7) The release delay times  $t_{DR}$  in Examples 3 and 4 are the values calculated from Equation (2). (Note 8) The detect delay time  $t_{DF}$  in Example 4 is the value calculated from Equation (4).

(Note 9) Note that the delay times will vary depending on the actual capacitance value of the delay capacitance Cd.

#### <Manual reset function>

The Cd/MRB pin can also be used as a manual reset pin. When the Cd and RESET switch are connected to the Cd/MRB pin (refer to Fig.1), and under the release condition, if the RESET switch turns on, then the detect signal is generated at the RESET/RESETB pin forcibly.

For Active Low type (RESETB), under the release condition, if the RESET switch turns on, then the voltage at the RESETB pin changes from H to L after the detect delay time.

For Active High type (RESET), under the release condition, if the RESET switch turns on, then the voltage at the RESET pin changes from L to H after the detect delay time.

Under the detect condition, the condition will be kept even if the RESET switch turns on and off.

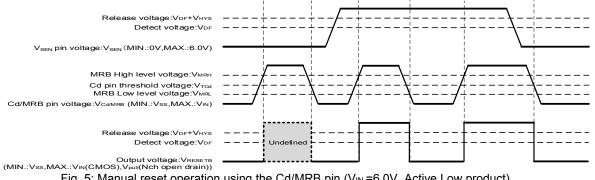

In the case that either H level or L level is fed to the Cd/MRB pin without the RESET switch, the behavior of the XC6132 follows the timing chart in Fig. 5.

L level is fed to the MRB pin under the detect condition, the RESET switch will be kept. H level is fed to the MRB pin under the detect condition, the RESET switch will be undefined.

Even though the voltage at the VSEN pin changes from a higher voltage than the detect voltage to a lower voltage, as long as H level is fed to the MRB pin, the release condition is kept.

If H level or L level is fed to the Cd/MRB pin forcibly, then even though Cd is connected to the pin, the XC6132 can't have any delay time.

Fig. 5: Manual reset operation using the Cd/MRB pin (VIN =6.0V, Active Low product)

### ■OPERATIONAL DESCRIPTION (Continued)

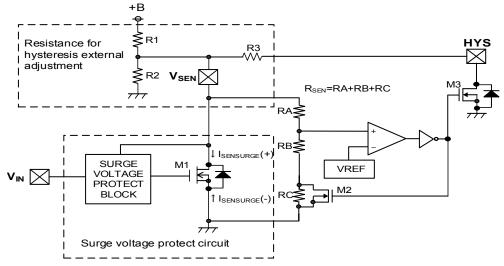

#### <Surge voltage protection function>

A surge voltage protection circuit is incorporated into the  $V_{SEN}$  pin. A surge current of +2.5mA( $\geq$ 200ms), -2.5mA( $\geq$ 20ms) is possible.

A positive surge current (I<sub>SENSURGE(+)</sub>) flows when M1 is turned ON by a SURGE VOLTAGE PROTECT BLOCK signal.

A negative surge current ( $I_{SENSURGE(-)}$ ) is made to flow by the M1 parasitic diode.

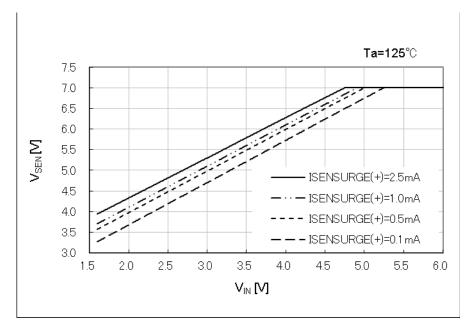

When a positive surge current flows and the surge voltage protection circuit activates, the  $V_{SEN}$  pin voltage rises in proportion to the  $V_{IN}$  voltage and surge current, so adjust the  $I_{SEN}$  current with an external resistor so that the  $V_{SEN}$  pin voltage does not exceed the operating voltage. Refer to Fig. 7.

%The  $V_{\text{SEN}}$  voltage rise is most pronounced at high temperature.

Example 5: When  $V_{IN}$ =3.3V and  $I_{SENSURGE(+)}$ =2.5mA (MAX), the  $V_{SEN}$  pin voltage from Fig. 7 is 5.6V. If the maximum battery voltage (+B) pin voltage is 100V, a voltage of (100-5.6)=94.4V will be applied to the R1 resistor. To keep the surge current from exceeding 2.5mA, use a resistance of R1=V/I=94.4/0.0025=37.8k $\Omega$  or above.

Example 6: When  $V_{IN}$  = 3.3V and  $I_{SENSURGE(-)}$  = -2.5mA(MAX), Vf of the parasitic diode M1 is -0.9V (MAX). If the battery voltage (+B) maximum is -100V, the voltage applied to the R1 resistor will be {-100 - (-0.9)} = -99.1V. To limit the surge current to -2.5mA, set the R1 resistance to R1 = V/I= -99.1/-0.0025 = 39.6k $\Omega$  or higher.

If the surge voltage on the positive side is different from the negative side, calculate the R1 resistance value using the side where the voltage difference applied to the R1 resistor is greatest.

Fig. 6: Surge voltage protect circuit

Fig. 7: Example of VIN-VSEN characteristics

19/30

### ■NOTES ON USE

1) Please use this IC within the stated maximum ratings. For temporary, transitional voltage drop or voltage rising phenomenon, the IC is liable to malfunction should the ratings be exceeded.

2) The power input pin voltage may fall due to the flow through current during IC operation and the resistance component between the power supply and the power input pin.

In the case of CMOS output, a drop in the power input pin voltage may occur in the same way due to the output current. When this happens, if the power input pin voltage drops below the minimum operating voltage, a malfunction may occur.

3) Note that large, sharp changes of the power input pin voltage may lead to malfunction.

4) Power supply noise is sometimes a cause of malfunction. Sufficiently test using the actual device, such as inserting a capacitor between  $V_{IN}$  and GND.

5) Internal hysteresis is not initially included with the product. Connect external resistors to the  $V_{SEN}$  pin and HYS pin to add a hysteresis of 1% or more. Note that if hysteresis is not added with external resistors, oscillation will occur when switching takes place at the detect voltage or the release voltage.

6) There is a possibility that oscillation will occur if the resistances of the  $V_{SEN}$  pin and HYS pin are high. Use a resistance of 1M $\Omega$  or less between the node to monitor and  $V_{SEN}$  pin, and between the  $V_{SEN}$  pin and HYS pin.

7) Exercise caution if  $V_{IN}$  and  $V_{SEN}$  are started in common, as the output will be undefined until  $V_{IN}$  reaches the operating voltage.

8) For a manual reset function, in case when the function is activated by feeding either MRB H level or MRB L level to Cd/MRB pin instead of using a reset switch, please note these phenomena below;

The RESET output signal will be undefined when MRB H is fed to Cd/MRB pin under the detect condition.

• The RESET output signal will be undefined based on the voltage relationship between V<sub>SEN</sub> pin and Cd/MRB pin.

9) When an N-ch open drain output is used, the V<sub>RESETB</sub> voltage at detection and release is determined by the pull-up resistance connected to the output pin. Refer to the following when selecting the resistance value.

At detection:

V<sub>RESETB</sub>=V<sub>pull</sub>/(1+R<sub>pull</sub>/R<sub>ON</sub>) V<sub>pull</sub>: Voltage after pull-up

$R_{ON}^{(*1)}$ : ON resistance of N-ch driver M6 (calculated from V<sub>RESETB</sub>/I<sub>RBOUTN</sub> based on electrical characteristics) Example: When V<sub>IN</sub>=2.0V<sup>(\*2)</sup>, R<sub>ON</sub>=0.3/4.2×10<sup>-3</sup>=71.4 $\Omega$  (MAX.).

If it is desired to make V<sub>RESETB</sub> at detection 0.1V or less when V<sub>pull</sub> is 3.0V,

$R_{pull} = \{(V_{pull}/V_{RESETB})-1\} \times R_{ON} = \{(3/0.1)-1\} \times 71.4 \Rightarrow 2.1 k\Omega$

Therefore, to make the output voltage at detection 0.1V or less under the above conditions, the pull-up resistance must be  $2.1k\Omega$  or higher. (\*1) Note that R<sub>ON</sub> becomes larger as V<sub>IN</sub> becomes smaller.

$^{(*2)}$  For V<sub>IN</sub> in the calculation, use the lowest value of the input voltage range you will use.

At release:

V<sub>RESETB</sub>=V<sub>pull</sub>/(1+R<sub>pull</sub>/R<sub>off</sub>) V<sub>pull</sub>: Voltage after pull-up

Roff: Resistance when N-ch driver M6 is OFF (calculated from VRESETB/ILEAKN based on electrical characteristics)

Example: When  $V_{\text{pull}}$  is 6.0V,  $R_{\text{off}}$ =6/(0.1×10<sup>-6</sup>)=60M $\Omega$  (MIN.). If it is desired to make  $V_{\text{RESETB}}$  5.99V or higher,

$$R_{pull} = \{(V_{pull}/V_{RESETB})-1\} \times R_{off} = \{(6/5.99)-1\} \times 60 \times 10^6 \Rightarrow 100 k\Omega$$

Therefore, to make the output voltage at release 5.99V or higher under the above conditions, the pull-up resistance must be  $100k\Omega$  or less.

10) If the discharge time of the delay capacitance Cd at detection is short and the delay capacitance Cd cannot be discharged to ground level, charging will take place at the next release operation with electric charge remaining in the delay capacitance Cd, and this may cause the release delay time to become noticeably short.

11) If the charging time of the delay capacitance Cd at release is short and the delay capacitance Cd cannot be charged to the  $V_{IN}$  level, the delay capacitance Cd will discharge from less than the  $V_{IN}$  level at the next detection operation, and this may cause the detect delay time to become noticeably short.

12) Torex places an importance on improving our products and their reliability. We request that users incorporate fail-safe designs and post-aging protection treatment when using Torex products in their systems.

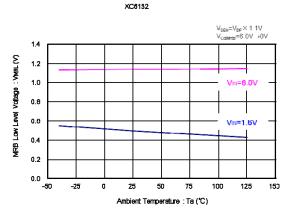

### ■TYPICAL PERFORMANCE CHARACTERISTICS

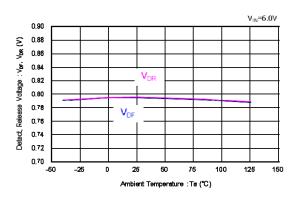

(1) Detect, Release Voltage vs. Ambient Temperature

#### XC6132 (V<sub>DF(T)</sub>=0.8V)

(2) Output Voltage vs Sense Voltage

Ţ

ε 6

5

4

3

2

1

0

0

1

OutPut Voltage : Vress

XC6132x08A (V<sub>DFCD</sub>=0.8V)

3

Vsev pin Voltage : VSEN(V)

4

V<sub>IN</sub>-6.0V

-40°C

6

Ta=25°C

Ta=125°0

5

2

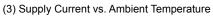

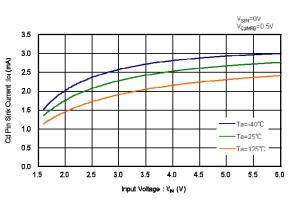

(4) Supply Current vs. Input Voltage

XC6132

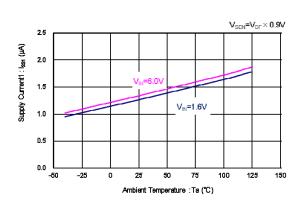

### ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

(5) Sense Resistance vs Ambient Temperature

(6) Delay Resistance vs Ambient Temperature XC6132

XC6132

XC6132

### ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

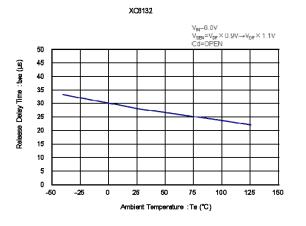

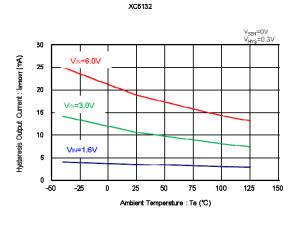

#### (7) Delay Time vs Ambient Temperature

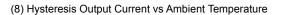

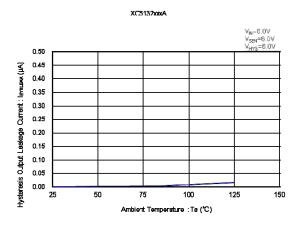

(10) Hysteresis Output Leakage Current vs Ambient Temperature

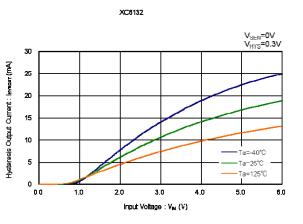

(9) Hysteresis Output Current vs Input Voltage

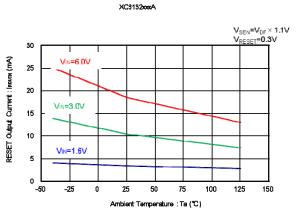

(11) RESET Output Current vs Ambient Temperature

### ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

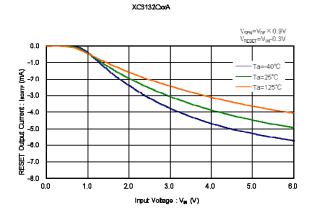

(11) RESET Output Current vs Ambient Temperature (Continued)

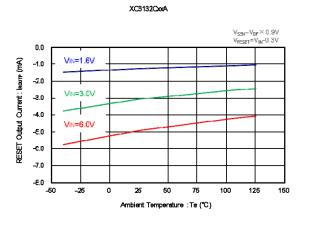

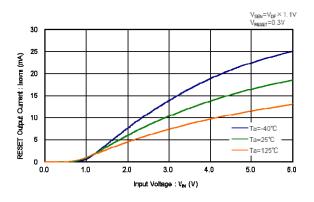

(12) RESET Output Current vs Input Voltage

XC6132000A

0.50

0.45

0.40

0.35

0.30

0.25 0.20 0.15 0.10

0.05

0.00

25

50

RESET Output: Leakage Currert : ILEAK (ILA)

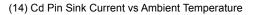

(13) RESET Output Leakage Current vs Ambient Temperature

100

Ambient Temperature : Ta (°C)

**'2**5

150

V<sub>N</sub>=6.0V V<sub>SEN</sub>=0V V<sub>RESET</sub>=6.0V

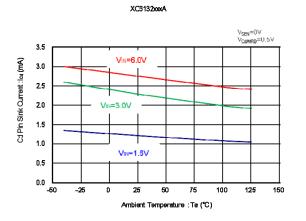

(15) Cd Pin Sink Current vs Input Voltage

75

TOIREX 23/30

### ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

(16) Cd Pin Threshold Voltage vs Ambient Temperature

(17) MRB High Level Threshold Voltage vs Ambient Temperature

(18) MRB Low Level Threshold Voltage vs Ambient Temperature

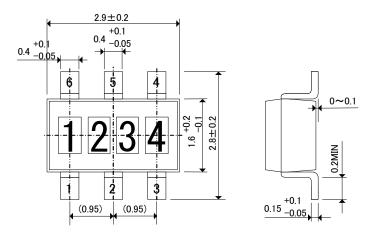

### ■ PACKAGING INFORMATION

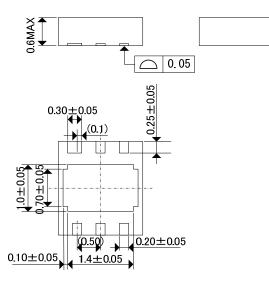

#### ●SOT-26 (unit:mm)

●SOT-26 Reference Pattern Layout (unit:mm)

### ■ PACKAGING INFORMATION (Continued)

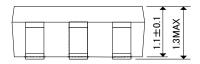

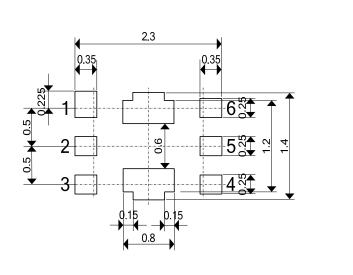

●USP-6C (unit:mm)

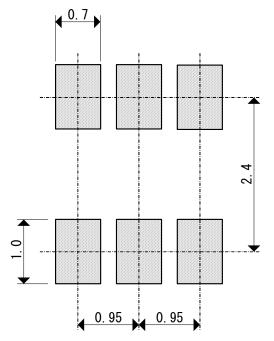

●USP-6C Reference Pattern Layout (unit:mm)

0.45

U

0.05

1.0

6

4 🖏

5 <sup>6</sup> ÷ <sup>∞</sup>

2.4

0.45

3 🕖

### ●USP-6C Reference Metal Mask Design

0.5 0.5

## ■PACKAGING INFORMATION (Continued)

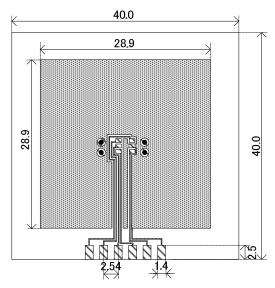

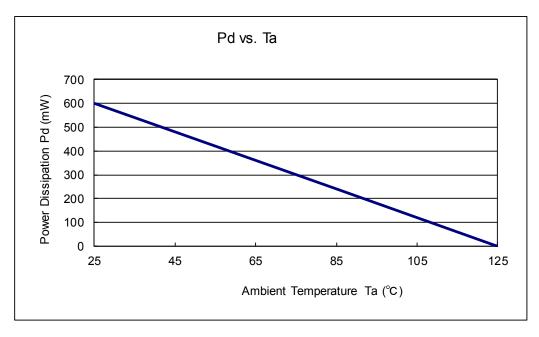

### SOT-26 Power Dissipation Toprmax+125°C (40mm x 40mm Standard board)

Power dissipation data for the SOT-26 is shown in this page. The value of power dissipation varies with the mount board conditions. Please use this data as the reference data taken in the following condition.

#### 1. Measurement Condition

| Condition:    | Mount on a board                               |

|---------------|------------------------------------------------|

| Ambient:      | Natural convection                             |

| Soldering:    | Lead (Pb) free                                 |

| Board:        | Dimensions 40 x 40 mm                          |

|               | (1600 mm2 in one side)                         |

|               | Copper (Cu) traces occupy 50% of the board     |

|               | area In top and back faces                     |

|               | Package heat-sink is tied to the copper traces |

| Material:     | Glass Epoxy (FR-4)                             |

| Thickness:    | 1.6mm                                          |

| Through-hole: | 4 x 0.8 Diameter                               |

Evaluation Board (Unit:mm)

#### 2. Power Dissipation vs. Ambient Temperature

| Board Mount (Tj max = 125°C) |                          |                           |

|------------------------------|--------------------------|---------------------------|

| Ambient Temperature (°C)     | Power Dissipation Pd(mW) | Thermal Resistance (°C/W) |

| 25                           | 600                      |                           |

| 85                           | 240                      | 166.67                    |

| 125                          | 0                        |                           |

### ■PACKAGING INFORMATION (Continued)

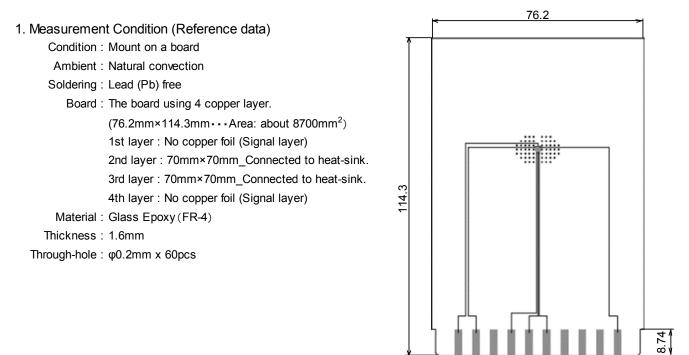

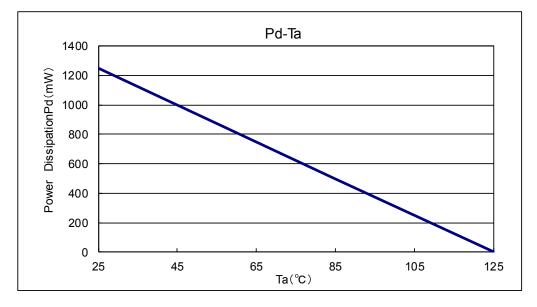

#### USP-6C Power Dissipation (JEDEC board)

Power dissipation data for the USP-6C is shown in this page. The value of power dissipation varies with the mount board conditions. Please use this data as one of reference data taken in the described condition.

#### 2. Power Dissipation vs. Ambient temperature

#### Board Mount(Tjmax = 125°C)

| AmbientTemperature(°C) | PowerDissipation Pd(mW) | <i>θ</i> ja(°C/W) |

|------------------------|-------------------------|-------------------|

| 25                     | 1250                    |                   |

| 85                     | 500                     | 80.00             |

| 125                    | 0                       |                   |

Evaluation Board (Unit:mm)

### ■MARKING RULE

SOT-26

USP-6C

1 represents products series

| MARK | PRODUCT SERIES |

|------|----------------|

| Х    | XC6132*****-G  |

2,3 represents internal sequential number

01, ...,09, 10, ..., 99, A0, ..., A9, B0, ..., B9, ..., Z9... repeated. (G, I, J, O, Q, W excluded)

(4),(5) represents production lot number

01~09, 0A~0Z, 11~9Z, A1~A9, AA~AZ, B1~ZZ in order.

(G, I, J, O, Q, W excluded)

\* No character inversion used.

- 1. The product and product specifications contained herein are subject to change without notice to improve performance characteristics. Consult us, or our representatives before use, to confirm that the information in this datasheet is up to date.

- 2. The information in this datasheet is intended to illustrate the operation and characteristics of our products. We neither make warranties or representations with respect to the accuracy or completeness of the information contained in this datasheet nor grant any license to any intellectual property rights of ours or any third party concerning with the information in this datasheet.

- 3. Applicable export control laws and regulations should be complied and the procedures required by such laws and regulations should also be followed, when the product or any information contained in this datasheet is exported.

- 4. The product is neither intended nor warranted for use in equipment of systems which require extremely high levels of quality and/or reliability and/or a malfunction or failure which may cause loss of human life, bodily injury, serious property damage including but not limited to devices or equipment used in 1) nuclear facilities, 2) aerospace industry, 3) medical facilities, 4) automobile industry and other transportation industry and 5) safety devices and safety equipment to control combustions and explosions. Do not use the product for the above use unless agreed by us in writing in advance.

- 5. Although we make continuous efforts to improve the quality and reliability of our products; nevertheless Semiconductors are likely to fail with a certain probability. So in order to prevent personal injury and/or property damage resulting from such failure, customers are required to incorporate adequate safety measures in their designs, such as system fail safes, redundancy and fire prevention features.

- 6. Our products are not designed to be Radiation-resistant.

- 7. Please use the product listed in this datasheet within the specified ranges.

- 8. We assume no responsibility for damage or loss due to abnormal use.

- 9. All rights reserved. No part of this datasheet may be copied or reproduced unless agreed by Torex Semiconductor Ltd in writing in advance.

TOREX SEMICONDUCTOR LTD.

单击下面可查看定价,库存,交付和生命周期等信息

>>Torex Semiconductor(特瑞仕)