ETR32008-001

## Offline Controller for LED Lighting with Power Factor Correction

### ■GENERAL DESCRIPTION

The XC9404 series are LED lighting offline controllers that use PFM(Pulse Frequency Modulation) control and have a Power Factor improvement function. The operating input voltage range is 85VAC to 270VAC, and the current is controlled on the primary side without using a Opto-coupler or secondary side control circuit. Because LED current fluctuations caused by input voltage fluctuations and LED voltage fluctuations can be suppressed, a stable LED lighting power supply is obtained.

A high Power Factor and low THD are attained by synchronizing the input current with the input voltage, and operation in DCM(Discontinuous Current Mode) makes it possible to achieve high efficiency. An internal acceleration startup circuit enables the LED lighting to illuminate quickly.

Over Voltage Protection, Over Current Protection, UVLO and Thermal shutdown are provided as protective functions to protect the LED lighting in the event of LED Open/Short-circuiting.

### APPLICATIONS

·LED Bulb

•LED spot Light

•LED Tube

Street Light

Residential Lighting

•Other applications with LED Lighting

### **FEATURES**

Operating Voltage Output Wattage Power Factor / THD

Control Method Function

Protection Function

**Operating Ambient Temperature**

Environmentally Friendly

Package

: 85VAC ~ 270VAC

: up to 50W

- : Power Factor 0.95 or more

- / THD up to 10% attainable

- : PFM control

- : Opto-coupler free due to primary control Built-in acceleration Start

- Low Start up Current 20µA : LED Open/Short protection Over Voltage Protection Over Current Protection UVLO

Thermal shutdown

: SOP-8D

: -40°C ~ +105 °C

: EU RoHS Compliant, Pb Free

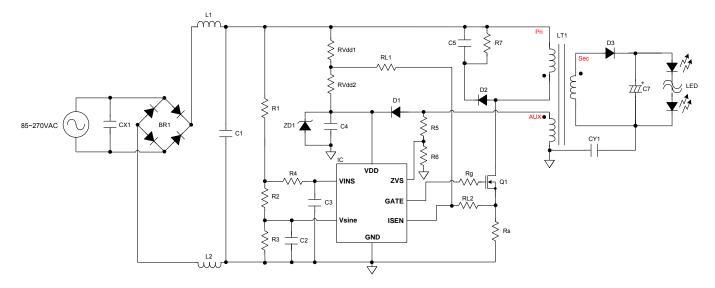

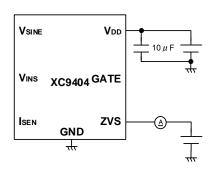

# TYPICAL APPLICATION CIRCUITS

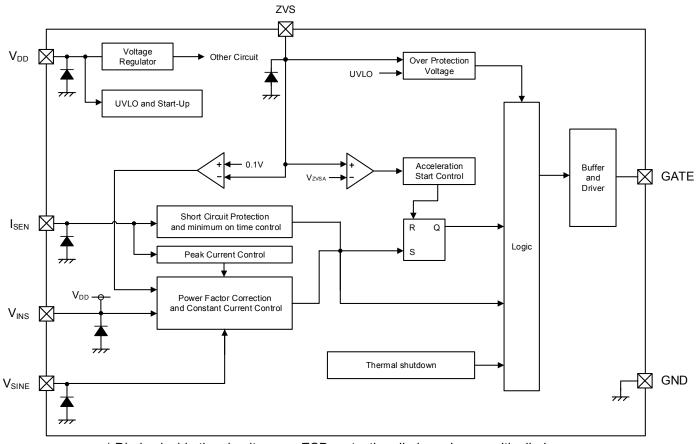

# BLOCK DIAGRAM

XC9404 Series

\* Diodes inside the circuit are an ESD protection diode and a parasitic diode.

# ■ PRODUCT CLASSFICATION

Ordering Information

XC9404123456-7(\*1)

| DESIGNATOR                        | ITEM        | SYMBOL | DESCRIPTION                            |

|-----------------------------------|-------------|--------|----------------------------------------|

| 1                                 | Туре        | А      | With PFC Function                      |

| 2                                 | Application | L      | For Off-line Driver for LED Lighting   |

| 34                                | Accuracy    | 03     | LED Current Accuracy is ±3%            |

| ⑤⑥-⑦ Package<br>(Order Unit) SR-G |             | SR-G   | SOP-8D (2,500pcs/Reel) <sup>(*2)</sup> |

<sup>(\*1)</sup> The "-G" suffix denotes Halogen and Antimony free as well as being fully EU RoHS compliant.

(\*2) The XC9404 reels are shipped in a moisture-proof packing.

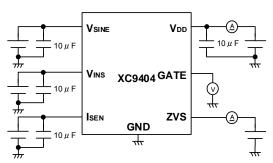

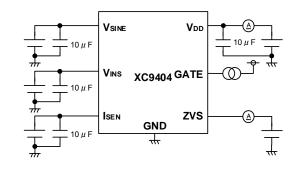

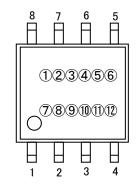

# ■ PIN CONFIGURATION

### ■ PIN ASSIGNMENT

| PIN NUMBER | PIN NAME          | FUNCTIONS                                                                                                                                           |  |  |

|------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1          | NC                | No connection.                                                                                                                                      |  |  |

| 2          | V <sub>SINE</sub> | VSINE pin to detect the rectified sine waveform of input voltage.                                                                                   |  |  |

| 3          | V <sub>INS</sub>  | VINS pin to detect the rectified sine waveform peak value of input voltage.                                                                         |  |  |

| 4          | Isen              | ISEN pin monitors the primary current.                                                                                                              |  |  |

| 5          | ZVS               | ZVS pin to detect the feedback voltage from the auxiliary winding.<br>ZVS voltage is used to control Over Voltage Protection and Acceleration Mode. |  |  |

| 6          | GND               | Ground pin.                                                                                                                                         |  |  |

| 7          | GATE              | External power MOSFET drive pin.                                                                                                                    |  |  |

| 8          | V <sub>DD</sub>   | Power Input pin.                                                                                                                                    |  |  |

# ■ABSOLUTE MAXIMUM RATINGS

|                               |                 |               | Ta=25°C |

|-------------------------------|-----------------|---------------|---------|

| PARAMETER                     | SYMBOL          | RATINGS       | UNITS   |

| V <sub>DD</sub> Pin Voltage   | V <sub>DD</sub> | -0.3 ~ +35    | V       |

| VINS Pin Voltage              | VINS            | -0.3 ~ +7.0   | V       |

| V <sub>SINE</sub> Pin Voltage | VSINE           | -0.3 ~ +7.0   | V       |

| ISEN Pin Voltage              | VISEN           | -0.3 ~ +7.0   | V       |

| ZVS Pin Voltage               | Vzvs            | -40.0 ~ +10.0 | V       |

| GATE Pin Maximum Current      | Igate           | 300           | mA      |

| Power Dissipation             | PD              | 0.525         | W       |

| Operating Ambient Temperature | Та              | -40 ~ 105     | °C      |

| Storage Temperature           | Tstg            | -65 ~ +150    | °C      |

(\*1) All voltages are described based on GND.

Ta=25°C

# ELECTRICAL CHARACTERISTICS

#### XC9404 Series

| PARAMETER                                               | SYMBOL                                         | CONDITIONS                                                                                                                                                                                                                                                                | MIN. | TYP. | MAX. | UNITS | CIRCUIT |

|---------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|---------|

| V <sub>DD</sub> Voltage Range                           | V <sub>DD</sub>                                |                                                                                                                                                                                                                                                                           | 9    | -    | 21   | V     | -       |

| Start-up Threshold<br>Voltage                           | V <sub>ST</sub>                                | $\label{eq:V_SINE} \begin{split} V_{\text{SINE}} = V_{\text{INS}} = 3V, V_{\text{ISEN}} = 2V, V_{\text{ZVS}} = 0V \\ \text{The voltage which } V_{\text{DD}} \text{ pin current becomes 200uA or} \\ \text{more while } V_{\text{DD}} \text{ is increasing.} \end{split}$ | 18   | 19   | 20   | V     | 1       |

| UVLO Detect Voltage                                     | V <sub>UVLO</sub>                              | $\label{eq:V_SINE} \begin{split} V_{SINE} = & V_{INS} = 3V, V_{ISEN} = 2V, V_{ZVS} = 0V \\ The voltage which V_{DD} pin current becomes 200uA or less while V_{DD} is decreasing. \end{split}$                                                                            | 7.5  | 8.0  | 8.5  | V     | 1       |

| V <sub>DD</sub> Over Voltage<br>Protection              | $V_{DD_OVP}$                                   | $\label{eq:V_SINE} \begin{split} V_{SINE} = & V_{INS} = 3V, V_{ISEN} = V_{ZVS} = 0V, V_{DD} = 20V \\ \text{The voltage which GATE Voltage becomes "L" while} \\ V_{DD} \text{ is increasing.} \end{split}$                                                                | 28   | 32   | 34   | V     | 2       |

| Start-up Current                                        | I <sub>ST</sub>                                | $V_{SINE}=V_{INS}=3V, V_{ISEN}=2V, V_{ZVS}=0V$<br>$V_{DD}=V_{ST}=0.5V$                                                                                                                                                                                                    | -    | -    | 20   | μA    | 1       |

| Supply Current                                          | I <sub>DD1</sub>                               | V <sub>SINE</sub> =V <sub>INS</sub> =3V,V <sub>ISEN</sub> =1.2V,V <sub>ZVS</sub> =0V<br>V <sub>DD</sub> =20V→15V                                                                                                                                                          | -    | 1000 | 1300 | μA    | 1       |

| GATE "H" level<br>Voltage                               | $V_{\text{GATEH}}$                             | $V_{SINE}=V_{INS}=3V, V_{ZVS}=V_{ISEN}=0V$<br>$V_{DD}=20V\rightarrow 12V$                                                                                                                                                                                                 | 10   | -    | -    | V     | 1       |

| GATE "L" level<br>Voltage                               | V <sub>GATEL</sub>                             | V <sub>SINE</sub> =V <sub>INS</sub> =3V,V <sub>ZVS</sub> =V <sub>ISEN</sub> =0V,V <sub>DD</sub> =20V→15V<br>V <sub>ISEN</sub> is increased until GATE "L" occurs, 20 mA is<br>applied to the GATE pin, and the GATE pin voltage is<br>measured.                           | -    | -    | 1    | V     | 2       |

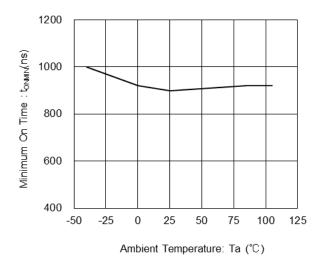

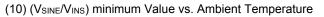

| GATE clamp Voltage                                      | V <sub>GATEC</sub>                             | $V_{SINE}=V_{INS}=3V, V_{ZVS}=V_{ISEN}=0V, V_{DD}=20V$                                                                                                                                                                                                                    | 12   | 13   | 15   | V     | 1       |

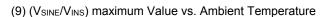

| (V <sub>SINE</sub> /V <sub>INS</sub> ) maximum<br>Value | (V <sub>SINE</sub> /V <sub>INS</sub> )_<br>max | $V_{SINE}=V_{INS}=3V, V_{ZVS}=0V, V_{DD}=20V \rightarrow 15V$<br>The voltage which GATE voltage becomes "L" while $V_{ISEN}$ is increasing.                                                                                                                               | 0.8  | 1.0  | 1.2  | V     | 2       |

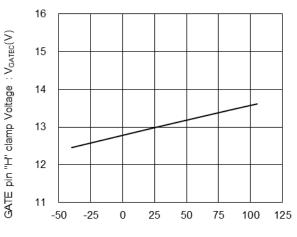

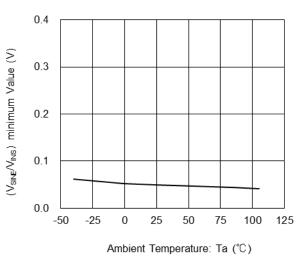

| (V <sub>SINE</sub> /V <sub>INS</sub> ) minimum<br>Value | (V <sub>SINE</sub> /V <sub>INS</sub> )_<br>min | $V_{SINE}$ =0V, $V_{INS}$ =3V, $V_{ZVS}$ =0V, $V_{DD}$ =20V $\rightarrow$ 15V<br>The voltage which GATE voltage becomes "L" while<br>$V_{ISEN}$ is increasing.                                                                                                            | -    | -    | 0.2  | V     | 2       |

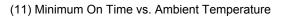

| Minimum On Time                                         | t <sub>onmin</sub>                             | V <sub>SINE</sub> =V <sub>INS</sub> =3V,V <sub>ZVS</sub> =0V,V <sub>ISEN</sub> =2V<br>VDD is raised from 0V to 20V, and the GATE signal<br>pulse width is measured.                                                                                                       | 500  | 750  | 1000 | ns    | 1       |

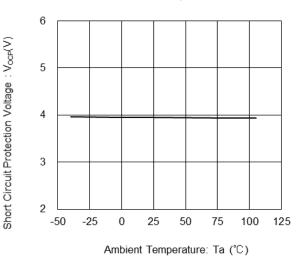

| Short Circuit<br>Protection Voltage                     | V <sub>OCP</sub>                               | $\label{eq:VSINE} \begin{split} &V_{SINE}{=}3V, V_{INS}{=}0.5V, V_{ZVS}{=}V_{ISEN}{=}0V, \\ &V_{DD}{=}20V{\rightarrow}15V \\ & \text{The voltage which GATE voltage becomes "L" while} \\ &V_{ISEN} \text{ is increasing.} \end{split}$                                   | 3.0  | 4.0  | -    | V     | 0       |

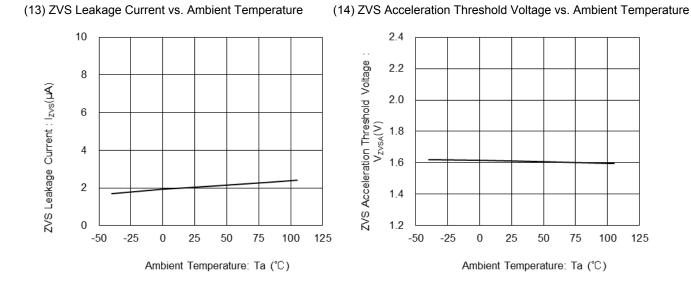

| ZVS Leakage Current                                     | I <sub>ZVS</sub>                               | V <sub>DD</sub> =20V→15V,V <sub>ZVS</sub> =4V                                                                                                                                                                                                                             | -    | 2    | 8    | μΑ    | 3       |

| ZVS Acceleration<br>Threshold Voltage                   | Vzvsa                                          | $V_{SINE}=1V, V_{INS}=3V, V6=1.5V, V_{DD}=20V \rightarrow 15V$<br>The V6 voltage is raised, and the voltage at which the GATE pin voltage oscillation period slows is measured.                                                                                           |      | 1.8  | 2.2  | V     | 4       |

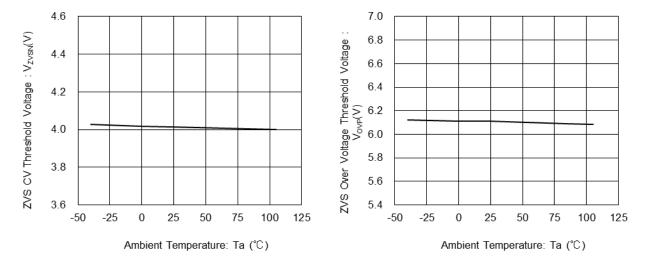

| ZVS CV Threshold<br>Voltage                             | V <sub>ZVSN</sub>                              | $V_{SINE}=1V, V_{INS}=3V, V6=2.8V, V_{DD}=20V \rightarrow 15V$<br>The V6 voltage is raised, and the voltage at which the GATE pin voltage oscillation stops is measured.                                                                                                  |      | 4.0  | 4.4  | V     | 4       |

| ZVS Over Voltage<br>Threshold Voltage                   | V <sub>OVP</sub>                               | $\label{eq:V_SINE} \begin{split} &V_{SINE} = V_{INS} = 3V, V_{ZVS} = V_{ISEN} = 0V, V_{DD} = 20V \rightarrow 15V \\ & \text{The voltage which GATE voltage becomes "L" while} \\ &V_{ISEN} \text{ is increasing.} \end{split}$                                            | 5.6  | 6.0  | 6.9  | V     | 2       |

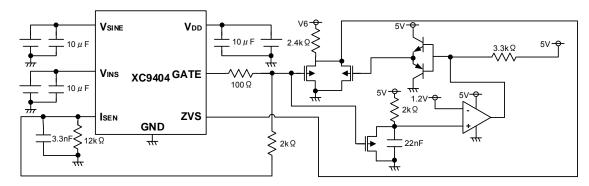

# ■TEST CIRCUITS

1) Circuit ①

2) Circuit2

#### 3) Circuit3

#### 4) Circuit④

### ■OPERATIONAL EXPLANATION

The internal circuitry of the XC9404 series consists of a power factor improvement circuit, buffer drive circuit, over-current protection circuit, over-voltage protection circuit, UVLO circuit and Thermal shutdown circuit. (Refer to the block diagram)

#### <Operation description>

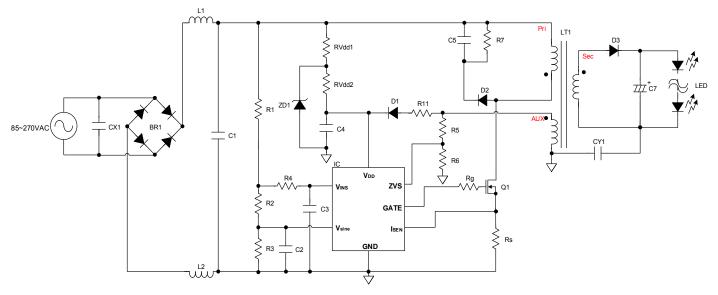

The operation of the XC9404 series is described below using an isolated flyback type circuit.

Fig.1 XC9404 Isolated flyback circuit

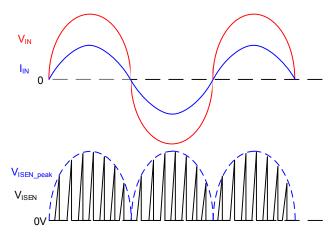

By controlling the primary peak current of the transformer so that it matches the  $V_{ISEN}$  voltage, which has the same phase as the input voltage, the IC improves the power factor. (Refer to Fig. 2)

In addition, by controlling the on-time/off-time so that it is optimum for the input voltage, phase and LED voltage, a stable constant current can be supplied within the input voltage range 85VAC to 270VAC.

The on-time,off-time can be adjusted with external resistances R1 to R3, enabling the optimum constant to be set for the input voltage, LED voltage, LED current. Operation in discontinuous mode (DCM) is recommended for this IC, so the external resistances R1 to R3 should be adjusted to enable discontinuous mode.

Fig.2 XC9404 Operation Waveform

### OPERATIONAL EXPLANATION

<Operation modes>

The XC9404 series operates in modes (a) to (d) based on the ZVS pin voltage.

#### (a) Acceleration Mode

Acceleration Mode is used for fast startup.

To shorten the startup time, the output voltage is low, and when the ZVS pin voltage is below the ZVS Acceleration Threshold Voltage, the IC operates in critical mode rather than Discontinuous Current Mode to reduce the startup time.

When the ZVS pin voltage rises above the ZVS Acceleration Threshold Voltage, the mode changes to CC Mode.

#### (b) CC Mode

CC mode provides the high power factor and low THD that are desirable in a LED lighting power source, and outputs a stable constant current that is not affected by fluctuations of input voltage and LED voltage. While in CC Mode, the IC operates in Discontinuous Current Mode.

#### (c) CV Mode

CV Mode prevents the output voltage from exceeding a set voltage. In the event that the output voltage reaches the over-voltage state, the ZVS pin voltage rises. When the ZVS pin voltage rises above the ZVS CV Threshold Voltage, the GATE pin outputs "L" voltage, and maintains "L" voltage until the ZVS pin voltage drops below the ZVS CV Threshold Voltage.

#### (d) Over-Voltage Protection

This mode prevents damage to peripheral devices in the event that the output voltage reaches the over-voltage state. When the output voltage reaches the over-voltage state, the ZVS pin voltage rises. When the ZVS pin voltage rises above the ZVS Over-Voltage Threshold Voltage, the GATE pin voltage is forcibly latched to the "L" state. To release the voltage from the latched state and return to normal operation, the V<sub>DD</sub> pin voltage is lowered below the latch release at 5.6V voltage and then raised above the Start-up Threshold Voltage.

Even when the LED is in the open state, this function can suppress destruction of external components.

#### <Minimum On Time>

Because the charge stored on the capacitance between Q1 Drain-Source flows to the sense resistance Rs immediately after power MOSFET Q1 turns on, a spike occurs in the  $I_{SEN}$  pin voltage. To prevent this spike noise from causing malfunctioning of the internal circuitry, a minimum on-time  $t_{ONMIN}$  is established. The GATE pin voltage is forcibly held in the "L" state until the minimum on-time elapses.

#### <GATE pin Voltage>

When in the GATE pin "H" state, the GATE pin Voltage is controlled so as not to exceed the GATE clamp voltage. This prevents over-voltage between Gate-Source of FET Q1 that may destroy the FET.

The GATE pin voltage in the GATE pin "H" state varies depending on the  $V_{DD}$  pin voltage.

- (a)  $V_{DD}$  pin Voltage < GATE clamp Voltage + (12V GATE "H" level Voltage) GATE "H" Voltage =  $V_{DD}$  - (12V - GATE "H" level Voltage)

- (b) V<sub>DD</sub> pin Voltage > GATE clamp Voltage + (12V GATE "H" level Voltage) GATE "H" Voltage = GATE clamp Voltage

# ■OPERATIONAL EXPLANATION

#### <UVLO>

If the  $V_{DD}$  pin voltage drops below the UVLO detect voltage ( $V_{UVLO}$ ), the GATE pin voltage is forcibly put in the "L" state to prevent IC malfunctioning. When the  $V_{DD}$  pin voltage rises above the Start-up Threshold Voltage, the UVLO state is released and normal operation starts. The IC quiescent current is held below 20µA in the UVLO state, enabling reduction of standby power and the need for high resistances for  $R_{VDD}$ 1, 2.

When a LED short circuits, the  $V_{DD}$  pin voltage drops below the UVLO detect voltage, and thus the UVLO function can suppress destruction of external components.

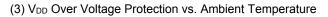

#### <V<sub>DD</sub> Over Voltage Protection>

This prevents IC destruction caused by  $V_{DD}$  pin over-voltage. When the  $V_{DD}$  pin voltage rises above the  $V_{DD}$  Over-Voltage Protection voltage, the GATE pin voltage is forcibly kept in the "L" state to suppress any further increases of the  $V_{DD}$  pin voltage.

#### <Short Circuit Protection Voltage>

This prevents peripheral component destruction in the event that excessive current flows to the sense resistance Rs due to short-circuiting of an external component or otherwise.

This function protects external components in the event that excessive current flows to the sense resistance Rs due to short-circuiting of an external component or otherwise.

When excessive current flows to the sense resistance Rs and the I<sub>SEN</sub> pin voltage rises above the Short Circuit Protection Voltage, the GATE pin voltage is forcibly latched to the "L" state. This suppresses damage to external components due to over-current.

The latched state is released and normal operation resumes when the  $V_{DD}$  pin voltage is lowered below the latch release voltage at 5.6V and then raised above the Start-up Threshold Voltage.

#### <Thermal shutdown>

To protect the IC from thermal destruction, the thermal shutdown function activates when the chip temperature reaches 170°C and forcibly puts the GATE pin voltage in the "L" state. When the chip temperature drops down to 145°C, normal operation resumes.

### NOTES ON USE

- 1) Take care that the absolute maximum ratings of external components and the IC are not exceeded.

- 2) External components and the circuit board layout have a large effect on characteristics. Test sufficiently with the actual device before use.

- Give consideration to derating when selecting external components. In particular, external components may become hot due to heat generated by LEDs and other components. Select components and design for heat radiation.

- 4) Select external components and design the test circuit board so as to satisfy applicable regulations and standards.

- 5) Torex places an importance on improving our products and their reliability. We request that users incorporate fail-safe designs and post-aging protection treatment when using Torex products in their systems.

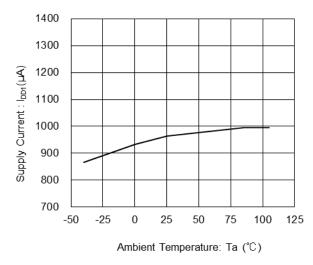

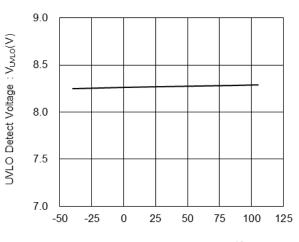

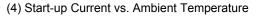

# ■TYPICAL PERFORMANCE CHARACTERISTICS

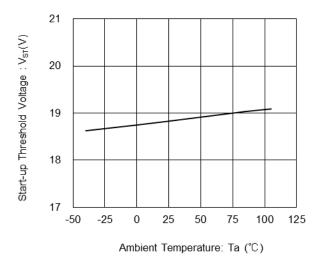

(1) Start-up Threshold Voltage vs. Ambient Temperature

(2) UVLO Detect Voltage vs. Ambient Temperature

Ambient Temperature: Ta (°C)

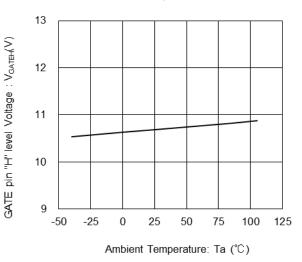

(6) GATE pin "H" level Voltage vs. Ambient Temperature

# ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

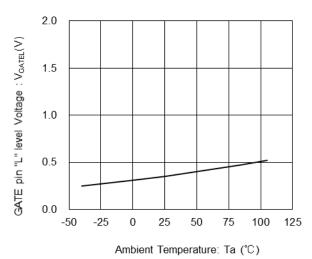

(7) GATE pin "L" level Voltage vs. Ambient Temperature

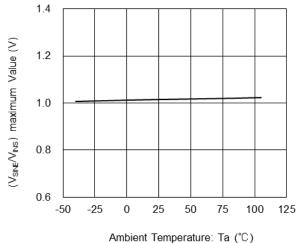

(8) GATE pin clamp Voltage vs. Ambient Temperature

Ambient Temperature: Ta (°C)

(12) Short Circuit Protection Voltage vs. Ambient Temperature

# ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

(15) ZVS CV Threshold Voltage vs. Ambient Temperature (16) ZVS Over Voltage Threshold Voltage vs. Ambient Temperature

# ■ PACKAGING INFORMATION

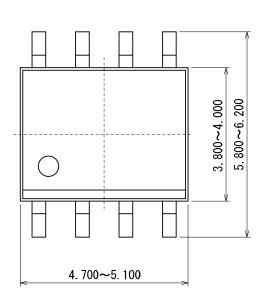

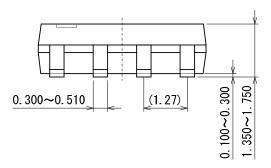

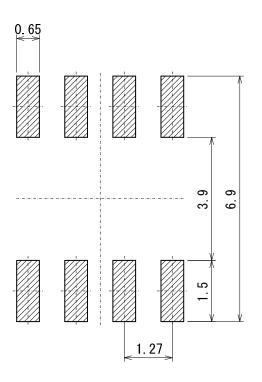

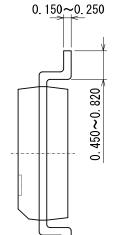

●SOP-8D (unit:mm)

SOP-8DReference Pattern Layout (unit:mm)

### ■MARKING RULE

#### SOP-8D

#### $\textcircled{1}{\sim}\textcircled{6}$ represents Marking ID

|   |   | MA | RK |   |   |                |

|---|---|----|----|---|---|----------------|

| 1 | 2 | 3  | 4  | 5 | 6 | PRODUCT SERIES |

| Х | С | 9  | 4  | 0 | 4 | XC9404*****-G  |

#### $\ensuremath{\overline{\mathcal{O}}}$ represents Last digit of manufacture year

Example

| MARK | MANUFACTURE YEAR |

|------|------------------|

| 5    | Y2015            |

(8,9) represents working week at molding process

1 represents Assembly Site Code

N:Nantong Fujitsu

(1),(12) represents Batch No.

- 1. The product and product specifications contained herein are subject to change without notice to improve performance characteristics. Consult us, or our representatives before use, to confirm that the information in this datasheet is up to date.

- 2. The information in this datasheet is intended to illustrate the operation and characteristics of our products. We neither make warranties or representations with respect to the accuracy or completeness of the information contained in this datasheet nor grant any license to any intellectual property rights of ours or any third party concerning with the information in this datasheet.

- 3. Applicable export control laws and regulations should be complied and the procedures required by such laws and regulations should also be followed, when the product or any information contained in this datasheet is exported.

- 4. The product is neither intended nor warranted for use in equipment of systems which require extremely high levels of quality and/or reliability and/or a malfunction or failure which may cause loss of human life, bodily injury, serious property damage including but not limited to devices or equipment used in 1) nuclear facilities, 2) aerospace industry, 3) medical facilities, 4) automobile industry and other transportation industry and 5) safety devices and safety equipment to control combustions and explosions. Do not use the product for the above use unless agreed by us in writing in advance.

- 5. Although we make continuous efforts to improve the quality and reliability of our products; nevertheless Semiconductors are likely to fail with a certain probability. So in order to prevent personal injury and/or property damage resulting from such failure, customers are required to incorporate adequate safety measures in their designs, such as system fail safes, redundancy and fire prevention features.

- 6. Our products are not designed to be Radiation-resistant.

- 7. Please use the product listed in this datasheet within the specified ranges.

- 8. We assume no responsibility for damage or loss due to abnormal use.

- 9. All rights reserved. No part of this datasheet may be copied or reproduced unless agreed by Torex Semiconductor Ltd in writing in advance.

TOREX SEMICONDUCTOR LTD.

单击下面可查看定价,库存,交付和生命周期等信息

>>Torex Semiconductor(特瑞仕)