TOSHIBA CD process Integrated Circuit Silicon Monolithic

# TC78H670FTG

Clock-in and Serial controlled Bipolar Stepping Motor Driver

### 1. Outline

The TC78H670FTG is a two-phase bipolar stepping motor driver using a PWM

chopper which incorporate DMOS with low on-resistance in output

transistors. The clock-in decoder is built in.

Weight: 22.9 mg (typ.)

### 2. Features

- Built-in Dual H Bridges, Capable of controlling 1 bipolar stepping motor

- PWM controlled constant-current drive

- Power supply operating voltage: 2.5 V to 16.0 V

- Output current ratings: 2.0 A (max)

- Low on-resistance (High + Low side = 0.48  $\Omega$  (typ.)) MOSFET output stage

- Allows full, half, quarter, 1/8, 1/16, 1/32, 1/64, 1/128 step operation

- Built-in Sense resistor less current control architecture (Advanced Current Detection System)

- Multi error detect functions (Thermal shutdown (TSD), Over current (ISD), motor load open (OPD) and Under voltage lockout(UVLO))

- Error detection (TSD/ISD/OPD) flag output function

- Built-in VCC regulator for internal circuit

- Chopping frequency of a motor can be adjusted by external resistor

- Small QFN package with thermal pad (16pin)

Note: Please be careful about thermal conditions during using.

Note: It is possible to detect OPD only when Serial mode is selected.

1

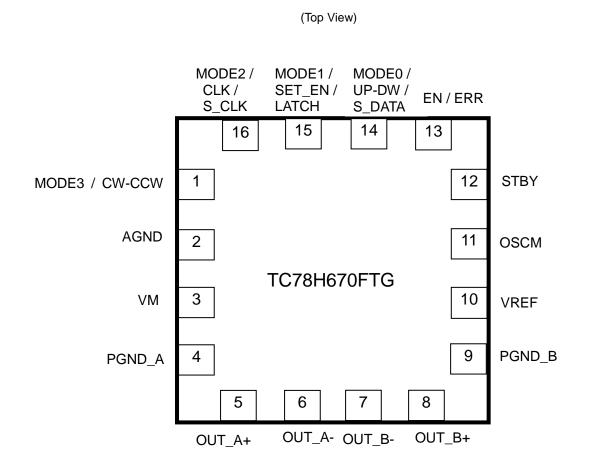

## 3. Pin Assignment

Note: Please solder the corner pads and the rear thermal pad of the QFN package, to the GND pattern of the PCB.

# 4. Pin Description

| Pin No. | STBY = Low | STBY =                    | High        | Din depaription                                                                                |  |

|---------|------------|---------------------------|-------------|------------------------------------------------------------------------------------------------|--|

| PIN NO. | SIBY = LOW | CLK-IN mode               | Serial mode | Pin description                                                                                |  |

| 1       | MODE3      |                           |             | MODE3: Step mode select pin<br>CW-CCW: Current direction setup pin                             |  |

| 2       | AGND       | ←                         | ←           | GND pin                                                                                        |  |

| 3       | VM         | $\leftarrow$              | ←           | Motor power supply input pin                                                                   |  |

| 4       | PGND_A     | ←                         | ←           | Ach Power GND pin                                                                              |  |

| 5       | OUT_A+     | $\leftarrow$              | ←           | A channel motor output(+) pin                                                                  |  |

| 6       | OUT_A-     | $\leftarrow$              | ←           | A channel motor output(-) pin                                                                  |  |

| 7       | OUT_B-     | $\leftarrow$              | ←           | B channel motor output(-) pin                                                                  |  |

| 8       | OUT_B+     | $\leftarrow$              | ←           | B channel motor output(+) pin                                                                  |  |

| 9       | PGND_B     | ←                         | ←           | Bch Power GND pin                                                                              |  |

| 10      | VREF       | ← ←                       |             | Current threshold reference pin                                                                |  |

| 11      | OSCM       | $\leftarrow$ $\leftarrow$ |             | Internal oscillator frequency setting pin                                                      |  |

| 12      | STBY       | $\leftarrow$              | ←           | Standby pin                                                                                    |  |

| 13      | EN/ERR     | ←                         | ←           | Enable(Motor output ON/OFF) pin /<br>Error detection flag output pin                           |  |

| 14      | MODE0      | UP-DW                     | S_DATA      | MODE0: Step mode select pin<br>UP-DW: Step mode setting pin<br>S_DATA: Serial data input pin   |  |

| 15      | MODE1      | SET_EN                    | LATCH       | MODE1: Step mode select pin<br>SET_EN: Step mode setting enable pin<br>LATCH: Latch enable pin |  |

| 16      | MODE2      | CLK                       | S_CLK       | MODE2: Step mode select pin<br>CLK: Step Clock input pin<br>S_CLK: Serial clock input pin      |  |

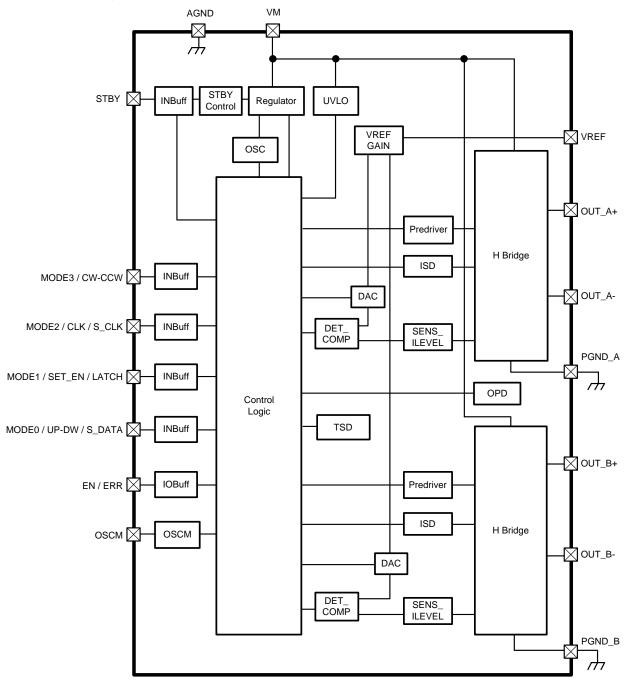

# 5. Block Diagram

- Note: Some of the functional blocks, circuits, or constants in the block diagram may be omitted or simplified for explanatory purpose.

- Note: All the grounding wires should be solid patterns and be externally terminated at only one point. Also, a grounding method should be considered for efficient heat dissipation. Careful attention should be paid to the layout of the output, VM and GND traces, to avoid short circuits across output pins or to the power supply or ground. If such a short circuit occurs, the device may be permanently damaged. Also, the utmost care should be taken for pattern designing and implementation of the device since it has power supply pins (VM, AGND, PGND\_x, OUT\_x+ and OUT\_x- (x = A or B)) through which a particularly large current may run. If these pins are wired incorrectly, an operation error may occur or the device may be destroyed. The logic input pins must also be wired correctly. Otherwise, the device may be damaged owing to a current running through the IC that is larger than the specified current. Careful attention should be paid to design patterns and mounting.

# 6. Input / Output Equivalent Circuit

| Pin name                                                                                          | Equivalent circuit                                                                                |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| MODE3 / CW-CCW<br>MODE2 / CLK / S_CLK<br>MODE1 / SET_EN / LATCH<br>MODE0 / UP-DW / S_DATA<br>STBY | MODE3 / CW-CCW<br>MODE2 / CLK / S_CLK<br>MODE1 / SET_EN / LATCH<br>MODE0 / UP-DW / S_DATA<br>STBY |

| EN / ERR                                                                                          |                                                                                                   |

| VREF                                                                                              | VREF                                                                                              |

| OSCM                                                                                              | I SCM                                                                                             |

| OUT_A+<br>OUT_A-<br>OUT_B+<br>OUT_B-<br>PGND_A<br>PGND_B                                          | VM<br>VM<br>OUT_x+<br>OUT_x-<br>OUT_x-<br>OUT_x-<br>A or B<br>PGND_x                              |

Note: The equivalent circuit diagrams may be simplified for explanatory purposes.

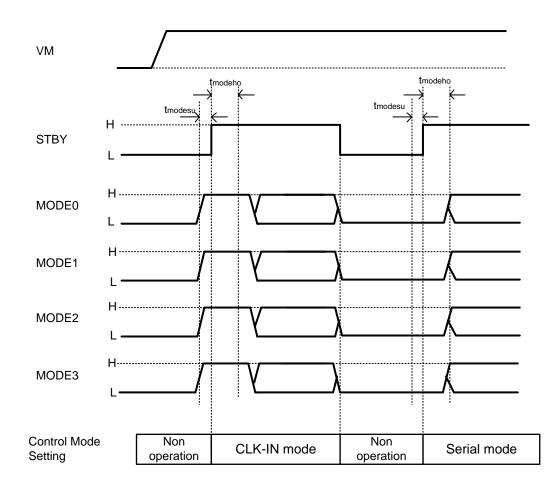

# 7. Control Mode Select Function

The MODE0-3 pins set Serial mode or CLK-IN mode. The control mode is set up by the input state of the MODE0-3 pins after releasing standby mode.

| MODE3<br>pin input   | MODE2<br>pin input | MODE1<br>pin input | MODE0<br>pin input | Function    |

|----------------------|--------------------|--------------------|--------------------|-------------|

| L                    | L                  | L                  | L                  | Serial mode |

| Other than the above |                    |                    | CLK-IN mode        |             |

| Characteristics                | Symbol              | Test condition | Min | Тур. | Max | Unit |

|--------------------------------|---------------------|----------------|-----|------|-----|------|

| Mode setting<br>Setup time     | t <sub>modesu</sub> | To STBY edge   | 1   | _    | _   | μs   |

| Mode setting<br>Data hold time | t <sub>modeho</sub> | From STBY edge | 100 |      |     | μs   |

# 8. Functional Description 1 (for CLK-IN mode)

### 8.1. CLK Function

Each up-edge of the CLK signal will shift the motor's electrical angle per step.

| CLK pin input | Function                                        |

|---------------|-------------------------------------------------|

| Up-edge       | Shifts the electrical angle per step            |

| Down-edge     | (State of the electrical angle does not change) |

### 8.2. ENABLE Function

The EN pin controls the ON and OFF of the stepping motor outputs. Motor operation starts and stops by setting H and L to the EN pin.

(When the EN pin is set to L (OFF), all of the MOSFETs turn off and become high impedance (hereafter, Hi-Z).) Setting the EN pin to L, and avoiding the motor to operate during VM power-on and power-off (i.e., outside of the operating voltage range) is recommended. Then, switch the EN pin to H after the VM reaches the target voltage and becomes stable. The EN pin should input High level through a resistor.

| EN pin input | Function                   |

|--------------|----------------------------|

| L            | OFF (Hi-Z)                 |

| Н            | ON (Normal operation mode) |

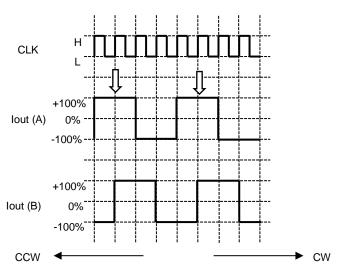

### 8.3. CW-CCW Function

CW-CCW pin controls the rotation direction of the motor.

| CW-CCW pin input | Function                          |

|------------------|-----------------------------------|

| L                | Counter clockwise operation (CCW) |

| Н                | Clockwise operation (CW)          |

7

### 8.4. Step Resolution Select Function

Step resolution is set up. TC78H670FTG has the two modes, Variable Mode and Fixed Mode. These modes are set up by the input state of MODE0-3 pins after releasing standby mode.

Variable Mode: Variable mode can be started with Full step resolution and changed step resolution during motor operating

Fixed Mode: Fixed mode can be started with the mode user selected and continued it during motor operating

| MODE3<br>pin input | MODE2<br>pin input | MODE1<br>pin input | MODE0<br>pin input | Mode          | Function                                                                                         |

|--------------------|--------------------|--------------------|--------------------|---------------|--------------------------------------------------------------------------------------------------|

| L                  | L                  | L                  | Н                  |               | Full step resolution <-> 1/2 step resolution<br>(2-phase excitation) (1-2-phase excitation)      |

| L                  | L                  | Н                  | L                  |               | Full step resolution <-> 1/4 step resolution<br>(2-phase excitation) (W1-2-phase excitation)     |

| L                  | L                  | Н                  | Н                  |               | Full step resolution <-> 1/8 step resolution<br>(2-phase excitation) (2W1-2-phase excitation)    |

| L                  | Н                  | L                  | L                  | Variable Mode | Full step resolution <-> 1/16 step resolution<br>(2-phase excitation) (4W1-2-phase excitation)   |

| L                  | Н                  | L                  | Н                  |               | Full step resolution <-> 1/32 step resolution<br>(2-phase excitation) (8W1-2-phase excitation)   |

| L                  | н                  | Н                  | L                  |               | Full step resolution <-> 1/64 step resolution<br>(2-phase excitation) (16W1-2-phase excitation)  |

| L                  | н                  | Н                  | Н                  |               | Full step resolution <-> 1/128 step resolution<br>(2-phase excitation) (32W1-2-phase excitation) |

| Н                  | L                  | L                  | L                  |               | Full step resolution (2-phase excitation)                                                        |

| Н                  | L                  | L                  | Н                  |               | 1/2 step resolution (1-2-phase excitation)                                                       |

| Н                  | L                  | Н                  | L                  |               | 1/4 step resolution (W1-2-phase excitation)                                                      |

| Н                  | L                  | Н                  | Н                  | Fixed Mede    | 1/8 step resolution (2W1-2-phase excitation)                                                     |

| Н                  | Н                  | L                  | L                  | Fixed Mode    | 1/16 step resolution (4W1-2-phase excitation)                                                    |

| Н                  | Н                  | L                  | Н                  |               | 1/32 step resolution (8W1-2-phase excitation)                                                    |

| Н                  | Н                  | Н                  | L                  |               | 1/64 step resolution (16W1-2-phase excitation)                                                   |

| Н                  | Н                  | Н                  | Н                  | <u> </u>      | 1/128 step resolution (32W1-2-phase excitation)                                                  |

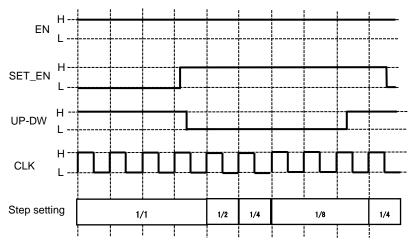

When Step mode is changed during operating, Step resolution can be set by SET\_EN pin and UP-DW pin. Step mode is changed synchronously with Step Clock.

| SET_EN pin input | Function                       |

|------------------|--------------------------------|

| L                | Setting step mode is invalid   |

| Н                | Setting step mode is available |

| UP-DW pin input | Function                            |

|-----------------|-------------------------------------|

| L               | Change step mode to high resolution |

| Н               | Change step mode to Low resolution  |

[Example: Full Step <-> 1/8 Step]

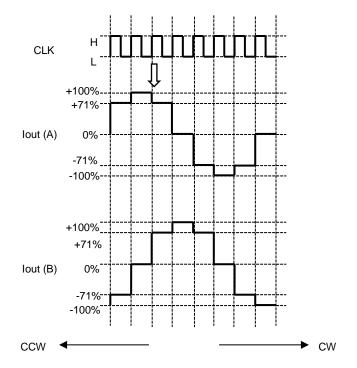

### 8.5. Timing Chart of Step Resolution Setting and Initial Angle

The arrow in the below figures indicates the timing of initial angle.

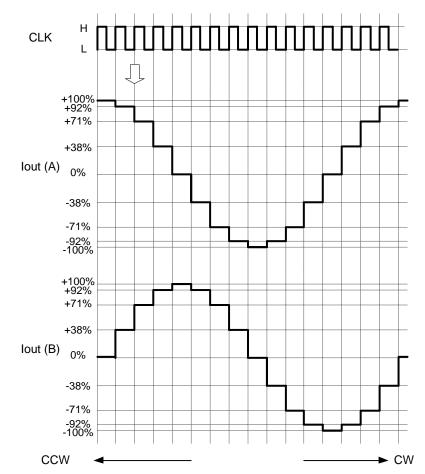

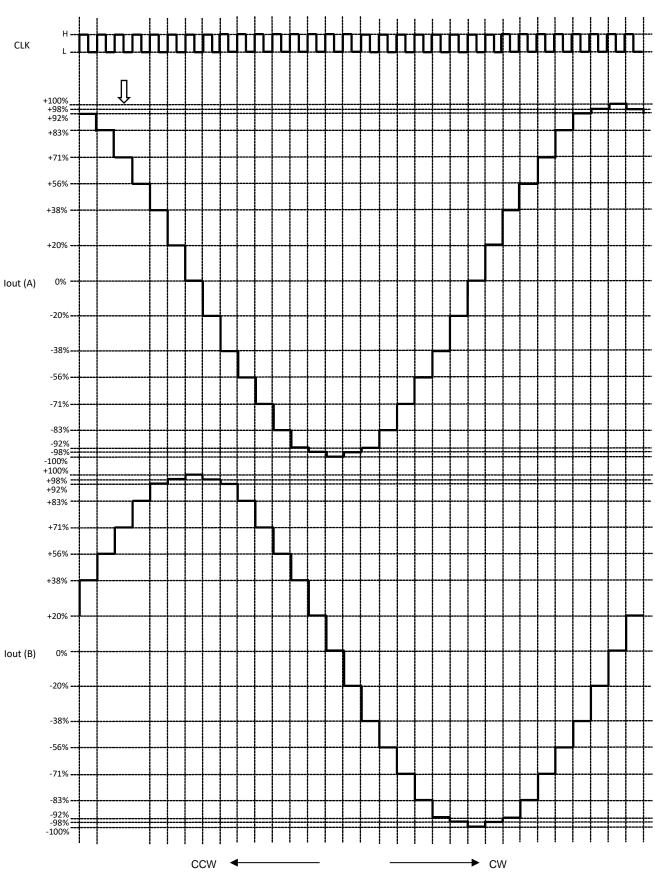

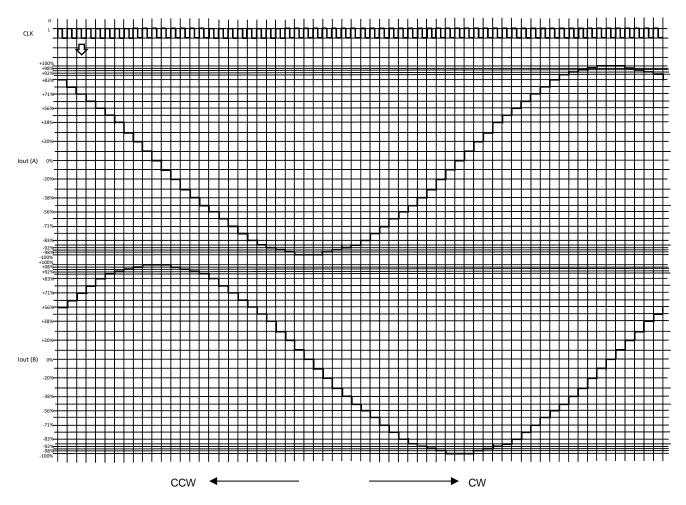

[Full step resolution]

[1/2 step resolution]

[1/4 step resolution]

#### [1/8 step resolution]

#### [1/16 step resolution]

Note: Timing charts may be simplified for explanatory purpose.

13

### 8.6. Step Setting and Current Percentage

| Current (%) | 1/1 | 1/2 | 1/4 | 1/8 | 1/16 | 1/32 | 1/64     | 1/128 |

|-------------|-----|-----|-----|-----|------|------|----------|-------|

| 100%        | 0   | 0   | 0   | 0   | 0    | 0    | 0        | 0     |

| 99%         |     |     |     |     | 0    | 0    | 0        | 0     |

| 98%         |     |     |     | 0   | 0    | 0    | 0        | 0     |

| 97%         |     |     |     |     | 0    | 0    | 0        | 0     |

| 96%         |     |     |     | 0   | 0    | 0    | 0        | 0     |

| 95%         |     |     |     |     |      |      | 0        | 0     |

| 94%         |     |     |     |     |      | 0    | 0        | 0     |

| 93%         |     |     |     |     |      |      | 0        | 0     |

| 92%         |     |     |     |     |      | 0    | 0        | 0     |

| 91%         |     |     |     |     |      |      | 0        | 0     |

| 90%         |     |     |     |     | 0    | 0    | 0        | 0     |

| 89%         |     |     |     |     |      |      | 0        | 0     |

| 88%         |     |     |     |     |      | 0    | 0        | 0     |

| 87%         |     |     |     |     |      |      | 0        | 0     |

| 86%         |     |     |     |     |      | 0    | 0        | 0     |

| 85%         |     |     |     |     |      |      |          | 0     |

| 84%         |     |     |     |     |      |      | 0        | 0     |

| 83%         |     |     |     | 0   | 0    | 0    | 0        | 0     |

| 82%         |     |     |     |     |      |      | 0        | 0     |

|             |     |     |     |     |      |      |          | 0     |

| 81%         |     |     |     |     |      | 0    | 0        | 0     |

| 80%         |     |     |     |     |      |      | 0        | 0     |

| 79%         |     |     |     |     |      |      | Ű        | 0     |

| 78%         |     |     |     |     | 0    | 0    | 0        | 0     |

| 77%         |     |     |     |     | 0    | 0    | 0        | 0     |

| 76%         |     |     |     |     |      |      | 0        | 0     |

| 75%         |     |     |     |     |      | 0    | <u>^</u> |       |

| 74%         |     |     |     |     |      | 0    | 0        | 0     |

| 73%         |     |     |     |     |      |      |          | 0     |

| 72%         |     |     |     |     |      |      | 0        | 0     |

| 71%         |     | 0   | 0   | 0   | 0    | 0    | 0        | 0     |

| 70%         |     |     |     |     |      |      |          | 0     |

| 69%         |     |     |     |     |      |      | 0        | 0     |

| 68%         |     |     |     |     |      |      |          | 0     |

| 67%         |     |     |     |     |      | 0    | 0        | 0     |

| 66%         |     |     |     |     |      |      |          | 0     |

| 65%         |     |     |     |     |      |      | 0        | 0     |

| 64%         |     |     |     |     |      |      |          | 0     |

| 63%         |     |     |     |     | 0    | 0    | 0        | 0     |

| 62%         |     |     |     |     |      |      | 0        | 0     |

| 61%         |     |     |     |     |      |      |          | 0     |

| 60%         |     |     |     |     |      | 0    | 0        | 0     |

| 59%         |     |     |     |     |      |      |          | 0     |

| 58%         |     |     |     |     |      |      | 0        | 0     |

| 57%         |     |     |     |     |      |      |          | 0     |

| 56%         |     |     |     | 0   | 0    | 0    | 0        | 0     |

| 55%         |     |     |     |     |      |      |          | 0     |

| 53%         |     |     |     |     |      |      | 0        | 0     |

| 52%         |     |     |     |     |      |      |          | 0     |

# TC78H670FTG

| Current (%) | 1/1 | 1/2 | 1/4 | 1/8 | 1/16 | 1/32 | 1/64 | 1/128 |

|-------------|-----|-----|-----|-----|------|------|------|-------|

| 51%         |     |     |     |     |      | 0    | 0    | 0     |

| 50%         |     |     |     |     |      |      |      | 0     |

| 49%         |     |     |     |     |      |      | 0    | 0     |

| 48%         |     |     |     |     |      |      |      | 0     |

| 47%         |     |     |     |     | 0    | 0    | 0    | 0     |

| 46%         |     |     |     |     |      |      |      | 0     |

| 45%         |     |     |     |     |      |      | 0    | 0     |

| 44%         |     |     |     |     |      |      |      | 0     |

| 43%         |     |     |     |     |      | 0    | 0    | 0     |

| 42%         |     |     |     |     |      |      |      | 0     |

| 41%         |     |     |     |     |      |      | 0    | 0     |

| 39%         |     |     |     |     |      |      |      | 0     |

| 38%         |     |     | 0   | 0   | 0    | 0    | 0    | 0     |

| 37%         |     |     |     |     |      |      |      | 0     |

| 36%         |     |     |     |     |      |      | 0    | 0     |

| 35%         |     |     |     |     |      |      |      | 0     |

| 34%         |     |     |     |     |      | 0    | 0    | 0     |

| 33%         |     |     |     |     |      |      |      | 0     |

| 31%         |     |     |     |     |      |      | 0    | 0     |

| 30%         |     |     |     |     |      |      |      | 0     |

| 29%         |     |     |     |     | 0    | 0    | 0    | 0     |

| 28%         |     |     |     |     |      |      |      | 0     |

| 27%         |     |     |     |     |      |      | 0    | 0     |

| 25%         |     |     |     |     |      | 0    |      | 0     |

| 24%         |     |     |     |     |      |      | 0    | 0     |

| 23%         |     |     |     |     |      |      |      | 0     |

| 22%         |     |     |     |     |      |      | 0    | 0     |

| 21%         |     |     |     |     |      |      |      | 0     |

| 20%         |     |     |     | 0   | 0    | 0    | 0    | 0     |

| 18%         |     |     |     |     |      |      |      | 0     |

| 17%         |     |     |     |     |      |      | 0    | 0     |

| 16%         |     |     |     |     |      |      |      | 0     |

| 15%         |     |     |     |     |      | 0    | 0    | 0     |

| 13%         |     |     |     |     |      |      |      | 0     |

| 12%         |     |     |     |     |      |      | 0    | 0     |

| 11%         |     |     |     |     |      |      |      | 0     |

| 10%         |     |     |     |     | 0    | 0    | 0    | 0     |

| 9%          |     |     |     |     |      |      |      | 0     |

| 7%          |     |     |     |     |      |      | 0    | 0     |

| 6%          |     |     |     |     |      |      |      | 0     |

| 5%          |     |     |     |     |      | 0    | 0    | 0     |

| 4%          |     |     |     |     |      |      |      | 0     |

| 2%          |     |     |     |     |      |      | 0    | 0     |

| 1%          |     |     |     |     |      |      |      | 0     |

| 0%          |     | 0   | 0   | 0   | 0    | 0    | 0    | 0     |

# 8.7. Step Resolution and Set Current

| STEP |            | 28       | 1/         | 64       | 1/         | 32       | 1/         | 16       | 1.         | /8       | 1.         | /4       | 1          | /2       | F   | ull |

|------|------------|----------|------------|----------|------------|----------|------------|----------|------------|----------|------------|----------|------------|----------|-----|-----|

|      | Ach        | Bch      | Ach | Bch |

| θ0   | (%)<br>100 | (%)<br>0 | (%) | (%) |

| θ1   | 100        | 1        | 100        | •        | 100        | •        | 100        | Ŭ        | 100        | Ű        | 100        | Ŭ        | 100        | Ű        |     |     |

| θ2   | 100        | 2        | 100        | 2        |            |          |            |          |            |          |            |          |            |          |     |     |

| θ3   | 100        | 4        |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ4   | 100        | 5        | 100        | 5        | 100        | 5        |            |          |            |          |            |          |            |          |     |     |

| θ5   | 100        | 6        |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| 06   | 100        | 7        | 100        | 7        |            |          |            |          |            |          |            |          |            |          |     |     |

| θ7   | 100        | 9        |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ8   | 100        | 10       | 100        | 10       | 100        | 10       | 100        | 10       |            |          |            |          |            |          |     |     |

| 09   | 99         | 11       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ10  | 99         | 12       | 99         | 12       |            |          |            |          |            |          |            |          |            |          |     |     |

| θ11  | 99         | 13       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ12  | 99         | 15       | 99         | 15       | 99         | 15       |            |          |            |          |            |          |            |          |     |     |

| θ13  | 99         | 16       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ14  | 99         | 17       | 99         | 17       |            |          |            |          |            |          |            |          |            |          |     |     |

| θ15  | 98         | 18       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ16  | 98         | 20       | 98         | 20       | 98         | 20       | 98         | 20       | 98         | 20       |            |          |            |          |     |     |

| θ17  | 98         | 21       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ18  | 98         | 22       | 98         | 22       |            |          |            |          |            |          |            |          |            |          |     |     |

| θ19  | 97         | 23       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ20  | 97         | 24       | 97         | 24       | 97         | 24       |            |          |            |          |            |          |            |          |     |     |

| θ21  | 97         | 25       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ22  | 96         | 27       | 96         | 27       |            |          |            |          |            |          |            |          |            |          |     |     |

| θ23  | 96         | 28       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ24  | 96         | 29       | 96         | 29       | 96         | 29       | 96         | 29       |            |          |            |          |            |          |     |     |

| θ25  | 95         | 30       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ26  | 95         | 31       | 95         | 31       |            |          |            |          |            |          |            |          |            |          |     |     |

| θ27  | 95         | 33       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ28  | 94         | 34       | 94         | 34       | 94         | 34       |            |          |            |          |            |          |            |          |     |     |

| θ29  | 94         | 35       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ30  | 93         | 36       | 93         | 36       |            |          |            |          |            |          |            |          |            |          |     |     |

| θ31  | 93         | 37       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ32  | 92         | 38       | 92         | 38       | 92         | 38       | 92         | 38       | 92         | 38       | 92         | 38       |            |          |     |     |

| θ33  | 92         | 39       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ34  | 91         | 41       | 91         | 41       |            |          |            |          |            |          |            |          |            |          |     |     |

| θ35  | 91         | 42       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ36  | 90         | 43       | 90         | 43       | 90         | 43       |            |          |            |          |            |          |            |          |     |     |

| θ37  | 90         | 44       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ38  | 89         | 45       | 89         | 45       |            |          |            |          |            |          |            |          |            |          |     |     |

| θ39  | 89         | 46       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

| θ40  | 88         | 47       | 88         | 47       | 88         | 47       | 88         | 47       |            |          |            |          |            |          |     |     |

| θ41  | 88         | 48       |            |          |            |          |            |          |            |          |            |          |            |          |     |     |

# TC78H670FTG

| STEP            | 1/1       | 28        | 1/        | 64        | 1/  | 32  | 1/  | 16  | 1   | /8  | 1   | /4  | 1   | /2  | F   | ull       |

|-----------------|-----------|-----------|-----------|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----------|

| _               | Ach       | Bch       | Ach       | Bch       | Ach | Bch | Ach | Bch | Ach | Bch | Ach | Bch | Ach | Bch | Ach | Bch       |

| θ42             | (%)<br>87 | (%)<br>49 | (%)<br>87 | (%)<br>49 | (%) | (%) | (%) | (%) | (%) | (%) | (%) | (%) | (%) | (%) | (%) | (%)       |

| 043             | 86        | 50        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

| 044             | 86        | 51        | 86        | 51        | 86  | 51  |     |     |     |     |     |     |     |     |     |           |

| θ45             | 85        | 52        |           |           |     | -   |     |     |     |     |     |     |     |     |     |           |

| θ46             | 84        | 53        | 84        | 53        |     |     |     |     |     |     |     |     |     |     |     |           |

| θ47             | 84        | 55        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

| θ48             | 83        | 56        | 83        | 56        | 83  | 56  | 83  | 56  | 83  | 56  |     |     |     |     |     |           |

| θ49             | 82        | 57        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

| θ50             | 82        | 58        | 82        | 58        |     |     |     |     |     |     |     |     |     |     |     |           |

| θ51             | 81        | 59        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

| θ52             | 80        | 60        | 80        | 60        | 80  | 60  |     |     |     |     |     |     |     |     |     |           |

| θ53             | 80        | 61        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

| θ54             | 79        | 62        | 79        | 62        |     |     |     |     |     |     |     |     |     |     |     |           |

| θ55             | 78        | 62        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

| θ56             | 77        | 63        | 77        | 63        | 77  | 63  | 77  | 63  |     |     |     |     |     |     |     |           |

| θ57             | 77        | 64        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

| θ58             | 76        | 65        | 76        | 65        |     |     |     |     |     |     |     |     |     |     |     |           |

| θ59             | 75        | 66        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

| θ60             | 74        | 67        | 74        | 67        | 74  | 67  |     |     |     |     |     |     |     |     |     |           |

| <del>0</del> 61 | 73        | 68        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

| θ62             | 72        | 69        | 72        | 69        |     |     |     |     |     |     |     |     |     |     |     |           |

| θ63             | 72        | 70        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

| θ64             | 71        | 71        | 71        | 71        | 71  | 71  | 71  | 71  | 71  | 71  | 71  | 71  | 71  | 71  | 100 | 100       |

| θ65             | 70        | 72        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

| <del>0</del> 66 | 69        | 72        | 69        | 72        |     |     |     |     |     |     |     |     |     |     |     |           |

| 067             | 68        | 73        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

| <del>0</del> 68 | 67        | 74        | 67        | 74        | 67  | 74  |     |     |     |     |     |     |     |     |     |           |

| 069             | 66        | 75        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

| θ70             | 65        | 76        | 65        | 76        |     |     |     |     |     |     |     |     |     |     |     |           |

| θ71             | 64        | 77        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

| θ72             | 63        | 77        | 63        | 77        | 63  | 77  | 63  | 77  |     |     |     |     |     |     |     |           |

| θ73             | 62        | 78        |           | 70        |     |     |     |     |     |     |     |     |     |     |     |           |

| θ74<br>075      | 62        | 79<br>80  | 62        | 79        |     |     |     |     |     |     |     |     |     |     |     |           |

| θ75<br>976      | 61<br>60  | 80<br>80  | 60        | 00        | 60  | 00  |     |     |     |     |     |     |     |     |     |           |

| θ76<br>977      | 60<br>50  | 80<br>81  | 60        | 80        | 60  | 80  |     |     |     |     |     |     |     |     |     |           |

| θ77<br>θ78      | 59<br>58  | 81<br>82  | 58        | 82        |     |     |     |     |     |     |     |     |     |     |     |           |

| θ78<br>θ79      | 58<br>57  | 82<br>82  | 50        | 02        |     |     |     |     |     |     |     |     |     |     |     |           |

| θ79<br>θ80      | 57<br>56  | 83        | 56        | 83        | 56  | 83  | 56  | 83  | 56  | 83  |     |     |     |     |     |           |

| θ80<br>θ81      | 55        | 84        | 50        | 00        | 50  | 03  | 50  | 03  | 50  | 03  |     |     |     |     |     |           |

| 001             | 53        | 84        | 53        | 84        |     |     |     |     |     |     |     |     |     |     |     |           |

| 002             | 52        | 85        |           | 04        |     |     |     |     |     |     |     |     |     |     |     |           |

| θ84             | 52        | 86        | 51        | 86        | 51  | 86  |     |     |     |     |     |     |     |     |     | <b>  </b> |

| θ85             | 50        | 86        |           | 00        |     | 00  |     |     |     |     |     |     |     |     |     | <b>  </b> |

| 000             | 50        | 50        |           |           |     |     |     |     |     |     |     |     |     |     |     |           |

# TC78H670FTG

| STEP            | 1/1       | 28        | 1/        | 64        | 1/  | 32  | 1/  | 16  | 1,  | /8  | 1,  | /4  | 1   | /2  | F   | ull |

|-----------------|-----------|-----------|-----------|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| _               | Ach       | Bch       | Ach       | Bch       | Ach | Bch | Ach | Bch | Ach | Bch | Ach | Bch | Ach | Bch | Ach | Bch |

| 086             | (%)<br>49 | (%)<br>87 | (%)<br>49 | (%)<br>87 | (%) | (%) | (%) | (%) | (%) | (%) | (%) | (%) | (%) | (%) | (%) | (%) |

| 087             | 48        | 88        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| 088             | 47        | 88        | 47        | 88        | 47  | 88  | 47  | 88  |     |     |     |     |     |     |     |     |

| 089             | 46        | 89        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| 090             | 45        | 89        | 45        | 89        |     |     |     |     |     |     |     |     |     |     |     |     |

| <del>0</del> 91 | 44        | 90        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ92             | 43        | 90        | 43        | 90        | 43  | 90  |     |     |     |     |     |     |     |     |     |     |

| θ93             | 42        | 91        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ94             | 41        | 91        | 41        | 91        |     |     |     |     |     |     |     |     |     |     |     |     |

| θ95             | 39        | 92        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| 096             | 38        | 92        | 38        | 92        | 38  | 92  | 38  | 92  | 38  | 92  | 38  | 92  |     |     |     |     |

| θ97             | 37        | 93        |           |           |     | L   |     |     |     |     | L   |     |     |     |     |     |

| <del>0</del> 98 | 36        | 93        | 36        | 93        |     |     |     |     |     |     |     |     |     |     |     |     |

| 099             | 35        | 94        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ100            | 34        | 94        | 34        | 94        | 34  | 94  |     |     |     |     |     |     |     |     |     |     |

| θ101            | 33        | 95        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ102            | 31        | 95        | 31        | 95        |     |     |     |     |     |     |     |     |     |     |     |     |

| θ103            | 30        | 95        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ104            | 29        | 96        | 29        | 96        | 29  | 96  | 29  | 96  |     |     |     |     |     |     |     |     |

| θ105            | 28        | 96        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ106            | 27        | 96        | 27        | 96        |     |     |     |     |     |     |     |     |     |     |     |     |

| θ107            | 25        | 97        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ108            | 24        | 97        | 24        | 97        | 24  | 97  |     |     |     |     |     |     |     |     |     |     |

| θ109            | 23        | 97        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ110            | 22        | 98        | 22        | 98        |     |     |     |     |     |     |     |     |     |     |     |     |

| θ111            | 21        | 98        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ112            | 20        | 98        | 20        | 98        | 20  | 98  | 20  | 98  | 20  | 98  |     |     |     |     |     |     |

| θ113            | 18        | 98        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ114            | 17        | 99        | 17        | 99        |     |     |     |     |     |     |     |     |     |     |     |     |

| θ115            | 16        | 99        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ116            | 15        | 99        | 15        | 99        | 15  | 99  |     |     |     |     |     |     |     |     |     |     |

| θ117            | 13        | 99        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ118            | 12        | 99        | 12        | 99        |     |     |     |     |     |     |     |     |     |     |     |     |

| θ119            | 11        | 99        |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ120            | 10        | 100       | 10        | 100       | 10  | 100 | 10  | 100 |     |     |     |     |     |     |     |     |

| θ121            | 9         | 100       |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ122            | 7         | 100       | 7         | 100       |     |     |     |     |     |     |     |     |     |     |     |     |

| θ123            | 6         | 100       |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ124            | 5         | 100       | 5         | 100       | 5   | 100 |     |     |     |     |     |     |     |     |     |     |

| θ125            | 4         | 100       |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ126            | 2         | 100       | 2         | 100       |     |     |     |     |     |     |     |     |     |     |     |     |

| θ127            | 1         | 100       |           |           |     |     |     |     |     |     |     |     |     |     |     |     |

| θ128            | 0         | 100       | 0         | 100       | 0   | 100 | 0   | 100 | 0   | 100 | 0   | 100 | 0   | 100 |     |     |

\_B0

\_B1

0

1

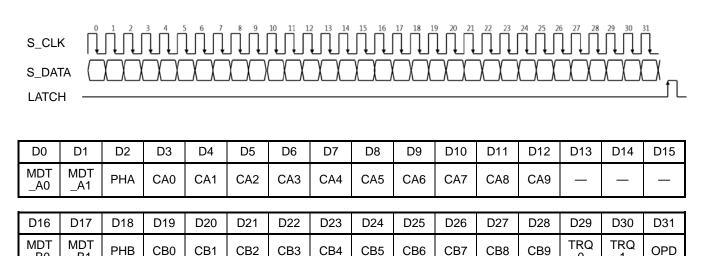

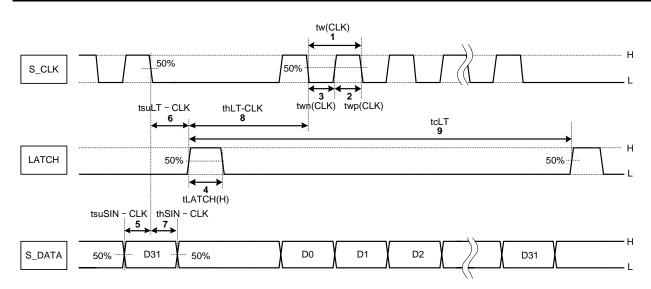

## 9. Functional Description 2 (for Serial mode)

Under the serial mode, it performs setting and motor control in the following 32-bit format. For the motor control, each current value is set in the serial setting, and the output is updated to the set current value at the timing of the LATCH signal.

Note: Every issuing a command, the current setting transfers by one step.

### 9.1. Register

The registers to use the serial control are shown below.

### 9.1.1. PHx (x = A or B)

The polality of the output current can be selected by PHx registers for each channel.

| PHx | Function                                             |           |

|-----|------------------------------------------------------|-----------|

| L   | Setting the direction of the output current to minus | * Default |

| Н   | Setting the direction of the output current to p     | plus      |

#### 9.1.2. Cx0 to Cx9 (x = A or B)

The output of each channel's DAC for current limitation can be set by Cx0 to Cx9 registers. The relation between Setting DAC and the output current (lout) are shown below.

lout (Max) = Vref (V) ×  $\frac{Cx[9:0]}{1023}$  × Setting torque by the torque function (%)

#### 9.1.3. TRQ0 and TRQ1

The value of the motor torque can be set by TRQ0 and TRQ1 registers.

| TRQ1 | TORQ0 | Function                       |  |  |  |  |

|------|-------|--------------------------------|--|--|--|--|

| L    | L     | Torque setting: 100% * Default |  |  |  |  |

| L    | Н     | Torque setting: 75%            |  |  |  |  |

| Н    | L     | Torque setting: 50%            |  |  |  |  |

| Н    | Н     | Torque setting: 25%            |  |  |  |  |

#### 9.1.4. OPD

An ON/OFF of the open detection function of motor output pins can be switched by OPD register.

| OPD | Function                     |

|-----|------------------------------|

| L   | Open detection OFF * Default |

| Н   | Open detection ON            |

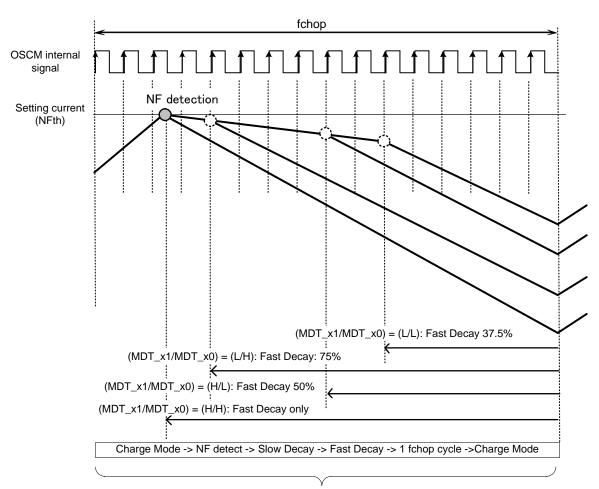

### 9.1.5. Selectable Mixed Decay Function MDT\_x0 and MDT\_x1 (x = A or B)

The Selectable Mixed Decay can adjust the current regeneration amount during the period of current regeneration. Though the Mixed Decay is determined by controlling 2 different types of Decay (Fast Decay and Slow Decay), this function enables the user to select the ratio of the Mixed Decay using MDT\_x0 and MDT\_x1 register.

| MDT_x1 | MDT_x0 | Function                                            |

|--------|--------|-----------------------------------------------------|

| L      | L      | Fast Decay: 37.5% (Fast Decay = OSCM × 6) * Default |

| L      | Н      | Fast Decay: 75%                                     |

| н      | L      | Fast Decay: 50%                                     |

| н      | Н      | Fast Decay only                                     |

1fchop cycle: OSCM × 16 clock

#### Note: x = A or B

Note: Decay control is controlled in order of Charge, Slow Decay and Fast Decay.

- Note: The blanking time(AtBLK) is also set to prevent an incorrect operation in the NF detection (the motor current reaches the set current value (NFth))..

- Note: Timing charts may be simplified for explanatory purpose.

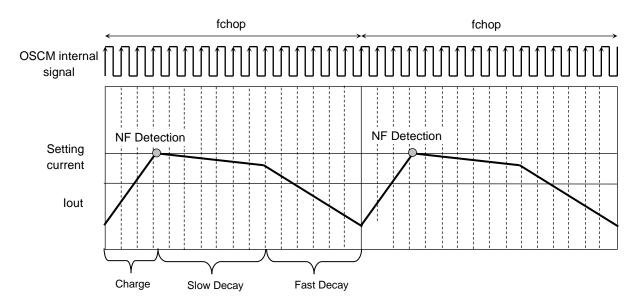

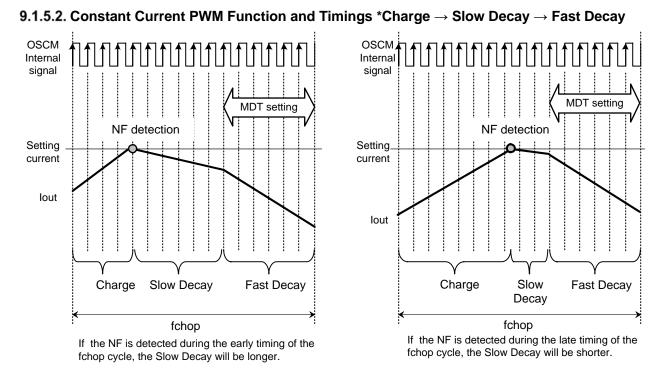

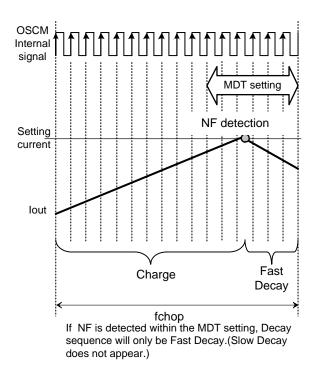

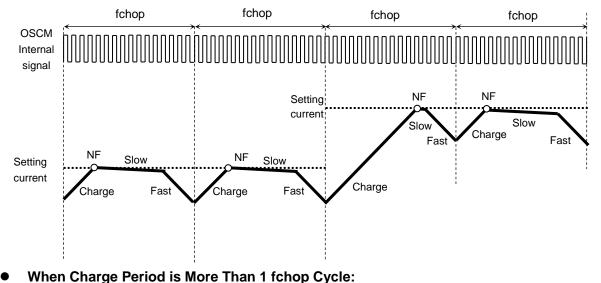

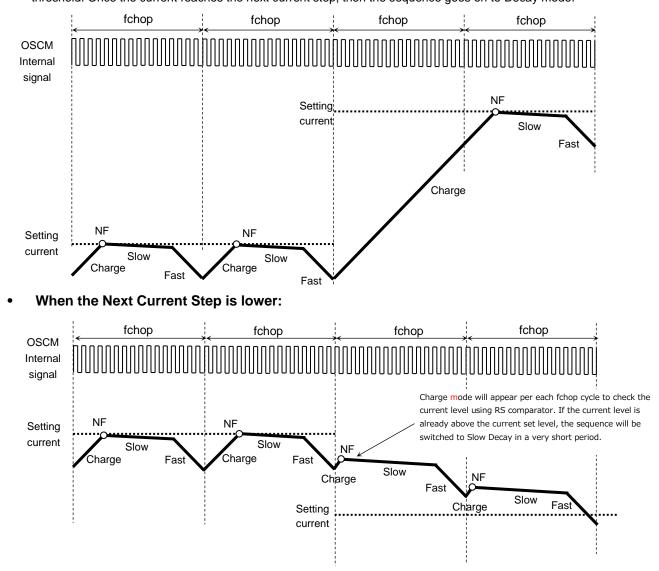

### 9.1.5.1. Mixed Decay Waveform (Current Waveform) \*Charge $\rightarrow$ Slow Decay $\rightarrow$ Fast Decay

The Charge period (the time until the motor current reaches the set current value) is determined by the operating status. Therefore the NF detection timing (the motor current reaches the set current value) with the chopping cycle (fchop) may change. If NF is detected in the early period of the fchop cycle, the Slow Decay will be longer. If NF is detected in the late period of the fchop cycle, the Slow Decay will be shorter, as shown above.

Note: The chopping cycle is determined as: fchop - (Charge + Fast Decay) = Slow Decay (Fast Decay ratio can be changed by MDT\_x0 and MDT\_x1 (x = A or B) registers setting.)

### 9.1.5.3. Mixed Decay current waveform \*Charge $\rightarrow$ Slow Decay $\rightarrow$ Fast Decay

• When the next current step is higher:

When the Charge period is longer than fchop cycle, the Charge period extends until the motor current reaches the NF threshold. Once the current reaches the next current step, then the sequence goes on to Decay mode.

### 9.2. Serial Setting Example when driving a motor

Serial setting example for motor operation is shown below. The motor operates with full step resolution by transmitting from the 1st to 4th commands repeatedly.

1st Command

| 1st Co | ommano       | k   |     |     |     |     |     |     |     |     |     |     |     |     |     |

|--------|--------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D0     | D1           | D2  | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 |

| 0      | 0            | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | 0   |

| D16    | D17          | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 |

| 0      | 0            | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | 0   |

| 2nd C  | Comman       | d   |     |     |     |     |     |     |     |     |     |     |     |     |     |

| D0     | D1           | D2  | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 |

| 0      | 0            | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | 0   |

| D16    | D17          | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 |

| 0      | 0            | 1   | 1   | 1   | 1   | 1   | 1   |     | 1   | 1   | 1   |     | 0   | 0   |     |

| 0      | 0            | I   | I   | I   | I   | I   | I   | 1   | I   | I   | I   | 1   | 0   | 0   | 0   |

| 3rd C  | omman        | d   |     |     |     |     |     |     |     |     |     |     |     |     |     |

| D0     | D1           | D2  | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 |

| 0      | 0            | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | 0   |

| D16    | D17          | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 |

| 0      | 0            | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | 0   |

|        |              |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| 4th C  | ommano<br>D1 | D2  | D3  | D4  | D5  | D6  | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 |

| DU     |              | DZ  | 03  | D4  | D5  | Do  | Di  | 00  | Da  | DIU | DII | DIZ | 013 |     | D15 |

| 0      | 0            | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | 0   |

| D16    | D17          | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 |

|        |              | -   |     |     |     |     |     |     |     |     |     |     |     |     |     |

| 0      | 0            | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | 0   |

### **10. Common Function (CLK-IN Mode and Serial Mode)**

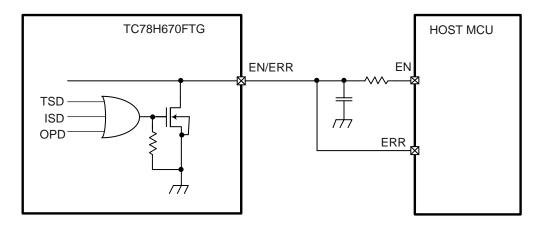

### 10.1. Error Function (Error detect flag output)

When TC78H670FTG detects some errors, ERR pin outputs low level to peripheral block.

Since ERR pin and EN pin share the function, the below peripheral circuit between TC78H670FTG and HOST MCU should be inserted. EN pin should input High level through a resistor.

In normal status, since the internal MOSFET is OFF, the level of ERR pin is equal to the EN control voltage from outside. When the error function (Thermal shutdown (TSD), Over current (ISD), or motor load open (OPD)) occurs, ERR pin will become Low (the internal MOSFET is ON). When the error detection is released by reasserting the VM power supply or setting the device to STANDBY mode, ERR pins show "normal status".

Note: This figure may be simplified for explanatory purpose.

Note: It is possible to detect OPD only when Serial mode is selected.

| ERR pin output | Function                            |

|----------------|-------------------------------------|

| H (Pull-up)    | Normal status (Normal operation)    |

| L              | Detect error status (ISD, TSD, OPD) |

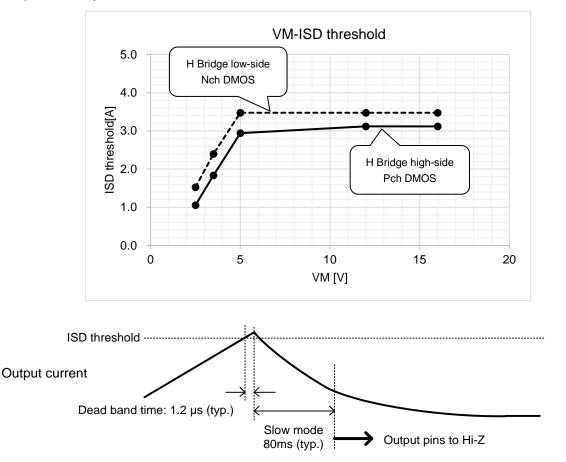

After detecting TSD detection: TC78H670FTG draws out currents of motor by Fast mode. If the output current is zerodetected or for 1ms at maximum, the output becomes Hi-Z.

After detecting ISD detection: In H Bridge high-side (Pch DMOS) detection, TC78H670FTG draws out currents of motor by Slow mode on low-side. The output after 80 ms (typ.) becomes Hi-Z. In H Bridge low-side (Nch DMOS) detection, it draws out by Slow mode on high-side.

Note: Above times are reference values, and are not guaranteed.

26

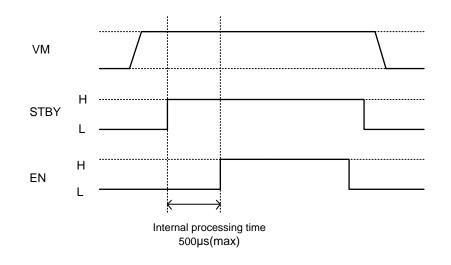

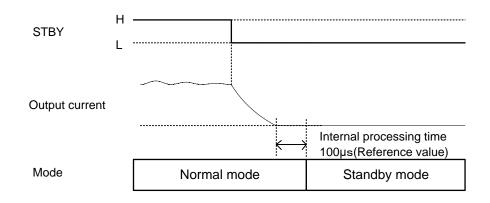

### **10.2. STANDBY Function**

It is possible to switch to Standby mode by STBY pin.

| STBY pin input | Function         | MEMO                  |  |  |  |

|----------------|------------------|-----------------------|--|--|--|

| L              | Standby mode     | Electrical angle: 45° |  |  |  |

| Н              | Normal operation | —                     |  |  |  |

Note: When STBY pin is Low, TC78H670FTG stops supplying the power to logic circuit. Therefore, Logic circuit is reset and Electrical angle and Step mode are initialized.

If the output current is zero-detected, the operation mode enters into the standby mode after 100  $\mu$ s. The mode enters into the standby mode forcedly after 1 ms(max) from STBY=L.

Note: Above times are reference values, and are not guaranteed.

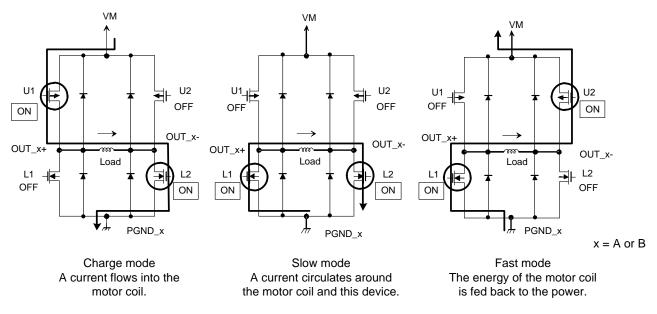

### **11. Output Transistor Function Mode**

Note: The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

### **11.1. Output Transistor Function**

| MODE   | U1  | U2  | L1  | L2  |

|--------|-----|-----|-----|-----|

| Charge | ON  | OFF | OFF | ON  |

| Slow   | OFF | OFF | ON  | ON  |

| Fast   | OFF | ON  | ON  | OFF |

Note: This table shows an example of when the current flows as indicated by the arrows in the figures shown above. If the current flows in the opposite direction, refer to the following table.

| MODE   | U1  | U2  | L1  | L2  |

|--------|-----|-----|-----|-----|

| Charge | OFF | ON  | ON  | OFF |

| Slow   | OFF | OFF | ON  | ON  |

| Fast   | ON  | OFF | OFF | ON  |

This IC controls the motor current to be constant by changing 3 modes listed above automatically

Note: To eliminate shoot-through current that flows from supply to ground due to the simultaneous conduction of high side and low side transistors in the bridge output, a dead time (100ns (Reference value)) is generated in this IC when transistors switch from on to off, or vice versa.

# 12. Calculation of the Predefined Output Current

The peak output current (Setting current value) can be set via the reference voltage (Vref), as follows:

lout (Max) =  $1.1 \times Vref(V)$

# **13. OSCM Oscillation Frequency and Chopping Frequency**

The OSCM oscillation frequency (fOSCM) and chopping frequency (fchop) can be adjusted by the external resistor (ROSC) connecting to OSCM pin.

| ROSC[kΩ] | fOSCM [kHz](typ.) | fchop[kHz](typ.) |

|----------|-------------------|------------------|

| 18       | 3290              | 206              |

| 22       | 2691              | 168              |

| 30       | 1982              | 124              |

| 39       | 1526              | 95               |

| 47       | 1266              | 79               |

| 56       | 56 1064           |                  |

| 75       | 795               | 50               |

| 91       | 656               | 41               |

If chopping frequency is raised, ripple of current will become small and wave-like reproducibility will improve.

However, the gate loss inside IC goes up and generation of heat becomes large.

By lowering chopping frequency, reduction in generation of heat is expectable. However, ripple of current may become large.

It is a standard about 70 kHz. A setup in the range of 50 kHz to 100 kHz is recommended.

# 14. Absolute Maximum Ratings (Ta = 25°C)

| Characteristics                 | Symbol  | Rating     | Unit | Remarks         |

|---------------------------------|---------|------------|------|-----------------|

| Motor output voltogo            | Vout    | 20         | V    | Outputs are OFF |

| Motor output voltage            | Vout    | 18         | V    | Outputs are ON  |

| Motor power supply (non-active) | VM      | 20         | V    | STBY pin = L    |

| Motor power supply (active)     | VIVI    | -0.4 to 18 | V    | STBY pin = H    |

| Motor output current            | lout    | 2.0        | А    | (Note 1)        |

|                                 | VIN(H)  | 6.0        | V    | _               |

| Logic input voltage             | VIN(L)  | -0.4       | V    | —               |

| ERR output pin voltage          | VLO     | 6.0        | V    | —               |

| ERR output pin inflow current   | ILO     | 6.0        | mA   | —               |

| Power dissipation               | PD      | 1.79       | W    | (Note 2)        |

| Operating temperature           | Topr    | -40 to 85  | °C   | —               |

| Storage temperature             | Tstg    | -55 to 150 | °C   | —               |

| Junction temperature            | Tj(max) | 150        | °C   | _               |

Note1: Usually, the maximum current value at the time should use 70% or less of the absolute maximum ratings for a standard on thermal rating. The maximum output current may be further limited in view of thermal considerations, depending on ambient temperature and board conditions.

Note2: When mounted on the board (JEDEC 4 layers) (Ta =25°C)

- When Ta exceeds 25°C, it is necessary to do the derating with 14.3 mW/°C.

- Ta: Ambient temperature

Topr: Ambient temperature while the IC is active

Tj: Junction temperature while the IC is active.

The maximum junction temperature is limited by the thermal shutdown (TSD) circuitry. It is advisable to keep the maximum current below a certain level so that the maximum junction temperature, Tj (MAX), will not exceed 120°C.

#### Caution) Absolute maximum ratings

The absolute maximum ratings of a semiconductor device are a set of ratings that must not be exceeded, even for a moment. Do not exceed any of these ratings. Exceeding the rating (s) may cause device breakdown, damage or deterioration, and may result in injury by explosion or combustion.

The value of even one parameter of the absolute maximum ratings should not be exceeded under any circumstances. The TC78H670FTG does not have overvoltage detection circuit. Therefore, the device is damaged if a voltage exceeding its rated maximum is applied.

All voltage ratings, including supply voltages, must always be followed. The other notes and considerations described later should also be referred to.

## 15. Operating Range (Ta = -40 to 85°C)

| Characteristics        | Symbol | Min | Тур. | Max  | Unit | Remarks  |

|------------------------|--------|-----|------|------|------|----------|

| Motor power supply     | VM     | 2.5 | -    | 16.0 | V    | -        |

| Motor output current   | lout   | -   | 1.1  | 2.0  | А    | (Note 1) |

| ERR pin output voltage | VLO    | -   | -    | 5.5  | V    | -        |

| Vref reference voltage | Vref   | 0   | -    | 1.8  | V    | -        |

Note1: Maximum current for actual usage may be limited by the operating circumstances such as operating conditions (exciting mode, operating time, and so on), ambient temperature, and heat conditions (board condition and so on).

# **16. Electrical Specifications 1**

|                                                      |           | (Ta =    | = 25°C, VM = 2.5 to 16V u                                     | nless c | otherwis | se spec | cified) |

|------------------------------------------------------|-----------|----------|---------------------------------------------------------------|---------|----------|---------|---------|

| Characteristics                                      |           | Symbol   | Test condition                                                | Min     | Тур.     | Max     | Unit    |

|                                                      | HIGH      | VIN(H)   | Logic input (Note1)                                           | 1.5     | —        | 5.5     | V       |

| Logic input voltage                                  | LOW       | VIN(L)   | Logic input (Note1)                                           | 0       | —        | 0.7     | V       |

| Logic input hysteresis vol                           | tage      | VIN(HYS) | Logic input (Note1)                                           | _       | 60       | _       | mV      |

| Logic input current                                  | HIGH      | IIN(H)   | VIN(H) = 3.3 V                                                | _       | 33       | 45      | μA      |

| Logic input current                                  | LOW       | IIN(L)   | VIN(L) = 0 V                                                  | —       | —        | 1       | μΑ      |

| ERR pin output voltage LOW                           |           | VOL(LO)  | IOL = 5 mA, output = L                                        | —       | _        | 0.5     | V       |

| Current consumption                                  |           | IM1      | Output pins = open<br>Standby mode                            | _       | _        | 0.1     | μA      |

|                                                      |           | IM2      | Output pins = open<br>EN pin = L<br>in releasing Standby mode | _       | 2.8      | 3.5     | mA      |

|                                                      |           | IM3      | Output pins = open<br>Full step resolution<br>fCLK=75 kHz     | _       | 3.3      | 4.3     | mA      |

|                                                      | High-side | IOH      | VM = 18 V, Vout = 0 V                                         | _       | —        | 1       | μA      |

| Output leakage current Low-side                      |           | IOL      | VM = Vout = 18 V                                              | -1      | —        | _       | μA      |

| Motor current channel differential                   |           | ∆lout1   | Current differential between Ch                               | -5      | 0        | 5       | %       |

| Motor current setting accuracy                       |           | ∆lout2   | lout = 1.1 A                                                  | -5      | 0        | 5       | %       |

| Motor output ON resistance<br>(High side + Low side) |           | Ron(H+L) | Tj = 25°C,<br>VM = 12 V, lout = 1 A                           | _       | 0.48     | 0.6     | Ω       |

Note: When the logic signal is applied to the device whilst the VM power supply is not asserted; the device is designed not to function, but for safe usage, please apply the logic signal after the VM power supply is asserted and the VM voltage reaches the proper operating range.

Note1: VIN(H) is defined as the VIN voltage that causes the outputs (OUT\_A+ pin, OUT\_A- pin, OUT\_B+ pin, OUT\_Bpin) to change when a pin under test is gradually raised from 0 V.VIN(L) is defined as the VIN voltage that causes the outputs (OUT\_A+ pin, OUT\_A- pin, OUT\_B+ pin, OUT\_B- pin) to change when the pin is then gradually lowered from 5V. The difference between VIN(H) and VIN(L) is defined as the VIN(HYS).

## **17. Electrical Specifications 2**

|                                                | (10 = 2   | 25  C,  VIVI = 2.5  C  I | ov unica |      | nac aper | mea  |

|------------------------------------------------|-----------|--------------------------|----------|------|----------|------|

| Characteristics                                | Symbol    | Test condition           | Min      | Тур. | Max      | Unit |

| Vref input current                             | Iref      | Vref = 1.8 V             | —        | 0    | 1        | μA   |

| Thermal shutdown (TSD)<br>threshold (Note1)    | TjTSD     | _                        | 145      | 165  | 175      | °C   |

| UVLO release voltage (Note 2)                  | VUVLO     | At rising VM             | 2.1      | 2.3  | —        | V    |

| UVLO hysteresis voltage                        | Vhys_uvlo |                          |          | 200  | —        | mV   |

| Over current detection (ISD) threshold (Note3) | ISD       | VM = 12V                 | 2.5      | 3.2  | 4.2      | А    |

|                                                |           |                          |          |      |          | •    |

### (Ta = 25°C, VM = 2.5 to 16V unless otherwise specified)

#### Note1: Thermal shutdown (TSD)

When the junction temperature of the device reaches the TSD threshold, the TSD circuit is triggered; the internal reset circuit then turns off the output transistors. Once the TSD circuit is triggered, the device will set output pin to Hi-Z, and can be cleared by reasserting the VM power source, or setting the STBY pins to standby mode. The TSD circuit is a backup function to detect a thermal error, therefore is not recommended to be used aggressively.

#### Note 2: Under voltage lockout (UVLO)

When the supply voltage to VM pin is 2.1 or less (typ.), the internal circuit is triggered; the internal reset circuit then turns off the output transistors. Once the UVLO is triggered, it can be cleared by reasserting the VM supply voltage to 2.3V or more (typ.)

#### Note3: Over current detection (ISD)

When the output current reaches the threshold, the ISD circuit is triggered; the internal reset circuit then turns off the output transistors. It has a dead band time of 1.2  $\mu$ s (typ.) to avoid ISD false triggering by switching noise. Once the ISD circuit is triggered, the device will set output pins to Hi-Z, and can be cleared by reasserting the VM power source, or setting the STBY pin to standby mode.

Note: Above ISD operation threshold value and band times are reference values, and are not guaranteed.

### Back-EMF

While a motor is rotating, there is a timing at which power is fed back to the power supply. At that timing, the motor current recirculates back to the power supply due to the effect of the motor back-EMF.

If the power supply does not have enough sink capability, the power supply and output pins of the device might rise above the rated voltages. The magnitude of the motor back-EMF varies with usage conditions and motor characteristics. It must be fully verified that there is no risk that the TC78H670FTG or other components will be damaged or fail due to the motor back-EMF.

### Cautions on Overcurrent Shutdown (ISD) and Thermal Shutdown (TSD)

The ISD and TSD circuits are only intended to provide temporary protection against irregular conditions such as an output short-circuit; they do not necessarily guarantee the complete IC safety.

If the device is used beyond the specified operating ranges, these circuits may not operate properly: then the device may be damaged due to an output short-circuit.

The ISD circuit is only intended to provide a temporary protection against an output short-circuit. If such a condition persists for a long time, the device may be damaged due to overstress. Overcurrent conditions must be removed immediately by external hardware.

#### **IC Mounting**

Do not insert devices incorrectly or in the wrong orientation. Otherwise, it may cause breakdown, damage and/or deterioration of the device.

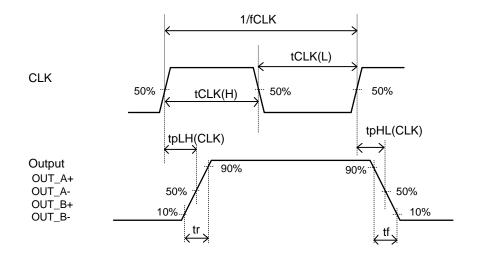

# **18. AC Electrical Specification 1**

### (Ta = 25°C, VM =12V, 6.8 mH/5.7 Ω unless otherwise specified)

|                                                 | u = <b>10</b> 0, |                                         |      |      |      |      |

|-------------------------------------------------|------------------|-----------------------------------------|------|------|------|------|

| Characteristics                                 | Symbol           | Test condition                          | Min  | Тур. | Max  | Unit |

| CLK input frequency                             | fCLK             | _                                       |      |      | 400  | kHz  |

| Inside filter of CLK input minimum High width   | tCLK(H)          | The CLK(H) minimum pulse width          | 500  | —    | _    | ns   |

| Inside filter of CLK input<br>minimum Low width | tCLK(L)          | The CLK(L) minimum pulse width          | 500  | _    | _    | ns   |

|                                                 | tr               | —                                       | 10   | 20   | 30   | ns   |

| Output transistor                               | tf               | —                                       | 10   | 20   | 30   | ns   |

| switching specific                              | tpLH(CLK)        | —                                       | _    | 840  | _    | ns   |

|                                                 | tpHL(CLK)        | _                                       | _    | 900  |      | ns   |

| Analog noise blanking time                      | AtBLK            | VM = 12 V                               | 340  | 540  | 740  | ns   |

| Oscillator frequency accuracy                   | ∆fOSCM           | ROSC = 47 kΩ<br>VM = 2.5 V to 16 V      | -15  | _    | +15  | %    |

| Oscillator reference frequency                  | fOSCM            | ROSC = 47 kΩ                            | 1076 | 1266 | 1456 | kHz  |

| Chopping frequency                              | fchop            | Output: Active, fOSCM = 1266 kHz — 79 — |      | —    | kHz  |      |

### **AC Electrical Specification Timing chart**

# **19. AC Electrical Specification 2**

### (Ta = 25°C, VM = 2.5 to 16V unless otherwise specified)

| Characteristics           | Symbol       | Test condition                             | Min  | Тур. | Max | Unit | No.in Timing<br>Chart |

|---------------------------|--------------|--------------------------------------------|------|------|-----|------|-----------------------|

| Serial CLK frequency      | fSCLK        | VIN = 3.3 V                                | 1.0  | —    | 25  | MHz  | —                     |

| CLK cycle                 | tsCKW        | VIH = 3.3 V, VIL = 0 V,<br>tr = tf = 23 ns | 46   | _    | _   | ns   | _                     |

|                           | tw(CLK)      | VIN = 3.3 V                                | 40   | —    | _   | ns   | 1                     |

| Minimum CLK pulse width   | twp(CLK)     |                                            | 20   | —    | _   | ns   | 2                     |

|                           | twn(CLK)     |                                            | 20   | —    | _   | ns   | 3                     |

| Minimum LATCH pulse width | tLATCH (H)   | VIN = 3.3 V                                | 20   | —    | _   | ns   | 4                     |

| Data actus tima           | tsuSIN - CLK |                                            | 10   | —    | _   | ns   | 5                     |

| Data setup time           | tsuLT - CLK  | VIN = 3.3 V                                | 10   |      | _   | ns   | 6                     |

| Data kaldtina             | thSIN - CLK  |                                            | 10   |      | _   | ns   | 7                     |

| Data hold time            | thLT - CLK   | VIN = 3.3 V                                | 40   | _    | —   | ns   | 8                     |

| LATCH cycle               | tcLT         | VIN = 3.3 V                                | 1.32 |      | _   | μs   | 9                     |

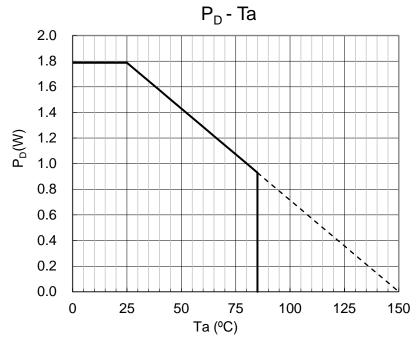

# 20. (Reference data) P<sub>D</sub>-Ta Characteristics

When mounted on the board (JEDEC 4 layers)

Note: Characteristics shown above are reference values and not guaranteed.

36

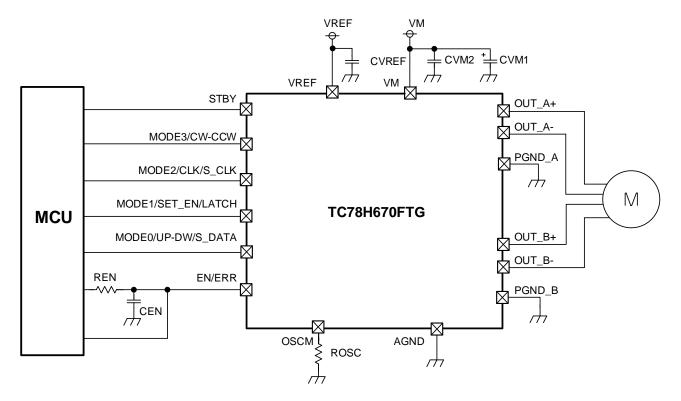

# 21. Application Circuit Example

The application circuit shown in this document is provided for reference purposes only. The data for mass production are not guaranteed.

Component values (for reference only)

| Part's symbol | Component              | Value  |

|---------------|------------------------|--------|

| CVM1          | Electrolytic capacitor | 47 μF  |

| CVM2          | Ceramic capacitor      | 0.1 µF |

| CVREF         | Ceramic capacitor      | 0.1 µF |

| CEN           | Ceramic capacitor      | 22 nF  |

| ROSC          | Resistor               | 47 kΩ  |

| REN           | Resistor               | 10 kΩ  |

Note: Componet values in above table are for reference only. Some components other than reference value can be adopted depending on the usage conditions.

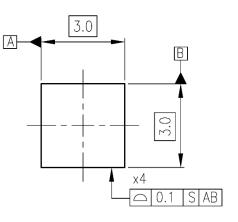

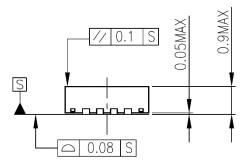

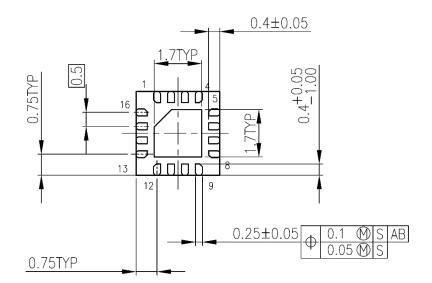

# 22. Package Dimensions

P-VQFN16-0303-0.50-001

Unit: mm

Weight: 22.9 mg (typ.)

### **Notes on Contents**

#### 1. Block Diagrams

Some of the functional blocks, circuits, or constants in the block diagram may be omitted or simplified for explanatory purposes.

#### 2. Equivalent Circuits

The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

#### 3. Timing Charts

Timing charts may be simplified for explanatory purposes.

#### 4. Application Circuits

The application circuits shown in this document are provided for reference purposes only. Thorough evaluation is required, especially at the mass production design stage.

Providing these application circuit examples does not grant a license for industrial property rights.

39

### **IC Usage Considerations**

### Notes on handling of ICs

- The absolute maximum ratings of a semiconductor device are a set of ratings that must not be exceeded, even for a moment. Do not exceed any of these ratings.

Exceeding the rating(s) may cause the device breakdown, damage or deterioration, and may result injury by explosion or combustion.

- (2) Use an appropriate power supply fuse to ensure that a large current does not continuously flow in case of over current and/or IC failure. The IC will fully break down when used under conditions that exceed its absolute maximum ratings, when the wiring is routed improperly or when an abnormal pulse noise occurs from the wiring or load, causing a large current to continuously flow and the breakdown can lead smoke or ignition. To minimize the effects of the flow of a large current in case of breakdown, appropriate settings, such as fuse capacity, fusing time and insertion circuit location, are required.

- (3) If your design includes an inductive load such as a motor coil, incorporate a protection circuit into the design to prevent device malfunction or breakdown caused by the current resulting from the inrush current at power ON or the negative current resulting from the back electromotive force at power OFF. IC breakdown may cause injury, smoke or ignition. Use a stable power supply with ICs with built-in protection functions. If the power supply is unstable, the protection function may not operate, causing IC breakdown. IC breakdown may cause injury, smoke or ignition.

- (4) Do not insert devices in the wrong orientation or incorrectly.

Make sure that the positive and negative terminals of power supplies are connected properly. Otherwise, the current or power consumption may exceed the absolute maximum rating, and exceeding the rating(s) may cause the device breakdown, damage or deterioration, and may result injury by explosion or combustion. In addition, do not use any device that is applied the current with inserting in the wrong orientation or incorrectly even just one time.

(5) Carefully select external components (such as inputs and negative feedback capacitors) and load components (such as speakers), for example, power amp and regulator. If there is a large amount of leakage current such as from input or negative feedback condenser, the IC output DC voltage will increase. If this output voltage is connected to a speaker with low input withstand voltage, overcurrent or IC failure may cause smoke or ignition. (The overcurrent may cause smoke or ignition from the IC itself.) In particular, please pay attention when using a Bridge Tied Load (BTL) connection-type IC that inputs output DC voltage to a speaker directly.

#### Points to remember on handling of ICs

#### (1) Over current Protection Circuit

Over current protection circuits (referred to as current limiter circuits) do not necessarily protect ICs under all circumstances. If the Over current protection circuits operate against the over current, clear the over current status immediately.

Depending on the method of use and usage conditions, such as exceeding absolute maximum ratings can cause the over current protection circuit to not operate properly or IC breakdown before operation. In addition, depending on the method of use and usage conditions, if over current continues to flow for a long time after operation, the IC may generate heat resulting in breakdown.

#### (2) Thermal Shutdown Circuit