#### **Features**

Product number: UMW TMP102AIDRLRS, UMW TMP102AIDRLRD

• Temperature range: -55°C ~ +150°C

• Temperature accuracy: ±0.5°C (-40°C ~ +125°C)

±0.25°C (0°C ~ +65°C)

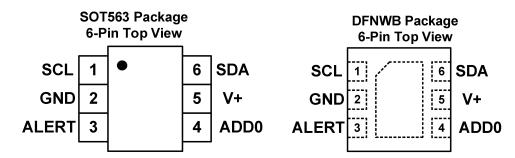

• Package: 6-Pin SOT563 (UMW TMP102AIDRLRS)

6-Pin DFNWB (UMW TMP102AIDRLRD)

• Supply voltage range: 1.4V ~ 5.5V

• Low quiescent current:

Normal operation: ≤10µA (4Hz)

Shutdown mode: ≤1µA

• Resolution: 12bits, 0.0625°C

• Digital output: SMBus<sup>TM</sup> and I<sup>2</sup>C interface

compatibility

# **Applications**

- Portable and battery-powered applications

- Power-supply temperature monitoring

- Computer peripheral thermal protection

- Notebook computers

- · Battery management

- Office machines

- Thermostat controls

- Electromechanical device temperatures

- General temperature measurements:

- Industrial controls

# **Description**

The UMW TMP102A is a digital temperature sensor with high-accuracy, low-power, and NTC/PTC thermistor replacements. It can be used for extended temperature measurement in communication, computer, environmental, industrial consumer electronics. and instrumentation applications. The **UMW** TMP102A provides  $\leq$ ± 0.5°C temperature accuracy with good temperature linearity over the normal operating range of -40°C to +125°C. The UMW TMP102A can provide extended temperature measurement mode, extending the temperature measurement range from -55°C to +150°C.

The rated working voltage range of the UMW TMP102A is 1.4V~5.5V, and the maximum quiescent current in the entire working rage is 10µA (temperature measurement frequency 4Hz). The on-chip 12-bit ADC offers resolutions down to 0.0625°C.

The UMW TMP102A adopts SOT563 / DFNWB package of 1.6mm × 1.6mm, is compatible with SMBus and I<sup>2</sup>C interface, and allows up to four devices on one bus. The device also features an SMBus alert function.

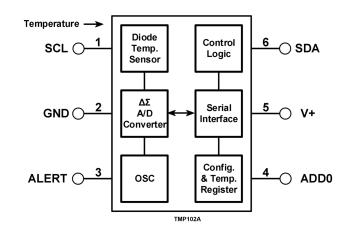

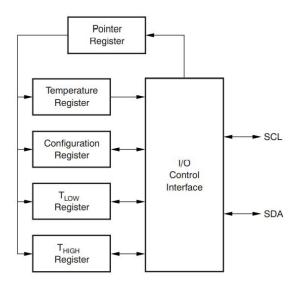

Figure 1. UMW TMP102A Internal Schematic Diagram

# **Pin Configuration and Functions**

**Pin Functions**

|     | PIN   | DESCRIPTION                                                             |  |

|-----|-------|-------------------------------------------------------------------------|--|

| NO. | NAME  | DESCRIPTION                                                             |  |

| 1   | SCL   | Serial clock. Open-drain output, requires a pull-up resistor.           |  |

| 2   | GND   | Ground.                                                                 |  |

| 3   | ALERT | Over temperature alert. Open-drain output, requires a pull-up resistor. |  |

| 4   | ADD0  | Address select. Connect to V+, GND, SCL or SDA.                         |  |

| 5   | V+    | Supply voltage, 1.4V to 5.5V.                                           |  |

| 6   | SDA   | Serial data input. Open-drain output, requires a pull-up resistor.      |  |

# **Specifications**

# **Absolute Maximum Ratings**

|                               | MIN  | MAX        | UNIT |  |

|-------------------------------|------|------------|------|--|

| Supply Voltage, V+            |      | 6          | V    |  |

| Voltage at SCL, SDA, and ADD0 | -0.5 | 6          | V    |  |

| Voltage et ALERT              | 0.5  | ((V+)+0.3) | V    |  |

| Voltage at ALERT              | -0.5 | and ≤5.5   | V    |  |

| Operating Temperature         | -55  | 160        | °C   |  |

| Junction Temperature          |      | 150        | °C   |  |

| Storage Temperature           | -60  | 150        | °C   |  |

Over operating free-air temperature range (unless otherwise noted). Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

# **ESD Ratings**

|                             |                                                   | Value | UNIT |

|-----------------------------|---------------------------------------------------|-------|------|

| Electrostatic               | Human Body Mode (HBM), per ANSI/ESDA/JEDEC JS-001 | ±5000 | V    |

| Discharge, V <sub>ESD</sub> | Machine Mode (MM), per JEDEC-STD Classification   | 300   | V    |

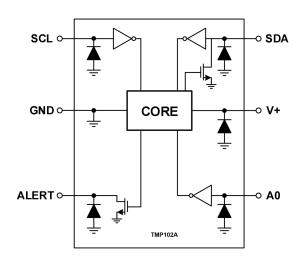

Figure 2. UMW TMP102A Internal ESD

# Recommended Operating Conditions

|                                      | MIN | NOM | MAX | UNIT |

|--------------------------------------|-----|-----|-----|------|

| Supply Voltage V+                    | 1.4 | 3.3 | 5.5 | V    |

| Operating Temperature T <sub>A</sub> | -50 |     | 150 | °C   |

# **Electrical Characteristics**

Electrical characteristics of devices at  $T_A$  = +25 $^{\circ}$ C and V+ = 1 4 V to 3 6 V (unless otherwise noted)

| PARAMETER                         | TEST CONDITONS                             | MIN   | TYP    | MAX   | UNIT   |  |

|-----------------------------------|--------------------------------------------|-------|--------|-------|--------|--|

| On anoting Tamananatura Dange     |                                            | -40   |        | 125   | °C     |  |

| Operating Temperature Range       | Extended mode                              | -55   |        | 150   | °C     |  |

|                                   | +25°C, V+ = 3.3V                           |       | ±0.1   | ±0.5  | °C     |  |

| Accuracy (Temperature Error)      | 0°C to +65°C, V+ = 3.3V                    |       | ±0.25  | ±0.5  | °C     |  |

|                                   | -40°C to +125°C                            |       | ±0.5   | ±1    | °C     |  |

| DC Power Supply Sensitivity       | -40°C to +125°C                            |       | 0.0625 | ±0.25 | °C/V   |  |

| Resolution                        |                                            |       | 0.0625 |       | °C     |  |

| Resolution                        |                                            |       | 12     |       | bits   |  |

| Conversion Time                   |                                            |       | 26     | 35    | ms     |  |

|                                   | CR1 = 0, CR0 = 0                           |       | 0.25   |       |        |  |

| Conversion Mades                  | CR1 = 0, CR0 = 1                           |       | 1      |       | conv/s |  |

| Conversion Modes                  | CR1 = 1, CR0 = 0 (default)                 |       | 4      |       |        |  |

|                                   | CR1 = 1, CR0 = 1                           |       | 8      |       |        |  |

| Timeout Time                      |                                            |       | 30     | 40    | ms     |  |

| Communication Fraguency           | Fast mode                                  | 0.001 |        | 0.4   | MHz    |  |

| Communication Frequency           | High-speed mode                            | 0.001 |        | 2.75  | IVITIZ |  |

| Power Supply Voltage              |                                            | 1.4   | 3.3    | 5.5   | V      |  |

|                                   | Serial bus inactive, CR1=1,CR0=0 (default) |       | 7      | 10    |        |  |

| Average Quiescent Current, IQ     | Serial bus active, SCL frequency=400 kHz   |       | 15     |       | μΑ     |  |

|                                   | Serial bus active, SCL frequency=2.75 MHz  |       | 85     |       |        |  |

|                                   | Serial bus inactive                        |       | 0.5    | 1     |        |  |

| Shutdown Current, I <sub>SD</sub> | Serial bus active, SCL frequency=400 kHz   |       | 10     |       | μΑ     |  |

|                                   | Serial bus active, SCL frequency=2.75 MHz  |       | 80     |       | 7      |  |

#### **Detailed Description**

#### **Device Functional Modes**

#### **Continuous Conversion Mode**

1

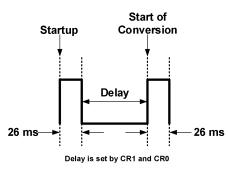

The default working mode of UMW TMP102A is continuous conversion mode, and the typical conversion time is 26ms. During continuous conversion mode, the ADC performs continuous temperature conversions and stores each results to the temperature register, overwriting the result from the previous conversion. The conversion rate bits, CR1 and CR0, configure the UMW TMP102A for conversion rates of 0.25Hz, 1Hz, 4Hz, or 8Hz. The conversion rate can be changed by configuring CR1 and CR0, the UMW TMP102A makes a conversion and then powers down and waits for the appropriate delay set by CR1 and CR0, as shown in Figure 3. Table 1 lists the settings for CR1 and CR0.

CR1

CR0

CONVERSION RATE

0

0

0.25Hz

0

1

1Hz

1

0

4Hz (default)

1

**Table 1. Conversion Rate Settings**

Figure 3. Schematic Diagram of Continuous Conversion

#### **Extended Mode**

The temperature measurement range of UMW TMP102A is -40°C to +125°C in normal temperature measurement mode. By setting the EM bit in the configuration register to1, the UMW TMP102A can enter the extended temperature measurement mode. Extended mode (EM = 1) allows measurement of temperatures above 128°C by configuring the temperature register and the temperature limit registers for 13-bit data format.

The read-only temperature register in UMW TMP102A uses two bytes to store the temperature

8Hz

measurement results, as shown in Table 8 and Table 9. Byte 1 is the MSB, byte 2 is the LSB, and the upper 12 bits (13 bits in extended mode) are used to indicate the temperature. It is not necessary to read the LSB when the temperature information of the LSB is not required.

The data format of the UMW TMP102A temperature measurement results is listed in Table 2 and Table 3, where 1LSB = 0.0625°C, and negative numbers are expressed in binary two's complement format. When powered on or reset, the temperature register of the UMW TMP102A will be set to 00h until the next temperature conversion is complete. Unused bits in the temperature register always read as 0 (not shown in the table below).

Table 2. 12-bit Temperature Data Format in Normal Temperature Measurement Mode

| TEMPERATURE (°C) | DIGITAL OUPUT (BINARY) | HEX |

|------------------|------------------------|-----|

| 128              | 0111 1111 1111         | 7FF |

| 127.9375         | 0111 1111 1111         | 7FF |

| 100              | 0110 0100 0000         | 640 |

| 80               | 0101 0000 0000         | 500 |

| 75               | 0100 1011 0000         | 4B0 |

| 50               | 0011 0010 0000         | 320 |

| 25               | 0001 1001 0000         | 190 |

| 0.25             | 0000 0000 0100         | 004 |

| 0                | 0000 0000 0000         | 000 |

| -0.25            | 1111 1111 1100         | FFC |

| -25              | 1110 0111 0000         | E70 |

| -55              | 1100 1001 0000         | C90 |

Table 3. 13-bit Temperature Data Format in Extended Temperature Measurement Mode

| TEMPERATURE (°C) | DIGITAL OUPUT (BINARY) | HEX  |

|------------------|------------------------|------|

| 150              | 0 1001 0110 0000       | 0960 |

| 128              | 0 1000 0000 0000       | 0800 |

| 127.9375         | 0 0111 1111 1111       | 07FF |

| 100              | 0 0110 0100 0000       | 0640 |

| 80               | 0 0101 0000 0000       | 0500 |

| 75               | 0 0100 1011 0000       | 04B0 |

| 50               | 0 0011 0010 0000       | 0320 |

| 25               | 0 0001 1001 0000       | 0190 |

| 0.25             | 0 0000 0000 0100       | 0004 |

| 0                | 0 0000 0000 0000       | 0000 |

| -0.25 | 1 1111 1111 1100 | 1FFC |

|-------|------------------|------|

| -25   | 1 1110 0111 0000 | 1E70 |

| -55   | 1 1100 1001 0000 | 1C90 |

#### **Shutdown Mode**

Shutdown mode of the UMW TMP102A device allows the user to conserve power by shutting down all device circuitry except the serial interface, thereby reducing the current of the UMW TMP102A to less than 0.5µA (typical value). Shutdown mode is initiated when the SD bit in the configuration register is set to 1; after configuring the registers in this way, the UMW TMP102AI will shut down after completing the current conversion. To exit shutdown mode, write SD bit to 0, the UMW TMP102A will re-enter continuous conversion mode.

#### **One-Shot Mode**

The UMW TMP102A features a one-shot mode. When the UMW TMP102A is in shutdown mode, writing 1 to the OS bit starts a single temperature conversion. During the conversion, the OS bit reads 0. The UMW TMP102AI returns to the shutdown state at the completion of the single conversion, the OS bit reads 1. This feature is useful for reducing power consumption when continuous temperature monitoring is not required.

Since the UMW TMP102A only needs 26ms for a single temperature measurement (typical value), it can achieve a higher conversion rate through this mode. When using one-shot mode, 30 or more conversions per second are possible.

#### **ALERT**

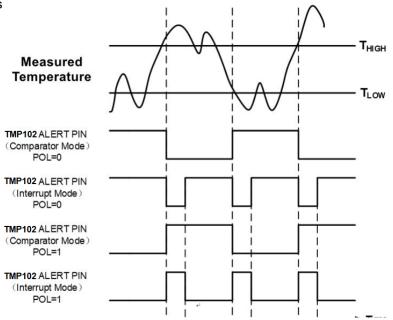

The UMW TMP102A has a temperature alarm function, by writing the TM bit in the configuration register as 0 or 1, the UMW TMP102A can be configured as comparator mode or interrupt mode to achieve different alarm functions

Figure 4 Status of the ALERT Pin in Different Modes

In comparison mode (TM=0), when the number of times the temperature measurement result continuously equals or exceeds the temperature upper limit register value T<sub>HIGH</sub> reaches the value defined by the F1/F0 bits in the configuration register (as shown in Table 4), the ALERT pin will be activated. The ALERT pin will remain active until the number of times the temperature measurement result is continuously lower than the temperature lower limit register value T<sub>LOW</sub> reaches the value defined by F1/F0.

In interrupt mode (TM=1), the ALERT pin will be activated when the temperature measurement result equals or exceeds T<sub>HIGH</sub> continuously for a number of times to the value defined by F1/F0 (as shown in Table 4). The ALERT pin remains active until it is cleared by one of three events: a read of any register, a successful SMBus alert response, or a shutdown command. After the ALERT pin is cleared, the device starts to compare temperature readings with the T<sub>LOW</sub>. The ALERT pin becomes active again only when the temperature drops below T<sub>LOW</sub> for a consecutive number of conversions as set by F1/F0 bits. The ALERT pin remains active until cleared by any of the same three clearing events. The user can also reset the UMW—TMP102A to clear the ALERT pin state by using the global response reset command (General Call). This operation also resets other internal registers in the UMW—TMP102A and returns the device to compare mode (TM=0). Table 4 shows the specific configuration of the F1/F0 bits.

Table 4. Number of Over-Temperature Required to Activate the ALERT Pin

| F1 | F0 | REQUIRED NUMBER (TIMES) |

|----|----|-------------------------|

| 0  | 0  | 1 (Default)             |

| 0  | 1  | 2                       |

| 1  | 0  | 4                       |

| 1  | 1  | 6                       |

The polarity bit (POL) in the configuration register allows the user to adjust the polarity of the ALERT pin output. If the POL bit is set to 0 (default), the ALERT pin becomes active low. When POL bit is set to 1, the ALERT pin becomes active high. The above situations are shown in Figure 4.

#### **Serial Interface**

#### **Bus Overview**

The UMW TMP102A is compatible with SMBus and I<sup>2</sup>C interfaces. In the SUMBus protocol, the device that initiates the transfer is called a master, and the devices controlled by the master are slaves. The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions. To address a specific device, a START condition is initiated, indicated by pulling the data line (SDA) from a high- to low-logic level when the SCL pin is high. All slaves on the bus receive the 8-bits slave address on the rising edge of the clock, and the last bit indicates whether a read or write operation is intended. During the ninth clock pulse, the addressed slave generates an acknowledge and pulls the SDA pin low to respond to the master. A data transfer is then initiated and sent over eight clock pulses followed by an acknowledge bit. When all data are transferred, the master generate a STOP signal to end the communication by pulling SDA from low to high when SCL is high.

During the data transfer, the SDA pin must remain stable when the SCL pin is high because any change in the SDA pin when the SCL pin is high is interpreted as a START or STOP signal.

#### Serial Bus Address

To communicate with the UMW TMP102A, the master must first address slave devices through an address byte. The address byte has seven address bits and a read-write (R/W) bit that indicates the intent of executing a read or write operation. The UMW TMP102A features an address pin to allow up to four devices to be addressed on a single bus. Table 5 shows the connection mode of the ADD0 pins corresponding to each slave address.

Table 5. Address Pin and Slave Addresses

| DEVICE TWO-WIRE ADDRESS | ADD0 PIN CONNECTION |

|-------------------------|---------------------|

| 1001000                 | GND                 |

| 1001001                 | V+                  |

| 1001010                 | SDA                 |

| 1001011                 | SCL                 |

# **Writing and Reading Operation**

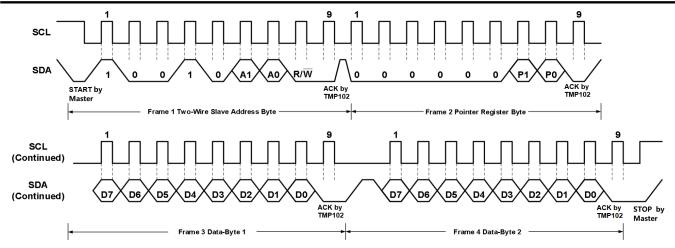

Figure 5. Two-wire Write Command Timing Diagram

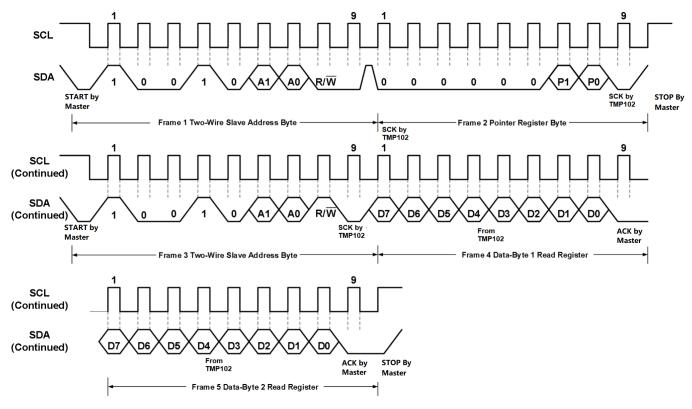

Figure 6. Two-wire Read Command Timing Diagram

When writing data to the UMW TMP102A, after the slave address byte is sent, accessing a particular register on the UMW TMP102A is accomplished by writing the appropriate value to the pointer register. Every write operation to the UMW TMP102A requires a value for the pointer register.

When reading from the UMW TMP102A device, after the slave address byte is sent, the corresponding pointer register byte also needs to be sent. Unlike the write operation, if the user need to repeatedly read data from the same register, it is not required to send the pointer register byte separately each time, the last value stored in the

pointer register will be read by the device automatically; to change the register pointer for a read operation, a new value must be written to the pointer register. The action is accomplished by issuing a slave-address byte with the R/W bit low, followed by the pointer register byte. The master can then generate a START condition and send the slave address byte with the R/W bit high to initiate the read command.

Register bytes are sent with the MSB first, followed by the LSB. Figure 5 and Figure 6 show schematic diagrams of the above read and write operations.

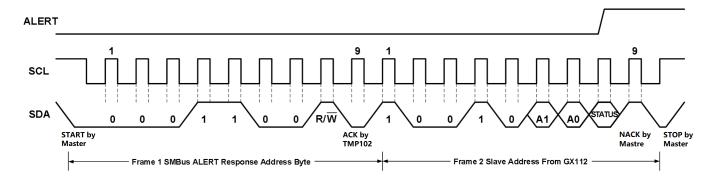

#### **SMBus Alert Function**

The UMW TMP102A supports the SMBus alert function. When the UMW TMP102A operates in interrupt mode (TM=1), the master can send out and SMBus ALERT command (19h) to the bus. If the ALERT pin is active, the device acknowledges the SMBus ALERT command and responds by returning the slave address. The eighth bit (LSB) of the slave address byte indicates if the alert condition is caused by the temperature exceeding T<sub>HIGH</sub> or falling below T<sub>LOW</sub>. This bit is equal to POL if the temperature is greater than or equal to T<sub>HIGH</sub>; this bit is equal to POL if the temperature is less than T<sub>LOW</sub>.

If multiple devices on the bus respond to the SMBus ALERT command, the bus will return the lowest two-wire address. The UMW TMP102A ALERT pin becomes inactive at the completion of the SMBus ALERT command; the ALERT pin of the UMW TMP102A that does not return an address will remain active. Sending the SMBus ALERT command again can continue to clear the ALERT pin of the UMW TMP102A with the current lowest address. The above process is detailed in Figure 7.

Figure 7. SMBus Alert Timing Diagram

#### **General Call Reset**

The UMW TMP102A responds to the two-wire general call address 00h. The device acknowledges the general call address and responds to commands in the second byte. If the second byte is 06h, the UMW

TMP102A resets the internal registers to the power-up reset values, and aborts the current temperature conversion. If the second byte is other value, the UMW TMP102A will not respond.

#### **High-Speed Mode**

For the two-wire bus to operate at frequencies above 400kHz, the host device must issue a High-Speed mode host code (0000 1xxxb) as the first byte after a START condition to switch the bus to high-speed operation. The UMW TMP102A device does not acknowledge this byte, but it does switch the input filters on the SDA and SCL and the output filters on the SDA to operate in High-Speed mode, allowing the bus to transmit data at frequencies up to 2.75MHz. After the High-Speed mode host code is issued, the host transmits a two-wire device address to initiate a data transfer operation. The bus continues to operate in High-Speed mode until a STOP condition occurs on the bus. Upon receiving the STOP condition, the UMW TMP102A switches the input and output filters back to fast-mode operation.

#### **Time-Out Function**

The UMW TMP102A resets the serial interface if SCL is held low for 30ms (typical) between a START and STOP condition, the UMW TMP102A releases the SDA bus and waits for a START condition. To avoid activating the Time-Out function, a communication speed of at least 1kHz must be maintained.

# **Register Descriptions**

## **Pointer Register**

Figure 8 shows the internal register structure of the UMW TMP102A device. The 8-bit Pointer Register of the device is used to address a given data register. The Pointer Register uses the two LSBs (see Table 6) to identify which of the data registers must respond to a read or write command. The power-up reset value of P1/P0 is '00'. By default, the UMW TMP102A reads the temperature on power-up.

Figure 8. Internal Register Structure

**Table 6 lists t**he pointer address of the registers available in the UMW TMP102A device. During a write command, bytes P2 through P7 must always be 0.

**Table 6. Pointer Address**

| P1 | P0 | REGISTER                                |  |  |

|----|----|-----------------------------------------|--|--|

| 0  | 0  | Temperature Register (Read Only)        |  |  |

| 0  | 1  | Configuration Register (Read/Write)     |  |  |

| 1  | 0  | T <sub>LOW</sub> Register (Read/Write)  |  |  |

| 1  | 1  | T <sub>HIGH</sub> Register (Read/Write) |  |  |

Table 7. Pointer Register Byte

| P7 | P6 | P5 | P4 | P3 | P2 | P1            | P0 |

|----|----|----|----|----|----|---------------|----|

| 0  | 0  | 0  | 0  | 0  | 0  | Register Bits |    |

## **Temperature Register**

The Temperature Register of the UMW TMP102A device is configured as a 12-bit or 13-bit read-only register (setting the EM bit to 0 or 1) that stores the output of the most recent conversion. Two bytes must be read to obtain data and are listed in Table 8 and Table 9. Byte 1 is the most significant byte (MSB), followed by byte 2, the least significant byte (LSB). The T11~T0 bits (T12~T0 bits in extended mode) are used to indicate temperature. Byte 2 does not have to be read if that information is not needed. The D0 bit of byte 2 in the temperature register indicates whether the device is in normal mode (D0=0) or extended mode (D0=1) at this time, which can be used to distinguish the format of the two temperature register data.

Table 8. Byte 1 of Temperature Register

| BYTE     | D7    | D6    | D5    | D4   | D3   | D2   | D1   | D0   |

|----------|-------|-------|-------|------|------|------|------|------|

| 4        | T11   | T10   | Т9    | T8   | T7   | Т6   | T5   | T4   |

| <b>'</b> | (T12) | (T11) | (T10) | (T9) | (T8) | (T7) | (T6) | (T5) |

Table 9. Byte 2 of Temperature Register

| BYTE | D7   | D6   | D5   | D4   | D3   | D2  | D1  | D0  |

|------|------|------|------|------|------|-----|-----|-----|

| 4    | Т3   | T2   | T1   | T0   | 0    | 0   | 0   | 0   |

| I    | (T4) | (T3) | (T2) | (T1) | (T0) | (0) | (0) | (1) |

#### **Temperature Limit Register**

The temperature limits are stored in the  $T_{HIGH}$  and  $T_{LOW}$  registers in the same format as the temperature result, and can be configured as 12-bit or 13-bit according to the value of the EM bit. Table 10 and Table 11 list the format for the  $T_{HIGH}$  and  $T_{LOW}$  registers, the configuration in extended mode is in brackets. The power-up reset values for  $T_{HIGH}$  and  $T_{LOW}$  are:

•  $T_{HIGH} = +80^{\circ}C$ ;  $T_{LOW} = +75^{\circ}C$

Table 10. Byte 1 and 2 of THIGH Register

| BYTE | D7    | D6    | D5    | D4   | D3   | D2   | D1   | D0   |

|------|-------|-------|-------|------|------|------|------|------|

| 4    | H11   | H10   | H9    | H8   | H7   | H6   | H5   | H4   |

| l l  | (H12) | (H11) | (H10) | (H9) | (H8) | (H7) | (H6) | (H5) |

| 2    | НЗ    | H2    | H1    | H0   | 0    | 0    | 0    | 0    |

|      |      |      |      |      |     |     | _   |

|------|------|------|------|------|-----|-----|-----|

| (H4) | (H3) | (H2) | (H1) | (H0) | (0) | (0) | (0) |

#### Table 11. Byte 1 and 2 of TLOW Register

| BYTE | D7    | D6    | D5    | D4   | D3   | D2   | D1   | D0   |

|------|-------|-------|-------|------|------|------|------|------|

| 1    | L11   | L10   | L9    | L8   | L7   | L6   | L5   | L4   |

|      | (L12) | (L11) | (L10) | (L9) | (L8) | (L7) | (L6) | (L5) |

| 2    | L3    | L2    | L1    | L0   | 0    | 0    | 0    | 0    |

| 2    | (L4)  | (L3)  | (L2)  | (L1) | (L0) | (0)  | (0)  | (0)  |

# **Configuration Register**

The Configuration Register is a 16-bit read/write register used to store bits that control the operational modes of the temperature sensor. Read/write operations are performed MSB first. Table 12 and Table 13 list the format and power-up and reset values of the configuration register.

Table 12. Configuration Register High Byte

| BIT | FIELD     | DEFAULT | DESCRIPTION                                  |  |  |  |

|-----|-----------|---------|----------------------------------------------|--|--|--|

|     |           |         | One-Shot and Conversion Completion Flag      |  |  |  |

| 7   | OS (R)    | 0       | 1 = Temperature not converting               |  |  |  |

|     |           |         | 0 = Temperature is converting                |  |  |  |

| 6   | R1 (R)    | 1       | Set to 11 on Power-up                        |  |  |  |

| 5   | R0 (R)    | 1       | Temperature measurement resolution is 12bits |  |  |  |

|     |           |         | Flag Bit for the Number of Over-Temperature  |  |  |  |

| 4   | F1 (R/W)  | 0       | Required to Activate the ALERT Pin           |  |  |  |

|     |           |         | 00 = 1 time (Default)                        |  |  |  |

|     |           |         | 01 = 2 times                                 |  |  |  |

| 3   | F0 (R/W)  | 0       | 10 = 4 times                                 |  |  |  |

|     |           |         | 11 = 6 times                                 |  |  |  |

|     |           |         | ALERT Pin Polarity Flag                      |  |  |  |

| 2   | POL (R/W) | 0       | 1 = ALERT pin is high when activated         |  |  |  |

|     |           |         | 0 = ALERT pin is low when activated          |  |  |  |

|     |           |         | Device Working Mode Flag Bit                 |  |  |  |

| 1   | TM (R/W)  | 0       | 1 = Interrupt mode                           |  |  |  |

|     |           |         | 0 = Comparator mode                          |  |  |  |

|     |           |         | Shutdown Mode Flag                           |  |  |  |

| 0   | SD (R/W)  | 0       | 1 = Shutdown mode                            |  |  |  |

|     |           |         | 0 = Continuous conversion mode               |  |  |  |

Table 13. Configuration Register Low Byte

| BIT | FIELD     | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|-----|-----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | CR1 (R/W) | 1       | Continuous Conversion Rate Flag<br>00 = 0.25Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 6   | CR0 (R/W) | 0       | 01 = 1Hz<br>10 = 4Hz (Default)<br>11 = 8Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 5   | AL (R)    | 1       | Alarm Function Fag Bit in Compare Mode  When the POL bit equals 0, the AL bit reads as 1 until the temperature equals or exceeds T <sub>HIGH</sub> for the programmed number of consecutive faults, causing the AL bit to read as 0. The AL bit continues to read as 0 until the temperature falls below T <sub>LOW</sub> for the programmed number of consecutive faults, when it again reads as 1. If POL=1, the behavior of the AL bit is the opposite of the above.  The status of the TM bit does not affect the status of the AL bit. |  |  |  |

| 4   | EM (R/W)  | 0       | Extended Mode Flag  1 = Extended mode  0 = Normal mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 3   | 0         | 0       | /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 2   | 0         | 0       | /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 1   | 0         | 0       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 0   | 0         | 0       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

# **Application and Implementation**

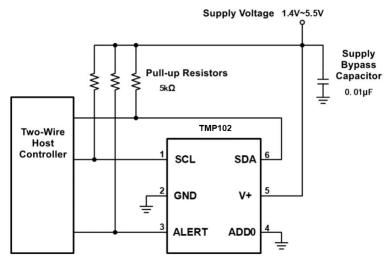

Figure 9. Typical Connections of the UMW TMP102A

The UMW TMP102A device requires pull-up resistors on the SCL, SDA, and ALERT pins, as shown in Figure 9, the recommended value for the pull-up resistors is  $5k\Omega$ . In some applications the pull-up resistor can be lower or higher than  $5k\Omega$  but must not exceed 3mA of current on any of those pins.

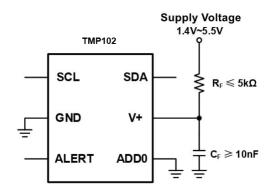

The UMW TMP102A device is a very low-power device and generates very low noise on the supply bus. Applying an RC filter to the V+ pin of the UMW TMP102A device can further reduce any noise that the device might propagate to other components.  $R_F$  in Figure 10 must be less than  $5k\Omega$  and  $C_F$  must be greater than 10nF.

Figure 10. Noise Reduction Techniques

-

# Ordering information

| Order code       | Order code Package |      | Deliverymode  |  |

|------------------|--------------------|------|---------------|--|

| UMW TMP102AIDRLR | SOT-563            | 4000 | Tape and reel |  |

# 单击下面可查看定价,库存,交付和生命周期等信息

# >>UMW(友台半导体)