Low Capacitance Diode Array for ESD Protection in a Single Data Line

NUP1301 is a MicroIntegration device designed to provide protection for sensitive components from possible harmful electrical transients; for example, ESD (electrostatic discharge).

#### **Features**

- Low Capacitance (0.9 pF Maximum)

- Single Package Integration Design

- Provides ESD Protection for JEDEC Standards JESD22

Machine Model = Class C Human Body Model = Class 3B

• Protection for IEC61000-4-2 (Level 4)

8.0 kV (Contact) 15 kV (Air)

- Ensures Data Line Speed and Integrity

- Fewer Components and Less Board Space

- Direct the Transient to Either Positive Side or to the Ground

- SZ Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q101 Qualified and PPAP Capable

- Pb-Free Package is Available

#### **Applications**

- T1/E1 Secondary IC Protection

- T3/E3 Secondary IC Protection

- HDSL, IDSL Secondary IC Protection

- Video Line Protection

- Microcontroller Input Protection

- Base Stations

- I<sup>2</sup>C Bus Protection

### MAXIMUM RATINGS (Each Diode) (T<sub>J</sub> = 25°C unless otherwise noted)

| Rating                                                                             | Symbol                 | Value             | Unit |

|------------------------------------------------------------------------------------|------------------------|-------------------|------|

| Reverse Voltage                                                                    | V <sub>R</sub>         | 70                | Vdc  |

| Forward Current                                                                    | I <sub>F</sub>         | 215               | mAdc |

| Peak Forward Surge Current                                                         | I <sub>FM(surge)</sub> | 500               | mAdc |

| Repetitive Peak Reverse Voltage                                                    | V <sub>RRM</sub>       | 70                | V    |

| Average Rectified Forward Current (Note 1) (averaged over any 20 ms period)        | I <sub>F(AV)</sub>     | 715               | mA   |

| Repetitive Peak Forward Current                                                    | I <sub>FRM</sub>       | 450               | mA   |

| Non-Repetitive Peak Forward Current $t = 1.0 \ \mu s$ $t = 1.0 \ ms$ $t = 1.0 \ S$ | I <sub>FSM</sub>       | 2.0<br>1.0<br>0.5 | А    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. FR-5 =  $1.0 \times 0.75 \times 0.062$  in.

Low Capacitance Diode

# Array for ESD Protection in a Single Data Line

#### THERMAL CHARACTERISTICS

| Characteristic                                      | Symbol           | Max         | Unit |

|-----------------------------------------------------|------------------|-------------|------|

| Thermal Resistance Junction-to-Ambient              | $R_{	heta JA}$   | 625         | °C/W |

| Lead Solder Temperature Maximum 10 Seconds Duration | TL               | 260         | °C   |

| Junction Temperature                                | T <sub>J</sub>   | -65 to 150  | °C   |

| Storage Temperature                                 | T <sub>stg</sub> | -65 to +150 | °C   |

### **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = 25°C unless otherwise noted) (Each Diode)

| Characteristic                                                                                                                                                               | Symbol            | Min              | Тур              | Max                        | Unit             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|------------------|----------------------------|------------------|

| OFF CHARACTERISTICS                                                                                                                                                          |                   |                  |                  |                            |                  |

| Reverse Breakdown Voltage (I <sub>(BR)</sub> = 100 μA)                                                                                                                       | V <sub>(BR)</sub> | 70               | _                | -                          | Vdc              |

| Reverse Voltage Leakage Current ( $V_R = 70 \text{ Vdc}$ ) ( $V_R = 25 \text{ Vdc}$ , $T_J = 150^{\circ}\text{C}$ ) ( $V_R = 70 \text{ Vdc}$ , $T_J = 150^{\circ}\text{C}$ ) | I <sub>R</sub>    | -<br>-<br>-      | -<br>-<br>-      | 2.5<br>30<br>50            | μAdc             |

| Diode Capacitance (between I/O and ground) (V <sub>R</sub> = 0, f = 1.0 MHz)                                                                                                 | C <sub>D</sub>    | _                | _                | 0.9                        | pF               |

| Forward Voltage ( $I_F = 1.0 \text{ mAdc}$ ) ( $I_F = 10 \text{ mAdc}$ ) ( $I_F = 50 \text{ mAdc}$ ) ( $I_F = 150 \text{ mAdc}$ )                                            | V <sub>F</sub>    | -<br>-<br>-<br>- | -<br>-<br>-<br>- | 715<br>855<br>1000<br>1250 | mV <sub>dc</sub> |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 2. FR-5 =  $1.0 \times 0.75 \times 0.062$  in.

- 3. Alumina = 0.4  $\times$  0.3  $\times$  0.024 in, 99.5% alumina.

- 4. Include SZ-prefix devices where applicable.

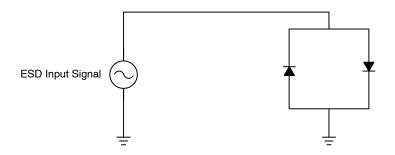

Figure 1. ESD Test Circuit

#### **APPLICATION NOTE**

#### **Electrostatic Discharge**

A common means of protecting high–speed data lines is to employ low–capacitance diode arrays in a rail–to–rail configuration. Two devices per line are connected between two fixed voltage references such as  $V_{CC}$  and ground. When the transient voltage exceeds the forward voltage  $(V_F)$  drop of the diode plus the reference voltage, the diodes direct the

surge to the supply rail or ground. This method has several advantages including low loading capacitance, fast response time, and inherent bidirectionality (within the reference voltages). See Figure 1 for the test circuit used to verify the ESD rating for this device.

Low Capacitance Diode

Array for ESD Protection in a Single Data Line

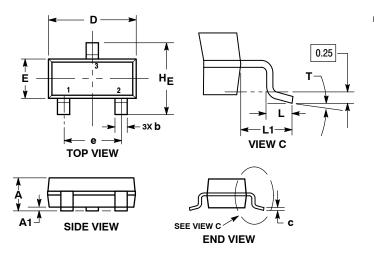

### **PACKAGE DIMENSIONS**

SOT-23 (TO-236) CASE 318-08 **ISSUE AR**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH.

MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF

THE BASE MATERIAL.

4. DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH,

PROTRUSIONS, OR GATE BURRS.

|     | MILLIMETERS |      | INCHES |       |       |       |

|-----|-------------|------|--------|-------|-------|-------|

| DIM | MIN         | NOM  | MAX    | MIN   | NOM   | MAX   |

| Α   | 0.89        | 1.00 | 1.11   | 0.035 | 0.039 | 0.044 |

| A1  | 0.01        | 0.06 | 0.10   | 0.000 | 0.002 | 0.004 |

| b   | 0.37        | 0.44 | 0.50   | 0.015 | 0.017 | 0.020 |

| С   | 0.08        | 0.14 | 0.20   | 0.003 | 0.006 | 0.008 |

| D   | 2.80        | 2.90 | 3.04   | 0.110 | 0.114 | 0.120 |

| E   | 1.20        | 1.30 | 1.40   | 0.047 | 0.051 | 0.055 |

| е   | 1.78        | 1.90 | 2.04   | 0.070 | 0.075 | 0.080 |

| L   | 0.30        | 0.43 | 0.55   | 0.012 | 0.017 | 0.022 |

| L1  | 0.35        | 0.54 | 0.69   | 0.014 | 0.021 | 0.027 |

| HE  | 2.10        | 2.40 | 2.64   | 0.083 | 0.094 | 0.104 |

| T   | 0°          |      | 10 °   | 0 °   |       | 10 °  |

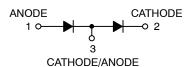

#### STYLE 11:

- PIN 1. ANODE 2. CATHODE 3. CATHODE-ANODE

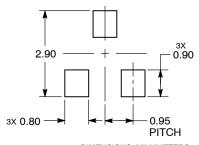

#### **RECOMMENDED SOLDERING FOOTPRINT\***

DIMENSIONS: MILLIMETERS

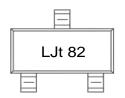

## Marking

#### **ORDERING INFORMATION**

| Order code  | Package | Base qty | Delivery mode |

|-------------|---------|----------|---------------|

| UMW NUP1301 | SOT-23  | 3000     | Tape and reel |

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# 单击下面可查看定价,库存,交付和生命周期等信息

# >>UMW(友台半导体)