# High-Voltage Current Mode PWM Controller for ISDN Power Supplies

#### **FEATURES**

- BiC/DMOS Technology

- Current Mode Control

- Max 50% Duty Cycle Operation

- 1.3-MHz Error Amp

- Up to 500-kHz Internal Oscillator

- Soft-Start

- 0.6-V Fast Over-Current Protection

- <5-μA Supply Current for +V<sub>IN</sub> <18 V</li>

- 23.5-V to 200-V Input Voltage Range

- Programmable Start/Stop Capability

- Internal Start-Up Circuit

- Power\_Good Output

#### DESCRIPTION

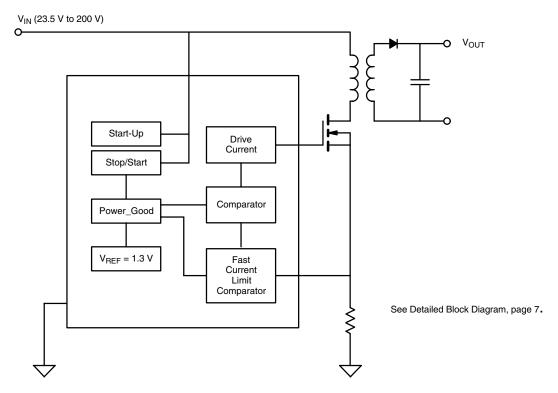

Si9113 is a current mode PWM controller for ISDN power supplies. In a 14-pin SOIC package, it provides all necessary functions to implement a single-switch PWM with a minimum of external parts. To maximize the circuit integration, the Si9113 is designed with a 200-V depletion mode MOSFET capable of powering directly off the high input bus without an external start-up circuit. The Start and Stop input voltage thresholds can be programmed within the operating input voltage range by means of a resistor divider, provided  $+V_{\text{IN}}$

(Start) >  $+V_{IN}$  (Stop). The internal clock frequency is set with a single external resistor and is capable of capacitor-coupled external synchronization. In order to satisfy the stringent ambient temperature requirements, the Si9113 is rated to handle the industrial range of  $-40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ .

The Si9113 is available in both standard and lead (Pb)-free packages.

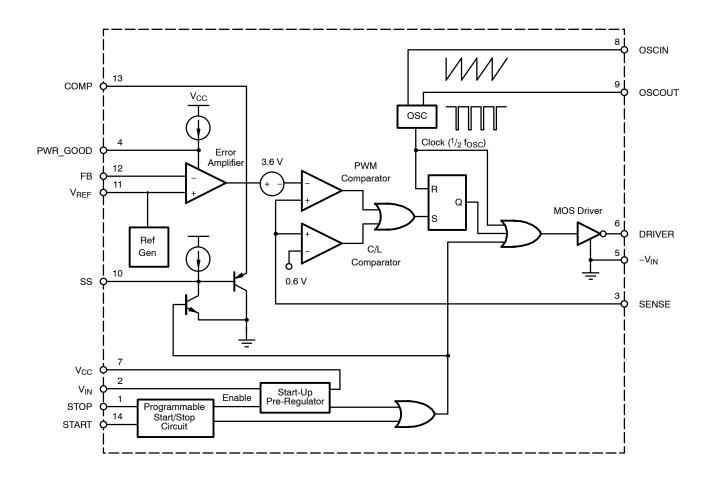

#### **FUNCTIONAL BLOCK DIAGRAM**

Applications information see AN728.

A Demonstration Borad data sheet is available for this product.

Document Number: 71093 S-40746—Rev. B. 19-Apr-04

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>IN</sub>                                                  | Junction Temperature                                                         |

|------------------------------------------------------------------|------------------------------------------------------------------------------|

| V <sub>CC</sub>                                                  | Power Dissipation (Package) <sup>a</sup> 14-Pin SOIC (Y Suffix) <sup>b</sup> |

| or $\pm 10$ mA  Linear Inputs (FB, V <sub>RFF</sub> , SENSE, SS) | Thermal Impedance ( $\Theta_{JA}$ ) 14-Pin SOIC                              |

| Storage Temperature –65 to 150°C                                 | Notes  a. Device mounted with all leads soldered or welded to PC board.      |

| Operating Temperature40 to 85°C                                  | b. Derate 7.2 mW/°C above 25°C.                                              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING RANGE**

| V <sub>IN</sub> | Linear Outputs 0 V to V <sub>CC</sub> – 3 V |

|-----------------|---------------------------------------------|

| V <sub>CC</sub> | F <sub>OSC</sub> 30 kHz to 500 kHz          |

| Digital Inputs  |                                             |

| <b>SPECIFICATIONS</b> <sup>2</sup>   | 1                    |                                                                   |              |                              |                  |               |        |  |

|--------------------------------------|----------------------|-------------------------------------------------------------------|--------------|------------------------------|------------------|---------------|--------|--|

|                                      |                      | Test Conditions Unless Otherwise Specified                        |              | <b>Limits</b><br>-40 to 85°C |                  |               |        |  |

| Parameter                            | Symbol               | $V_{CC}$ = 10 V, + $V_{IN}$ = 48 V, $R_{OSC}$ = 390 k $\Omega$    | Tempb        | Min <sup>c</sup>             | Typ <sup>d</sup> | Maxc          | Unit   |  |

| Reference                            |                      |                                                                   |              |                              |                  |               |        |  |

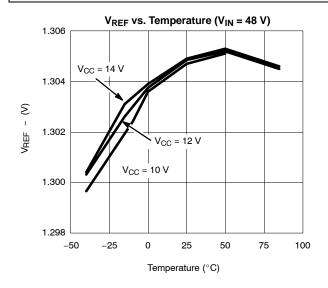

| Output Voltage                       | V <sub>REF</sub>     | $OSC_{IN} = -V_{IN}$ (OSC Disabled)<br>$R_L = 10 \text{ M}\Omega$ | Room<br>Full | 1.275<br>1.26                | 1.3<br>1.3       | 1.325<br>1.34 | V      |  |

| Short Circuit Current                | I <sub>SREF</sub>    | V <sub>REF</sub> = -V <sub>IN</sub>                               | Room         |                              | -25              | -10           | mA     |  |

| Load Regulation                      |                      | I <sub>REF</sub> = 0 to -0.5 mA                                   | Full         |                              | ±10              | 40            | .,     |  |

| Line Regulation                      | $\Delta V_{REF}$     | V <sub>CC</sub> = 10 to 14 V                                      | Full         |                              | ±2               | 5             | mV     |  |

| UVLO                                 | •                    | ·                                                                 | •            |                              |                  |               |        |  |

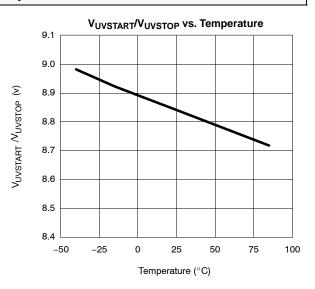

| Linday Voltage Lagicavi              | V <sub>UVSTART</sub> | Turn-On                                                           | Full         | 8.10                         | 8.8              | 9.50          |        |  |

| Under Voltage Lockout                | V <sub>UVSTOP</sub>  | Turn-Off                                                          | Full         | 8.10                         | 8.8              | 9.50          | V      |  |

|                                      | I <sub>START</sub>   | , avv                                                             | Room         |                              |                  | 0.05          | μΑ     |  |

| Input Bias Current                   | I <sub>STOP</sub>    | V <sub>STOP</sub> = 8 V, V <sub>START</sub> = 8 V                 | Room         |                              |                  | 0.05          |        |  |

| Pre-Regulated V <sub>CC</sub>        | V <sub>REG</sub>     |                                                                   | Room         | 8.5                          | 9.0              | 9.5           |        |  |

| UVLO for V <sub>CC</sub>             | V <sub>CCUV</sub>    | CCUV                                                              |              | 7.9                          | 8.4              | 8.9           | V      |  |

| V <sub>REG</sub> – V <sub>CCUV</sub> | VΔ                   |                                                                   | Room         | 0.3                          | 0.6              |               |        |  |

| PWR_Good Comparate                   | or                   |                                                                   |              |                              |                  |               |        |  |

| Rise Time                            | t <sub>rpg</sub>     | 0 400-5                                                           | Room         |                              | 35               |               | mS     |  |

| Fall Time                            | t <sub>fpg</sub>     | - C <sub>PWR_Good</sub> = 100 nF                                  | Room         |                              | 25               |               | μS     |  |

| Output Logic Low                     |                      | I <sub>SINK</sub> = 2.5 mA                                        | Room         |                              | 0.4              | 0.8           | V      |  |

| Soft-Start                           |                      |                                                                   |              |                              |                  |               |        |  |

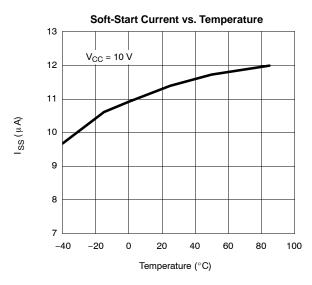

| SS Current                           | I <sub>SS</sub>      |                                                                   | Room         |                              | 11               |               | μΑ     |  |

| Output Inhibit Voltage               | V <sub>SS</sub>      |                                                                   | Room         |                              | 3.3              |               | V      |  |

| Oscillator                           |                      |                                                                   |              |                              |                  |               |        |  |

| Maximum Frequencye                   | f <sub>MAX</sub>     | R <sub>OSC</sub> = 0                                              | Room         | 500                          |                  |               |        |  |

| Initial Accuracy                     |                      | R <sub>OSC</sub> = 390 k (Note f)                                 | Room         | 80                           | 100              | 120           | kHz    |  |

| Initial Accuracy                     | fosc                 | R <sub>OSC</sub> = 180 k (Note f)                                 | Room         | 160                          | 200              | 240           |        |  |

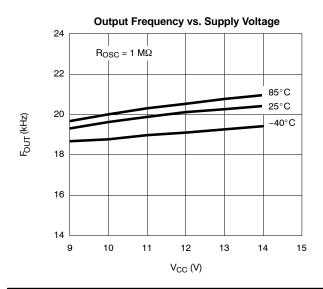

| Voltage Stability                    | Δf/f                 | $\Delta f/f = (f [14 V] - f [10 V]) / f [10 V]$                   | Room         |                              | 10               | 15            | %      |  |

| Temperature Coefficiente             | T <sub>OSC</sub>     |                                                                   | Full         |                              | 450              | 650           | ppm/°C |  |

| Maximum Duty Cycle                   | D <sub>MAX</sub>     | f <sub>OSC</sub> = 100 kHz                                        | Room         |                              | 50               |               | %      |  |

| SPECIFICATIONS <sup>a</sup>         |                     |                                                                                                                        |              |                       |                  |            |      |

|-------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------|------------------|------------|------|

|                                     |                     | Test Conditions Unless Otherwise Specified $V_{CC}$ = 10 V, +V <sub>IN</sub> = 48 V, R <sub>OSC</sub> = 390 k $\Omega$ |              | Limits<br>-40 to 85°C |                  |            |      |

| Parameter                           | Symbol              |                                                                                                                        | Tempb        | Min <sup>c</sup>      | Typ <sup>d</sup> | Maxc       | Unit |

| Error Amplifier                     | 1                   |                                                                                                                        | •            |                       |                  |            |      |

| Open Loop Voltage Gaine             | A <sub>VOL</sub>    | OSC IN = - V <sub>IN</sub>                                                                                             | Room         | 50                    | 60               |            | dB   |

| Input BIAS Current                  | I <sub>BIAS</sub>   | V <sub>FB</sub> = 1.3 V                                                                                                | Room         | -1                    |                  | 1          | μΑ   |

| Feedback Input Voltage              | V <sub>FB</sub>     | FB Tied to COMP, OSC IN = - V <sub>IN</sub>                                                                            | Full         | 1.28                  |                  | 1.32       | V    |

| Dynamic Output Impedancee           | Z <sub>OUT</sub>    |                                                                                                                        | Room         |                       | 1                | 2          | kΩ   |

| Unity Gain Bandwidthe               | BW                  |                                                                                                                        | Room         | 1                     | 1.3              |            | MHz  |

| 00                                  |                     | Source V <sub>FB</sub> = 0.8 V                                                                                         | Room         |                       | -5               | -1         | mA   |

| Output Current                      | lout                | Sink V <sub>FB</sub> = 1.8 V                                                                                           | Room         | 0.12                  | 0.15             |            |      |

| Power Supply Rejection <sup>e</sup> | PSRR                |                                                                                                                        | Room         | 50                    | 70               |            | dB   |

| Current Limit Comparato             | or                  |                                                                                                                        |              |                       |                  |            |      |

| Threshold Voltage                   | V <sub>SOURCE</sub> | V <sub>FB</sub> = 0 V                                                                                                  | Full         | 0.5                   | 0.6              | 0.7        | V    |

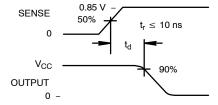

| Delay to Outpute                    | t <sub>d</sub>      | V <sub>SENSE</sub> = 0.85 V, See Figure 1                                                                              | Full         |                       | 100              | 150        | ns   |

| Output Drive                        | •                   |                                                                                                                        |              |                       | •                |            |      |

| Output High Voltage                 | V <sub>OH</sub>     | I <sub>OUT</sub> = -10 mA                                                                                              | Room<br>Full | 9.7<br>9.5            |                  |            | V    |

| Output Low Voltage                  | V <sub>OL</sub>     | I <sub>OUT</sub> = 10 mA                                                                                               | Room<br>Full |                       |                  | 0.3<br>0.5 | V    |

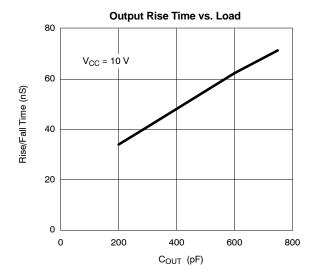

| Rise Time                           | t <sub>r</sub>      | C <sub>L</sub> = 500 pF                                                                                                | Room         |                       | 40               | 75         |      |

| Fall Time                           | t <sub>f</sub>      | (10% to 90%)                                                                                                           | Room         |                       | 40               | 75         | ns   |

| Supply                              | •                   | ·                                                                                                                      |              |                       |                  |            |      |

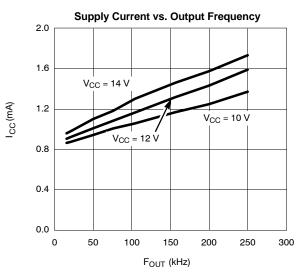

|                                     | I <sub>CC</sub>     | $V_{CC}$ = 10 V, $R_{OSC}$ = 390 k $\Omega$<br>$V_{UVUP} \le V_{IN} \le 200$ V                                         | Full         |                       | 1                | 1.4        | mA   |

| Supply Current                      | I <sub>VIN</sub>    | Excluding I From Resistive Divider of<br>Stop and Start Pins                                                           | Room         |                       | 75               | 100        | μА   |

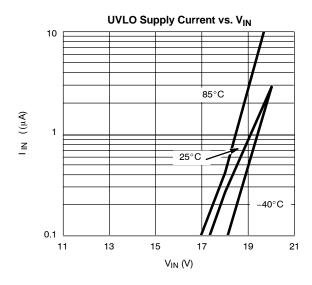

| Supply Current UVLO Mode            | I <sub>VIN</sub>    | $+V_{IN} \le 18 \text{ V}, V_{START} \text{ (Pin 14)} < 8.8 \text{ V}$                                                 | Room         |                       | 2                | 5          | •    |

- Notes

a. Refer to PROCESS OPTION FLOWCHART for additional information.

b. Room = 25°C, Full = −40 to 85°C.

c. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum.

d. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

e. Guaranteed by design, not subject to production test.

f. C<sub>STRAY</sub> Pin 8 = ≤ 5 pF.

#### **TIMING WAVEFORMS**

FIGURE 1. Delay Time for Current Sense

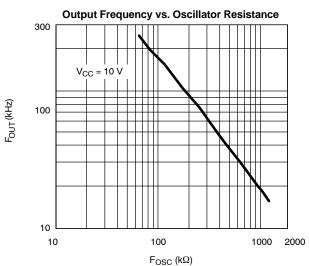

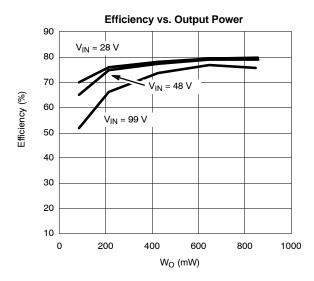

#### TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

#### TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

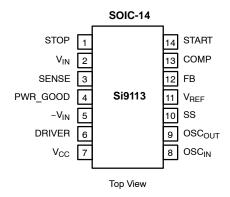

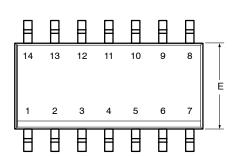

#### **PIN CONFIGURATION**

| ORDERING INFORMATION                  |             |               |  |  |  |

|---------------------------------------|-------------|---------------|--|--|--|

| Part Number Temperature Range Package |             |               |  |  |  |

| Si9113DY                              |             | Bulk          |  |  |  |

| Si9113DY-T1                           | −40 to 85°C | Tone and Deel |  |  |  |

| Si9113DY-T1—E3                        |             | Tape and Reel |  |  |  |

| Eval Kit Temperature Range |             | Board Type        |

|----------------------------|-------------|-------------------|

| Si9113D1                   | –10 to 70°C | Surface Mount and |

| Si9113D2                   | -10 to 70 C | Thru-Hole         |

| PIN DESCRIPTION |                    |                                                                                           |  |  |

|-----------------|--------------------|-------------------------------------------------------------------------------------------|--|--|

| Pin Number      | Name               | Function                                                                                  |  |  |

| 1               | STOP               | Set up the stop threshold of +V <sub>IN</sub> for V <sub>CC</sub> via resistive dividers  |  |  |

| 2               | +V <sub>IN</sub>   | Input voltage to UVLO and Start-Up circuitry                                              |  |  |

| 3               | SENSE              | Current sense amplifier input for current mode control and OCP.                           |  |  |

| 4               | PWR_GOOD           | Logic high PWR_Good signal indicates FB voltage is within regulation.                     |  |  |

| 5               | -V <sub>IN</sub>   | Ground pin                                                                                |  |  |

| 6               | DRIVER             | MOSFET gate drive signal.                                                                 |  |  |

| 7               | V <sub>CC</sub>    | Supply voltage to internal circuitry and MOSFET gate drive.                               |  |  |

| 8               | OSC <sub>IN</sub>  | R <sub>OSC</sub> terminal                                                                 |  |  |

| 9               | OSC <sub>OUT</sub> | R <sub>OSC</sub> terminal, square waveform output                                         |  |  |

| 10              | SS                 | Soft-Start, time programmed by capacitor value.                                           |  |  |

| 11              | V <sub>REF</sub>   | 1.3-V reference. Decoupled with 0.1-μF capacitor.                                         |  |  |

| 12              | FB                 | Inverting input of an error amplifier.                                                    |  |  |

| 13              | COMP               | Error amplifier output for external compensation network.                                 |  |  |

| 14              | START              | Set up the start threshold of +V <sub>IN</sub> for V <sub>CC</sub> via resistive dividers |  |  |

#### **DETAILED BLOCK DIAGRAM**

#### **DETAILED DESCRIPTION**

#### Start-Up

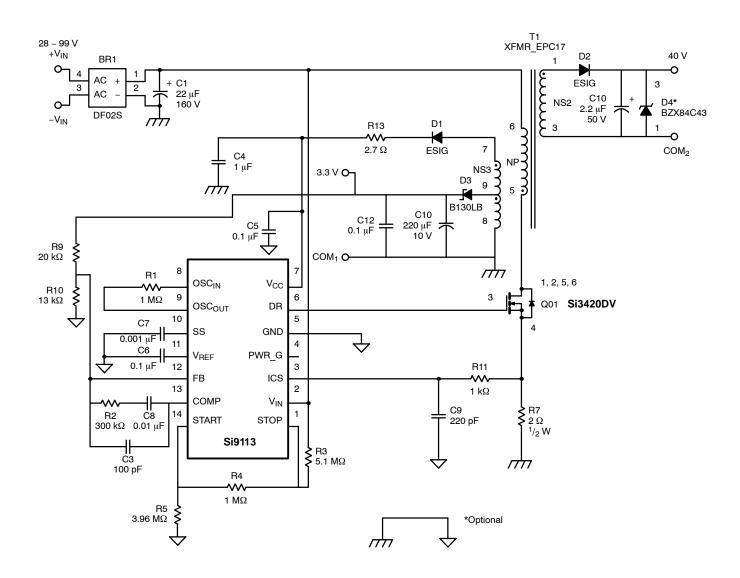

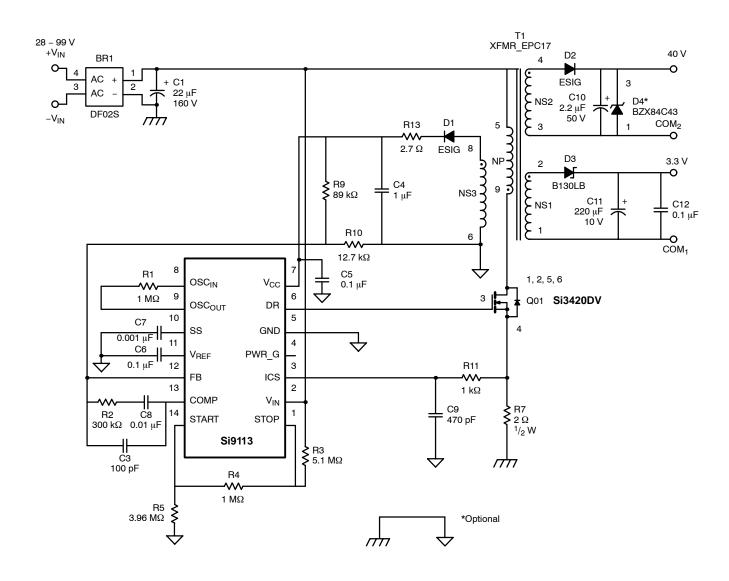

The Si9113 start-up circuit prevents the internal circuits from turning on until the voltage on the  $+\mbox{V}_{IN}$  pin, via the resistor divider  $R_3,\,R_4,\,R_5,$  is sufficiently positive such that the voltage across  $R_3$  (V\_{START}) is >8.8 V (typical value for the internal reference  $\mbox{V}_{UVSTART}$  [see Figure 2]). When this occurs, the internal 1.3-V reference, soft-start and oscillator circuits are enabled. A constant current source provides the current to the external soft-start capacitor, which allows the output voltage to rise gradually without overshoot. The output drive circuit is disabled until the soft-start voltage reaches 3.3 V. The controller is continuously powered in the state until the  $\mbox{V}_{IN}$  voltage falls and  $\mbox{V}_{STOP}$  drops below 8.8 V (the typical value for

the internal reference  $V_{UVSTOP}$ ). The user can program the  $+V_{IN}$  START and  $+V_{IN}$  STOP voltage with the external resistor divider  $R_3-R_5$  (see Figure 2) as follows:

$$V_{IN(START)} = \left(\frac{R_3 + R_4 + R_5}{R_5}\right) \times V_{UVSTART}$$

(1)

$$V_{IN(STOP)} = \left(\frac{R_3 + R_5}{R_5}\right) \times V_{UVSTOP}$$

(2)

Since  $V_{UVSTART} = V_{UVSTOP} = 8.8 \text{ V}$  (typical) the hysteresis voltage can be expressed as:

$$\Delta V_{IN} = \left(\frac{R_4}{R_5}\right) \times V_{UVSTART} \tag{3}$$

#### **V<sub>CC</sub>** Circuit

The depletion MOSFET process allows the Si9113 controller to power directly from the high input bus voltage. Once  $V_{UVSTART}$  is met, the pre-regulator start-up circuit generates the 9.0-V  $V_{CC}$  voltage. The  $V_{CC}$  voltage is used internally to power the IC as well as providing the drive current for the external MOSFET. An internal  $V_{CC}$  circuit is disabled once a higher external voltage ( $\sim\!10$  V) is applied to this pin. If  $V_{CC}$  is below  $V_{CCUV}$ , the Si9113 will inhibit the driver output switching.

#### **REF**

The reference voltage of Si9113 is set at 1.3 V. The reference voltage is internally connected to the non-inverting input of error amplifier. The reference is decoupled with 0.1- $\mu F$  capacitor.

#### Soft-Start

The soft-start circuit provides a constant 10-µA current to external capacitor attached to SS pin. A constant soft-start current forces a gradual increase in duty cycle which in turn ensures gradual output voltage rise without overshooting. The soft-start time is programmed by the capacitance value.

#### Oscillator

The oscillator consists of a ring of CMOS inverters, capacitors, and a capacitor discharge switch. An external resistor,  $R_{OSC}$ , between the  $OSC_{IN}$  and  $OSC_{OUT}$  pins sets the frequency. The maximum frequency is obtained when  $R_{OSC}=0~\Omega.$  A frequency divider in the logic section limits the switch duty cycle to 50% by locking the switching frequency to one-half of the oscillator frequency.

#### **PWM Mode**

As the load and line voltage vary, the switching frequency remains constant. The switching frequency is programmed by the  $R_{OSC}$  value as shown by the oscillator curve. In the PWM mode, a duty cycle pulse is generated for each switching

period eliminating any chance of undesirable noise frequency. When the output load current decreases to 0 A, the controller is forced to enter the pulse skipping mode. This is a natural phenomenal for all controllers since the duty cycle cannot decrease linearly to 0%.

#### **Error Amplifier**

The error amplifier gain-bandwidth product and slew rate are critical parameters which determine the transient response of converter. The transient response is the function of both small and large signal responses. The small signal response is determined by the converter closed loop bandwidth and phase margin while the large signal is determined by the error amplifier dv/dt and the inductor di/dt slew rate. Besides the inductance value, the error amplifier determines the converter response time. In order to minimize the response time, the Si9113 is designed with 1.3-MHz error amplifier gain-bandwidth product to generate the widest converter bandwidth.

#### **Current Limit**

Over current protection circuit is provided by monitoring the voltage on the Sense pin. Once the current sense voltage reaches 0.6V peak, the output drive stage is disabled for the remainder of the clock cycle.

#### Power\_Good Comparator

The PWR\_Good signal indicates the status of output voltage. If the output voltage and  $V_{CC}$  are within regulation, the PWR\_Good signal generates a logic high output by monitoring the voltage on COMP and  $V_{CC}$  pins. If either one is out of regulation, a logic low PWR\_Good signal is generated. The capacitor at the PWR\_Good pin determines the rise time of the power good signal, once all the conditions are met for power good. The PWR\_Good signal is an open collector output capable of sinking 2.5 mA.

#### **MOSFET Gate Drive**

The DRIVER pin is designed to drive the low-side n-channel MOSFET. Typically, the driver stage is sized to sink and source 200-mA of peak current when  $V_{CC} = 12 \text{ V}$ .

www.vishay.com

#### TYPICAL APPLICATION CIRCUITS

FIGURE 2. Dual Output Flyback Converter with 2% Regulation for 3.3 V (As used on Demo Board—DB1)

#### TYPICAL APPLICATION CIRCUITS

FIGURE 3. Dual Output Flyback Converter with Moderately Regulated Outputs (As used on Demo Board DB-2)

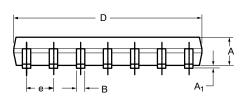

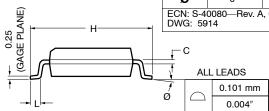

### SOIC (NARROW): 14-LEAD (POWER IC ONLY)

|                                             | MILLIMETERS |      | INC       | CHES  |  |

|---------------------------------------------|-------------|------|-----------|-------|--|

| Dim                                         | Min         | Max  | Min       | Max   |  |

| Α                                           | 1.35        | 1.75 | 0.053     | 0.069 |  |

| A <sub>1</sub>                              | 0.10        | 0.20 | 0.004     | 0.008 |  |

| В                                           | 0.38        | 0.51 | 0.015     | 0.020 |  |

| С                                           | 0.18        | 0.23 | 0.007     | 0.009 |  |

| D                                           | 8.55        | 8.75 | 0.336     | 0.344 |  |

| Е                                           | 3.8         | 4.00 | 0.149     | 0.157 |  |

| е                                           | 1.27        | BSC  | 0.050 BSC |       |  |

| Н                                           | 5.80        | 6.20 | 0.228     | 0.244 |  |

| L                                           | 0.50        | 0.93 | 0.020     | 0.037 |  |

| Ø                                           | 0°          | 8°   | 0°        | 8°    |  |

| ECN: S-40080—Rev. A, 02-Feb-04<br>DWG: 5914 |             |      |           |       |  |

Document Number: 72809

28-Jan-04

www.vishay.com

1

Vishay

### **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of any of the products, services or opinions of the corporation, organization or individual associated with the third-party website. Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website or for that of subsequent links.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

### 单击下面可查看定价,库存,交付和生命周期等信息

>>Vishay(威世)