COMPLIANT

HALOGEN

**FREE**

## **E Series Power MOSFET**

| PRODUCT SUMMARY                            |                              |     |  |  |

|--------------------------------------------|------------------------------|-----|--|--|

| V <sub>DS</sub> (V) at T <sub>J</sub> max. | 65                           | 50  |  |  |

| R <sub>DS(on)</sub> typ. (Ω) at 25 °C      | V <sub>GS</sub> = 10 V 0.120 |     |  |  |

| Q <sub>g</sub> max. (nC)                   | 4                            | 4   |  |  |

| Q <sub>gs</sub> (nC)                       | 11                           |     |  |  |

| Q <sub>gd</sub> (nC)                       | 8                            | 3   |  |  |

| Configuration                              | Sin                          | gle |  |  |

#### **FEATURES**

- 4<sup>th</sup> generation E series technology

- Low figure-of-merit (FOM) Ron x Qg

- Low effective capacitance (Co(er))

- · Reduced switching and conduction losses

- Avalanche energy rated (UIS)

- · Material categorization: for definitions of compliance please see www.vishay.com/doc?99912

#### **APPLICATIONS**

- · Server and telecom power supplies

- Switch mode power supplies (SMPS)

- Power factor correction power supplies (PFC)

- Lighting

- High-intensity discharge (HID)

- Fluorescent ballast lighting

- Industrial

- Welding

- Induction heating

- Motor drives

- Battery chargers

- Solar (PV inverters)

| ORDERING INFORMATION            |                    |

|---------------------------------|--------------------|

| Package                         | PowerPAK 8 x 8     |

| Lead (Pb)-free and halogen-free | SiHH120N60E-T1-GE3 |

| ABSOLUTE MAXIMUM RATINGS (                         | T <sub>C</sub> = 25 °C, unl | ess otherwis            | se noted)                         |             |        |

|----------------------------------------------------|-----------------------------|-------------------------|-----------------------------------|-------------|--------|

| PARAMETER                                          |                             |                         | SYMBOL                            | LIMIT       | UNIT   |

| Drain-source voltage                               |                             |                         | $V_{DS}$                          | 600         | V      |

| Gate-source voltage                                |                             |                         | $V_{GS}$                          | ± 30        | 7 v    |

| Continuous drain surrent (T. 150 °C)               | V <sub>GS</sub> at 10 V     | T <sub>C</sub> = 25 °C  |                                   | 24          |        |

| Continuous drain current (T <sub>J</sub> = 150 °C) | VGS at 10 V                 | T <sub>C</sub> = 100 °C | I <sub>D</sub>                    | 15          | Α      |

| Pulsed drain current <sup>a</sup>                  |                             |                         | I <sub>DM</sub>                   | 57          |        |

| Linear derating factor                             |                             |                         |                                   | 1.25        | W/°C   |

| Single pulse avalanche energy b                    |                             |                         | E <sub>AS</sub>                   | 56          | mJ     |

| Maximum power dissipation                          |                             |                         | $P_{D}$                           | 156         | W      |

| Operating junction and storage temperature range   |                             |                         | T <sub>J</sub> , T <sub>stg</sub> | -55 to +150 | °C     |

| Drain-source voltage slope T <sub>J</sub> = 125 °C |                             |                         | dv/dt                             | 100         | \//no  |

| Reverse diode dv/dt <sup>c</sup>                   |                             |                         |                                   | 50          | - V/ns |

#### **Notes**

- a. Repetitive rating; pulse width limited by maximum junction temperature

- b.  $V_{DD}$  = 140 V, starting  $T_J$  = 25 °C, L = 28.2 mH,  $R_q$  = 25  $\Omega$ ,  $I_{AS}$  = 2 A

- c.  $I_{SD} \le I_D$ , di/dt = 100 A/ $\mu$ s, starting  $T_J = 25$  °C

| THERMAL RESISTANCE RATINGS       |                   |                |      |      |

|----------------------------------|-------------------|----------------|------|------|

| PARAMETER                        | SYMBOL            | TYP.           | MAX. | UNIT |

| Maximum junction-to-ambient      | R <sub>thJA</sub> | 42             | 55   | °C/W |

| Maximum junction-to-case (drain) | R <sub>thJC</sub> | 0.57 0.80 °C/\ |      | C/VV |

| PARAMETER                                                 | SYMBOL                | TES                                                                  | T CONDITIONS                                              | MIN. | TYP.  | MAX.  | UNIT |

|-----------------------------------------------------------|-----------------------|----------------------------------------------------------------------|-----------------------------------------------------------|------|-------|-------|------|

| Static                                                    |                       |                                                                      |                                                           |      |       |       |      |

| Drain-source breakdown voltage                            | V <sub>DS</sub>       | V <sub>GS</sub> =                                                    | = 0 V, I <sub>D</sub> = 250 μA                            | 600  | -     | -     | V    |

| V <sub>DS</sub> temperature coefficient                   | $\Delta V_{DS}/T_{J}$ | Referenc                                                             | e to 25 °C, I <sub>D</sub> = 1 mA                         | -    | 0.60  | -     | V/°C |

| Gate-source threshold voltage (N)                         | V <sub>GS(th)</sub>   | V <sub>DS</sub> =                                                    | - V <sub>GS</sub> , I <sub>D</sub> = 250 μA               | 3.0  | -     | 5.0   | V    |

| Orto come legicore                                        | I <sub>GSS</sub>      | ,                                                                    | V <sub>GS</sub> = ± 20 V                                  | -    | -     | ± 100 | nA   |

| Gate-source leakage                                       |                       | ,                                                                    | $V_{GS} = \pm 30 \text{ V}$                               | -    | -     | ± 1   | μΑ   |

| Zana mata walta na aluaina awamant                        |                       | V <sub>DS</sub> =                                                    | = 600 V, V <sub>GS</sub> = 0 V                            | -    | -     | 1     | _    |

| Zero gate voltage drain current                           | I <sub>DSS</sub>      | V <sub>DS</sub> = 480 V                                              | ', V <sub>GS</sub> = 0 V, T <sub>J</sub> = 125 °C         | -    | -     | 10    | μA   |

| Drain-source on-state resistance                          | R <sub>DS(on)</sub>   | V <sub>GS</sub> = 10 V                                               | I <sub>D</sub> = 12 A                                     | -    | 0.106 | 0.120 | Ω    |

| Forward transconductance                                  | 9 <sub>fs</sub>       | $V_{DS}$                                                             | = 20 V, I <sub>D</sub> = 12 A                             | -    | 6.9   | -     | S    |

| Dynamic                                                   |                       |                                                                      |                                                           |      |       |       |      |

| Input capacitance                                         | C <sub>iss</sub>      | V <sub>GS</sub> = 0 V,                                               |                                                           | -    | 1600  | -     |      |

| Output capacitance                                        | C <sub>oss</sub>      | 1                                                                    | $V_{DS} = 100 V$                                          | -    | 76    | -     |      |

| Reverse transfer capacitance                              | C <sub>rss</sub>      | 1                                                                    | f = 1 MHz                                                 | -    | 6     | -     |      |

| Effective output capacitance, energy related <sup>a</sup> | C <sub>o(er)</sub>    | ., .,                                                                |                                                           | -    | 57    | -     | pF   |

| Effective output capacitance, time related <sup>b</sup>   | C <sub>o(tr)</sub>    | $V_{DS} = 0$                                                         | V to 480 V, V <sub>GS</sub> = 0 V                         | -    | 355   | -     |      |

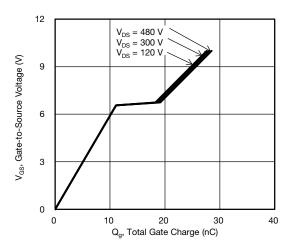

| Total gate charge                                         | $Q_{g}$               |                                                                      |                                                           | -    | 29    | 44    |      |

| Gate-source charge                                        | $Q_{gs}$              | V <sub>GS</sub> = 10 V                                               | $I_D = 12 \text{ A}, V_{DS} = 480 \text{ V}$              | -    | 11    | -     | nC   |

| Gate-drain charge                                         | Q <sub>qd</sub>       | 1                                                                    |                                                           | -    | 8     | -     |      |

| Turn-on delay time                                        | t <sub>d(on)</sub>    |                                                                      |                                                           | -    | 25    | 50    |      |

| Rise time                                                 | t <sub>r</sub>        | V <sub>DD</sub> =                                                    | = 480 V, I <sub>D</sub> = 12 A,                           | -    | 47    | 94    |      |

| Turn-off delay time                                       | t <sub>d(off)</sub>   | V <sub>GS</sub> =                                                    | = 10 V, $R_g = 9.1 \Omega$                                | -    | 38    | 78    | ns   |

| Fall time                                                 | t <sub>f</sub>        | 1                                                                    |                                                           | -    | 29    | 58    | -    |

| Gate input resistance                                     | $R_g$                 |                                                                      | f = 1 MHz                                                 | 0.32 | 0.63  | 1.26  | Ω    |

| <b>Drain-Source Body Diode Characteristic</b>             | s                     |                                                                      |                                                           |      |       |       |      |

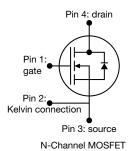

| Continuous source-drain diode current                     | Is                    | MOSFET sym                                                           | bol                                                       | -    | -     | 24    |      |

| Pulsed diode forward current                              | I <sub>SM</sub>       | integral revers                                                      | integral reverse p - n junction diode                     |      | -     | 57    | Α    |

| Diode forward voltage                                     | V <sub>SD</sub>       | T <sub>J</sub> = 25 °C, I <sub>S</sub> = 12 A, V <sub>GS</sub> = 0 V |                                                           | -    | -     | 1.2   | V    |

| Reverse recovery time                                     | t <sub>rr</sub>       |                                                                      |                                                           | -    | 343   | 686   | ns   |

| Reverse recovery charge                                   | Q <sub>rr</sub>       |                                                                      | 5 °C, I <sub>F</sub> = I <sub>S</sub> = 12 A,             | -    | 5.6   | 11.2  | μC   |

| Reverse recovery current                                  | I <sub>RRM</sub>      |                                                                      | $100 \text{ A/}\mu\text{s}, V_{\text{R}} = 400 \text{ V}$ | -    | 30    | -     | A    |

#### Notes

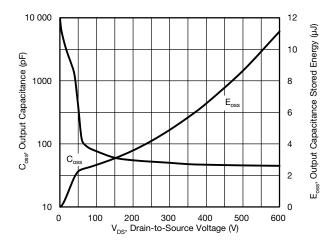

- a.  $C_{oss(er)}$  is a fixed capacitance that gives the same energy as  $C_{oss}$  while  $V_{DS}$  is rising from 0 % to 80 %  $V_{DS}$

- b.  $C_{oss(tr)}$  is a fixed capacitance that gives the same charging time as  $C_{oss}$  while  $V_{DS}$  is rising from 0 % to 80 %  $V_{DS}$

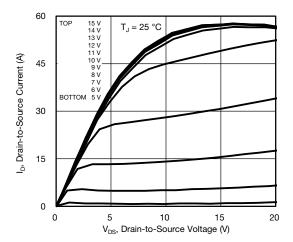

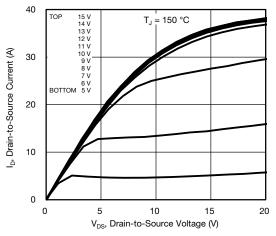

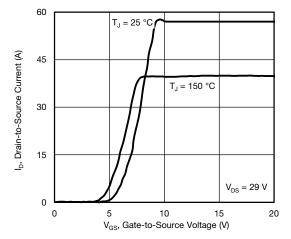

### TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

Fig. 1 - Typical Output Characteristics

Fig. 2 - Typical Output Characteristics

Fig. 3 - Typical Transfer Characteristics

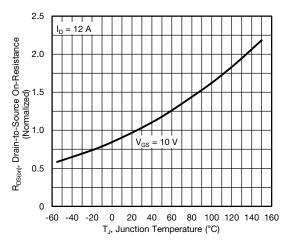

Fig. 4 - Normalized On-Resistance vs. Temperature

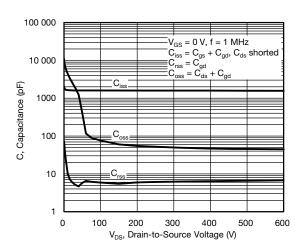

Fig. 5 - Typical Capacitance vs. Drain-to-Source Voltage

Fig. 6 - Coss and Eoss vs. V<sub>DS</sub>

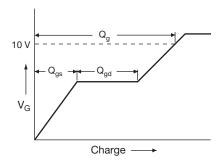

Fig. 7 - Typical Gate Charge vs. Gate-to-Source Voltage

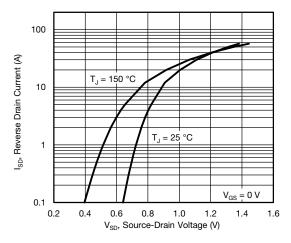

Fig. 8 - Typical Source-Drain Diode Forward Voltage

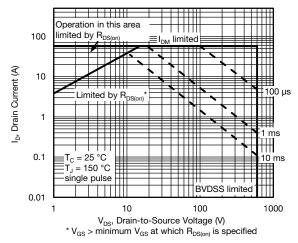

Fig. 9 - Maximum Safe Operating Area

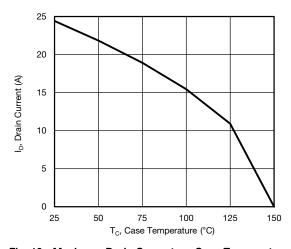

Fig. 10 - Maximum Drain Current vs. Case Temperature

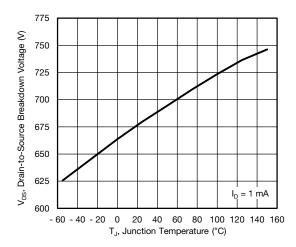

Fig. 11 - Temperature vs. Drain-to-Source Voltage

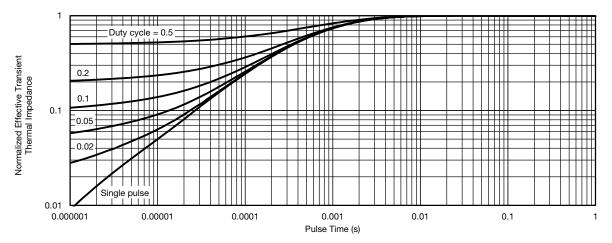

Fig. 12 - Normalized Thermal Transient Impedance, Junction-to-Case

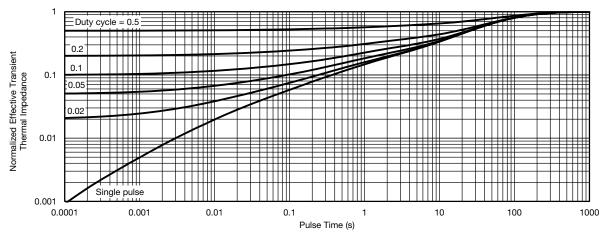

Fig. 13 - Normalized Thermal Transient Impedance, Junction-to-Ambient

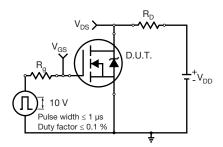

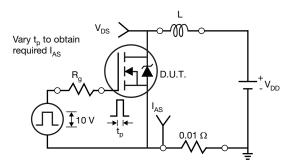

Fig. 14 - Switching Time Test Circuit

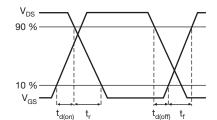

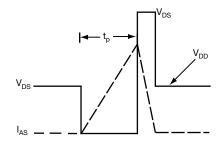

Fig. 15 - Switching Time Waveforms

Fig. 16 - Unclamped Inductive Test Circuit

Fig. 17 - Unclamped Inductive Waveforms

Fig. 18 - Basic Gate Charge Waveform

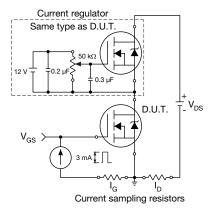

Fig. 19 - Gate Charge Test Circuit

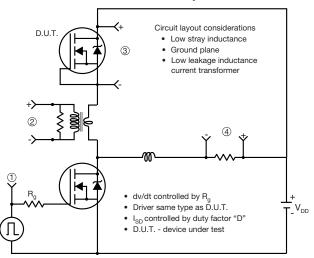

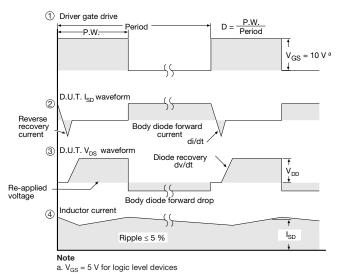

#### Peak Diode Recovery dv/dt Test Circuit

Fig. 20 - For N-Channel

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="https://www.vishay.com/ppg?92093">www.vishay.com/ppg?92093</a>.

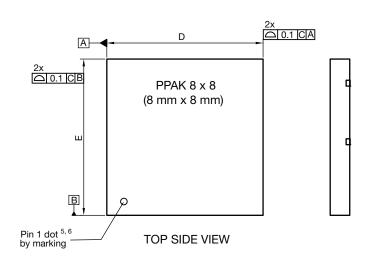

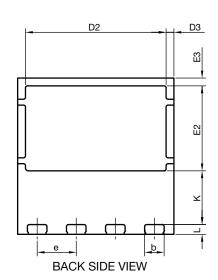

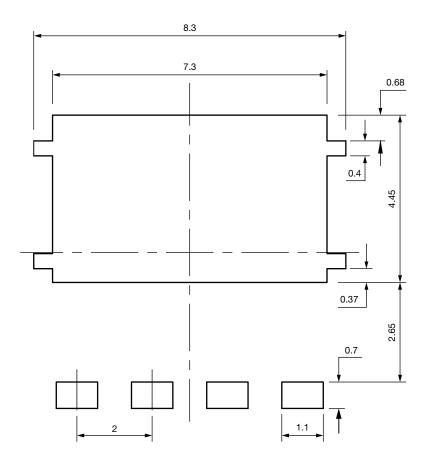

## PowerPAK® 8 x 8 Case Outline

| DIM.             | MILLIMETERS |      |           | INCHES     |       |       |  |

|------------------|-------------|------|-----------|------------|-------|-------|--|

| DIM.             | MIN.        | NOM. | MAX.      | MIN.       | NOM.  | MAX.  |  |

| Α                | 0.95        | 1.00 | 1.05      | 0.037      | 0.039 | 0.041 |  |

| A1               | 0.00        | -    | 0.05      | 0.000      | -     | 0.002 |  |

| A2               | 020 ref.    |      |           | 0.008 ref. |       |       |  |

| b                | 0.95        | 1.00 | 1.05      | 0.037      | 0.039 | 0.041 |  |

| D                | 7.90        | 8.00 | 8.10      | 0.311      | 0.315 | 0.319 |  |

| D2               | 7.10        | 7.20 | 7.30      | 0.280      | 0.283 | 0.287 |  |

| D3               | 0.40 BSC    |      |           | 0.016 BSC  |       |       |  |

| е                | 2.00 BSC    |      |           | 0.079 BSC  |       |       |  |

| Е                | 7.90        | 8.00 | 8.10      | 0.311      | 0.315 | 0.319 |  |

| E2               | 4.30        | 4.35 | 4.40      | 0.169      | 0.171 | 0.173 |  |

| E3               | 0.40 BSC    |      |           | 0.016 BSC  |       |       |  |

| K                | 2.75 BSC    |      | 0.108 BSC |            |       |       |  |

| L                | 0.45        | 0.50 | 0.55      | 0.018      | 0.020 | 0.022 |  |

| N <sup>(3)</sup> | 8           |      |           | 8          |       |       |  |

#### Notes

- (1) Use millimeters as the primary measurement

- (2) Dimensioning and tolerances conform to ASME Y14.5 M 1994

- (3) N is the number of terminals

- (4) The pin 1 identifier must be existed on the top surface of the package by using indentation mark or other feature of package body

- (5) Exact shape and size of this feature is optional

ECN: E20-0518-Rev. B, 28-Sep-2020

DWG: 6041

Revision: 28-Sep-2020 1 Document Number: 67859

# Recommended Minimum PADs for PowerPAK® 8 mm x 8 mm

Dimensions in millimeters

Vishay

## **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of any of the products, services or opinions of the corporation, organization or individual associated with the third-party website. Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website or for that of subsequent links.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

# 单击下面可查看定价,库存,交付和生命周期等信息

>>Vishay(威世)