### N-Channel Synchronous MOSFETs With Break-Before-Make

#### **DESCRIPTION**

The Si4724CY N-Channel synchronous MOSFET with break-before-make (BBM) is a high speed driver designed to operate in high frequency DC/DC switchmode power supplies. It's purpose is to simplify the use of N-Channel MOSFETs in high frequency buck regulators. This device is designed to be used with any single output PWM IC or ASIC to produce a highly efficient low cost synchronous rectifier converter. A synchronous enable pin (disable = low, enable = high) controls the synchronous function for light load conditions.

The Si4724CY is packaged in Vishay Siliconix's high performance LITTLE FOOT® SO-16 package.

#### **FEATURES**

- 0 V to 30 V operation

- Driver impedance-3

- Undervoltage lockout

- · Fast switching times

- 30 V MOSFETs

- High side: 0.0375 at V<sub>DD</sub> = 4.5 V

- Low side: 0.029 at V<sub>DD</sub> = 4.5 V

- · Switching frequency: 250 kHz to 1 MHz

- Integrated schottky

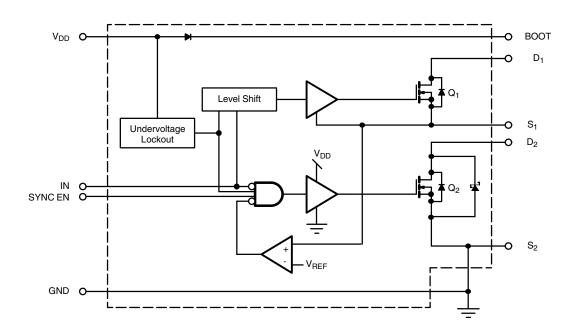

#### **FUNCTIONAL BLOCK DIAGRAM**

| ABSOLUTE MAXIMUM RATINGS (T <sub>A</sub> = 25 °C, unless otherwise noted) |                        |                                   |                                |      |  |  |

|---------------------------------------------------------------------------|------------------------|-----------------------------------|--------------------------------|------|--|--|

| Parameter                                                                 |                        | Symbol                            | Steady State                   | Unit |  |  |

| Logic Supply                                                              |                        | $V_{DD}$                          | 7                              |      |  |  |

| Logic Inputs                                                              |                        | V <sub>IN</sub>                   | - 0.7 to V <sub>DD</sub> + 0.3 |      |  |  |

| Drain Voltage                                                             |                        | V <sub>D1</sub>                   | 30                             | V    |  |  |

| Bootstrap Voltage                                                         |                        | V <sub>BOOT</sub>                 | V <sub>S1</sub> + 7            |      |  |  |

| Synchronous pin Voltage                                                   | V <sub>SYNC</sub>      | - 0.7 to V <sub>DD</sub> + 0.3    |                                |      |  |  |

|                                                                           | T <sub>A</sub> = 25 °C | I <sub>D1</sub>                   | 5.1                            |      |  |  |

| Continuous Drain Current                                                  | T <sub>A</sub> = 70 °C |                                   | 4.09                           | Α    |  |  |

| Continuous Diam Current                                                   | T <sub>A</sub> = 25 °C |                                   | 6.5                            |      |  |  |

|                                                                           | T <sub>A</sub> = 70 °C | I <sub>D2</sub>                   | 5.2                            |      |  |  |

| Maximum Power Dissipation <sup>a</sup>                                    |                        | P <sub>D</sub>                    | 1.2                            | W    |  |  |

| Operating Junction and Storage Temperature Range                          | Driver                 | T <sub>J</sub> , T <sub>stg</sub> | - 65 to 125                    | °C   |  |  |

| Operating Junction and Storage Temperature hange                          | MOSFETs                | 'J, 'stg                          | - 65 to 150                    | C    |  |  |

#### Notes:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING CONDITIONS |                   |                                          |      |  |  |

|----------------------------------|-------------------|------------------------------------------|------|--|--|

| Parameter                        | Symbol            | Steady State                             | Unit |  |  |

| Drain Voltage                    | V <sub>D1</sub>   | 0 to 30                                  |      |  |  |

| Logic Supply                     | V <sub>DD</sub>   | 4.5 to 5.5                               | V    |  |  |

| Input Logic High Voltage         | V <sub>IH</sub>   | 0.7 x V <sub>DD</sub> to V <sub>DD</sub> | v    |  |  |

| Input Logic Low Voltage          | V <sub>IL</sub>   | - 0.3 to 0.3 x V <sub>DD</sub>           |      |  |  |

| Bootstrap Capacitor              | C <sub>BOOT</sub> | 0.1 to 1                                 | μ    |  |  |

| Ambient Temperature              | T <sub>A</sub>    | - 40 to 85                               | °C   |  |  |

| THERMAL RESISTANCE RATINGS                     |              |                    |    |     |      |  |  |

|------------------------------------------------|--------------|--------------------|----|-----|------|--|--|

| Parameter Symbol Typical Maximum Unit          |              |                    |    |     |      |  |  |

| Highside Junction-to-Ambient <sup>a</sup>      |              | R <sub>thJA1</sub> | 85 | 105 |      |  |  |

| Lowside Junction-to-Ambient <sup>a</sup>       | Steady State | R <sub>thJA2</sub> | 68 | 85  | °C/W |  |  |

| Highside Junction-to-Foot (Drain) <sup>b</sup> | Steady State | R <sub>thJF1</sub> | 28 | 35  | C/VV |  |  |

| Lowside Junction-to-Foot (Drain) <sup>b</sup>  |              | R <sub>thJF2</sub> | 19 | 24  |      |  |  |

#### Notes:

a. Surface mounted on 1" x 1" FR4 board, full copper two sides.

a. Surface mounted on 1" x 1" FR4 board.

b. Junction-to-foot thermal impedance represents the effective thermal impedance of all heat carrying leads in parallel and is intended for use in conjunction with the thermal impedance of the PC board pads to ambient ( $R_{th,JA} = R_{th,JF} + R_{th,PCB-A}$ ). It can also be used to estimate chip temperature if power dissipation and the lead temperature of a heat carrying (drain) lead is known.

| SPECIFICATIONS                                        |         |                          |                                                                                                                |                                   |        |      |      |       |

|-------------------------------------------------------|---------|--------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------|--------|------|------|-------|

| Parameter                                             |         |                          | Test Conditions Unless Specified $T_A = 25~^{\circ}\text{C}$ 4.5 V < $V_{DD}$ < 5.5 V, 4.5 V < $V_{D1}$ < 30 V |                                   | Limits |      |      |       |

|                                                       |         | Symbol                   |                                                                                                                |                                   | Min.   | Тур. | Max. | Unit  |

| Power Supplies                                        |         |                          |                                                                                                                | T DI TOTAL                        |        |      |      |       |

| Logic Voltage                                         |         | $V_{DD}$                 |                                                                                                                |                                   | 4.5    |      | 5.5  | V     |

|                                                       |         | I <sub>DD(EN)</sub>      | V <sub>DD</sub> = 4.5 V, V <sub>IN</sub> =                                                                     | 4.5 V                             |        | 280  | 500  |       |

| Logic Current                                         |         | I <sub>DD(DIS)</sub>     | V <sub>DD</sub> = 4.5 V, V <sub>IN</sub> =                                                                     | = 0 V                             |        | 220  | 500  | μΑ    |

| Logic Input                                           |         | ,                        |                                                                                                                |                                   |        |      | l    |       |

| Logic Input Voltage (V <sub>IN</sub> )                | High    | $V_{IH}$                 | V <sub>DD</sub> = 4.5                                                                                          |                                   | 3.15   | 2.3  |      | V     |

| Logic input voitage (VIN)                             | Low     | $V_{IL}$                 | - 40 °C ≤ T <sub>A</sub> ≤ 85                                                                                  | °C                                | - 0.3  | 2.25 | 0.8  | 7 °   |

| Protection                                            |         |                          |                                                                                                                |                                   |        |      |      |       |

| Break-Before-Make Reference                           |         | $V_{BBM}$                | $V_{DD} = 5.5$                                                                                                 |                                   |        | 2.4  |      |       |

| Undervoltage Lockout                                  |         | V <sub>UVLO</sub>        | 0)410 45                                                                                                       |                                   | 3.75   | 4    | 4.25 | V     |

| Undervoltage Lockout Hysteresis                       |         | V <sub>H</sub>           | SYNC = 4.5                                                                                                     |                                   |        | 0.4  |      |       |

| MOSFET Drivers                                        |         |                          |                                                                                                                |                                   |        |      |      | ,     |

| Driver Impedance                                      |         | R <sub>DR1</sub>         | V <sub>DD</sub> = 4.5 V                                                                                        | Driver 1                          |        | 3    |      | V     |

| Driver Impedance                                      |         | $R_{DR2}$                | DD = 4.5 V                                                                                                     | Driver 2                          |        | 2    |      | ]     |

| MOSFETs                                               |         |                          |                                                                                                                |                                   |        |      |      |       |

| Drain-Source Voltage                                  |         | $V_{DS}$                 | $I_{D} = 250 \mu A$                                                                                            |                                   | 30     |      |      | V     |

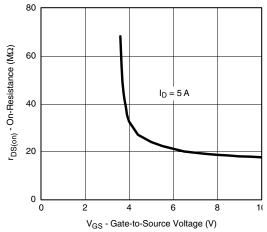

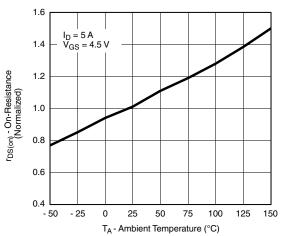

| Dunin Course On Chata Desistance                      | a       | R <sub>DS(on)1</sub>     | $V_{DD} = 4.5 \text{ V}, I_D = 5 \text{ A}$                                                                    | Q1                                |        | 30   | 37.5 | mΩ    |

| Drain Source On State Resistance                      | 9"      | R <sub>DS(on)2</sub>     | $T_A = 25  ^{\circ}C$                                                                                          | Q2                                |        | 24   | 29   | 11152 |

| D: 1 = 1   1   2                                      |         | V <sub>SD1</sub>         |                                                                                                                | Q1                                |        | 0.7  | 1.1  | V     |

| Diode Forward Voltage <sup>a</sup>                    |         | $V_{SD2}$                | $I_S = 2 A, V_{GS} = 0$                                                                                        | Q2                                |        | 0.7  | 1.1  | 7 °   |

| Dynamic <sup>b</sup> (Unless Specified-F <sub>s</sub> | = 250 k | Hz, V <sub>IN</sub> = 12 | V. V <sub>DD</sub> = 5 V, I = 5 A, Refer to                                                                    | Switching Test                    | Setup) |      |      |       |

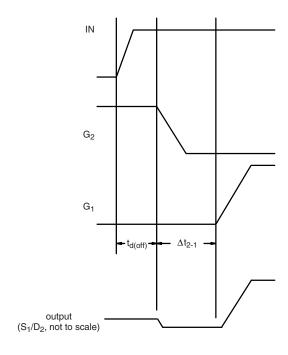

| Turn Off Dalan                                        |         | t <sub>d(off)1</sub>     |                                                                                                                | V <sub>IN</sub> to G <sub>1</sub> |        | 28   | 56   |       |

| Turn Off Delay                                        |         | t <sub>d(off)2</sub>     | 1                                                                                                              | V <sub>IN</sub> to G <sub>2</sub> |        | 17   | 40   |       |

| 11                                                    |         | Δt <sub>1-2</sub>        | See Timing Diagram                                                                                             | G <sub>1</sub> to G <sub>2</sub>  |        | 16   | 32   | ns    |

| Δt                                                    |         | Δt <sub>2-1</sub>        | 1                                                                                                              | G <sub>2</sub> to G <sub>1</sub>  |        | 38   | 80   | 115   |

| Source-Drain Reverse Recovery Time-Q <sub>2</sub>     |         | t <sub>frr</sub>         | I <sub>F</sub> 2.7 A, di/dt = 100 A/μs                                                                         |                                   |        | 50   | 80   |       |

Notes:

a. Pulse test; pulse width ≤ 300 μs, duty cycle ≤ 2 %.

b. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

| SCHOTTKY SPECIFICATIONS (T <sub>J</sub> = 25 °C, unless otherwise noted) |                 |                                                  |     |       |       |      |  |

|--------------------------------------------------------------------------|-----------------|--------------------------------------------------|-----|-------|-------|------|--|

| Parameter                                                                | Symbol          | Test Conditions                                  | Min | Тур   | Max   | Unit |  |

| Forward Voltage Drop                                                     | V <sub>F</sub>  | I <sub>F</sub> = 1 A                             |     | 0.47  | 0.50  | V    |  |

|                                                                          |                 | I <sub>F</sub> = 1 A, T <sub>J</sub> = 125 °C    |     | 0.36  | 0.42  |      |  |

| Maximum Reverse Leakage Current                                          | I <sub>rm</sub> | V <sub>r</sub> = 30 V                            |     | 0.004 | 0.100 |      |  |

|                                                                          |                 | V <sub>r</sub> = 30 V, T <sub>J</sub> = 100 °C   |     | 0.7   | 10    | mA   |  |

|                                                                          |                 | V <sub>r</sub> = - 30 V, T <sub>J</sub> = 125 °C |     | 3     | 20    |      |  |

| Junction Capacitance                                                     | C <sub>T</sub>  | V <sub>r</sub> = 10 V                            |     | 50    |       | pF   |  |

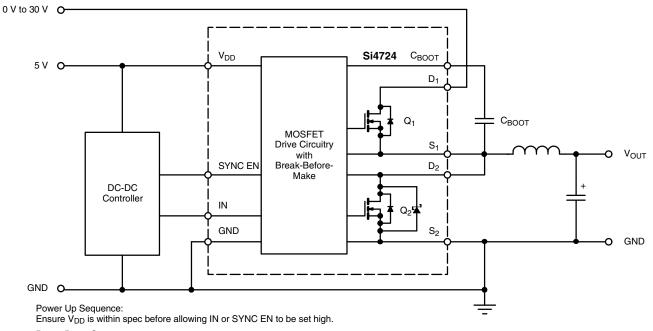

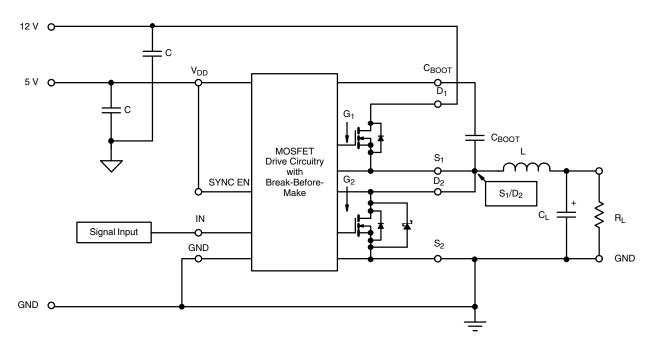

#### **APPLICATION CIRCUIT**

Power Down Sequence: Ensure IN and SYNC EN are low before turning  ${\rm V}_{\rm DD}$  off.

Figure 1.

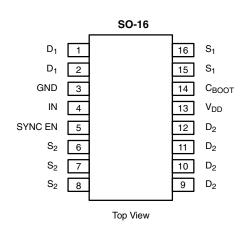

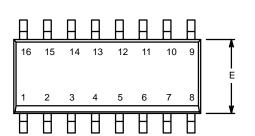

#### **PIN CONFIGURATION**

Ordering Information: Si4724CY-T1 Si4724CY-T1-E3 (Lead (Pb)-free)

| TRUTH TABLE |     |                |       |  |  |

|-------------|-----|----------------|-------|--|--|

| Sync EN     | CLK | Q <sub>1</sub> | $Q_2$ |  |  |

| Н           | Н   | ON             | OFF   |  |  |

| Н           | L   | OFF            | ON    |  |  |

| L           | Н   | ON             | OFF   |  |  |

| L           | L   | OFF            | OFF   |  |  |

| PIN DESCRIPTION |                   |                                                                     |  |  |

|-----------------|-------------------|---------------------------------------------------------------------|--|--|

| Pin<br>Number   | Symbol            | Description                                                         |  |  |

| 1, 2            | D <sub>1</sub>    | Highside MOSFET Drain                                               |  |  |

| 3               | GND               | Ground                                                              |  |  |

| 4               | IN                | Input Logic Signal                                                  |  |  |

| 5               | SYNC EN           | Synchronous Enable                                                  |  |  |

| 6, 7, 8         | S <sub>2</sub>    | Lowside MOSFET Source                                               |  |  |

| 9, 10, 11, 12   | $D_2$             | Lowside MOSFET Drain                                                |  |  |

| 13              | $V_{DD}$          | Logic Supply, decoupling to GND with a cap is strongly recommended. |  |  |

| 14              | C <sub>BOOT</sub> | Bootstrap Capacitor for Upper MOSFET                                |  |  |

| 15, 16          | S <sub>1</sub>    | Highside MOSFET Source                                              |  |  |

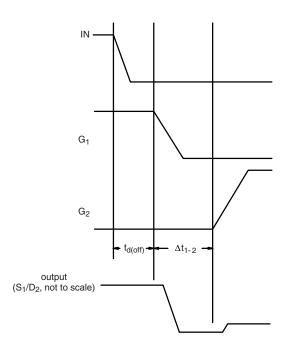

#### **TIMING DIAGRAM**

Figure 2.  $\Delta t_{1-2}$

Figure 3. ∆t<sub>2-1</sub>

#### **SWITCHING TEST SET-UP**

Figure 4.

### TYPICAL CHARACTERISTICS (25 °C unless noted)

On-Resistance vs. Gate-to-Source Voltage (Q<sub>1</sub>)

On-Resistance vs. Ambient Temperature

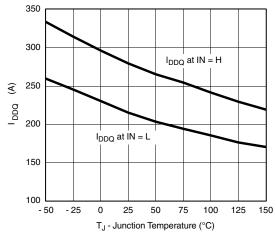

Input Current vs. Junction Temperature

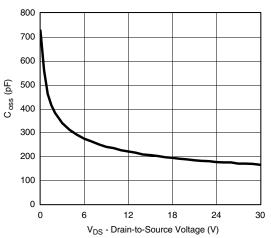

Output Capacitance vs. Drain Voltage ( $\mathbf{Q}_1$  and  $\mathbf{Q}_2$ )

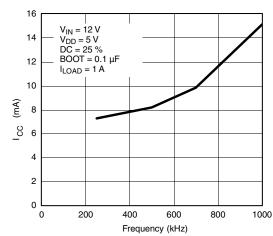

I<sub>CC</sub> vs. Frequency

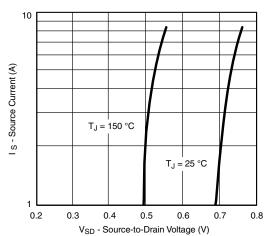

Source-Drain Diode Forward Voltage

### TYPICAL CHARACTERISTICS (25 °C unless noted)

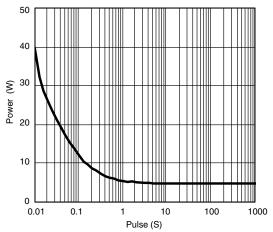

Single Pulse Power, Junction-to-Foot (Q<sub>1</sub>)

Single Pulse Power, Junction-to-Foot (Q2)

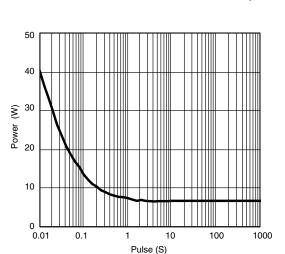

Single Pulse Power, Junction-to-Ambient (Q<sub>1</sub>)

Single Pulse Power, Junction-to-Ambient (Q2)

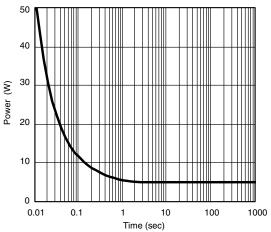

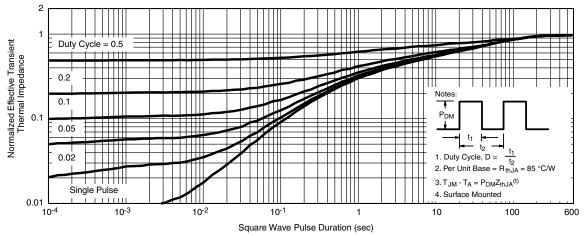

Normalized Thermal Transient Impedance, Junction-to-Ambient (Q1)

### TYPICAL CHARACTERISTICS (25 °C unless noted)

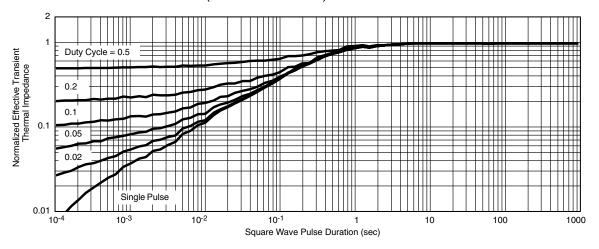

#### Normalized Thermal Transient Impedance, Junction-to-Foot (Q1)

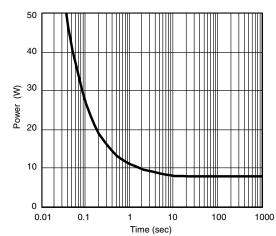

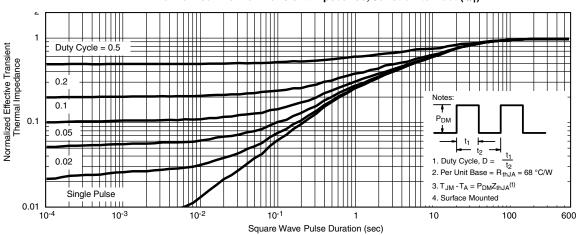

#### Normalized Thermal Transient Impedance, Junction-to-Ambient (Q2)

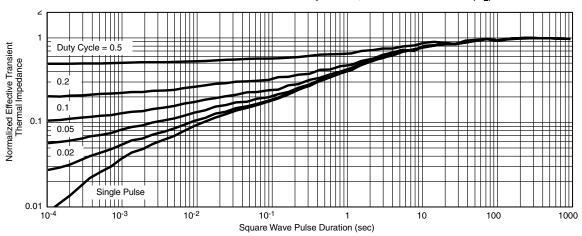

### Normalized Thermal Transient Impedance, Junction-to-Foot (Q2)

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see www.vishay.com/ppg?71863.

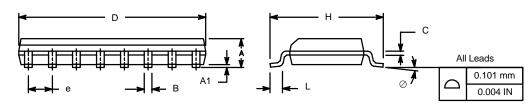

SOIC (NARROW): 16-LEAD

JEDEC Part Number: MS-012

|                                 | MILLIM | IETERS | INC   | HES   |  |

|---------------------------------|--------|--------|-------|-------|--|

| Dim                             | Min    | Max    | Min   | Max   |  |

| Α                               | 1.35   | 1.75   | 0.053 | 0.069 |  |

| A <sub>1</sub>                  | 0.10   | 0.20   | 0.004 | 0.008 |  |

| В                               | 0.38   | 0.51   | 0.015 | 0.020 |  |

| С                               | 0.18   | 0.23   | 0.007 | 0.009 |  |

| D                               | 9.80   | 10.00  | 0.385 | 0.393 |  |

| E                               | 3.80   | 4.00   | 0.149 | 0.157 |  |

| е                               | 1.27   | BSC    | 0.050 | BSC   |  |

| Н                               | 5.80   | 6.20   | 0.228 | 0.244 |  |

| L                               | 0.50   | 0.93   | 0.020 | 0.037 |  |

| 0                               | 0°     | 8°     | 0°    | 8°    |  |

| FCN: S-03946—Rev. F. 09- Jul-01 |        |        |       |       |  |

ECN: S-03946—Rev. F, 09-Jul-01

DWG: 5300

Document Number: 71194 www.vishay.com 02-Jul-01 sww.vishay.com

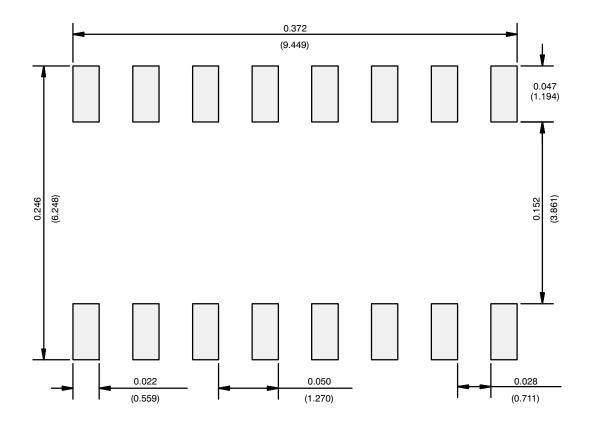

### **RECOMMENDED MINIMUM PADS FOR SO-16**

Recommended Minimum Pads Dimensions in Inches/(mm)

Return to Index

### **Legal Disclaimer Notice**

Vishay

### **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

### **Material Category Policy**

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.

Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as Halogen-Free follow Halogen-Free requirements as per JEDEC JS709A standards. Please note that some Vishay documentation may still make reference to the IEC 61249-2-21 definition. We confirm that all the products identified as being compliant to IEC 61249-2-21 conform to JEDEC JS709A standards.

## 单击下面可查看定价,库存,交付和生命周期等信息

>>Vishay(威世)