# **Dual Output Power Switch with Inverting Input**

#### FEATURES

Pb-free Available

- Two Output Power Switches

- Total Output Drive 200 mA Continuous

- 9-V to 35-V Supply Voltage Range

- Low Side or High Side Switch Configuration

- User Programmable Phasing of Output Switches

- Internal Output Over Voltage Clamp For Driving Inductive Loads

- Current Limit Protection

- Thermal Shutdown Protection

- UVLO With User Programmable Time Delay

#### **APPLICATIONS**

• Optical Detectors for Factory Automation

#### DESCRIPTION

SiP43101 is a dual power switch IC which contains all control and power switching circuitry required to drive resistive and inductive loads in industrial applications. The output switches are NPN power transistors which can be configured as either high-side or low-side switches. These switches can operate from voltages as high as 35 V and have a continuous output current rating of 200 mA, combined or individually. Internal zener diodes are provided to clamp the power switch voltages to safe levels when driving inductive loads. The IN1 pin is a non-inverting input which controls the output of switch 1. A 2-input Exclusive OR gate input controls switch 2, allowing switch 2 to be controlled by either an inverting or non-inverting control signal. SiP43101 contains under voltage lockout, UVLO, a user definable turn on delay, current limit, short circuit protection, and thermal shutdown.

The SiP43101 is available in both standard and lead (Pb)-free 16-pin TSSOP and PowerPAK® MLP-44 packages, which are specified over the industrial, D suffix (-40 to  $85^{\circ}$ C) temperature range.

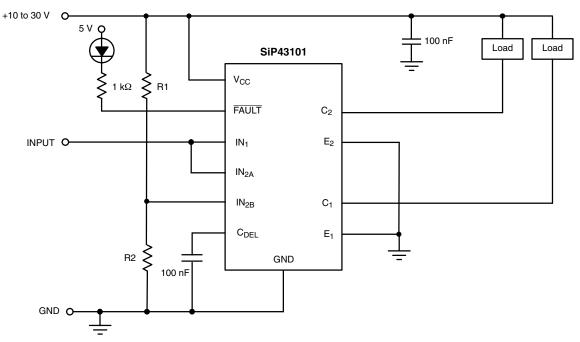

#### **TYPICAL APPLICATION CIRCUIT**

Both Switches Configured as Low-Side, Switch 2 Inverted With Respect to Switch 1, R1 +R2 Set Logic High

# **Vishay Siliconix**

#### ABSOLUTE MAXIMUM RATINGS

| V <sub>CC</sub>                                                                                                | V |

|----------------------------------------------------------------------------------------------------------------|---|

| Output Current<br>Continuous for one Output                                                                    |   |

| Peak for one Output     1.3 /       FAULT Output Current     10 m/       FAULT Output Current     0.0 V/0.0 V/ | A |

| FAULT Output Voltage $-0.3 V$ to $V_{CC} + 0.3 V$ IN1, IN2A, IN2B $-0.3 V$ to $V_{CC} + 0.3 V$                 | V |

| Storage Temperature   -65 to 150°C     Operating Junction Temperature   125°C                                  |   |

| Power Dissipation                     |          |

|---------------------------------------|----------|

| TSSOP-16 <sup>a</sup> @ 85°C          | 440 mW   |

| PowerPAK MLP44-16 <sup>b</sup> @ 85°C | 850 mW   |

| Thermal Impedance ( $\Theta_{JA}$ )   |          |

| TSSOP-16 <sup>c</sup>                 | . 90°C/W |

| PowerPAK MLP44-16 <sup>d</sup>        | . 47°C/W |

Notes

a. Derate 11.1 mW/°C

b. Derate 21.3 mW/°C

d. Device mounted on JEDEC compliant two layer test board.

d. Device mounted on JEDEC compliant four layer test board.

Currents are positive into, negative out of the specificed terminal.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **RECOMMENDED OPERATING RANGE**

| V <sub>CC</sub> | 9 to 32 V |

|-----------------|-----------|

|-----------------|-----------|

Operating Temperature Range ......-40 to 85°C

# SPECIFICATIONS

|                                |                    | Test Conditions Unless Specified $V_{CC} = 25 \text{ V,IN1, IN2} = 0 \text{ V, IN1, IN2, INV2} = 5 \text{ V}$ $C_{DEL} = 10 \text{ nF, } T_A = T_J$ |                                        |                  | Limits           |                  |      |

|--------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|------------------|------------------|------|

| Parameter                      | Symbol             |                                                                                                                                                     |                                        | Min <sup>a</sup> | Тур <sup>ь</sup> | Max <sup>a</sup> | Unit |

| Power Supply                   | ·                  |                                                                                                                                                     |                                        |                  | •                | •                |      |

| Supply Voltage                 | V <sub>CC</sub>    |                                                                                                                                                     |                                        | 9                |                  | 32               | V    |

| Supply Current                 | Icc                | -40 to 85°C, Both Inputs E                                                                                                                          | nabled                                 |                  | 6                | 9                | mA   |

| Logic Inputs (IN1, IN2A, II    | N <sub>2B</sub> )  |                                                                                                                                                     |                                        |                  |                  |                  |      |

| Digital Input High Level       | V <sub>IH</sub>    |                                                                                                                                                     |                                        | 3.5              |                  |                  | v    |

| Digital Input Low Level        | V <sub>IL</sub>    |                                                                                                                                                     |                                        |                  |                  | 1.5              | v    |

| Input Bias Current, Low Level  | Ι <sub>ΙL</sub>    | IN <sub>1</sub> , IN <sub>2A</sub> , IN <sub>2B</sub> = 0 \                                                                                         | /                                      |                  | -0.40            |                  |      |

| Input Bias Current, High Level | I <sub>IH</sub>    | IN <sub>1</sub> , IN <sub>2A</sub> , IN <sub>2B</sub> = 5 \                                                                                         | 1                                      |                  | 0.02             |                  | μA   |

| Switches 1&2 – High Sid        | e Configuration    |                                                                                                                                                     |                                        |                  |                  |                  |      |

| Rise Time (Off to On)          | t <sub>r</sub>     | $R_{\rm LOAD}$ = 250 $\Omega$ to GND, $C_1$ , $C_2$ = 25 V                                                                                          |                                        |                  | 300              |                  |      |

| Rise Tiem (On to Off)          | t <sub>f</sub>     |                                                                                                                                                     |                                        |                  | 300              |                  | ns   |

| Saturation Voltage             | V <sub>SATHS</sub> | $R_{I,OAD} = 125 \Omega$ to GND                                                                                                                     | T <sub>A</sub> = 25 °C                 |                  |                  | 1.3              | v    |

| Saturation voltage             | V SATHS            | HLOAD - 123 S2 10 GIVD                                                                                                                              | $T_A = -40 \ ^{\circ}C$                |                  |                  | 1.5              | v    |

| Current Limit                  | ILIMHS             | $R_{LOAD}$ = 0.25 $\Omega$ to GND, $T_A$ = 25 °C                                                                                                    |                                        |                  | 1.1              |                  | A    |

| Leakage Current                | I <sub>LHS</sub>   | $E_1$ , $E_2$ = GND, $C_1$ , $C_2$ = 25 V, $IN_1$ , $IN_{2A}$ , $IN_{2B}$ = 0 V                                                                     |                                        |                  |                  | 5                | μΑ   |

| Voltabe Clamp                  | V <sub>CLHS</sub>  | Measure (V <sub>C1</sub> – V <sub>E1</sub> ) or (V <sub>C2</sub> – V <sub>E2</sub> )                                                                |                                        |                  | 52               |                  | V    |

| Switches 1&2 - Low Side        | e Configuration    |                                                                                                                                                     |                                        |                  |                  |                  |      |

| Rise Time (On to Off)          | t <sub>r</sub>     |                                                                                                                                                     |                                        |                  | 400              |                  |      |

| Rise Tiem (Off to On)          | t <sub>f</sub>     | $R_{LOAD} = 250 \Omega$ to $V_{CC}$ , $L_{OAD} = 2$                                                                                                 | 5 v 10 C <sub>1</sub> , C <sub>2</sub> |                  | 350              |                  | ns   |

| Caturatian Valtage             |                    | T <sub>A</sub> = 25 °C                                                                                                                              |                                        |                  | 1.3              | v                |      |

| Saturation Voltage             | V <sub>SATLS</sub> | $R_{LOAD} = 125 \Omega \text{ to } V_{CC}$ $T_A =$                                                                                                  | $T_A = -40 \ ^{\circ}C$                |                  |                  | 1.5              | v    |

| Current Limit                  | I <sub>LIMLS</sub> | $R_{LOAD}$ = 0.25 $\Omega$ to $V_{CC}, \ T_{A}$ = 25 $^{\circ}C$                                                                                    |                                        |                  | 1.1              |                  | A    |

| Leakage Current                | I <sub>LLS</sub>   | $E_1,E_2=GND,C_1,C_2=25\;V,IN_1,IN_{2A},IN_{2B}=0\;V$                                                                                               |                                        |                  |                  | 5                | μA   |

| Voltabe Clamp                  | V <sub>CLLS</sub>  | Measure (V <sub>C1</sub> – V <sub>E1</sub> ) or (V <sub>C2</sub> – V <sub>E2</sub> )                                                                |                                        |                  | 52               |                  | V    |

| SPECIFICATIONS                           |                    |                                                                                         |                  |                  |                  |      |  |

|------------------------------------------|--------------------|-----------------------------------------------------------------------------------------|------------------|------------------|------------------|------|--|

|                                          |                    | Test Conditions Unless Specified                                                        |                  | Limits           |                  |      |  |

| Parameter                                | Symbol             | $V_{CC}$ = 25 V,IN1, IN2 = 0 V, IN1, IN2, INV2 = $5$ V $C_{DEL}$ = 10 nF, $T_A$ = $T_J$ | Min <sup>a</sup> | Тур <sup>ь</sup> | Max <sup>a</sup> | Unit |  |

| Turn-On Delay                            |                    |                                                                                         |                  |                  |                  |      |  |

| C <sub>DEL</sub> Maximum Voltage         | V <sub>DEL</sub>   |                                                                                         |                  | 4.7              |                  | v    |  |

| C <sub>DEL</sub> Threshold               | V <sub>DELTH</sub> |                                                                                         |                  | 4                |                  | ľ    |  |

| I <sub>CDEL</sub>                        | I <sub>CDEL</sub>  |                                                                                         |                  | 2.5              |                  | μΑ   |  |

| FAULT Output                             |                    |                                                                                         |                  |                  |                  |      |  |

| V <sub>CESAT</sub> Conducting State (On) | V <sub>SDON</sub>  | Load on $\overline{FAULT} \leq 10 \text{ mA}$                                           |                  | 0.4              |                  | V    |  |

| Operating Frequency                      |                    |                                                                                         | •                |                  |                  |      |  |

| Switching Frequency                      | f <sub>SW</sub>    |                                                                                         |                  |                  | 25               | kHz  |  |

| Under Voltage Lockout                    |                    |                                                                                         |                  |                  |                  | •    |  |

| UVLO Threshold                           | V <sub>UVLO</sub>  |                                                                                         | 7.5              | 8                | 8.5              | v    |  |

| UVLO Hysteresis                          | V <sub>HYS</sub>   |                                                                                         | 0.4              | 0.5              | 0.6              | v    |  |

| Thermal Shutdown                         |                    |                                                                                         | •                | •                | •                |      |  |

| Thermal Shutdown Threshold               | Т                  |                                                                                         |                  | 160              |                  | °C   |  |

| Hysteresis                               | T <sub>HYS</sub>   |                                                                                         |                  | 20               |                  |      |  |

Notes a. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum ( $-40^{\circ}$  to  $85^{\circ}$ C). b. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing and are measured at V<sub>CC</sub> = 12 V unless otherwise noted.

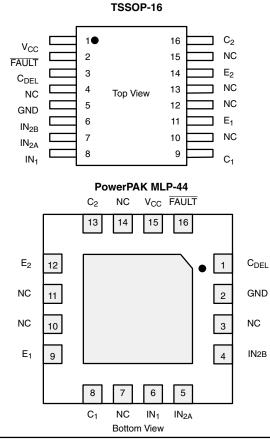

# **PIN CONFIGURATION**

| TSSOP-16<br>ORDERING INFORMATION |                               |                      |         |  |

|----------------------------------|-------------------------------|----------------------|---------|--|

| Standard<br>Part Number          | Lead (Pb)-Free<br>Part Number | Temperature<br>Range | Marking |  |

| SiP43101DQ-T1                    | SiP43101DQ-T1—E3              | –40 to 85°C          | 43101   |  |

| PowerPAK MLP-44<br>ORDERING INFORMATION |                               |                      |         |  |

|-----------------------------------------|-------------------------------|----------------------|---------|--|

| Standard<br>Part Number                 | Lead (Pb)-Free<br>Part Number | Temperature<br>Range | Marking |  |

| SiP43101DLP-T1                          | SiP43101DLP-T1-E3             | –40 to 85°C          | 43101   |  |

#### Document Number: 72640 S-51493, Rev. D-15-Aug-05

# Vishay Siliconix

| PIN DESCRIPTION      |                  |                  |                                                                                                   |  |

|----------------------|------------------|------------------|---------------------------------------------------------------------------------------------------|--|

| Pin Number           |                  |                  |                                                                                                   |  |

| TSSOP-16             | MLP44-16         | Name             | Function                                                                                          |  |

| 1                    | 15               | V <sub>CC</sub>  | Positive Supply Voltage                                                                           |  |

| 2                    | 16               | FAULT            | Open collector output that is switched low on in the event of Short Circuit or Thermal Shut Down. |  |

| 3                    | 1                | CDEL             | Connection for the external capacitor controlling the turn on delay.                              |  |

| 4, 10, 12, 13,<br>15 | 3, 7, 10, 11, 14 | NC               | No connection                                                                                     |  |

| 5                    | 2                | GND              | Ground Pin.                                                                                       |  |

| 6                    | 4                | IN <sub>2B</sub> | Input to the Exclusive OR controlling power switch 2.                                             |  |

| 7                    | 5                | IN <sub>2A</sub> | Input to the Exclusive OR controlling power switch 2.                                             |  |

| 8                    | 6                | IN <sub>1</sub>  | Input controlling power switch 1.                                                                 |  |

| 9                    | 8                | C <sub>1</sub>   | Collector of power switch 1.                                                                      |  |

| 11                   | 9                | E <sub>1</sub>   | Emitter of power switch 1.                                                                        |  |

| 14                   | 12               | E <sub>2</sub>   | Emitter of power switch 2.                                                                        |  |

| 16                   | 13               | C <sub>2</sub>   | Collector of power switch 2.                                                                      |  |

#### **DETAILED PIN DESCRIPTION**

CDEL

A capacitor connected to this pin is used to set the duration the turn on delay. The delay starts after the UVLO threshold has been reached.

#### $IN_1$

This pin controls the state of the output NPN switch 1. A Logic 0 holds the switch off while a Logic 1 turns the switch on.

#### $\mathsf{IN}_{\mathsf{2A}}, \mathsf{IN}_{\mathsf{2B}}$

These pins are the inputs to the Exclusive OR gate that controls the state of the output NPN switch 2. This allows the use of either a non-inverting or an inverted signal to control the switch. Refer to the truth table for the logic function description.

| IN <sub>2A</sub> | IN <sub>2B</sub> | SWITCH 2 |

|------------------|------------------|----------|

| Low              | Low              | Off      |

| Low              | High             | On       |

| High             | Low              | On       |

| High             | High             | Off      |

# E<sub>1</sub>

This pin is the emitter of Switch 1. This pin is connected to the load in the High-Side Switch configuration, and is connected to Ground in the Low-Side configuration.

# $E_2$

This pin is the emitter of switch 2. This pin is connected to the load in the High-Side switch configuration, and is connected to Ground in the Low-Side configuration.

# C<sub>1</sub>

This pin is the collector of switch 1. This pin is connected to the  $V_{CC}$  in the High-Side switch configuration, and is connected to the load in the Low-Side configuration.

# $C_2$

This pin is the collector of switch 2. This pin is connected to the  $V_{CC}$  in the High-Side switch configuration, and is connected to the load in the Low-Side configuration.

# FAULT

This pin is an open collector output that is pulled to Ground in the event of a short circuit, an overcurrent, or a thermal shut down

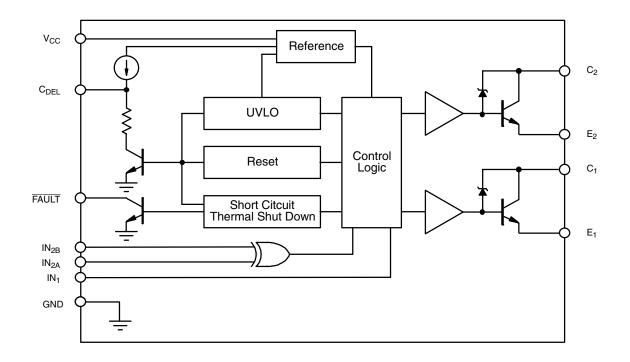

### FUNCTIONAL BLOCK DIAGRAM

# **DETAILED OPERATION**

#### **Turn On Delay**

The turn on delay prohibits the output switches from being turned on for a period of time after V<sub>CC</sub> has passed through 8 V and the undervoltage condition no longer exists. The UVLO function keeps the external C<sub>DEL</sub> capacitor discharged until V<sub>CC</sub> is greater than 8 V. Subsequently, an internal 2.5- $\mu$ A current source charges the capacitor from GND to 4.7 V. A comparator detects when the voltage on C<sub>DEL</sub> passes through 4 V and enables the output switches. The delay time is a function of the capacitor value and is defined as 1.6 ms/nF.

An external switch can be connected across the capacitor to disable the output switches and reset the time delay.

#### Short Circuit and Overcurrent indication

When an overcurrent or short circuit condition occurs on either switch, the SiP43101 enters a hiccup current limiting mode. In this mode, the capacitor on  $C_{DEL}$  is discharged down to 3 V, thus turning off the output switches, and then is charged up to 4 V by a 2.5- $\mu$ A internal current source, thus turning the switches on again. If the overcurrent or short circuit condition remains this cycle will continue. The switches are enabled at a very low duty cycle, minimizing the power dissipation and protecting the switches from damage.

The FAULT output will switch to GND, indicating that an overload condition or short circuit condition exists.

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="http://www.vishay.com/pg272640">http://www.vishay.com/pg272640</a>.

Vishay

# Disclaimer

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

单击下面可查看定价,库存,交付和生命周期等信息

>>Vishay(威世)