## 500-kHz Half-Bridge DC/DC Controller with Integrated Secondary Synchronous Rectification Drivers

#### DESCRIPTION

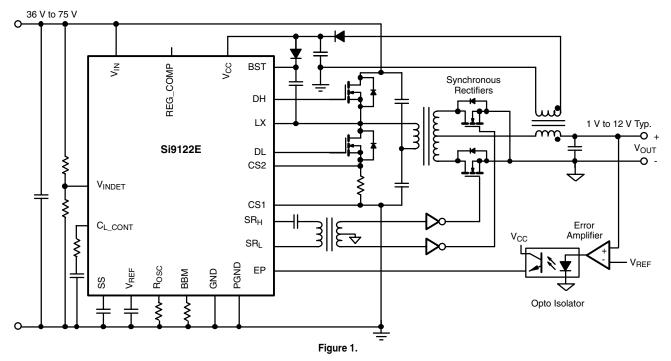

Si9122E is a half-bridge controller IC ideally suited to fixed telecom applications where high efficiency is required at low output voltages (e.g. < 3.3 V). Designed to operate within the fixed telecom voltage range of 36 V to 75 V, the IC is capable of controlling and driving both the low and high-side switching devices of a half bridge circuit and also controlling the switching devices on the secondary side of the bridge. Due to the very low on-resistance of the secondary MOSFETs, a significant increase in conversion efficiency can be achieved as compared with conventional Schottky diodes. Control of the secondary devices is by means of a pulse transformer and a pair of inverters. Such a system has efficiencies well in excess of 90 % even for low output voltages.

On-chip control of the dead time delays between the primary and secondary synchronous signals keep efficiencies high and prevent shorting of the power transformer. An external resistor sets the oscillator frequency from 200 kHz to 500 kHz.

Si9122E has advanced current monitoring and control circuitry which allow the user to set the maximum current in the primary circuit. Such a feature acts as protection against output shorting and also provides constant current into large capacitive loads during start-up or when paralleling power supplies. Current sensing is by means of a sense resistor on the low-side primary device.

#### FEATURES

- 92 % primary/secondary duty cycle

- 135 °C over temperature protection

- Compatible with ETSI 300 132-2

- 28 V to 75 V input voltage range

- Integrated ± 1 A half bridge primary drivers

- Secondary synchronous rectifier control signals with programmable deadtime delay

- Voltage mode control

- Voltage feedforward compensation

- High voltage pre-regulator operates during start-up

- · Current sensing on low-side primary device

- Frequency foldback eliminates constant current tail

- Advanced maximum current control during start-up and shorted load

- Low input voltage detection

- Programmable soft-start function

#### APPLICATIONS

- Network cards

- Power supply modules

- · Distributed power systems

- Intermediate bus converter

- Brick converter

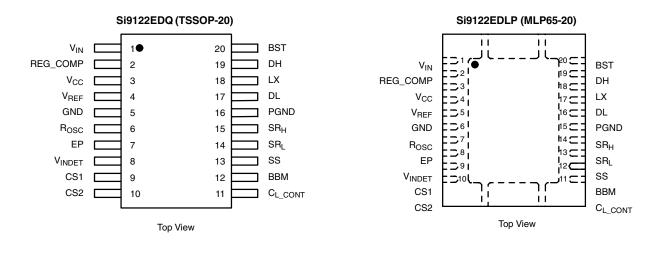

#### FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION

COMPLIANT

#### **TECHNICAL DESCRIPTION**

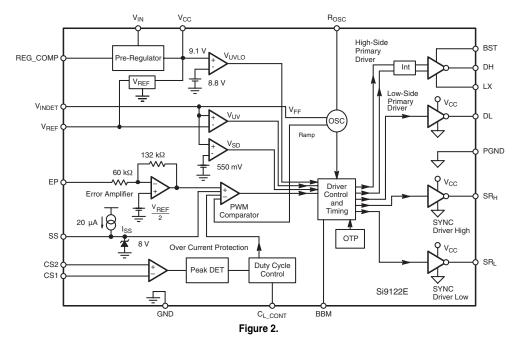

Si9122E is a voltage mode controller for the half-bridge topology. With 100 V depletion mode MOSFET, the Si9122E is capable of powering directly from the high voltage bus to  $V_{CC}$  through an external PNP pass transistor, or may be powered through an external regulator directly through the  $V_{CC}$  pin. With PWM control, Si9122E provides peak efficiency throughout the entire line and load range. In order to simplify the design of efficient secondary synchronous rectification circuitry, the Si9122E provides intelligent gate drive signals to control the secondary MOSFETs. With independent gate drive signals from the controller, transformer design is no longer limited by the gate to source rating of the secondary-side MOSFETs. Si9122E provides constant  $V_{GS}$  voltage, independent of the line voltage to minimize the gate charge loss as well as conduction loss.

To prevent shoot-through current or transformer shorting, adjustable Break-Before-Make (BBM) time is incorporated into the IC and is programmed by an external precision resistor.

Si9122E is assembled in lead (Pb)-free TSSOP-20 and MLP65-20 packages. To satisfy stringent ambient temperature requirements, Si9122E is rated to handle the industrial temperature range of - 40 °C to 85 °C. When a situation arises which results in a rapid increase in primary (or secondary) current such as output shorted or start-up with a large output capacitor, control of the PWM generator is handed over to the current loop. Monitoring of the load current is by means of an external current sense resistor in the source of the primary low-side switch. With the lower OTP set at 135 °C , the DNF20 package improves the thermal headroom.

| ABSOLUTE MAXIMUM RA                       | TINGS All voltages referenced | to GND = 0 V                   |      |

|-------------------------------------------|-------------------------------|--------------------------------|------|

| Parameter                                 |                               | Limit                          | Unit |

| V <sub>IN</sub> (Continuous)              |                               | 80                             |      |

| V <sub>IN</sub> (100 ms)                  |                               | 100                            |      |

| V <sub>CC</sub>                           |                               | 14.5                           |      |

| V <sub>BST</sub>                          | Continuous                    | 95                             |      |

| BST                                       | 100 ms                        | 113.2                          |      |

| V <sub>LX</sub>                           |                               | 100                            | v    |

| V <sub>BST</sub> - V <sub>LX</sub>        |                               | 15                             |      |

| V <sub>REF</sub> R <sub>OSC</sub>         |                               | - 0.3 to V <sub>CC</sub> + 0.3 |      |

| Logic Inputs                              |                               | - 0.3 to V <sub>CC</sub> + 0.3 |      |

| Analog Inputs                             |                               | - 0.3 to V <sub>CC</sub> + 0.3 | 7    |

| HV Pre-Regulator Input Current Continuous |                               | 5                              | mA   |

| ABSOLUTE MAXIMUM RATINGS All voltages referenced to GND = 0 V |                                                |             |      |  |  |  |

|---------------------------------------------------------------|------------------------------------------------|-------------|------|--|--|--|

| Parameter                                                     |                                                | Limit       | Unit |  |  |  |

| Storage Temperature                                           |                                                | - 65 to 150 | °C   |  |  |  |

| Operating Junction Temperature                                |                                                | 150         | U    |  |  |  |

| Power Dissipation <sup>a</sup>                                | TSSOP-20 <sup>b</sup><br>MLP65-20 <sup>c</sup> | 850<br>2500 | mW   |  |  |  |

| Thermal Impedance $(\theta_{JA})$                             | TSSOP-20<br>MLP65-20                           | 75<br>38    | °C/W |  |  |  |

Notes:

a. Device mounted on JEDEC compliant 1S2P test board.

b. Derate 14 mW/°C above 25 °C.

c. Derate 26 mW/°C above 25 °C.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING RANGE All voltag | es referenced to GND = 0 V |      |  |

|----------------------------------------|----------------------------|------|--|

| Parameter                              | Limit                      | Unit |  |

| V <sub>IN</sub>                        | 36 to 75                   | V    |  |

| V <sub>CC</sub>                        | 10.5 to 13.2               | V    |  |

| CV <sub>CC</sub>                       | ≥ 4.7                      | μF   |  |

| fosc                                   | 200 to 500                 | kHz  |  |

| R <sub>OSC</sub>                       | 30 to 72                   | kΩ   |  |

| R <sub>BBM</sub>                       | 22 to 50                   |      |  |

| C <sub>REF</sub>                       | 0.1                        |      |  |

| C <sub>BOOST</sub>                     | 0.1                        | μF   |  |

| Analog Inputs                          | 0 to V <sub>CC</sub> - 2   | V    |  |

| Digital Inputs                         | 0 to V <sub>CC</sub>       |      |  |

| Reference Voltage Output Current       | 0.1 to 2.5                 | mA   |  |

| SPECIFICATIONS <sup>a</sup>      |                   |                                                                                |                         |                   |                   |       |  |

|----------------------------------|-------------------|--------------------------------------------------------------------------------|-------------------------|-------------------|-------------------|-------|--|

|                                  |                   | Test Conditions<br>Unless Otherwise Specified                                  | Limits<br>- 40 to 85 °C |                   | 2                 |       |  |

| Parameter                        | Symbol            |                                                                                |                         | Typ. <sup>c</sup> | Max. <sup>b</sup> | Unit  |  |

| Reference (3.3 V)                | · · ·             |                                                                                |                         |                   |                   |       |  |

| Output Voltage                   | V <sub>REF</sub>  | V <sub>CC</sub> = 12 V, 25 °C Load = 0 mA                                      | 3.2                     | 3.3               | 3.4               | V     |  |

| Short Circuit Current            | I <sub>SREF</sub> | V <sub>REF</sub> = 0 V                                                         |                         |                   | - 50              | mA    |  |

| Load Regulation                  | dVr/dir           | I <sub>REF</sub> = 0 to - 2.5 mA                                               |                         | - 30              | - 75              | mV    |  |

| Power Supply Rejection           | PSRR              | at 100 Hz                                                                      |                         | 60                |                   | dB    |  |

| Oscillator                       |                   |                                                                                |                         |                   | •                 |       |  |

| Accuracy (1 % R <sub>OSC</sub> ) |                   | $R_{OSC}$ = 30 kΩ, $f_{NOM}$ = 500 kHz                                         | - 20                    |                   | 20                | %     |  |

| Max Frequency <sup>g</sup>       | F <sub>MAX</sub>  | R <sub>OSC</sub> = 22.6 kΩ                                                     | 400                     | 500               | 600               | - kHz |  |

| Foldback Frequency <sup>d</sup>  | F <sub>FOBK</sub> | $f_{NOM} = 500 \text{ kHz}, \text{ V}_{CS2} - \text{V}_{CS1} > 150 \text{ mV}$ |                         | 100               |                   | - KHZ |  |

| Error Amplifier                  | · · ·             |                                                                                |                         |                   |                   |       |  |

| Input Bias Current               | I <sub>BIAS</sub> | V <sub>EP</sub> = 0 V                                                          | - 40                    |                   | - 15              | μΑ    |  |

| Gain                             | A <sub>V</sub>    |                                                                                |                         | - 2.2             |                   | V/V   |  |

| Bandwidth                        | BW                |                                                                                |                         | 5                 |                   | MHz   |  |

| Power Supply Rejection           | PSRR              | at 110 Hz                                                                      |                         | 60                |                   | dB    |  |

| Slew State                       | SR                |                                                                                |                         | 0.5               |                   | V/µs  |  |

|                                                    |                      | Test Conditions<br>Unless Otherwise Specified                                                                                                                             |                   | Limits<br>- 40 to 85 °C | C                 |          |

|----------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------|-------------------|----------|

|                                                    |                      | f <sub>NOM</sub> = 500 kHz, V <sub>IN</sub> = 75 V                                                                                                                        |                   |                         | -                 | 1        |

| Parameter                                          | Symbol               | $V_{INDET} = 7.5 \text{ V}; 10.5 \text{ V} \le V_{CC} \le 13.2 \text{ V}$                                                                                                 | Min. <sup>b</sup> | Typ. <sup>c</sup>       | Max. <sup>b</sup> | Unit     |

| Current Sense Amplifier                            |                      | 1                                                                                                                                                                         |                   |                         | 1                 | -        |

| Input Voltage CM Range                             | V <sub>CM</sub>      | V <sub>CS1</sub> - GND, V <sub>CS2</sub> - GND                                                                                                                            |                   | ± 150                   |                   | mV       |

| Current Sense Amplifier                            | CIW                  |                                                                                                                                                                           |                   |                         |                   | <u> </u> |

| Input Amplifier Gain                               | A <sub>VOL</sub>     |                                                                                                                                                                           |                   | 17.5                    |                   | dB       |

| Input Amplifier Bandwidth                          | BW                   |                                                                                                                                                                           |                   | 5                       |                   | MHz      |

| Input Amplifier Offset Voltage                     | V <sub>OS</sub>      |                                                                                                                                                                           |                   | ± 5                     |                   | mV       |

|                                                    | -03                  | dV <sub>CS</sub> = 0                                                                                                                                                      |                   | 120                     |                   |          |

| C <sub>L CONT</sub> Current                        |                      | $dV_{CS} = 0$<br>$dV_{CS} = 100 \text{ mV}$                                                                                                                               |                   | 0                       |                   | μA       |

| CL_CONT Current                                    | I <sub>CL_CONT</sub> | $\frac{dV_{CS} = 100 \text{ mV}}{dV_{CS} = 100 \text{ mV}}$                                                                                                               |                   | 0<br>> 2                |                   | mA       |

|                                                    |                      |                                                                                                                                                                           |                   | >2                      |                   | mA       |

| Lower Current Limit Threshold                      | V <sub>TLCL</sub>    | $I_{PD} = I_{PU} - I_{CL\_CONT} = 0$                                                                                                                                      |                   | 100                     |                   | mV       |

| Upper Current Limit Threshold                      | V <sub>THCL</sub>    | I <sub>PD</sub> > 2 mA                                                                                                                                                    |                   | 150                     |                   | 1        |

| Hysteresis                                         |                      | l <sub>PU</sub> < 500 μA                                                                                                                                                  |                   | - 50                    |                   | 1        |

| C <sub>L_CONT</sub> Clamp Level                    | C <sub>L_CONT</sub>  | I <sub>PU</sub> = 500 μA                                                                                                                                                  | 0.6               |                         | 1.5               | V        |

| PWM Operation                                      | •                    |                                                                                                                                                                           |                   |                         |                   |          |

|                                                    | D <sub>MAX</sub>     | face = 500 kHz 25 °C Vac = 0 V Primary                                                                                                                                    | 88                | 91                      | 94                | %        |

| Duty Cycle                                         | DMAX                 | $f_{OSC} = 500 \text{ kHz}, 25 \text{ °C}$ $V_{EP} = 0 \text{ V} \qquad Primary$ $Secondary$ $V_{INDET} = 4.8 \text{ V}, V_{IN} = 48 \text{ V}$ $V_{EP} = 1.75 \text{ V}$ | 90                | 93                      | 95                | %        |

| Duty Cycle                                         | D <sub>MIN</sub>     |                                                                                                                                                                           |                   | < 17                    |                   |          |

|                                                    | PMIN                 | V <sub>CS2</sub> - V <sub>CS1</sub> > 150 mV                                                                                                                              |                   | 3                       |                   |          |

| Pre-Regulator                                      |                      |                                                                                                                                                                           |                   |                         |                   |          |

| Input Voltage                                      | + V <sub>IN</sub>    | I <sub>IN</sub> = 10 μA                                                                                                                                                   |                   |                         | 75                | V        |

| Input Leakage Current                              | I <sub>LKG</sub>     | $V_{IN} = 75 \text{ V},  V_{CC} > V_{REG}$                                                                                                                                |                   |                         | 10                | μA       |

| Regulator Bias Current                             | I <sub>REG1</sub>    | $V_{IN} = 75 V, V_{INDET} < V_{SD}$                                                                                                                                       |                   | 86                      | 200               | μι       |

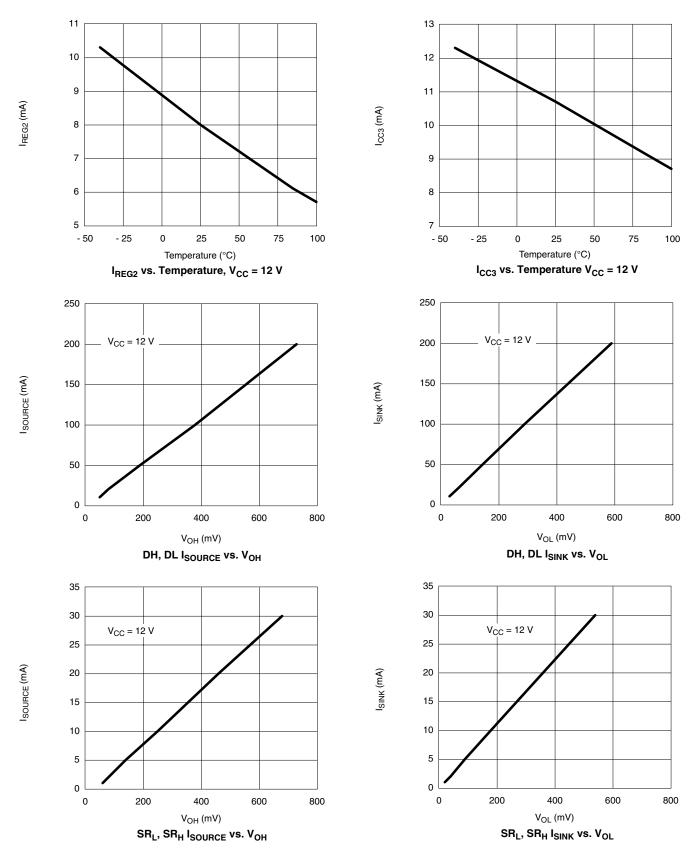

|                                                    | I <sub>REG2</sub>    | $V_{IN} = 75 V, V_{INDET} > V_{REF}$                                                                                                                                      |                   | 8                       | 14                | mA       |

| Regulator_Comp                                     | ISOURCE              | V <sub>CC</sub> = 12 V                                                                                                                                                    | - 29              | - 19                    | - 9               | μA       |

|                                                    | I <sub>SINK</sub>    |                                                                                                                                                                           | 50                | 82                      | 110               | μι       |

| Pre-Regulator drive Capability                     | ISTART               | V <sub>CC</sub> < V <sub>REG</sub>                                                                                                                                        | 20                |                         |                   | mA       |

| V <sub>CC</sub> Pre-Regulator Turn Off             | V <sub>REG1</sub>    | V <sub>INDET</sub> > V <sub>REF</sub>                                                                                                                                     | 7.4               | 9.1                     | 10.4              |          |

| Threshold Voltage                                  |                      | $I_{A} = 25  {}^{\circ}C$                                                                                                                                                 | 8.5               | 9.1                     | 9.7               |          |

| ······································             | V <sub>REG2</sub>    | V <sub>INDET</sub> = 0 V                                                                                                                                                  |                   | 9.2                     |                   | v        |

| Undervoltage Lockout                               | V <sub>UVLO</sub>    | V <sub>CC</sub> Rising                                                                                                                                                    | 7.15              | 8.8                     | 9.8               | Ň        |

|                                                    | 010                  | $T_A = 25 \text{ °C}$                                                                                                                                                     | 8.1               | 8.8                     | 9.3               |          |

| V <sub>ULVO</sub> Hysteresis <sup>f</sup>          | V <sub>UVLOHYS</sub> |                                                                                                                                                                           |                   | 0.5                     |                   |          |

| Soft-Start                                         |                      |                                                                                                                                                                           |                   |                         |                   |          |

| Soft-Start Current Output                          | I <sub>SS</sub>      | Start-Up Condition                                                                                                                                                        | 12                | 20                      | 28                | μΑ       |

| Soft-Start Completion Voltage                      | $V_{SS\_COMP}$       | Normal Operation                                                                                                                                                          |                   | 8.05                    | 8.85              | V        |

| Shutdown                                           |                      |                                                                                                                                                                           |                   |                         |                   |          |

| V <sub>INDET</sub> Shutdown                        | V <sub>SD</sub>      | V <sub>INDET</sub> Rising                                                                                                                                                 | 350               | 550                     | 720               | mV       |

| V <sub>SD</sub> Hysteresis                         |                      | V <sub>INDET</sub> Falling                                                                                                                                                |                   | 200                     |                   |          |

| V <sub>INDET</sub> Input Threshold Protecti        |                      |                                                                                                                                                                           |                   |                         |                   |          |

| V <sub>INDET</sub> - V <sub>IN</sub> Under Voltage | V <sub>UV</sub>      | V <sub>INDET</sub> Rising                                                                                                                                                 | ng 3.13 3.3 3     |                         | 3.46              | v        |

| V <sub>UV</sub> Hysteresis                         |                      | V <sub>INDET</sub> Falling                                                                                                                                                | 0.23              | 0.3                     | 0.35              | v        |

| Over Temperature Voltages                          |                      |                                                                                                                                                                           |                   |                         |                   |          |

| Activating Temperature                             | OTP_on               | T <sub>J</sub> Increasing                                                                                                                                                 |                   | 135                     |                   | °C       |

| De-Activating Temperature                          | OTP_off              | T <sub>.1</sub> Decreasing                                                                                                                                                |                   | 113                     | 1                 | 1        |

|                                            |                           | Test Conditions<br>Unless Otherwise Specified                                                                                                         | -                      | Limits<br>40 to 85 ° | С                     |          |  |

|--------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------|-----------------------|----------|--|

| Parameter                                  | Symbol                    | $f_{NOM} = 500 \text{ kHz}, \text{ V}_{IN} = 75 \text{ V}$<br>$\text{V}_{INDET} = 7.5 \text{ V}; 10.5 \text{ V} \le \text{V}_{CC} \le 13.2 \text{ V}$ | Min. <sup>b</sup>      | Typ. <sup>c</sup>    | Max. <sup>b</sup>     | Unit     |  |

| Converter Supply Current (V <sub>C</sub>   | -                         |                                                                                                                                                       | WIIII.                 | iyp.                 | iviax.                | Unit     |  |

| Shutdown                                   |                           | Shutdown, V <sub>INDET</sub> = 0 V                                                                                                                    | 50                     |                      | 350                   | μA       |  |

| Converter Supply Current (V <sub>C</sub>   |                           |                                                                                                                                                       |                        |                      |                       |          |  |

| Switching Disabled                         |                           | 2 V <sub>INDET</sub> < V <sub>REF</sub> 4                                                                                                             |                        | 8                    | 12                    |          |  |

| Switching w/o Load                         | I <sub>CC3</sub>          | V <sub>INDET</sub> > V <sub>REF</sub> f <sub>NOM</sub> = 500 kHZ                                                                                      | 5                      | 10                   | 15                    |          |  |

| Switching with C <sub>LOAD</sub>           | I <sub>CC4</sub>          | $V_{CC} = 12 \text{ V}, C_{DH} = C_{DL} = 3 \text{ nF}$<br>$C_{SBH} = C_{SBL} = 0.3 \text{ nF}$                                                       |                        | 21                   |                       | mA       |  |

| Output MOSFET DH Driver (Hi                | iah-Side)                 |                                                                                                                                                       |                        |                      |                       |          |  |

| Output High Voltage                        | V <sub>OH</sub>           | Sourcing 10 mA                                                                                                                                        | V <sub>BST</sub> - 0.3 |                      | 1                     |          |  |

| Output Low Voltage                         | V <sub>OL</sub>           | Sinking 10 mA                                                                                                                                         |                        |                      | V <sub>LX</sub> + 0.3 | V        |  |

| Boost Current                              | I <sub>BST</sub>          | $V_{LX} = 48 \text{ V}, \text{ V}_{BST} = \text{V}_{LX} + \text{V}_{CC}$                                                                              | 1.3                    | 1.9                  | 2.7                   |          |  |

| LX Current                                 | I <sub>LX</sub>           | $V_{LX} = 48 \text{ V}, \text{ V}_{BST} = \text{V}_{LX} + \text{V}_{CC}$                                                                              | - 1.3                  | - 0.7                | - 0.4                 | mA       |  |

| Peak Output Source                         | I <sub>SOURCE</sub>       |                                                                                                                                                       | -                      | - 1.0                | - 0.75                | A        |  |

| Peak Output Sink                           | I <sub>SINK</sub>         | V <sub>CC</sub> = 10.5 V                                                                                                                              | 0.75                   | 1.0                  |                       |          |  |

| Rise Time                                  | t <sub>r</sub>            | 0 0 5                                                                                                                                                 |                        | 35                   |                       |          |  |

| Fall Time                                  | t <sub>f</sub>            | C <sub>DH</sub> = 3 nF                                                                                                                                |                        | 35                   |                       | ns       |  |

| Output MOSFET DL Driver (Lo                | ow-Side)                  |                                                                                                                                                       | 1 1                    |                      |                       |          |  |

| Output High Voltage                        | V <sub>OH</sub>           | Sourcing 10 mA                                                                                                                                        | V <sub>CC</sub> - 0.3  |                      |                       |          |  |

| Output Low Voltage                         | V <sub>OL</sub>           | Sinking 10 mA                                                                                                                                         |                        |                      | 0.3                   | V        |  |

| Peak Output Source                         | ISOURCE                   |                                                                                                                                                       |                        | - 1.0                | - 0.75                | <u> </u> |  |

| Peak Output Sink                           | I <sub>SINK</sub>         | V <sub>CC</sub> = 10.5 V                                                                                                                              | 0.75                   | 1.0                  |                       | A        |  |

| Rise Time                                  | t <sub>r</sub>            |                                                                                                                                                       |                        | 35                   |                       |          |  |

| Fall Time                                  | t <sub>f</sub>            | C <sub>DH</sub> = 3 nF                                                                                                                                |                        | 35                   |                       | ns       |  |

| Synchronous Rectifier (SR <sub>H</sub> , S | SR <sub>L</sub> ) Drivers |                                                                                                                                                       |                        |                      |                       |          |  |

| Output High Voltage                        | V <sub>OH</sub>           | Sourcing 10 mA                                                                                                                                        | V <sub>CC</sub> - 0.4  |                      |                       | v        |  |

| Output Low Voltage                         | V <sub>OL</sub>           | Sinking 10 mA                                                                                                                                         |                        |                      | 0.4                   | V        |  |

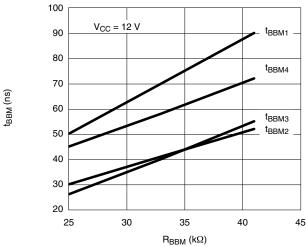

|                                            | t <sub>BBM1</sub>         | $T_A = 25 \text{ °C}, R_{BBM} = 33 \text{ k}\Omega, V_{INDET} = 4.8 \text{ V},$                                                                       |                        | 48                   |                       | [        |  |

|                                            | t <sub>BBM2</sub>         | $V_{EP} = 0 V, V_{IN} = 48 V$                                                                                                                         |                        | 9                    |                       |          |  |

| Break-Before-Make Time <sup>e</sup>        | t <sub>BBM3</sub>         | $T_A = 25 \text{ °C}, R_{BBM} = 33 \text{ k}\Omega, \text{ BST} = 60 \text{ V},$                                                                      |                        | 24                   |                       | ns       |  |

|                                            | t <sub>BBM4</sub>         | $V_{INDET}$ = 4.8 V, $V_{EP}$ = 0 V, $V_{IN}$ = 48 V = LX                                                                                             |                        | 18                   |                       | ł        |  |

| Peak Output Source                         | ISOURCE                   | V <sub>CC</sub> = 10.5 V                                                                                                                              |                        | - 100                |                       |          |  |

| Peak Output Sink                           | I <sub>SINK</sub>         | v <sub>CC</sub> = 10.5 v                                                                                                                              |                        | 100                  |                       | mA       |  |

| Rise Time                                  | t <sub>r</sub>            | C <sub>DH</sub> = 3 nF                                                                                                                                |                        | 35                   |                       | -        |  |

| Fall Time                                  | t <sub>f</sub>            | 0 <sub>DH</sub> = 3 m                                                                                                                                 |                        | 35                   |                       | ns       |  |

| Voltage Mode                               |                           |                                                                                                                                                       | · .                    |                      |                       |          |  |

| Error Amplifier                            | t <sub>d1DH</sub>         | Input to High-Side Switch Off                                                                                                                         |                        | < 200                |                       | ne       |  |

|                                            | t <sub>d2DL</sub>         | Input to Low-Side Switch Off                                                                                                                          |                        | < 200                |                       | ns       |  |

| Current Mode                               |                           |                                                                                                                                                       |                        |                      |                       |          |  |

| Current Amplifier                          | t <sub>d3DH</sub>         | Input to High-Side Switch Off                                                                                                                         |                        | < 200                |                       | ns       |  |

|                                            | t <sub>d4DL</sub>         | Input to Low-Side Switch Off                                                                                                                          |                        | < 200                |                       | 115      |  |

Notes:

a. Refer to PROCESS OPTION FLOWCHART for additional information.

b. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum (- 40 °C to 85 °C).

c. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

d.  $F_{MIN}$  when  $VC_{L\_CONT}$  at clamp level. Typical foldback frequency change + 20 %, - 30 % over temperature.

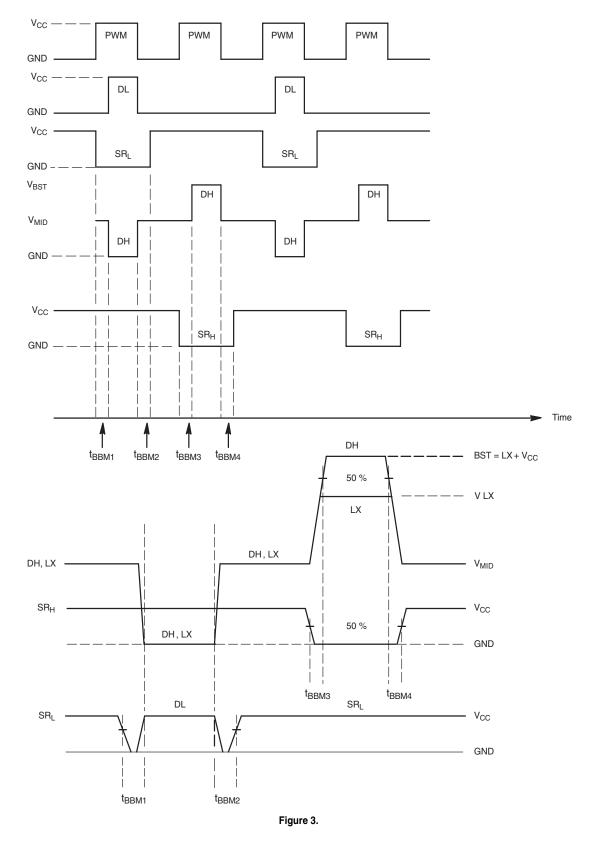

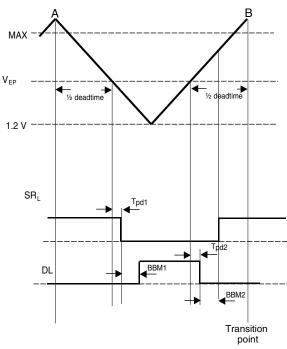

e. See Figure 3 for Break-Before-Make time definition.

f.  $V_{UVLO}$  tracks  $V_{REG1}$  by a diode drop.

g. Guaranteed by design and characterization, not tested in production.

#### TIMING DIAGRAM FOR MOS DRIVERS

#### **PIN CONFIGURATION**

**VISHAY**

| ORDERING INFORMATION |                   |          |

|----------------------|-------------------|----------|

| Part Number          | Temperature Range | Package  |

| Si9122EDQ-T1-E3      | - 40 °C to 85 °C  | TSSOP-20 |

| Si9122EDLP-T1-E3     | - 40 0 10 85 0    | MLP65-20 |

| Eval Board      | Temperature Range | Board Type                  |

|-----------------|-------------------|-----------------------------|

| Contact Factory | - 10 °C to 70 °C  | Surface Mount and Thru-Hole |

| PIN DESCR            | RIPTION             |                                                                                                                            |

|----------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------|

| 1                    | V <sub>IN</sub>     | Input supply voltage for the start-up circuit                                                                              |

| 2                    | REG_COMP            | Control signal for an external pass transistor                                                                             |

| 3                    | V <sub>CC</sub>     | Supply voltage for internal circuitry                                                                                      |

| 4                    | V <sub>REF</sub>    | 3.3 V reference                                                                                                            |

| 5                    | GND                 | Ground                                                                                                                     |

| 6                    | R <sub>OSC</sub>    | External resistor connection to oscillator                                                                                 |

| 7                    | EP                  | Voltage control input                                                                                                      |

| 8 V <sub>INDET</sub> |                     | $V_{\text{IN}}$ under voltage detect and shutdown function input. Shuts down or disables switching when $V_{\text{INDET}}$ |

| 0                    | *INDE1              | falls below preset threshold voltages and provides the feed forward voltage.                                               |

| 9                    | CS1                 | Current limit amplifier negative input                                                                                     |

| 10                   | CS2                 | Current limit amplifier positive input                                                                                     |

| 11                   | C <sub>L_CONT</sub> | Current limit compensation                                                                                                 |

| 12                   | BBM                 | Programmable Break-Before-Make time connection to an external resistor to set time delay                                   |

| 13                   | SS                  | Soft-Start control - external capacitor connection                                                                         |

| 14                   | SRL                 | Signal transformer drive, sequenced with the primary side.                                                                 |

| 15                   | SR <sub>H</sub>     | Signal transformer drive, sequenced with the primary side                                                                  |

| 16                   | PGND                | Power ground                                                                                                               |

| 17                   | DL                  | Low-side gate drive signal - primary                                                                                       |

| 18                   | LX                  | High-side source and transformer connection node                                                                           |

| 19                   | DH                  | High-side gate drive signal - primary                                                                                      |

| 20                   | BST                 | Bootstrap voltage to drive the high-side n-channel MOSFET switch                                                           |

# Si9122E

Vishay Siliconix

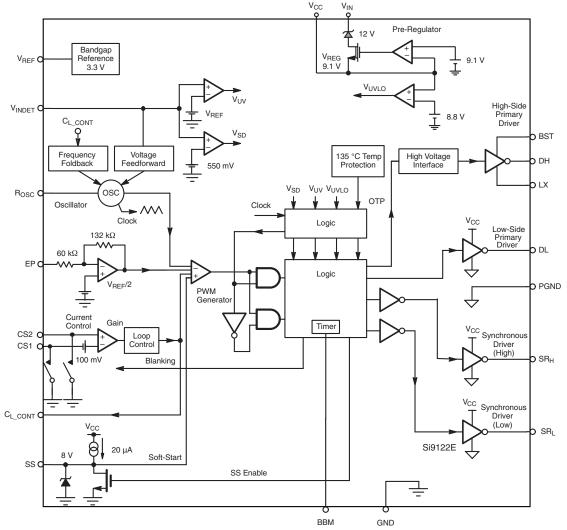

Figure 4. Detailed Si9122E Block Diagram

#### DETAILED OPTION

#### Start-Up

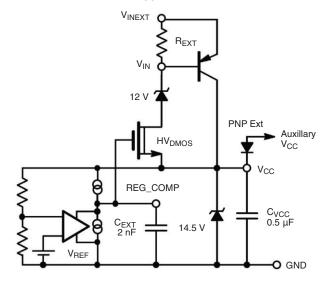

When VINEXT rises above 0 V, the internal pre-regulator begins to charge up the  $V_{\mbox{\scriptsize CC}}$  capacitor. Current into the external V<sub>CC</sub> capacitor is limited to typically 40 mA by the internal DMOS device. When V<sub>CC</sub> exceeds the UVLO voltage of 8.8 V a soft-start cycle of the switch mode supply is initiated. The  $V_{CC}$  supply continues to be charged by the pre-regulator until  $V_{CC}$  equals  $V_{REG}$ . During this period, between  $V_{UVLO}$  and  $V_{REG}$ , excessive load current will result in  $V_{CC}$  falling below  $V_{UVLO}$  and stopping switch mode operation. This situation is avoided by the hysteresis between  $V_{REG}$  and  $V_{UVLO}$  and correct sizing of the  $V_{CC}$ capacitor, bootstrap capacitor and the soft-start capacitor. The value of the V<sub>CC</sub> capacitor should therefore be chosen to be capable of maintaining switch mode operation until the required V<sub>CC</sub> current can be supplied from the external circuit (e.g via a power transformer winding and zener regulator). Feedback from the output of the switch mode supply charges V<sub>CC</sub> above V<sub>BEG</sub> and fully disconnects the pre-regulator,

isolating V<sub>CC</sub> from V<sub>IN</sub>. V<sub>CC</sub> is then maintained above V<sub>REG</sub> for the duration of switch mode operation. In the event of an over voltage condition on V<sub>CC</sub>, an internal voltage clamp turns on at 14.5 V to shunt excessive current to GND.

Care needs to be taken if there is a delay prior to the external circuit feeding back to the  $V_{CC}$  supply. To prevent excessive power dissipation within the IC it is advisable to use an external PNP device. A pin has been incorporated on the IC, (REG\_COMP) to provide compensation when employing the external device. In this case the  $V_{IN}$  pin is connected to the base of the PNP device and controls the current, while the REG\_COMP pin determines the frequency compensation of the circuit. The value of the REG\_COMP capacitor cannot be too big, otherwise it will slow down the response of the pre-regulator needs to be turned on again. To understand the operation, please refer to figure 5.

The soft-start circuit is designed for the dc-dc converter to start-up in an orderly manner and reduce component stresses on the Converter. This feature is programmable by selecting an external  $C_{SS}$ . An internal 20  $\mu$ A current source charges  $C_{SS}$  from 0 V to the final clamped voltage of 8 V. In the event of UVLO or shutdown,  $V_{SS}$  will be held low (< 1 V) disabling driver switching. To prevent oscillations, a longer soft-start time may be needed for highly capacitive loads and/or high peak output current applications.

#### Reference

The reference voltage of Si9122E is set at 3.3 V. The reference voltage should be de-coupled externally with 0.1  $\mu F$  capacitor. The V<sub>REF</sub> voltage is 0 V in shutdown mode and has 50 mA source capability.

#### **Voltage Mode PWM Operation**

Under normal load conditions, the IC operates in voltage mode and generates a fixed frequency pulse width modulated signal to the drivers. Duty cycle is controlled over a wide range to maintain output voltage under line and load variation. Voltage feedforward is also included to take account of variations in supply voltage  $V_{IN}$ .

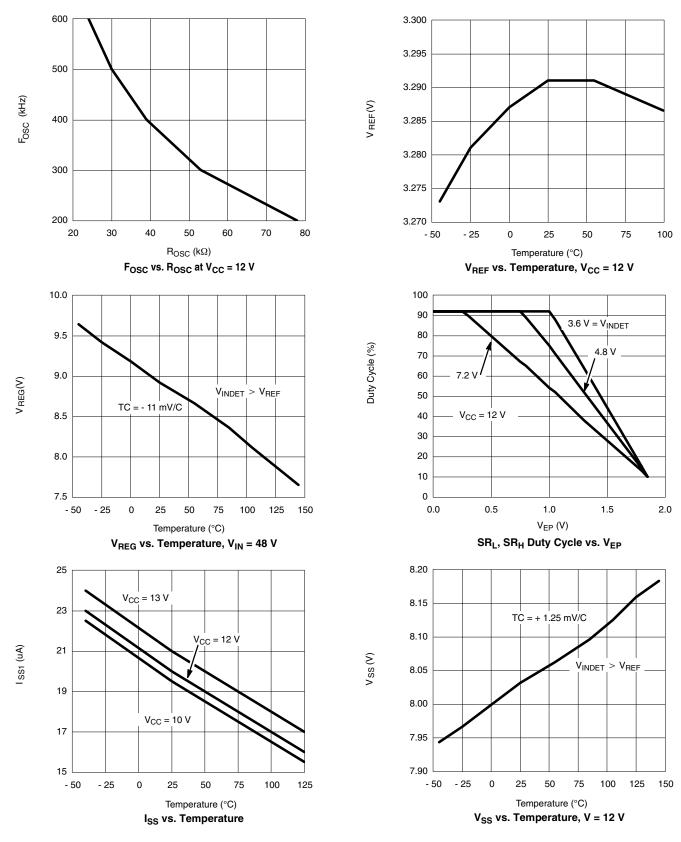

In the half-bridge topology requiring isolation between output and input, the reference voltage and error amplifier must be supplied externally, usually on the secondary side. The error information is thus passed to the power controller through an opto-coupling device. This information is inverted, hence 0 V represents the maximum duty cycle, while 2 V represents minimum duty cycle. The error information enters the IC via pin EP, and is passed to the PWM generator via an inverting amplifier. The relationship between Duty cycle and V<sub>EP</sub> is shown in the Typical Characteristic Graph, Duty Cycle vs. V<sub>EP</sub> 25 °C, page 12. Voltage feedforward is implemented by taking the attenuated V<sub>IN</sub> signal at V<sub>INDET</sub> and directly modulating the duty cycle.

At start-up, i.e., once  $V_{CC}$  is greater than  $V_{UVLO}$ , switching is initiated under soft-start control which increases primary switch on-times linearly from  $D_{MIN}$  to  $D_{MAX}$  over the soft-start period. Start-up from a  $V_{INDET}$  power down is also initiated under soft-start control.

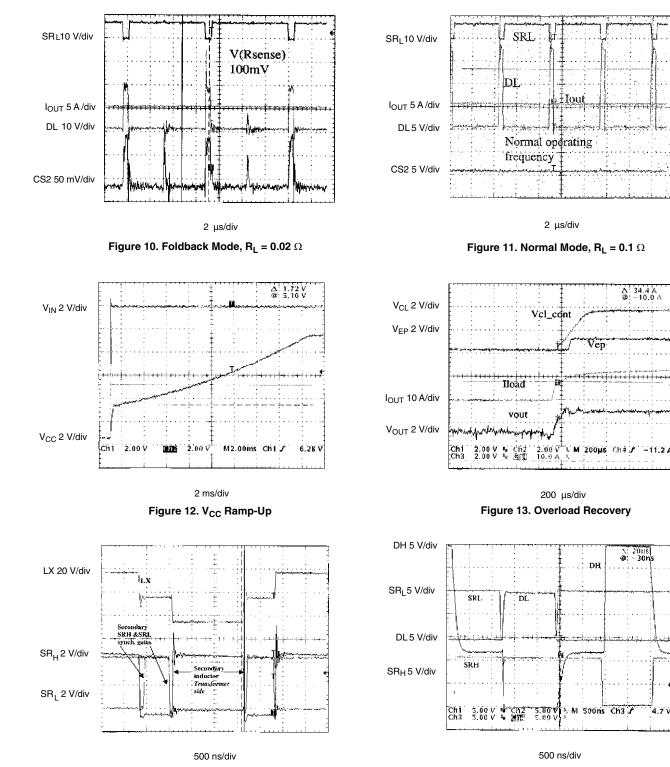

# Half Bridge and Synchronous Rectification Timing Sequence

The PWM signal generated within the Si9122E controls the low and high-side bridge drivers on alternative cycles. A period of inactivity always results after initiation of the soft-start cycle until the soft-start voltage reaches approximately 1.2 V and PWM controlled switching begins. The first bridge driver to switch is always the low-side (DL), as this allows charging of the high-side boost capacitor.

The timing and coordination of the drives to the primary and secondary stages is very important and shown in figure 3. It is essential to avoid the situation where both of the secondary MOSFETs are on when either the high or the low-side switch are active. In this situation the transformer would effectively be presented with a short across the output. To

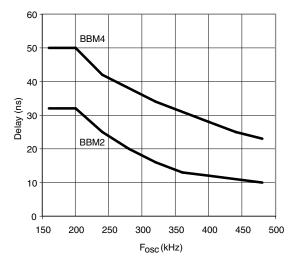

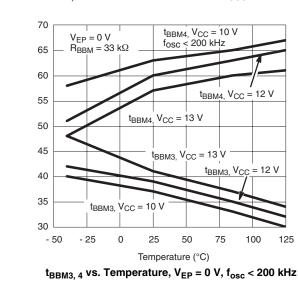

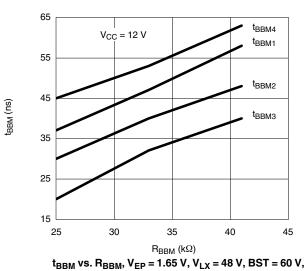

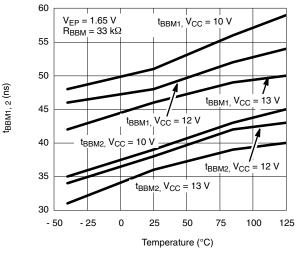

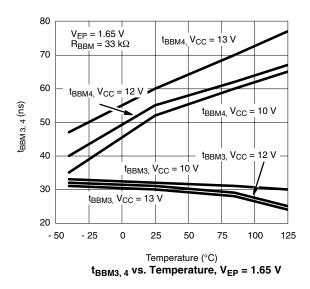

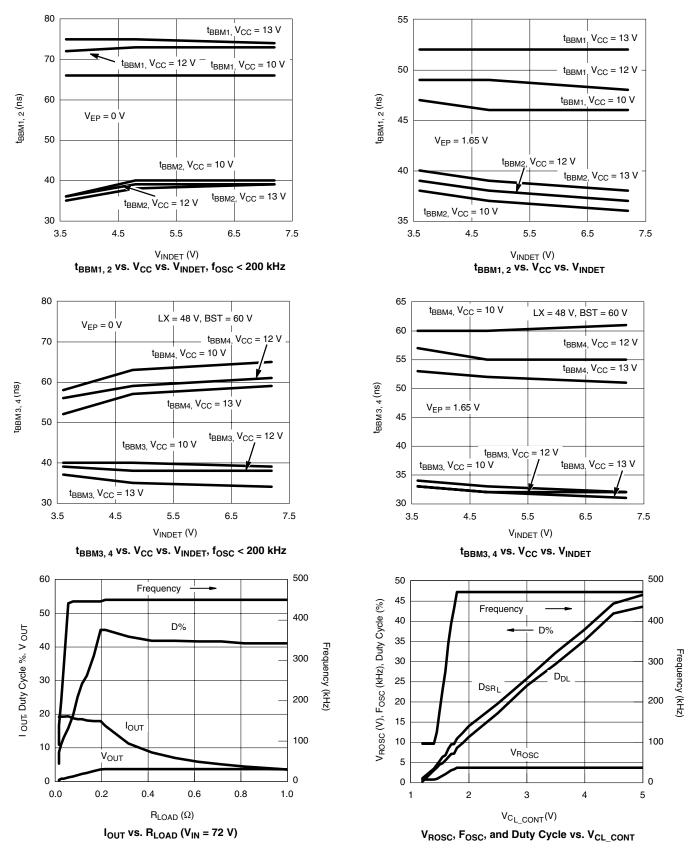

avoid this, a dedicated break-before-make circuit is included which will generate non-overlapping waveforms for the primary and the secondary drive signals. This is achieved by a programmable timer which delays the on switching of the primary driver relative to the off switching of the related secondary and subsequently delays the on switching of the secondary relative to the off switching of the related primary. Typical variations of BBM times with respect to R<sub>BBM</sub> and other operating parameters are shown on page 14 and 15.

#### Primary High- and Low-Side MOSFET Drivers

The drive voltage for the low-side MOSFET switch is provided directly from V<sub>CC</sub>. The high-side MOSFET however requires the gate voltage to be enhanced above V<sub>IN</sub>. This is achieved by bootstrapping the V<sub>CC</sub> voltage onto the LX voltage (the high-side MOSFET source). In order to provide the bootstrapping an external diode and capacitor are required as shown on the application schematic. The capacitor will charge up after the low-side driver has turned on. The switch gatedrive signals DH and DL are shown in figure 3.

#### Secondary MOSFET Drivers

The secondary side MOSFETs are driven from the Si9122E via a center tapped pulse transformer and inverter drivers. The waveforms from  $SR_H$  and  $SR_L$  are shown in figure 3. Of importance is the relative voltage between  $SR_H$  and  $SR_L$ , i.e. that which is presented across the primary of the pulse transformer. When both potentials of  $SR_L$  and  $SR_H$  are equal then by the action of the inverting drivers both secondary MOSFETs are turned on.

#### Oscillator

The oscillator is designed to operate at a nominal frequency of 500 kHz. The 500 kHz operating frequency allows the converter to minimize the inductor and capacitor size, improving the power density of the converter. The oscillator and therefore the switching frequency is programmable by attaching a resistor to the  $R_{OSC}$  pin. Under overload conditions the oscillator frequency is reduced by the current overload protection to enable a constant current to be maintained into a low impedance circuit.

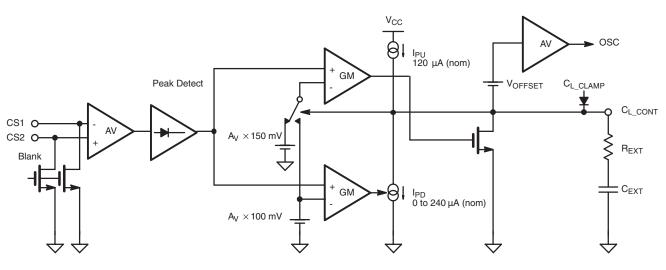

#### **Current Limit**

Current mode control providing constant current operation is achieved by monitoring the differential voltage V<sub>CS</sub> between the CS1 and CS2 pins, which are connected to a current sense resistor on the primary low-side MOSFET. In the absence of an overcurrent condition, V<sub>CS</sub> is less than lower current limit threshold V<sub>TLCL</sub> (typical 100 mV); C<sub>L\_CONT</sub> is pulled up linearly via the 120  $\mu$ A current source (I<sub>PU</sub>) and both DL and DH switch at half the oscillator set frequency. When a moderate overcurrent condition occurs (V<sub>TLCL</sub> < V<sub>CS</sub> < V<sub>THCL</sub>), the C<sub>L\_CONT</sub> capacitor will be discharged at a rate that is proportional to V<sub>CS</sub> - 100 mV by the I<sub>PD</sub> current source. Both driver outputs are in frequency fold-back mode and the switching frequency becomes roughly 20 % of

normal switching frequency. When a severe overcurrent condition occurs ( $V_{THCL} < V_{CS}$ ), the NMOS discharges  $C_{L\_CONT}$  capacitor immediately at 2 mA rate and the  $C_{L\_CONT}$  voltage will be clamped to 1.2 V disabling both DL and DH outputs.

Before V<sub>CS</sub> reaches severe overcurrent condition, a lowering of the C<sub>L\_CONT</sub> voltage results in PWM control of the output drive being taken over by the current limit control loop through C<sub>L\_CONT</sub>. Current control initially reduces the switching duty cycle toward the minimum the chip can reach (D<sub>MIN</sub>). If this duty cycle reduction still cannot lower the load current, then the switching frequency will start to fold back to minimum 1/5 of the nominal frequency. This prevents the on-time of the primary drivers from being reduced to below 100 ns and avoids current tails. If V<sub>CS</sub> > V<sub>THCL</sub>, the switching will then stop.

With constant current mode control and frequency foldback, protection of the MOSFET switches is increased. The converter reverts to voltage mode operation immediately when the primary current falls below the limit level, and  $C_{L\_CONT}$  capacitor is charged up and clamped to 6.5 V. The soft-start function does not apply during current limit period, as this would constitute hiccup mode operation.

#### VIN Voltage Monitor - VINDET

The chip provides a means of sensing the voltage of V<sub>IN</sub>, and withholding operation of the output drivers until a minimum voltage of V<sub>REF</sub> (3.3 V, 300 mV hysteresis), is achieved. This is achieved by choosing an appropriate resistive tap between the ground and V<sub>IN</sub>, and comparing this voltage with the reference voltage. When the applied voltage is greater than V<sub>REF</sub>, the output drivers are activated as normal. V<sub>INDET</sub> also provides the input to the voltage feedforward function.

However, if the divided voltage applied to the V<sub>INDET</sub> pin is greater than V<sub>CC</sub> - 0.3 V, the high-side driver, DH, will stop switching until the voltage drops below V<sub>CC</sub> - 0.3 V. Thus, the resistive tap on the V<sub>IN</sub> divider must be set to accommodate the normal V<sub>CC</sub> operating voltage to avoid this condition. Alternatively, a zener clamp diode from V<sub>INDET</sub> to GND may also be used.

#### **Shutdown Mode**

If V<sub>INDET</sub> is forced below the lower V<sub>SD</sub> threshold, the device will enter SHUTDOWN mode. This powers down all unnecessary functions of the controller, ensures that the primary switches are off, and results in a low level current demand from the V<sub>IN</sub> or V<sub>CC</sub> supplies.

Figure 5. High-Voltage Pre-Regulator Circuit

Figure 6. Current Limit Circuit

#### **REDUCTION OF BBM<sub>2, 4</sub> AT HIGHER fosc**

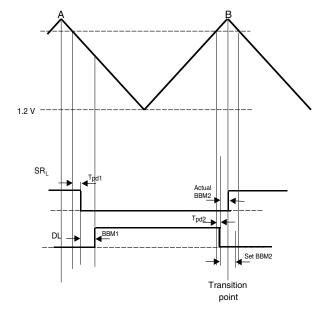

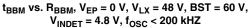

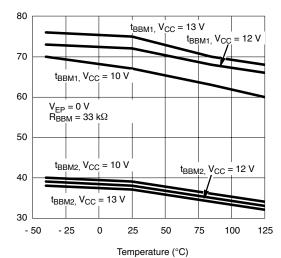

The start of a switching period is defined as the turning point of the oscillator, marked in Figure 7 as A, with the end of a switching period marked as B. For a half bridge, two switching periods are required for both the primary high-side and low-side drivers to operate as shown in Figure 3. For a given oscillator frequency there is a finite time in which all events from equation (1) have to occur. These are  $t_{dt}$  dead-time duration which is a function of  $V_{EP}$ ,  $t_{pd1}$  is the propagation delay from the PWM to  $SR_L$  (or  $SR_H$ ) output going low,  $t_{BBM1}$  (or  $t_{BBM3}$ ) rise delay, DL (or DH) primary driver on-time,  $t_{pd2}$  is the propagation delay from PWM to DL (or DH) output going low and  $t_{BBM2}$ (or  $t_{BBM4}$ ) fall delay.

Figure 7 shows the switching cycle for the low side primary driver and associated synchronous driver and equation (1) shows the switching time components.

(1)

At 500 kHz and maximum duty  $t_{pd2}$  is typically 60 ns. T<sub>switch</sub> = 1/2t<sub>dt</sub> + t<sub>pd1</sub>+ t<sub>SRLOFF</sub> + 1/2t<sub>dt</sub> - t<sub>pd2</sub>- t<sub>BBM2</sub>

The Si9122E has an improved primary and secondary duty cycles with typical maximum secondary duty at 93.2 %. Hence the dead-time is 6.8 % or 136 ns at 500 kHz. Half of the dead-time is 68 ns and during this time  $t_{pd2}$  plus  $t_{BBM2}$  has to occur before the next transition point of the oscillator cycle.  $R_{BBM}$  contributes 1.2 ns/k $\Omega$  to  $t_{BBM2}$ ; with 33 k $\Omega$  this amounts to 40 ns. If  $t_{BBM2}$  is set beyond the transition point, SR<sub>L</sub> will be forced high due to logic conditions and a reduction in the set  $t_{BBM2}$  will be determined by the half dead-time minus  $t_{pd2}$  and will be independent of the  $R_{BBM}$  value as shown in figure 8.

Note: this applies to  $t_{BBM4}$  as well.

To mitigate the decrease in set  $t_{BBM2}$  and  $t_{BBM4}$ , the following criteria must be met. The set  $t_{BBM2}$  plus its associated  $t_{pd2}$  must not exceed 3.4 % of the oscillator period. The typical  $t_{BBM2}$  and  $t_{BBM4}$  delays are provided in figure 9 to facilitate setting these delays for a given frequency with  $R_{BBM}$  of 33 k $\Omega$ .

| t <sub>BBM2</sub> + t <sub>pd2</sub> < 3.4 % of oscillator period | (2)                          |

|-------------------------------------------------------------------|------------------------------|

| $t_{BBM4} + t_{pd4} < 3.4$ % of oscillator period                 | (3)                          |

| It is critical to avoid the condition where the su                | m of t <sub>BBM2</sub> (set) |

| and tpd2 is greater than 6.8 % of oscillator period               | od whereby the               |

| correct sequence of logic signals cannot be g                     | juaranteed.                  |

Figure 8. Components of a Low-Side Switching Period with Maximum Duty and Limited BBM2

Figure 9. Reduction in BBM2 and BBM4 Si9122E BBM vs.  $F_{OSC},\,V_{IN}$  = 50 V,  $V_{CC}$  = 10 V, BST = 60 V, LX = 50 V,  $V_{EP}$  = 0 V

# Si9122E

Vishay Siliconix

#### **TYPICAL CHARACTERISTICS**

Si9122E Vishay Siliconix

#### **TYPICAL CHARACTERISTICS**

#### **TYPICAL CHARACTERISTICS**

$t_{BBM1, 2}$  vs. Temperature,  $V_{EP}$  = 0 V,  $f_{OSC}$  < 200 kHz

V<sub>INDET</sub> = 4.8 V

$t_{BBM1, 2}$  vs. Temperature, V<sub>EP</sub> = 1.65 V

t<sub>BBM1, 2</sub> (ns)

BBM3, 4 (ns)

Si9122E Vishay Siliconix

#### **TYPICAL CHARACTERISTICS**

Document Number: 73866 S-80112-Rev. D, 21-Jan-08

#### Figure 14. Effective BBM - Measured On Secondary

Figure 15. Drive Waveforms

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see http://www.vishay.com/ppg?73866.

/ISHA

∆ 34.4 A @: 10.0 A

N: 20ns ⊕: −30ns

4.7 V

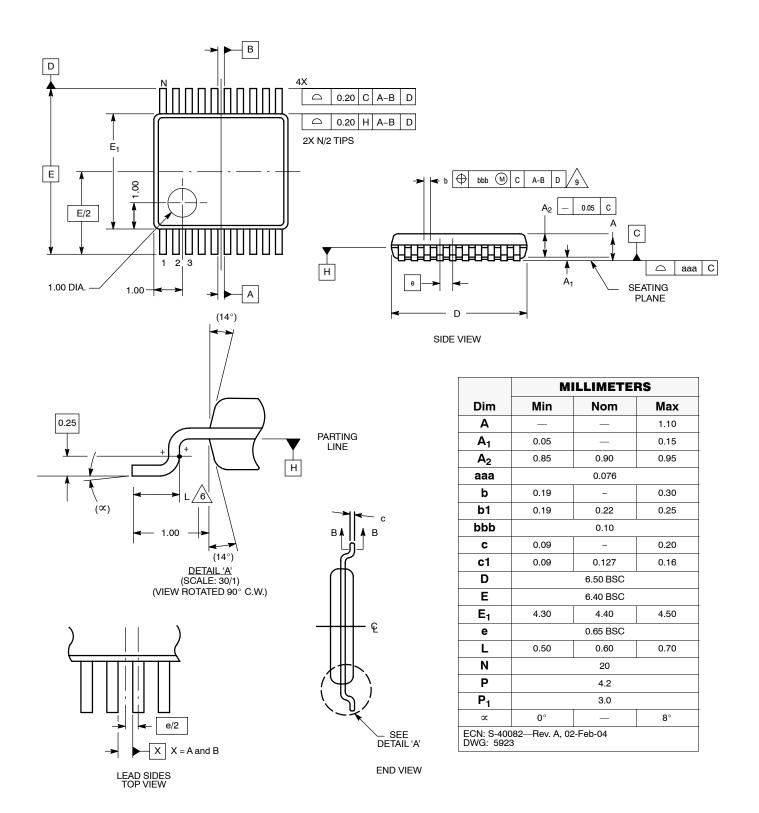

#### TSSOP: 20-LEAD (POWER IC ONLY)

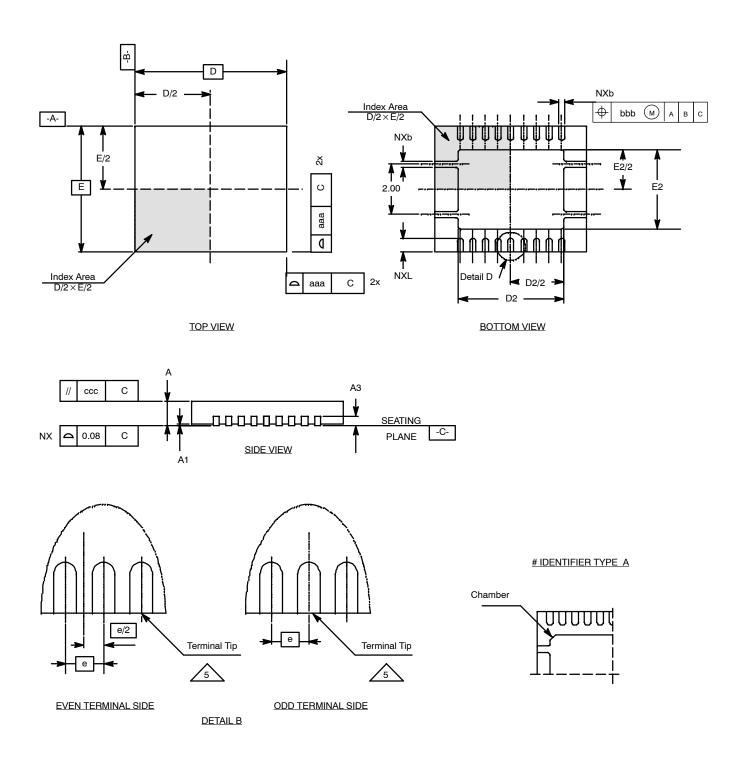

#### PowerPAK® MLP65-18/20 (POWER IC ONLY)

#### PowerPAK MLP65-18/20 (POWER IC ONLY)

|        | N = 10/      |          | : 0.5 mr | п, ворт | 31ZE: 0.  | 00 X 2.00 | )     |

|--------|--------------|----------|----------|---------|-----------|-----------|-------|

|        | MILLIMETERS* |          |          | INCHES  |           |           |       |

| Dim    | Min          | Nom      | Мах      | Min     | Nom       | Max       | Notes |

| А      | 0.80         | 0.90     | 1.00     | 0.031   | 0.035     | 0.039     | 1, 2  |

| A1     | 0.00         | 0.02     | 0.05     | 0.000   | 0.001     | 0.002     | 1, 2  |

| A2     | 0.00         | 0.65     | 1.00     | 0.000   | 0.003     | 0.004     | 1, 2  |

| A3     |              | 0.20 REF |          |         | 0.008 REF |           |       |

| aaa    | -            | 0.15     | -        | -       | 0.006     | -         |       |

| b      | 0.18         | 0.25     | 0.30     | 0.007   | 0.010     | 0.012     | 8     |

| bbb    | -            | 0.10     | -        | -       | 0.004     | -         |       |

| C'     | -            | 0.225    | -        | -       | 0.009     | -         | 4, 10 |

| CCC    | -            | 0.10     | -        | -       | 0.004     | -         |       |

| D      |              | 6.00 BSC |          |         | 0.236 BSC |           | 1, 2  |

| D2     | 4.00         | 4.15     | 4.25     | 0.157   | 1.63      | 0.167     | 1, 2  |

| Е      |              | 5.00 BSC |          |         | 0.197 BSC |           | 1, 2  |

| E2     | 3.00         | 3.15     | 3.25     | 0.118   | 0.124     | 0.128     | 1, 2  |

| е      | -            | 0.50     | -        | -       | 0.020     | -         |       |

| L      | 0.45         | 0.55     | 0.65     | 0.018   | 0.022     | 0.026     | 1, 2  |

| Ν      |              | 18, 20   |          |         | 18, 20    |           | 1, 2  |

| ND(18) |              | 9        |          |         | 9         |           | 1, 2  |

| NE(18) | 0            |          |          | 0       |           | 1, 2      |       |

| ND(20) |              | 10       |          |         | 10        |           | 1, 2  |

| NE(20) |              | 0        |          |         | 0         |           | 1, 2  |

#### N = 18/20 PITCH: 0.5 mm, BODY SIZE: 6.00 x 5.00

\* Use millimeters as the primary measurement.

| ECN: S-41946—Rev. A, 18-Oct-04<br>DWG: 5939 |

|---------------------------------------------|

|                                             |

NOTES:

- 1. Dimensioning and tolerancing conform to ASME Y14.5M-1994.

- 2. All dimensions are in millimeters. All angels are in degrees.

- 3. N is the total number of terminals.

- 4. The terminal #1 identifier and terminal numbering convention shall conform to JEDEC publication 95 SSP-022. Details of terminal #1 identifier are optional, but must be located within the zone indicated. A dot can be marked on the top side by pin 1 to indicate orientation.

$\sqrt{5.}$  ND and NE refer to the number of terminals on the D and E side respectively.

6. Depopulation is possible in a symmetrical fashion.

- 7. NJR refers to NON JEDEC REGISTERED.

- 8. Dimension "b" applies to metalized terminal and is measured between 0.15 mm and 0.30 mm from the terminal tip. If the terminal has optional radius on the other end of the terminal, the dimension "b" should not be measured in that radius area.

- 9. Coplanarity applies to the exposed heat slug as well as the terminal.

- 10. The  $45^{\circ}$  chamfer dimension C' is located by pin 1 on the bottom side of the package.

Vishay

# Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Hyperlinks included in this datasheet may direct users to third-party websites. These links are provided as a convenience and for informational purposes only. Inclusion of these hyperlinks does not constitute an endorsement or an approval by Vishay of any of the products, services or opinions of the corporation, organization or individual associated with the third-party website. Vishay disclaims any and all liability and bears no responsibility for the accuracy, legality or content of the third-party website or for that of subsequent links.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

单击下面可查看定价,库存,交付和生命周期等信息

>>Vishay(威世)