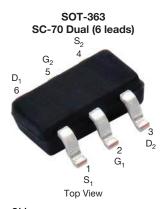

### Automotive Dual N-Channel 20 V (D-S) 175 °C MOSFET

Marking Code: 9H

| PRODUCT SUMMARY                                       |       |  |  |  |

|-------------------------------------------------------|-------|--|--|--|

| V <sub>DS</sub> (V)                                   | 20    |  |  |  |

| $R_{DS(on)}$ ( $\Omega$ ) at $V_{GS} = 4.5 \text{ V}$ | 0.280 |  |  |  |

| $R_{DS(on)}$ ( $\Omega$ ) at $V_{GS} = 2.5 \text{ V}$ | 0.360 |  |  |  |

| $R_{DS(on)}$ ( $\Omega$ ) at $V_{GS} = 1.8 \text{ V}$ | 0.450 |  |  |  |

| I <sub>D</sub> (A)                                    | 0.8   |  |  |  |

| Configuration                                         | Dual  |  |  |  |

| Package                                               | SC-70 |  |  |  |

#### **FEATURES**

- TrenchFET® power MOSFET

- AEC-Q101 qualified

- 100 % R<sub>q</sub> tested

- Material categorization: for definitions of compliance please see www.vishav.com/doc?99912

ROHS COMPLIANT HALOGEN FREE

| G <sub>1</sub> O | G <sub>2</sub> O |

|------------------|------------------|

| S <sub>1</sub>   | $S_2$            |

| ABSOLUTE MAXIMUM RATINGS (T <sub>C</sub> = 25 °C, unless otherwise noted) |                         |                                   |             |     |  |

|---------------------------------------------------------------------------|-------------------------|-----------------------------------|-------------|-----|--|

| PARAMETER                                                                 | SYMBOL                  | LIMIT                             | UNIT        |     |  |

| Drain-source voltage                                                      |                         | $V_{DS}$                          | 20          | V   |  |

| Gate-source voltage                                                       |                         | $V_{GS}$                          | ± 8         | V   |  |

| Continuous drain current <sup>a</sup>                                     | T <sub>C</sub> = 25 °C  | - I <sub>D</sub>                  | 0.8         |     |  |

| Continuous drain current "                                                | T <sub>C</sub> = 125 °C |                                   | 0.8         |     |  |

| Continuous source current (diode conduction) a                            | I <sub>S</sub>          | 0.8                               | Α           |     |  |

| Pulsed drain current <sup>b</sup>                                         |                         | I <sub>DM</sub>                   | 3           |     |  |

| Single pulse avalanche current                                            | L = 0.1 mH              | I <sub>AS</sub>                   | 3.8         |     |  |

| Single pulse avalanche energy                                             |                         | E <sub>AS</sub>                   | 7.2         | mJ  |  |

| Maximum power dissipation <sup>b</sup>                                    | T <sub>C</sub> = 25 °C  | Б                                 | 1.5         | W   |  |

| Maximum power dissipation -                                               | T <sub>C</sub> = 125 °C | $P_{D}$                           | 0.5         | V V |  |

| Operating junction and storage temperature range                          |                         | T <sub>J</sub> , T <sub>stg</sub> | -55 to +175 | °C  |  |

| THERMAL RESISTANCE RATINGS |                        |            |       |      |  |

|----------------------------|------------------------|------------|-------|------|--|

| PARAMETER                  |                        | SYMBOL     | LIMIT | UNIT |  |

| Junction-to-ambient        | PCB mount <sup>c</sup> | $R_{thJA}$ | 220   | °C/W |  |

| Junction-to-foot (drain)   |                        | $R_{thJF}$ | 100   | C/VV |  |

#### Notes

- a. Package limited

- b. Pulse test; pulse width  $\leq 300~\mu s,~duty~cycle \leq 2~\%$

- c. When mounted on 1" square PCB (FR4 material)

| PARAMETER                           | SYMBOL                   | TEST CONDITIONS                                                                                  |                                                 | MIN. | TYP.  | MAX.  | UNIT |

|-------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------|------|-------|-------|------|

| Static                              |                          |                                                                                                  |                                                 |      |       |       |      |

| Drain-source breakdown voltage      | V <sub>DS</sub>          | V <sub>GS</sub>                                                                                  | = 0, I <sub>D</sub> = 250 μA                    | 20   | -     | -     | V    |

| Gate-source threshold voltage       | V <sub>GS(th)</sub>      | V <sub>DS</sub> =                                                                                | · V <sub>GS</sub> , I <sub>D</sub> = 250 μA     | 0.45 | 0.6   | 1.5   | V    |

| Gate-source leakage                 | I <sub>GSS</sub>         | V <sub>DS</sub> =                                                                                | = 0 V, V <sub>GS</sub> = ± 8 V                  | -    | -     | ± 100 | nA   |

|                                     |                          | $V_{GS} = 0 V$                                                                                   | V <sub>DS</sub> = 20 V                          | -    |       | 1     |      |

| Zero gate voltage drain current     | I <sub>DSS</sub>         | V <sub>GS</sub> = 0 V                                                                            | V <sub>DS</sub> = 20 V, T <sub>J</sub> = 125 °C | -    | -     | 50    | μΑ   |

|                                     |                          | $V_{GS} = 0 V$                                                                                   | V <sub>DS</sub> = 20 V, T <sub>J</sub> = 175 °C | -    | -     | 150   |      |

| On-state drain current a            | I <sub>D(on)</sub>       | V <sub>GS</sub> = 4.5 V                                                                          | $V_{DS} \ge 5 V$                                | 1.5  | -     | -     | Α    |

|                                     |                          | V <sub>GS</sub> = 4.5 V                                                                          | I <sub>D</sub> = 1.2 A                          | -    | 0.200 | 0.280 | Ω    |

|                                     |                          | $V_{GS} = 4.5 \text{ V}$                                                                         | I <sub>D</sub> = 1.2 A, T <sub>J</sub> = 125 °C | -    | -     | 0.423 |      |

| Drain-source on-state resistance a  | R <sub>DS(on)</sub>      | $V_{GS} = 4.5 \text{ V}$                                                                         | I <sub>D</sub> = 1.2 A, T <sub>J</sub> = 175°C  | -    | -     | 0.510 |      |

|                                     |                          | $V_{GS} = 2.5 \text{ V}$                                                                         | I <sub>D</sub> = 1 A                            | -    | 0.261 | 0.360 |      |

|                                     |                          | V <sub>GS</sub> = 1.8 V                                                                          | $I_D = 0.2 A$                                   | -    | 0.320 | 0.450 |      |

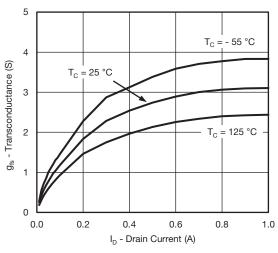

| Forward transconductance b          | 9 <sub>fs</sub>          | V <sub>DS</sub> :                                                                                | = 10 V, I <sub>D</sub> = 0.5 A                  | -    | 2.6   | -     | S    |

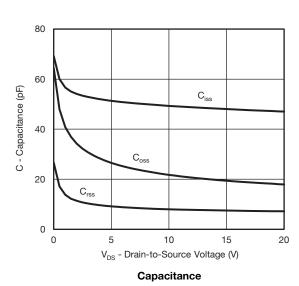

| Dynamic <sup>b</sup>                |                          |                                                                                                  |                                                 |      |       |       |      |

| Input capacitance                   | C <sub>iss</sub>         |                                                                                                  |                                                 | -    | 49    | 75    |      |

| Output capacitance                  | C <sub>oss</sub>         | $V_{GS} = 0 V$                                                                                   | $V_{DS} = 10 \text{ V}, f = 1 \text{ MHz}$      | -    | 22    | 32    | pF   |

| Reverse transfer capacitance        | C <sub>rss</sub>         |                                                                                                  |                                                 | -    | 8     | 12    |      |

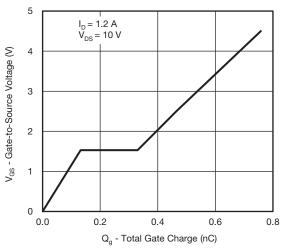

| Total gate charge <sup>c</sup>      | $Q_g$                    |                                                                                                  |                                                 | -    | 0.76  | 1.15  |      |

| Gate-source charge <sup>c</sup>     | $Q_{gs}$                 | $V_{GS} = 4.5 \text{ V}$                                                                         | $V_{DS} = 10 \text{ V}, I_{D} = 1.2 \text{ A}$  | -    | 0.13  | 1     | nC   |

| Gate-drain charge c                 | $Q_{gd}$                 |                                                                                                  |                                                 | -    | 0.33  | ı     |      |

| Gate resistance <sup>d</sup>        | $R_g$                    | f = 1 MHz                                                                                        |                                                 | 5.5  | 11.1  | 22.2  | Ω    |

| Turn-on delay time <sup>c</sup>     | t <sub>d(on)</sub>       |                                                                                                  |                                                 | -    | 3     | 5     |      |

| Rise time <sup>c</sup>              | t <sub>r</sub>           | $V_{DD}$ = 10 V, $R_L$ = 20 $\Omega$<br>$I_D \cong 0.5$ A, $V_{GEN}$ = 4.5 V, $R_g$ = 1 $\Omega$ |                                                 | -    | 21    | 31    | no   |

| Turn-off delay time <sup>c</sup>    | t <sub>d(off)</sub>      |                                                                                                  |                                                 | -    | 19    | 29    | ns   |

| Fall time <sup>c</sup>              | t <sub>f</sub>           |                                                                                                  |                                                 | -    | 17    | 25    |      |

| Source-Drain Diode Ratings and Char | acteristics <sup>b</sup> |                                                                                                  |                                                 |      |       |       |      |

| Pulsed current <sup>a</sup>         | I <sub>SM</sub>          |                                                                                                  |                                                 |      | -     | 3     | Α    |

| Forward voltage                     | $V_{SD}$                 | $I_F = 0.5 \text{ A}, V_{GS} = 0$                                                                |                                                 | _    | 0.8   | 1.2   | V    |

#### Notes

- a. Pulse test; pulse width  $\leq 300~\mu s,~duty~cycle \leq 2~\%$

- b. Guaranteed by design, not subject to production testing

- c. Independent of operating temperature

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

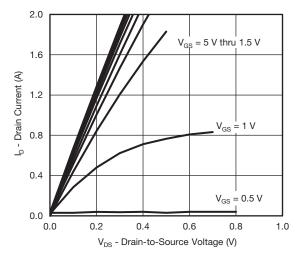

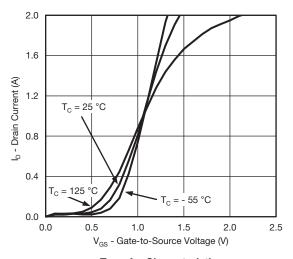

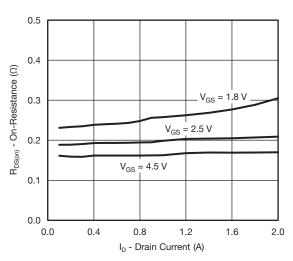

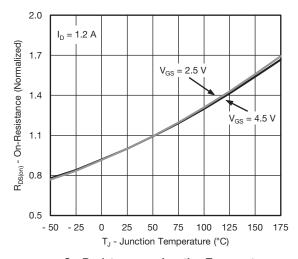

#### TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

#### **Output Characteristics**

#### Transconductance

#### **Transfer Characteristics**

On-Resistance vs. Drain Current

#### TYPICAL CHARACTERISTICS (25 °C, unless otherwise noted)

On-Resistance vs. Junction Temperature

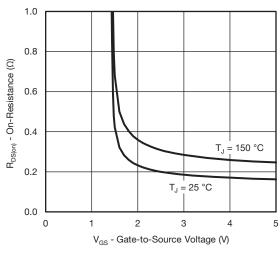

On-Resistance vs. Gate-to-Source Voltage

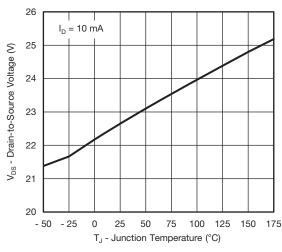

Drain Source Breakdown vs. Junction Temperature

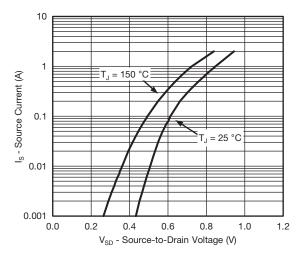

Source Drain Diode Forward Voltage

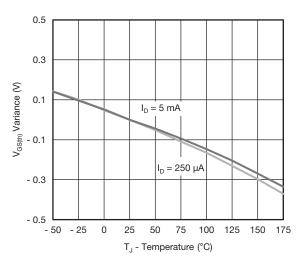

Threshold Voltage

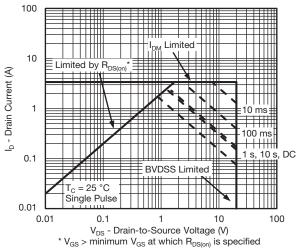

Safe Operating Area

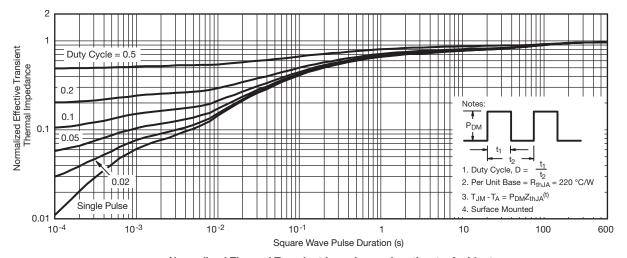

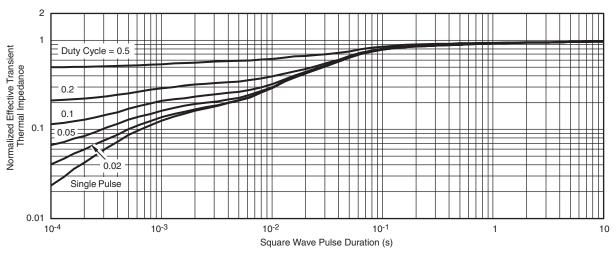

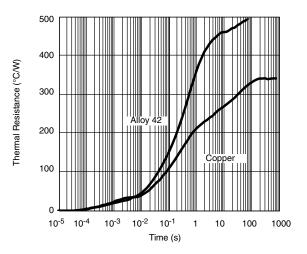

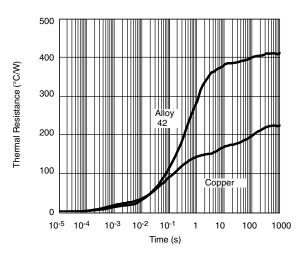

#### THERMAL RATINGS (T<sub>A</sub> = 25 °C, unless otherwise noted)

Normalized Thermal Transient Impedance, Junction-to-Ambient

Normalized Thermal Transient Impedance, Junction-to-Foot

#### Note

- The characteristics shown in the two graphs

- Normalized Transient Thermal Impedance Junction-to-Ambient (25 °C)

- Normalized Transient Thermal Impedance Junction-to-Foot (25 °C)

are given for general guidelines only to enable the user to get a "ball park" indication of part capabilities. The data are extracted from single pulse transient thermal impedance characteristics which are developed from empirical measurements. The latter is valid for the part mounted on printed circuit board - FR4, size 1" x 1" x 0.062", double sided with 2 oz. copper, 100 % on both sides. The part capabilities can widely vary depending on actual application parameters and operating conditions.

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="https://www.vishay.com/ppg?67394">www.vishay.com/ppg?67394</a>.

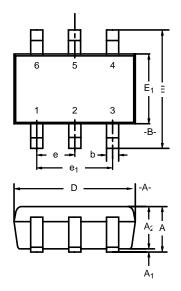

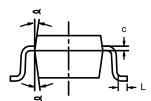

#### SC-70: 6-LEADS

|                                             | MILLIMETERS |      |      | I        | NCHE  | S     |

|---------------------------------------------|-------------|------|------|----------|-------|-------|

| Dim                                         | Min         | Nom  | Max  | Min      | Nom   | Max   |

| Α                                           | 0.90        | _    | 1.10 | 0.035    | _     | 0.043 |

| $A_1$                                       | _           | -    | 0.10 | -        | _     | 0.004 |

| A <sub>2</sub>                              | 0.80        | _    | 1.00 | 0.031    | _     | 0.039 |

| b                                           | 0.15        | _    | 0.30 | 0.006    | _     | 0.012 |

| С                                           | 0.10        | _    | 0.25 | 0.004    | _     | 0.010 |

| D                                           | 1.80        | 2.00 | 2.20 | 0.071    | 0.079 | 0.087 |

| Е                                           | 1.80        | 2.10 | 2.40 | 0.071    | 0.083 | 0.094 |

| E <sub>1</sub>                              | 1.15        | 1.25 | 1.35 | 0.045    | 0.049 | 0.053 |

| е                                           | 9 0.65BSC   |      |      | 0.026BSC | ;     |       |

| e <sub>1</sub>                              | 1.20        | 1.30 | 1.40 | 0.047    | 0.051 | 0.055 |

| L                                           | 0.10        | 0.20 | 0.30 | 0.004    | 0.008 | 0.012 |

| 4                                           | 7°Nom       |      |      |          | 7°Nom |       |

| ECN: S-03946—Rev. B, 09-Jul-01<br>DWG: 5550 |             |      |      |          |       |       |

Document Number: 71154 www.vishay.com 06-Jul-01 sww.vishay.com

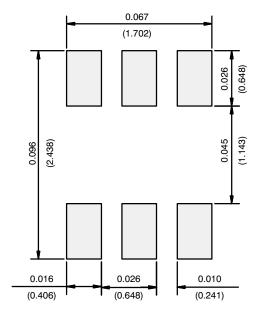

#### **RECOMMENDED MINIMUM PADS FOR SC-70: 6-Lead**

Recommended Minimum Pads Dimensions in Inches/(mm)

Return to Index

#### **Power MOSFETs**

**Application Note AN917**

# Dual-Channel LITTLE FOOT® 6-Pin SC-70 MOSFET Copper Leadframe Version Recommended Pad Pattern and Thermal Performance 175 °C Rated Part

#### INTRODUCTION

The new dual 6-pin SC-70 package with a copper leadframe enables improved on-resistance values and enhanced thermal performance as compared to the existing 3-pin and 6-pin packages with Alloy 42 leadframes. These devices are intended for small to medium load applications where a miniaturized package is required. Devices in this package come in a range of on-resistance values, in n-channel and p-channel versions. This technical note discusses pin-outs, package outlines, pad patterns, evaluation board layout, and thermal performance for the dual-channel version.

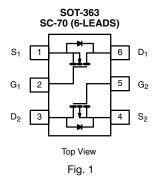

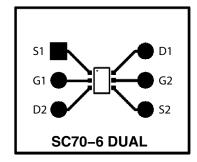

#### **PIN-OUT**

Figure 1 shows the pin-out description and pin 1 identification for the dual-channel SC-70 device in the 6-pin configuration. Both n-and p-channel devices are available in this package – the drawing example below illustrates the p-channel device.

For package dimensions see outline drawing SC-70 (6-Leads) (<a href="https://www.vishay.com/doc?71154">www.vishay.com/doc?71154</a>)

#### **BASIC PAD PATTERNS**

Revision: 15-Apr-13

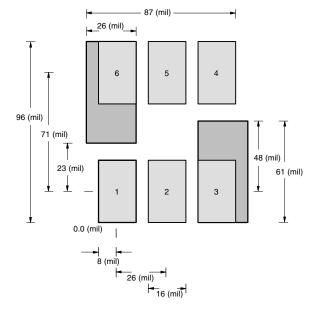

See Application Note 826, Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs, (<a href="www.vishay.com/doc?72286">www.vishay.com/doc?72286</a>) for the SC-70 6-pin basic pad layout and dimensions. This pad pattern is sufficient for the low-power applications for which this package is intended. Increasing the drain pad pattern (figure 2) yields a reduction in thermal resistance and is a preferred footprint.

Fig. 2 SC-70 (6 leads) Dual

## **EVALUATION BOARD FOR THE DUAL-CHANNEL** SC70-6

The 6-pin SC-70 evaluation board (EVB) shown in figure 3 measures 0.6 in. by 0.5 in. The copper pad traces are the same as described in the previous section, Basic Pad Patterns. The board allows for examination from the outer pins to the 6-pin DIP connections, permitting test sockets to be used in evaluation testing.

The thermal performance of the dual 6-pin SC-70 has been measured on the EVB, comparing both the copper and Alloy > 42 leadframes. This test was then repeated using the 1-inch<sup>2</sup> PCB with dual-side copper coating.

A helpful way of displaying the thermal performance of the 6-pin SC-70 dual copper leadframe is to compare it to the traditional Alloy 42 version.

APPLICATION NO

Document Number: 75130

## Dual-Channel LITTLE FOOT® 6-Pin SC-70 MOSFET Copper Leadframe Version Recommended Pad Pattern and Thermal Performance 175 °C Rated Part

#### Front of Board SC70-6

Back of Board SC70-6

Fig. 3

#### THERMAL PERFORMANCE

## Junction-to-Foot Thermal Resistance (the Package Performance)

Thermal performance for the dual SC-70 6-pin package is measured as junction-to-foot thermal resistance, in which the "foot" is the drain lead of the device as it connects with the body. The junction-to-foot thermal resistance for this device is typically 80 °C/W, with a maximum thermal resistance of approximately 100 °C/W. This data compares favorably with another compact, dual-channel package - the dual TSOP-6 - which features a typical thermal resistance of 75 °C/W and a maximum of 90 °C/W.

#### Power Dissipation for 175 °C Rated Part

The typical R $\theta$ JA for the dual-channel 6-pin SC-70 with a copper leadframe is 224 °C/W steady-state, compared to 413 °C/W for the Alloy 42 version. All figures are based on the 1-inch² FR4 test board. The following example shows how the thermal resistance impacts power dissipation for the dual 6-pin SC-70 package at varying ambient temperatures.

Alloy 42 Leadframe

PLICATION

Д

| ALLOY 42 LEADFRAME                                                                  |                                                                                        |  |  |  |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|

| ROOM AMBIENT 25 °C                                                                  | ELEVATED AMBIENT 60 °C                                                                 |  |  |  |

| $P_D = \frac{T_{J(max.)} - T_A}{R\theta_{JA}}$                                      | $P_{D} = \frac{T_{J(max.)} - T_{A}}{R\theta_{JA}}$                                     |  |  |  |

| $P_{D} = \frac{175 ^{\circ}\text{C} - 25 ^{\circ}\text{C}}{413 ^{\circ}\text{C/W}}$ | $P_{D} = \frac{175  ^{\circ}\text{C} - 60  ^{\circ}\text{C}}{413  ^{\circ}\text{C/W}}$ |  |  |  |

| $P_D = 363 \text{ mW}$                                                              | P <sub>D</sub> = 278 mW                                                                |  |  |  |

| COOPER LEADFRAME                                                                       |                                                                                        |  |  |  |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|

| ROOM AMBIENT 25 °C                                                                     | ELEVATED AMBIENT 60 °C                                                                 |  |  |  |

| $P_{D} = \frac{T_{J(max.)} - T_{A}}{R\theta_{JA}}$                                     | $P_{D} = \frac{T_{J(max.)} - T_{A}}{R\theta_{JA}}$                                     |  |  |  |

| $P_{D} = \frac{175  ^{\circ}\text{C} - 25  ^{\circ}\text{C}}{224  ^{\circ}\text{C/W}}$ | $P_{D} = \frac{175  ^{\circ}\text{C} - 60  ^{\circ}\text{C}}{224  ^{\circ}\text{C/W}}$ |  |  |  |

| $P_D = 669 \text{ mW}$                                                                 | $P_D = 513 \text{ mW}$                                                                 |  |  |  |

Although they are intended for low-power applications, devices in the 6-pin SC-70 dual-channel configuration will handle power dissipation in excess of 0.5 W.

#### **TESTING**

To further aid the comparison of copper and Alloy 42 leadframes, Figures 4 and 5 illustrate the dual-channel 6-pin SC-70 thermal performance on two different board sizes and pad patterns. The measured steady-state values of  $R\theta_{JA}$  for the dual 6-pin SC-70 with varying leadframes are as follows:

| LITTLE FOOT 6-PIN SC-70                                                      |          |          |  |  |  |

|------------------------------------------------------------------------------|----------|----------|--|--|--|

| ALLOY 42 COPPER                                                              |          |          |  |  |  |

| 1) Minimum recommended pad pattern on the EVB board (see fig. 3).            | 518 °C/W | 344 °C/W |  |  |  |

| 2) Industry standard 1-inch <sup>2</sup> PCB with maximum copper both sides. | 413 °C/W | 224 °C/W |  |  |  |

The results indicate that designers can reduce thermal resistance ( $\theta_{JA}$ ) by 34 % simply by using the copper leadframe device as opposed to the Alloy 42 version. In this example, a 174 °C/W reduction was achieved without an increase in board area. If an increase in board size is feasible, a further 120 °C/W reduction can be obtained by utilizing a 1-inch<sup>2</sup>. PCB area.

Revision: 15-Apr-13 2 Document Number: 75130

## Dual-Channel LITTLE FOOT® 6-Pin SC-70 MOSFET Copper Leadframe Version Recommended Pad Pattern and Thermal Performance 175 °C Rated Part

The dual copper leadframe versions have the following suffix:

Dual: Sx19xxEDH or Sx19xxEEH

Compl.: Sx15xxEDH or Sx15xxEEH

Fig. 4 Dual SC70-6 Thermal Performance on EVB

Fig. 5 Dual SC70-6 Comparison on 1-inch<sup>2</sup> PCB

Vishay

#### **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

单击下面可查看定价,库存,交付和生命周期等信息

>>Vishay(威世)