# **Product Specification**

# XBLW MAX490

High-speed Transceiver

#### **Description**

The MAX490, which is used for RS-485/RS-422 communication, is a high-speed transceiver with full-duplex communication that includes a driver and a receiver. When the receiver input is open or shorted, it ensures that the receiver output is at a logic high level. If all transmitters attached to the terminated matching bus are disabled (high-impedance), the receiver will output a logic high level.

The MAX490 has a low-rate driver that can reduce EMI and reflections caused by improper terminal matching cables, and achieve error-free data transfer rates up to 2.5Mbps. In addition, the MAX490 has a 1/8 unit load input impedance, and up to 256 transmitters and receivers can be attached to the bus.

#### Feature:

- Wide power range, full duplex

- > Up to 256 transceivers are allowed to be attached on the bus

- Powerful swing rate control function helps to achieve error-free data transmission

- > Provide a standard SOP-8 and DIP-8 package

#### **Applications**

- Industrial control

- Security system

- Power inverter

- POS machine

- Lighting system

## **Ordering Information**

| Product Model  | Package Type | Marking   | Packing | Packing Qty  |

|----------------|--------------|-----------|---------|--------------|

| XBLW MAX490ESA | SOP-8        | MAX490ESA | Tape    | 2500Pcs/Reel |

| XBLW MAX490EPA | DIP-8        | MAX490EPA | Tube    | 2000Pcs/Box  |

|                |              |           |         |              |

|                |              |           |         |              |

## Pin logic diagram and description

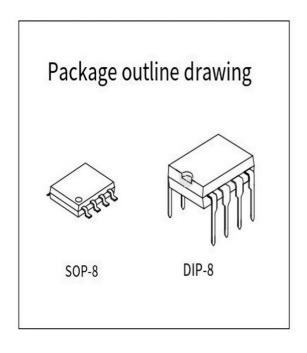

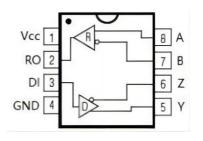

Figure 1: Pin diagram of MAX490

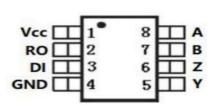

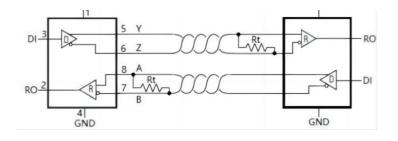

Figure 2: MAX490 logic diagram

## **Pin Description**

| lead<br>Full duplex | Name | Function                                                                                                                                                                                                                                         |

|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                   | VCC  | Positive phase supply end :3.0 ≤ VCC ≤ 5.5V                                                                                                                                                                                                      |

| 2                   | RO   | Receiver output. If A-B $\geq$ -50mV, RO output is high; If A-B $\leq$ -200mV, RO output is low                                                                                                                                                  |

| 3                   | וט   | Drive input. The low level on the DI forces the same phase output to be low level and the reverse phase output to be high level. Similarly, a high level on the DI will force the in-phase output to be high and the anti-phase output to be low |

| 4                   | GND  | Ground                                                                                                                                                                                                                                           |

| 5                   | Y    | Drive in-phase output end                                                                                                                                                                                                                        |

| 6                   | Z    | Drive inverting output end                                                                                                                                                                                                                       |

| 7                   | В    | Receiver inverting input                                                                                                                                                                                                                         |

| 8                   | Α    | Receiver in-phase input                                                                                                                                                                                                                          |

## **Absolute maximum rating**

| Project                      | Symbol | Parameter       | unit         |

|------------------------------|--------|-----------------|--------------|

| Supply voltage               | VCC    | + 7             | V            |

| Drive input voltage          | DI     | -0.3 to VCC+0.3 | V            |

| Drive output voltage         | Y, Z   | -8 to +13       | V            |

| Receiver input voltage       | A, B   | -8 to +13       | V            |

| Receiver output voltage      | RO     | -0.3 ~ VCC+0.3  | V            |

| Continuous power consumption | SOP8   | 471             | mW           |

| Operating temperature range  |        | 0 ~ +70         | $\mathbb{C}$ |

| Storage temperature          |        | -65 ~ +150      | $^{\circ}$ C |

| Welding temperature, 10S     | TLEAD  | 245             | $^{\circ}$   |

#### Note:

Any application attempt above the absolute maximum rating has the potential to cause permanent damage to the product, and the absolute maximum rating does not mean that the product will function properly under conditions other than the calibrated electrical characteristics.

# **Dc electrical characteristics** (unless otherwise stated, VCC=+5V $\pm$ 5,TA=TMIN ~ TMAX, typical values at VCC=+5V,TA= 25 $^{\circ}$ C) (Note 1)

| Parameter                                                | Symbol           | Test con                | dition   | MIN      | TYP   | MAX  | Units |

|----------------------------------------------------------|------------------|-------------------------|----------|----------|-------|------|-------|

| Drives                                                   |                  |                         |          |          |       |      |       |

| Supply voltage                                           | VCC              |                         |          | 3.0      |       | 5.5  | V     |

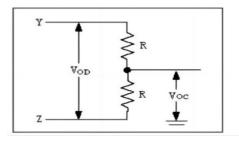

| Differential driver output (no load)                     | V <sub>OD1</sub> | Figure 4                |          | 1.5      |       | 5    | V     |

| Differential driver output                               |                  | Figure 4, R=50Ω(RS-422) |          | 2.0      |       | 5    | V     |

| Differential driver output                               | V <sub>OD2</sub> | Figure 4, R=27Ω(RS-     | -485)    | 1.5      |       | 5    | V     |

| Amplitude change in differential output voltage (Note 2) | ΔVod             | Figure 4, R=50Ω or      | R=27Ω    |          |       | 0.2  | V     |

| Drive common mode output voltage                         | Voc              | Figure 4, R=50Ω or      | R=27Ω    | 1        |       | 3    | V     |

| Amplitude change in common mode voltage (Note 2)         | ΔVος             | Figure 4, R=50Ω or      | R=27Ω    |          |       | 0.2  | V     |

| Input high voltage                                       | V <sub>IH1</sub> | DE,DI,/RE               |          | 2.0      |       |      | V     |

| Input low voltage                                        | VIL1             | DE,DI,/RE               |          |          |       | 0.8  | V     |

| DI input lag                                             | <b>V</b> HYS     |                         |          |          | 100   |      | mV    |

| Input current (A,B) full duplex                          | T                | DE=GND                  | VIN= 12V |          |       | 125  |       |

| Input current (A,b) full duplex                          | IIN4             | VCC=GND or<br>5.25V     | VIN=-7V  | - 75     |       |      | μA    |

|                                                          |                  | -7V≦VOUT ≦VCC           |          | - 250    |       |      | mA    |

| Drive short circuit output                               | Iosd             | 0V≦VOUT ≦ 12V           |          |          |       | 250  |       |

| current                                                  |                  | 0V≦VOUT ≦VCC            |          | ±25      |       |      |       |

| Receiver                                                 |                  |                         |          |          |       |      |       |

| Receiver differential threshold voltage                  | <b>V</b> тн      | -7V≦VCM≦ 12V            |          | - 200    | - 110 | - 50 | mV    |

| Receiver input lag                                       | <b>Δ V</b> TH    |                         |          |          | 30    |      | mV    |

| Receiver output high voltage                             | Vон              | IO=-4mA,VID=-50n        | nV       | Vcc -1.5 |       |      | V     |

| Receiver output low voltage                              | Vol              | IO=4mA,VID=-200r        | mV       |          |       | 0.4  | V     |

| Three state output current at receiver end               | <b>I</b> ozr     | 0.4V≦VO ≦2.4V           |          |          |       | ±1   | μΑ    |

| Receiver input impedance                                 | RIN              | -7V≦VCM≦ 12V            |          | 96       |       |      | ΚΩ    |

| Receiver output short-circuit current                    | Iosr             | 0V ≦ VRO ≦ VCC          |          | ±7       |       | ±95  | mA    |

| Supply current                                           |                  |                         |          | _        |       |      |       |

| Static working current                                   | Icc              | No load, DI=0 or VC     | C        |          | 270   | 600  | μA    |

| ESD electrostatic protection                             |                  |                         |          |          |       |      |       |

| ESD HBM                                                  |                  | ESD HBM                 |          |          |       | 3000 | V     |

Note 1: All current into the device is positive and all current out of the device is negative; All voltages, if without exception, are stated to be correct.

Note 2: When the DI input changes state,  $\Delta V_{OD}$  and  $\Delta V_{OC}$  are  $V_{OD}$  and  $V_{OC}$  changes, respectively.

Note 3: Maximum current is used for peak current only before feedback current limit, minimum current is used during current limit.

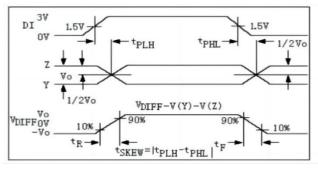

**Conversion characteristics** (If not stated otherwise, VCC =  $\pm$  5 %, TA = TMIN  $\sim$  TMAX,

typical value at VCC = + 5V, TA= $25^{\circ}$ C)

| Parameter                              | Symbol         | Condition                                                        | MIN | TYP | MAX  | Units |

|----------------------------------------|----------------|------------------------------------------------------------------|-----|-----|------|-------|

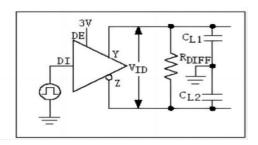

| Drive input to output                  | TDPLH          | Figures 5和6,RDIFF=54Ω                                            | 250 | 720 | 900  |       |

| Drive input to output                  | TDPHL          | CL1=CL2=100pF                                                    | 250 | 720 | 900  | ns    |

| Drive output  t DPLH - t<br>DPHL       | Tohkew         | Figures 5和6,RDIFF=54Ω<br>CL1=CL2=100pF                           |     | - 3 | ±100 | ns    |

| Drive up or down time                  | t DR, t DF     | Figures 5和6,RDIFF=54Ω<br>CL1=CL2=100pF                           | 200 | 530 | 750  | ns    |

| Maximum data rate                      | FMAX           |                                                                  |     |     | 2.5  | М     |

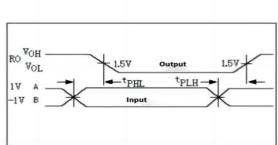

| Receiver input to output               | Trplh<br>Trphl | Figures 7 a n d 8, rise and fall times,   VID ≥2.0V VID ≦ 15 n s |     | 127 | 200  | ns    |

| Differential receiver  t DPLH - t DPHL | Trskd          | FIG. 7 a n d 8, rise and fall times of   VID ≥2.0V VID ≦ 15 n s  |     | 3   | ±30  | ns    |

#### **Feature Sheet**

| Send |        |   |  |  |

|------|--------|---|--|--|

| Туре | Output |   |  |  |

| DI   | В      | Α |  |  |

| 1    | 0      | 1 |  |  |

| 0    | 1      | 0 |  |  |

| Receive       |        |  |  |

|---------------|--------|--|--|

| Input         | Output |  |  |

| A-B           | RO     |  |  |

| P - 0.05 - V  | 1      |  |  |

| 0.2 V or less | 0      |  |  |

| Open/shorted  | 1      |  |  |

DIP/SOP

Figure 3: MAX490 typical full duplex application circuit

#### **Expatiate**

The MAX490 high-speed transceiver for RS-485 / RS-422 communication contains a drive and receiver. It has a failure protection circuit to ensure that the receiver output logic high level when the receiver input is open or short circuit. If all senders attached to the terminal match bus are disabled (high resistance), the receiver will output the logic high level. MAX490 With a low pendulum rate drive, it can reduce EMI and reflection due to improper cable termination, enabling error-free data transmission of up to 2 . 5 Mbps. MAX490 Is a full-duplex transceiver.

#### **Receiver input filtering**

When working in the MAX490 in 2.5 Mbps mode,

its receiver also includes the input filtering function in addition to having the input lag.

This filtering function improves the noise suppression ability of differential signals that rise and fall slowly.

The filter increases the receiver transmission delay by 25%.

#### Fail protect

The MAX490 ensures that the receiver output logic high level when the receiver input is short circuit or open circuit, or when all drives attached to the terminal matching transmission line are disabled. This was achieved by setting the receiver input threshold to-50 mV and-200 mV, respectively. If the differential receiver input voltage (A-B) is greater than or equal to-50 mV, RO is logic high level; if the voltage (A-B) is less than or equal to-200 mV, RO is logic low level.

When all the transmitters attached to the terminal matching bus are disabled, the receiver differential input voltage is pulled to 0V through the terminal resistance. According to the receiver threshold, a logical high level with a 50 mV minimum noise tolerance can be achieved. Unlike previous failure protection devices, the-50 mV to-200 mV threshold voltage meets the EIA / TIA-485 standard of  $\pm$  200 mV

#### 256 transceivers are attached to the bus

The standard RS-485 receiver has an input impedance of 12 k $\Omega$  (1 unit load), and the standard drive drives up to 32 unit loads. MAX490 The receiver of the transceiver has a 1 / 8 unit of load input impedance (96 k $\Omega$ ), allowing up to 256 transceivers to be attached in parallel to the same communication bus. These devices may be combined arbitrarily or with other RS-485 transceivers and may be attached to the same bus as long as the total load does not exceed 32 unit loads.

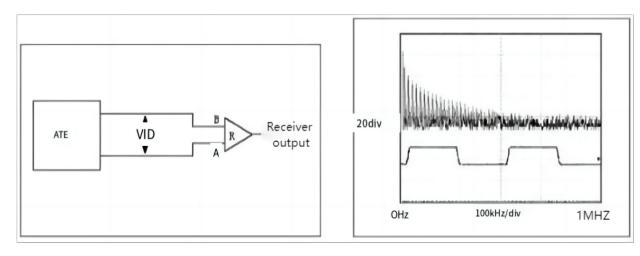

#### **Reduce EMI and reflection**

MAX490 Low pendulum rate drive can reduce the EMI, and reduce the reflection caused by inappropriate terminal matching cable, figure 9 shows the high frequency harmonic element in amplitude is lower than the general case, the drive along the time related to the length of the terminal, the following equation represents the relationship:  $\frac{10\times1.5ns}{ft}$ , tRISE is the drive along the time.

Figure 4: Drive DC test load

Figure 5: Drive timing test circuit

Figure 6: Driver propagation delay

Figure 7: Receiver propagation delay

Figure 8: Receiver propagation delay test circuit

Figure 9: MAX490 driver when transmitting 20kHz signal FFT diagram of output waveform

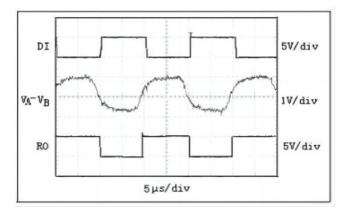

Figure 10: Driving 4000 ft cable at 50kHz MAX490 system differential voltage linear transponder

# **Package Outline Dimensions**

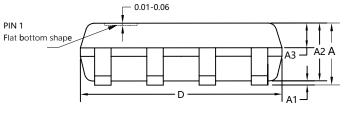

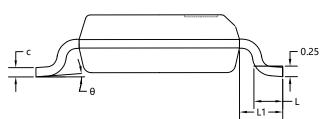

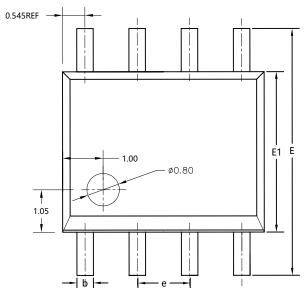

#### SOP-8

| SYMBOL   | MILLIMETER |      |      |  |

|----------|------------|------|------|--|

| STIVIBOE | MIN        | NOM  | MAX  |  |

| А        | 1.55       | 1.65 | 1.75 |  |

| A1       | 0.10       | 0.15 | 0.20 |  |

| A2       | 1.35       | 1.45 | 1.55 |  |

| A3       | 0.60       | 0.70 | 0.80 |  |

| b        | 0.30       | 0.40 | 0.50 |  |

| С        | 0.17       | 0.20 | 0.25 |  |

| D        | 4.80       | 4.90 | 5.00 |  |

| E        | 5.80       | 6.00 | 6.20 |  |

| E1       | 3.80       | 3.90 | 4.00 |  |

| е        | 1.27BSC    |      |      |  |

| L        | 0.50       | 0.60 | 0.70 |  |

| L1       | 1.05REF    |      |      |  |

| θ        | 0°         | 4°   | 8°   |  |

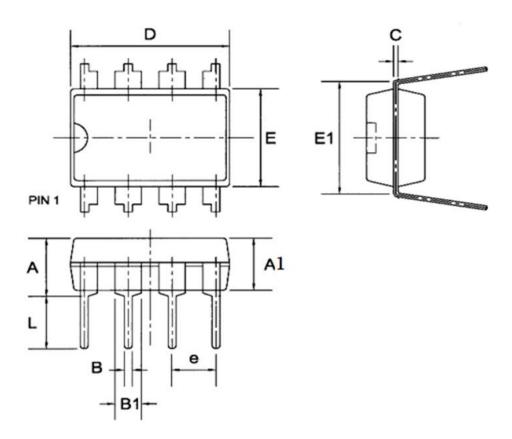

DIP-8

|        | Dimensions in Millimeters |      |      |  |

|--------|---------------------------|------|------|--|

| Symbol | Min                       | Nom  | Max  |  |

| A      |                           |      | 4.31 |  |

| A1     | 3.15                      | 3.30 | 3.65 |  |

| В      | 0.38                      | 0.46 | 0.51 |  |

| B1     | 1.27                      | 1.55 | 1.77 |  |

| С      | 0.20                      | 0.25 | 0.30 |  |

| D      | 8.95                      | 9.40 | 9.45 |  |

| Е      | 6.15                      | 6.20 | 6.65 |  |

| E1     |                           | 7.60 |      |  |

| e      |                           | 2.54 |      |  |

| L      | 3.00                      | 3.30 | 3.60 |  |

#### Statement:

- XBLW reserves the right to modify the product manual without prior notice! Before placing an order, customers need to confirm whether the obtained information is the latest version and verify the completeness of the relevant information.

- Any semi-guide product is subject to failure or malfunction under specified conditions. It is the buyer's responsibility to comply with safety standards when using XBLW products for system design and whole machine manufacturing. And take the appropriate safety measures to avoid the potential in the risk of loss of personal injury or loss of property situation!

- XBLW products are not licensed for life support, military, aerospace and other applications, and XBLW will not be responsible for the consequences of the use of products in these fields.

- If any or all XBLW products (including technical data, services) described or contained in this document are subject to any applicable local export control laws and regulations, they may not be exported without an export license from the relevant authorities in accordance with such laws.

- The specifications of any and all XBLW products described or contained in this document specify the performance, characteristics, and functionality of said products in their standalone state, but do not guarantee the performance, characteristics, and functionality of said products installed in Customer's products or equipment. In order to verify symptoms and conditions that cannot be evaluated in a standalone device, the Customer should ultimately evaluate and test the device installed in the Customer's product device.

- XBLW documentation is only allowed to be copied without any alteration of the content and with the relevant authorization. XBLW assumes no responsibility or liability for altered documents.

- XBLW is committed to becoming the preferred semiconductor brand for customers, and XBLW will strive to provide customers with better performance and better quality products.

## 单击下面可查看定价,库存,交付和生命周期等信息

## >>XBLW(芯伯乐)