# 2 A, 1- or 2- Cell Li-Ion Battery Charger in 3mm x 3mm Package

### **DESCRIPTION**

The MP2615A is a high-efficiency, switch mode battery charger suitable for 1- or 2- cell lithiumion or lithium-polymer applications. The MP2615A is capable of delivering 2 A of charge current programmable via an accurate sense resistor over the entire input range.

The MP2615A regulates the charge current and full battery voltage using two control loops to achieve high-accuracy constant current (CC) charge and constant voltage (CV) charge.

Constant-off-time (COT) control allows operation at up to 99% duty cycle when the battery voltage is close to the input voltage, ensuring the charge current always remains at a relatively high level.

The battery temperature and charging status are always monitored during each charging cycle. Two status monitor output pins are provided to indicate the battery charging status and input power status. Also, the MP2615A features internal reverse-blocking protection.

The MP2615A is available in a 3mm × 3mm 16-pin QFN package.

### **FEATURES**

- 4.75 V to 18 V Operating Input Voltage

- Up to 99% Duty Cycle Operation

- Up to 2 A Programmable Charging Current

- ±0.75% Full Battery Voltage Accuracy

- 4.2 V/Cell and 4.35 V/Cell Selection for Full Battery Voltage

- Fully Integrated Power Switches

- Internal Loop Compensation

- No External Reverse-Blocking Diode Required

- Preconditioning for Fully Depleted Battery

- Charging Operation Indicator

- Programmable Safety Timer

- Thermal Shutdown Protection

- Cycle-by-Cycle Over-Current Protection

- Battery Temperature Monitor and Protection

### APPLICATIONS

- Smart Phones

- Portable Hand-Held Solutions

- Portable Media Players

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance.

"MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

Analog digital adaptive modulation (ADAM) and advanced asynchronous modulation (AAM) are trademarks of Monolithic Power Systems, Inc.

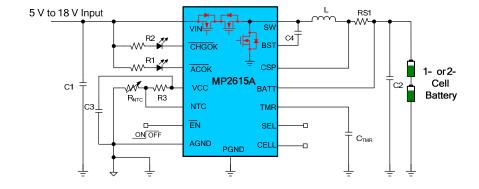

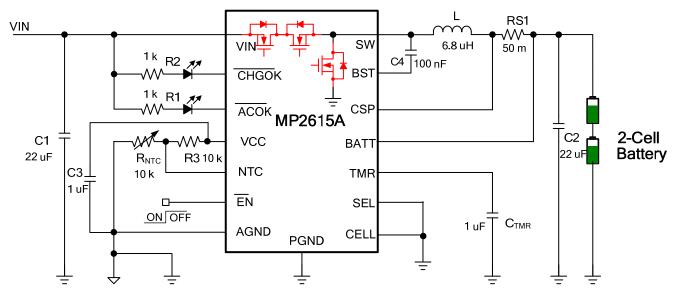

### TYPICAL APPLICATION

### ORDERING INFORMATION

| Part Number* | Package            | Top Marking |

|--------------|--------------------|-------------|

| MP2615AGQ    | QFN-16 (3mm × 3mm) | See Below   |

<sup>\*</sup> For Tape & Reel, add suffix –Z (e.g. MP2615AGQ–Z).

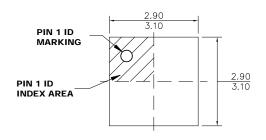

### **TOP MARKING**

ANKY

ANK: Product code of MP2615A

Y: Year code LLL: Lot number

### **PACKAGE REFERENCE**

###

| Thermal Resistance | $\boldsymbol{\theta}^{(4)}  \boldsymbol{\theta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |      |

|--------------------|-------------------------------------------------------|-------------------------|------|

| QFN-16 (3mm x 3mm) | 50                                                    | 12                      | °C/W |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

### **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12 V,  $V_{CELL}$  = 0 V,  $V_{SEL}$  = 0 V, C1 = 22  $\mu$ F, C2 = 22  $\mu$ F,  $T_A$  = 25°C, unless otherwise noted.

| · · · · · · · · · · · · · · · · · · ·      | 1                     | V, C1 - 22 μΓ, C2 - 22 μΓ, 1                      | -     |      | 1     | Units           |

|--------------------------------------------|-----------------------|---------------------------------------------------|-------|------|-------|-----------------|

| Parameter                                  | Symbol                | Condition                                         | Min   | Тур  | Max   | Units           |

| Input voltage and curre                    | nt                    | T                                                 |       | Т    |       | ı               |

| Input voltage                              | $V_{IN}$              | V <sub>CELL</sub> = 4 V                           | 4.5   | 5    | 18    | V               |

|                                            |                       | V <sub>CELL</sub> = 0 V                           | 8.75  | 12   | 18    |                 |

| Under-voltage lockout threshold rising     | $V_{\text{UVLO}}$     |                                                   | 3.55  | 3.75 | 3.95  | V               |

| Under-voltage lockout threshold hysteresis |                       |                                                   |       | 225  |       | mV              |

| Supply current                             | I <sub>SHDN</sub>     | $\overline{\sf EN}$ = 4 V, Shutdown current       |       | 0.27 |       | mA              |

| Supply current                             | ΙQ                    | EN = 0 V, Quiescent current                       |       | 1.1  |       | IIIA            |

| Power MOS                                  |                       |                                                   |       | •    | · ·   | · ·             |

| High-side switch on resistance             | R <sub>H_DS(ON)</sub> | Measured from VIN to SW                           |       | 110  |       | mΩ              |

| Low-side switch on resistance              | R <sub>L_DS(ON)</sub> |                                                   |       | 110  |       | mΩ              |

| Switch leakage                             |                       | $\overline{EN}$ = 4 V, $V_{SW}$ = 0 V             |       | 0    | 1     | μA              |

| Frequency and time pa                      | rameter               |                                                   |       |      | 1     | •               |

| Switching frequency                        | F <sub>sw</sub>       | V <sub>BATT</sub> = 7.5 V                         |       | 760  |       | kHz             |

| Foldback frequency                         |                       | V <sub>BATT</sub> = 0 V                           |       | 160  |       | kHz             |

| Minimum off time (5)                       | T <sub>OFF</sub>      | V <sub>BATT</sub> = 9 V                           |       | 200  |       | ns              |

| Charging parameter                         | l .                   |                                                   |       | ·    | I     | - I             |

| Tamainal battamaltam.                      | .,                    | V <sub>SEL</sub> = 0 V                            | 4.328 | 4.35 | 4.386 | V/Cell          |

| Terminal battery voltage                   | $V_{BATT\_FULL}$      | V <sub>SEL</sub> = 4 V                            | 4.168 | 4.2  | 4.252 |                 |

|                                            | $V_{BOVP}$            | V <sub>SEL</sub> = 0 V<br>V <sub>CELL</sub> = 0 V | 8.62  | 8.99 | 9.36  |                 |

| Battery over-voltage                       |                       | V <sub>SEL</sub> =4 V<br>V <sub>CELL</sub> = 0 V  | 8.34  | 8.71 | 9.08  | V               |

| threshold                                  |                       | V <sub>SEL</sub> =0 V<br>V <sub>CELL</sub> = 4 V  | 4.3   | 4.49 | 4.67  |                 |

|                                            |                       | V <sub>SEL</sub> = 4 V<br>V <sub>CELL</sub> = 4 V | 4.17  | 4.36 | 4.54  |                 |

| Recharge threshold at                      | V <sub>RECH</sub>     | V <sub>SEL</sub> = 0 V                            |       | 4.1  |       | V/Cell          |

| $V_{BATT}$                                 |                       | V <sub>SEL</sub> = 4 V                            |       | 4.0  |       |                 |

| Recharge hysteresis                        |                       |                                                   |       | 150  |       | mV/Cell         |

| Trickle charge voltage                     | V <sub>TC</sub>       | V <sub>SEL</sub> = 0 V                            |       | 3.1  |       | V/Cell          |

| threshold                                  |                       | V <sub>SEL</sub> = 4 V                            |       | 3.0  |       | - v/Cell        |

| Trickle charge hysteresis                  |                       |                                                   |       | 225  |       | mV/Cell         |

| Peak current limit                         |                       | CC                                                | 3.2   |      |       | ۸               |

| reak current iiiliit                       |                       | Trickle                                           |       | 2.2  |       | A               |

| CC current                                 | I <sub>cc</sub>       | RS1 = 50 mΩ                                       | 1.8   | 2    | 2.2   | Α               |

| Trickle charge current                     | I <sub>TC</sub>       |                                                   | 5%    | 10%  | 15%   | I <sub>CC</sub> |

### **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = 12 V,  $V_{CELL}$  = 0 V,  $V_{SEL}$  = 0 V, C1 = 22  $\mu$ F, C2 = 22  $\mu$ F,  $T_A$  = 25°C, unless otherwise noted.

| voltage (CSF to BATT)                                                                  | V <sub>SENSE</sub>                 |                                       | 90    | 10%<br>300<br>100 | 15%  | I <sub>CC</sub> mV |

|----------------------------------------------------------------------------------------|------------------------------------|---------------------------------------|-------|-------------------|------|--------------------|

| (reverse blocking)  Maximum current-sense voltage (CSP to BATT)  CSP, BATT current Ic. |                                    | Charging disabled                     | 90    |                   | 110  |                    |

| voltage (CSP to BATT)  CSP, BATT current  Ic                                           |                                    |                                       | 90    | 100               | 110  | m\/                |

| <u> </u>                                                                               | <sub>CSP</sub> , I <sub>BATT</sub> |                                       |       |                   | 110  | mV                 |

| ACOK/CHGOK open-drain                                                                  |                                    |                                       |       |                   | 3    | μΑ                 |

| sink current                                                                           |                                    | $V_{DRAIN} = 0.3 V$                   | 5     |                   |      | mA                 |

| VCC regulator output                                                                   |                                    |                                       | •     |                   |      |                    |

| VCC output voltage                                                                     | V <sub>CC</sub>                    |                                       | 4.25  | 4.5               | 4.75 | V                  |

| VCC load regulation                                                                    | $\Delta V_{CC}$                    | I <sub>LOAD</sub> = 0 to 10 mA        |       |                   | 10   | mV                 |

| EN control                                                                             |                                    |                                       |       |                   |      |                    |

| EN input low voltage                                                                   |                                    |                                       |       |                   | 0.4  | V                  |

| EN input high voltage                                                                  |                                    |                                       | 1.8   |                   |      | V                  |

| EN invest summer                                                                       |                                    | <u>EN</u> = 4 V                       | = 4 V | 4                 |      | μА                 |

| EN input current                                                                       | I <sub>EN</sub>                    | <u>EN</u> = 0 V                       |       | 0.2               |      |                    |

| Timer protection                                                                       |                                    |                                       |       |                   |      |                    |

| Trickle charge time t <sub>1</sub>                                                     | t <sub>Trickle_tmr</sub>           | C <sub>TMR</sub> = 0.47 μF            |       | 30                |      | Mins               |

|                                                                                        | t <sub>Total_tmr</sub>             | C <sub>TMR</sub> = 0.47 μF            |       | 165               |      | IVIIIIS            |

| NTC protection                                                                         |                                    |                                       |       |                   |      |                    |

| NTC low temp rising threshold                                                          |                                    | R <sub>NTC</sub> = NCP18 x 103, 0°C   | 72    | 73.3              | 74.6 |                    |

| NTC low temp rising threshold hysteresis                                               |                                    | K <sub>NTC</sub> - NOP 10 X 103, 0 C  |       | 2                 |      | %V <sub>cc</sub>   |

| NTC high temp falling threshold                                                        |                                    | R <sub>NTC</sub> = NCP18 x 103, 50°C  | 28    | 29.3              | 30.6 |                    |

| NTC low temp falling threshold hysteresis                                              |                                    | R <sub>NTC</sub> - NCP 16 X 103, 50 C |       | 2                 |      |                    |

| Thermal protection                                                                     |                                    |                                       |       |                   |      |                    |

| Thermal shutdown <sup>(5)</sup>                                                        | T <sub>SHDN</sub>                  |                                       |       | 150               |      | °C                 |

| Thermal shutdown hysteresis <sup>(5)</sup>                                             |                                    |                                       |       | 20                |      | °C                 |

| Reverse leakage blocking                                                               |                                    |                                       |       |                   |      |                    |

| Rattery reverse leakage                                                                |                                    | V <sub>CELL</sub> = 0 V               |       |                   | 3    | μA                 |

| current                                                                                | I <sub>LEAKAGE</sub>               | V <sub>CELL</sub> = 4 V               |       |                   | 0.5  | μA                 |

### NOTES:

<sup>5)</sup> Guaranteed by design.

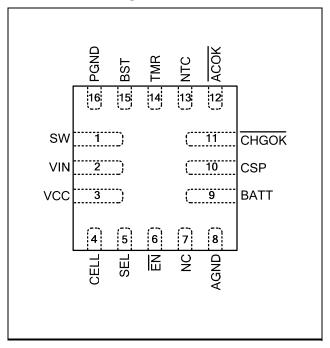

### **PIN FUNCTIONS**

| Package<br>Pin # | Name  | Description                                                                                                                                                                                                             |

|------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | SW    | Switch output.                                                                                                                                                                                                          |

| 2                | VIN   | Power supply voltage.                                                                                                                                                                                                   |

| 3                | VCC   | Coarse regulator output. Internally generated 4.5 V. Bypass with a 1 $\mu$ F capacitor to AGND. Used as low-side switch driver and pull-up bias voltage NTC resistivor divider. Do NOT connect an external load to VCC. |

| 4                | CELL  | <b>Command input for the number of li-ion cells.</b> Connect CELL to VCC for 1-cell application; short CELL to AGND for 2-cell application.                                                                             |

| 5                | SEL   | Input pin for setting terminal battery voltage:  SEL = Low-level: V <sub>BATT</sub> = 4.35 V/cell.  SEL = High-level: V <sub>BATT</sub> = 4.2 V/cell.                                                                   |

| 6                | EN    | On/off control input.  EN is pulled to GND with a 1 M internal resistor.                                                                                                                                                |

| 7                | NC    | No connection. Please leave NC floating.                                                                                                                                                                                |

| 8                | AGND  | Analog ground.                                                                                                                                                                                                          |

| 9                | BATT  | Positive battery terminal.                                                                                                                                                                                              |

| 10               | CSP   | Battery current sense positive input. Connect a resistor (RS1) between CSP and BATT.                                                                                                                                    |

| 11               | CHGOK | <b>Charging complete indicator</b> . A logic low indicates a charging operation. CHGOK will become an open drain once the charge is completed or suspended.                                                             |

| 12               | ACOK  | <b>Valid input supply indicator.</b> A logic low on $\overline{ACOK}$ indicates the presence of a valid input power supply.                                                                                             |

| 13               | NTC   | <b>Thermistor input.</b> Connect a resistor from NTC to VCC and the thermistor from NTC to ground.                                                                                                                      |

| 14               | TMR   | <b>Internal safety timer control.</b> Connect a capacitor from this node to AGND to set the timer. The timer can be disabled by connecting TMR to AGND directly.                                                        |

| 15               | BST   | <b>Bootstrap</b> . A capacitor is needed to drive the power switch's gate above the supply voltage. It is connected between SW and BST to form a floating supply across the power switch driver.                        |

| 16               | PGND  | Power ground.                                                                                                                                                                                                           |

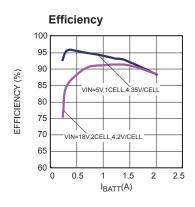

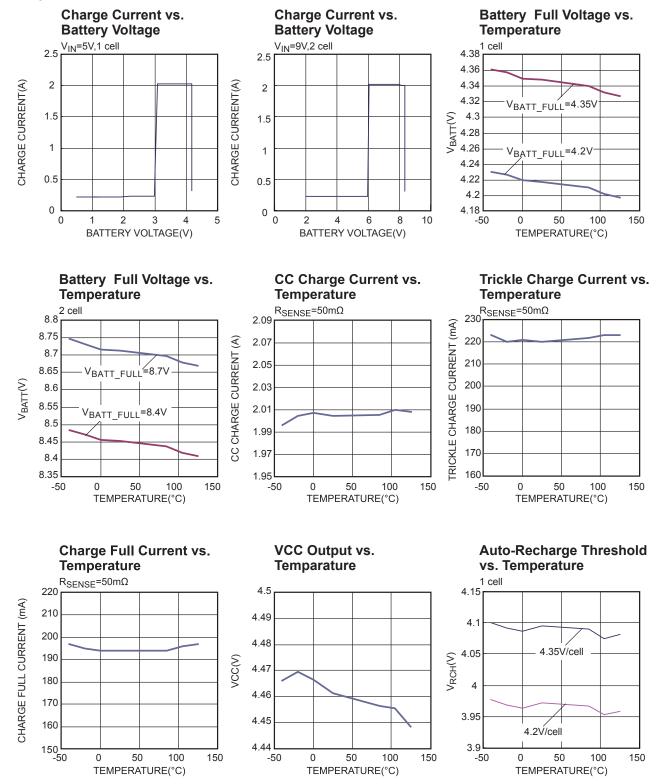

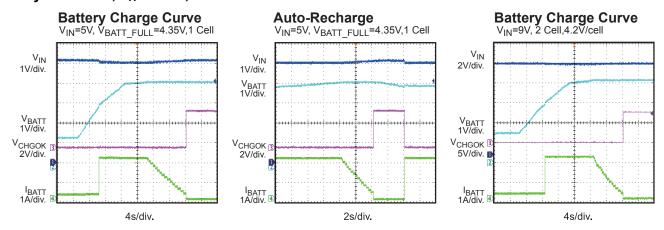

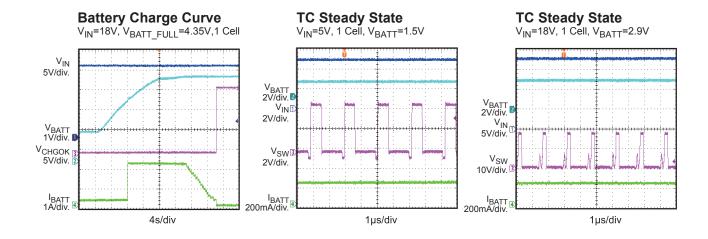

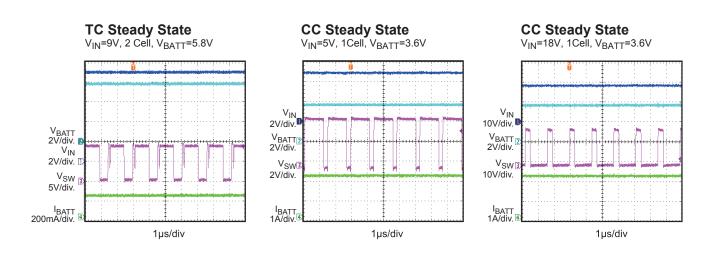

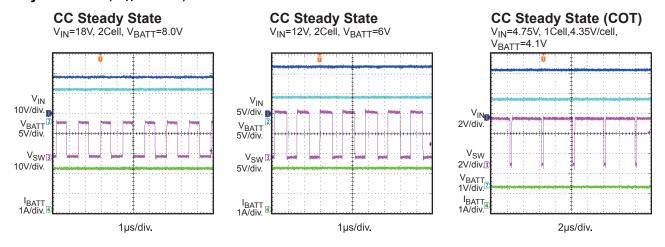

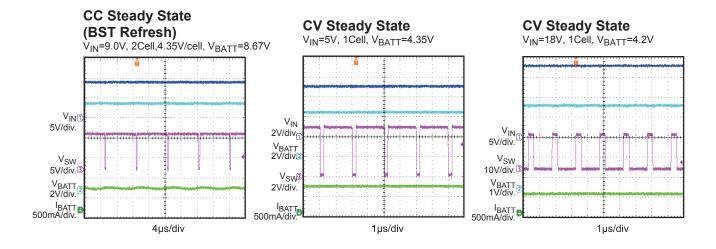

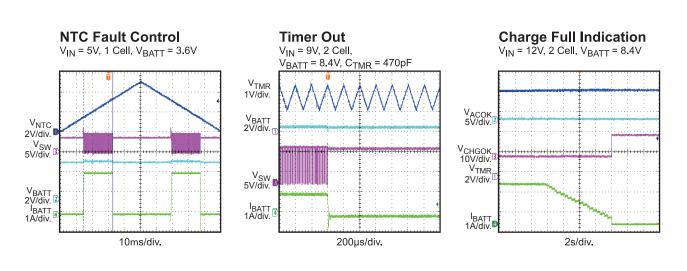

### TYPICAL PERFORMANCE CHARACTERISTICS

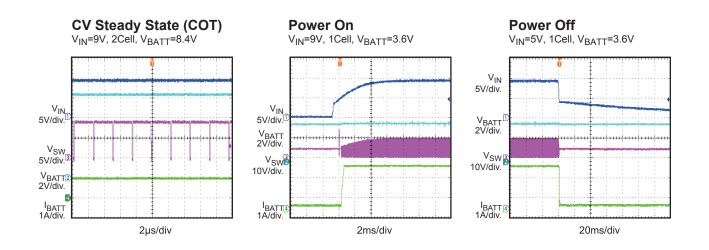

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

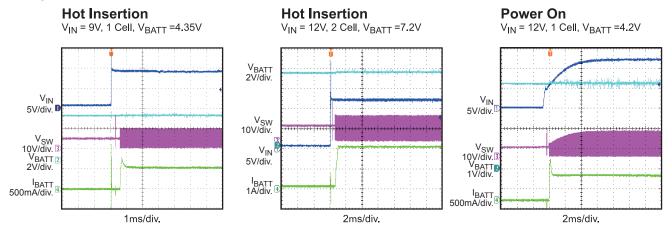

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

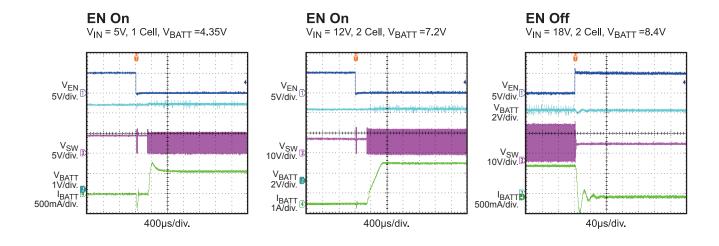

### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

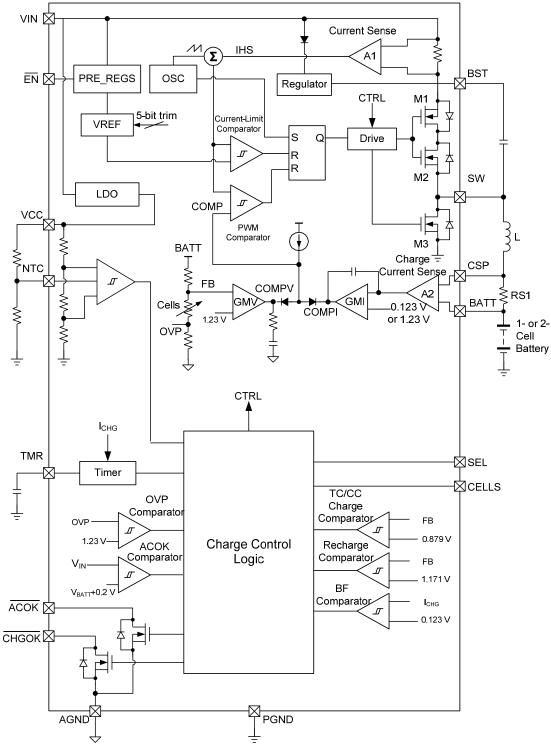

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1—Functional block diagram

### **OPERATION**

The MP2615A is a peak current mode controlled switching charger for 1- or 2- cell lithium-ion and lithium-polymer batteries. The MP2615A integrates both the high-side and low-side switches of the synchronous buck converter to provide high efficiency and save space on the PCB.

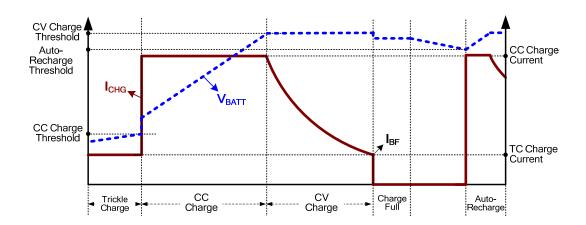

### Charge Cycle (Mode Change: TC→ CC→ CV)

The MP2615A regulates the charge current ( $I_{CHG}$ ) and battery voltage ( $V_{BATT}$ ) using two control loops. This achieves highly-accurate constant current (CC) charge and constant voltage (CV) charge.

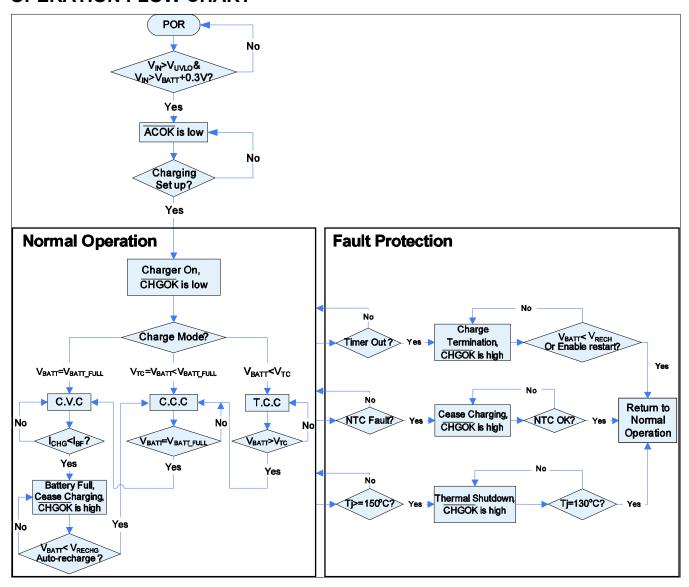

As shown in Figure 2, when the  $V_{BATT} < V_{TC}$ , the MP2615A stays in trickle-charge mode, and the output of the charge current loop (COMPI) dominates the control. The battery is charged by

a trickle-charge current ( $I_{TC}$ ) until the battery voltage reaches  $V_{TC}$ . If the charger stays in the trickle-charge mode until the trickle-charge timer is triggered, charging will be terminated.

The MP2615A enters constant-current charge mode once the battery voltage rises higher than  $V_{TC}$ . In this mode, the charge current increases from  $I_{TC}$  to  $I_{CC}$  to fast charge the battery.

When the battery voltage rises over the full battery voltage ( $V_{BATT\_FULL}$ ), the charger enters constant-voltage mode. In constant-voltage mode, the battery voltage is regulated at  $V_{BATT\_FULL}$  precisely, and the charge current decreases naturally due to the existing equivalent internal resistance of the battery. For the operation flow chart, please refer to Figure 4.

Figure 2—Li-ion battery charge profile

### **Charge Full Termination and Auto-Recharge**

When the charge current drops below the termination threshold ( $I_{BF}$ ) during the CV charge phase, the charger stops charging and  $\overline{CHGOK}$  becomes an open drain. Also, the timer is re-set and turns off. Once the battery voltage decreases below the recharge threshold ( $V_{RECH}$ ), recharging kicks in automatically, and the timer re-starts a new charge cycle.

### **COT Charge Mode**

The MP2615A uses the floating ground method to drive the high-side MOSFET (HS-FET) of the buck converter. During the HS-FET off time, the BST capacitor is recharged, and the voltage across the BST capacitor is used as the HS-FET gate drive. Thus a minimum off-time (200ns) is required to maintain sufficient voltage at the BST capacitor.

When the 200ns minimum off-time is achieved, due to a large duty cycle, the MP2615A enters constant off-time (COT) charge mode. In this mode of operation, the switching frequency is decreased slightly in order to achieve a 99% duty cycle.

### **Charge Status Indication**

Table 1—Charging status indication

| ACOK      | CHGOK             | Charger Status                                                |

|-----------|-------------------|---------------------------------------------------------------|

| Low       | Low               | In charging                                                   |

| Low       | High<br>impedance | End of charge NTC fault Timer out EN disable Thermal shutdown |

| High      | High              | V <sub>IN</sub> absent                                        |

| impedance | impedance         | $V_{IN} - V_{BATT} < 0.3 V$                                   |

### **Safety Timer Operation**

The MP2615A has an internal safety timer to terminate charging during time out. The capacitor ( $C_{\mathsf{TMR}}$ ) connected between TMR and GND is used to set the internal oscillator period. See Equation (1):

$$T_P(\text{seconds}) = 0.46 \times C_{TMR}(uF)$$

(1)

This timer limits the maxium trickle charge time to 8192 internal oscillating periods. If the charger stays in trickle-charge mode for longer than the maximum oscillating periods, it is terminated. CHGOK becomes an open drain to indicate the timer-out fault. If the charge cycle goes through the trickle charge successfully within the allowed time limit, it enters CC charge mode, and the timer continues to count the oscillating periods. When the battery is fully charged, the timer turns off and clears the counter, waiting for the autorecharge to re-start.

If the charge time during the CC/CV modes exceed 49152 oscillating periods, and the *battery full* has not been qualified, the charger is terminated, and a timer-out fault is indicated by floating  $\overline{\text{CHGOK}}$ . The charger exits the timer-out fault state, and the on-chip safety timer re-starts counting when the following conditions occur:

- The battery voltage falls below the autorecharge threshold (V<sub>RECH</sub>);

- a power-on-reset (POR) event occurs;

- EN is toggled.

The timer can be disabled by pulling TMR to AGND.

Thus, the trickle mode charge time is calculated using Equation (2):

$$t_{\text{Trickle\_tmr}}(\text{minutes}) = 62.8 \times C_{\text{TMR}}(\text{uF})$$

(2)

If a  $C_{\mathsf{TMR}}$  (0.47uF) is connected, the trickle charge time is about 30 minutes.

The CC/CV mode charge time is calculated with Equation (3):

$$t_{Total\_tmr}(hours) = 6.28 \times C_{TMR}(uF)$$

(3)

If a  $C_{TMR}$  (0.47 uF) is connected, the CC/CV charge time is 2.95 hours.

## Negative Thermal Coefficient (NTC) Thermistor

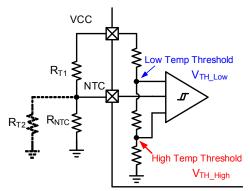

NTC allows the MP2615A to sense the battery temperature using an negative thermal coefficient (NTC) resistor. This resistor is available in the battery pack to ensure a safe operating environment for the battery. A resistor with an appropriate value should be connected from VCC to NTC, and the thermistor should be connected from NTC to AGND. The voltage on NTC is determined by the resistor divider whose divideratio depends on the battery temperature. When the voltage at NTC falls out of the NTC window range, the charging will pause until the battery temperature goes back to normal operating conditions.

As a result, the MP2615A stops charging and reports this condition to the status pins. Charging resumes automatically after the temperature falls back within safe range.

### **Short-Circuit Protection**

The MP2615A has an internal comparator to check for a battery short circuit. Once  $V_{BATT}$  falls below 2 V, the device detects a battery-short status, and the cycle-by-cycle peak current limit falls to about 2.2 A to limit the current spike during the battery-short transition. Also, the switching frequency folds back to minimize the power loss.

### Thermal Shutdown Protection (TSD)

To prevent the chip from overheating during charging, the MP2615A monitors the junction temperature ( $T_J$ ), of the die. Once  $T_J$  reaches the thermal shutdown threshold ( $T_{SHTDWN}$ ) of 150°C, the charger converter turns off. Once  $T_J$  falls below 130°C the charging re-starts.

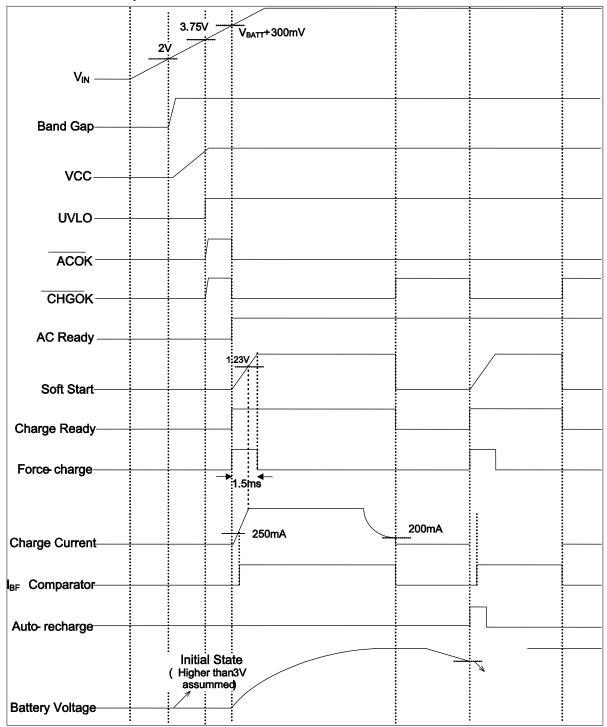

## INPUT POWER-UP, START-UP TIMING FLOW

Figure 3—Input power start-up timing diagram

### **OPERATION FLOW CHART**

Figure 4—Operation flow chart

### APPLICATION INFORMATION

### COMPONENT SELECTION

### **Charge Current Setting**

The constant charge current ( $I_{CC}$ ) of the MP2615A can be set by the sense resistor RS1 (see Typical Application). The equation to determine the programmable CC charge current is expressed in Equation (4):

$$I_{CC} = \frac{100mV}{RS1(m\Omega)}(A)$$

(4)

To get 2 A  $I_{\text{CC}},$  a RS1 of 50  $m\Omega$  should be selected.

Accordingly, the trickle-charge current ( $I_{TC}$ ) can be obtained using Equation (5):

$$I_{TC} = 10\%I_{CC} = \frac{10mV}{RS1(m\Omega)}(A)$$

(5)

### **Inductor Selection**

To select the right inductor, a trade off should be made between cost, size, and efficiency. An inductor with a lower inductance corresponds with smaller size, but it results in higher ripple currents, higher magnetic hysteretic losses. and higher output capacitances. Conversely, a higher inductance value is beneficial to getting a lower ripple current and smaller output filter capacitors. However, this results in higher inductor DC resistance (DCR) loss. Based on practical experience, the inductor ripple current should not exceed 30% of the maximum charge current under worst cases. For the MP2615A with a typical 12 V input voltage to charge a 2-cell battery, the maximum inductor current ripple occurs at the corner point between the trickle charge and the CC  $(V_{BATT} = 6 V)$ . Inductance estimations are calculated with Equation (6):

$$L = \frac{V_{IN} - V_{BATT}}{\Delta I_{L MAX}} \frac{V_{BATT}}{V_{IN} \cdot f_{S}}$$

(6)

Where  $V_{IN}$ ,  $V_{BATT}$ , and  $f_S$  are the typical input voltage, the CC charge threshold, and the switching frequency, respectively. And  $\Delta I_{L\_MAX}$  is the maximum inductor ripple current, which is usually 30% of the CC charge current. See Equation (7):

$$\Delta I_{L MAX} = 30\% I_{CC} \tag{7}$$

Based on the condition where  $I_{CC}=2$  A,  $V_{IN}=12$  V,  $V_{BATT}=6$  V, and  $f_s=760$  kHz, the calculated inductance is 6.6  $\mu$ H. The inductor saturation current must exceed at least 2.6 A and have some tolerance. To optimize efficiency, chose an inductor with a DC resistance less than 50 m $\Omega$ .

### **NTC Resistor Divider Selection**

Figure 5 shows that an internal resistor divider is used to set the low temperature threshold at  $29.3\% \cdot VCC$  and the high temperature threshold at  $73.3\% \cdot VCC$ , respectively. For a given NTC thermistor, select the appropriate  $R_{T1}$  and  $R_{T2}$  to set the NTC window.

Figure 5—NTC function block

The thermistor (NCP18XH103) noted above has the following electrical characteristics:

- At 0°C,  $R_{NTC Cold} = 27.445 k\Omega$ ;

- At 50°C,  $R_{NTC \text{ Hot}} = 4.1601 \text{k}\Omega$ .

Equation (8) and Equation (9) are derived assuming that the NTC window is between 0°C and 50°C:

$$\frac{R_{T2}//R_{NTC\_Cold}}{R_{T1} + R_{T2}//R_{NTC\_Cold}} = \frac{V_{TH\_Low}}{VREF33} = 73.3\%$$

(8)

$$\frac{R_{T2}//R_{NTC\_Hot}}{R_{T1} + R_{T2}//R_{NTC\_Hot}} = \frac{V_{TH\_High}}{VREF33} = 29.3\%$$

(9)

Calculate  $R_{T1}$  and  $R_{T2}$  according to Equation (8) and Equation (9) and the required battery temperature range.

### **Input Capacitor Selection**

The input capacitor C1 from the typical application circuit absorbs the maximum ripple current from the buck converter, which is given by Equation (10):

$$I_{RMS\_MAX} = I_{CC} \frac{\sqrt{V_{TC}(V_{IN\_MAX} - V_{TC})}}{V_{IN\_MAX}}$$

(10)

For a given  $I_{CC}$  = 2 A, and  $V_{TC}$  = 6 V when  $V_{IN\_MAX}$  = 12 V (the duty is 0.5), the maximum ripple current is 1 A. Select the input capacitors so that the temperature rise due to the ripple current does not exceed 10°C. Use ceramic capacitors with X5R or X7R dielectrics because of their low ESR and small temperature coefficients. For most applications, use a 22  $\mu$ F capacitor. A small, high-quality ceramic capacitor (i.e. 1.0  $\mu$ F) should be placed as close to the IC as possible from VIN to PGND.

### **Output Capacitor Selection**

The output capacitor C2 (see the typical application circuit) is in parallel with the battery. C2 absorbs the high-frequency switching ripple current and smoothes the output voltage. Its impedance must be much less than that of the battery to ensure it absorbs the ripple current. Use a ceramic capacitor because it has a lower ESR and smaller size. The output voltage ripple is given by Equation (11):

$$\Delta r_{O} = \frac{\Delta V_{O}}{V_{O}} = \frac{1 - \frac{V_{O}}{V_{IN}}}{8C_{O}f_{S}^{2}L}$$

(11)

In order to guarantee  $\pm 0.5\%$  full battery voltage accuracy, the maximum output voltage ripple must not exceed 0.5% (e.g., 0.1%). The maximum output voltage ripple occurs at the minimum battery voltage of the CC charge and the maximum input voltage.

For  $V_{IN\_MAX}$  = 18 V,  $V_{CC\_MIN}$  =  $V_{TC}$  =6 V, L = 6.8  $\mu$ H,  $f_S$  = 760 kHz,  $\Delta r_{O\_MAX}$  = 0.1%, the output capacitor can be calculated using Equation (12):

$$C_{O} = \frac{1 - \frac{V_{TC}}{V_{IN\_MAX}}}{8f_{s}^{2}L\Delta r_{OMAX}} = 21.3\mu F$$

(12)

We can then approximate this value and choose a 22  $\mu$ F ceramic capacitor.

### **PCB Layout Guidelines**

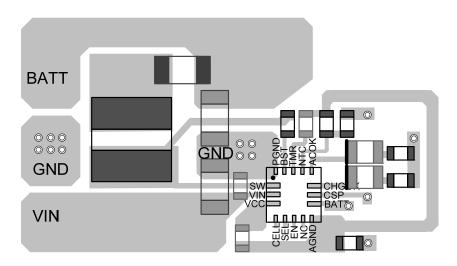

Efficient PCB layout is critical to meet specified noise, efficiency, and stability requirements. For optimum performance, refer to Figure 6 and follow the design considerations below:

- Route the power stage adjacent to the grounds. Aim to minimize the high-side switching node (SW, inductor), trace lengths in the high-current paths, and the current-sense resistor trace. Keep the switching node short and far away from the feedback network.

- Connect the charge current-sense resistor to CSP (pin 10) and BATT (pin 9). Minimize the length and area of this circuit loop.

- 3) Place the input capacitor as close as possible to VIN and PGND. Place the output inductor close to the IC and connect the output capacitor between the inductor and PGND of the IC. This minimizes the current path loop area from SW through the LC filter and back to PGND.

- Connect AGND and PGND at a single point.

Figure 6—Recommneded PCB layout

### **TYPICAL APPLICATION CIRCUITS**

Figure 7—Typical application circuit to charge a 2-cell battery with 12 V<sub>IN</sub>.

### PACKAGE INFORMATION

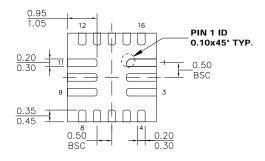

### QFN-16 (3mm x 3mm)

### **TOP VIEW**

**BOTTOM VIEW**

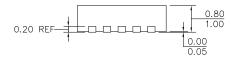

### **SIDE VIEW**

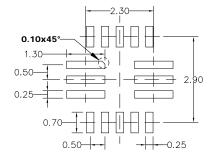

## RECOMMENDED LAND PATTERN

### **NOTE:**

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETERS MAX.

- 4) JEDEC REFERENCE IS MO-220.

- 5) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

## 单击下面可查看定价,库存,交付和生命周期等信息

## >>MPS(芯源系统)