### Non-Crack-Noise, Ultra-Low-EMI, 3W, Mono, Filter-Free, Class-D Audio Amplifier

### **Features**

- NCN Function Protects the Speaker

- EEE Function, Greatly reduces EMI over the full bandwidth

- Excellent Pop-Click Suppression

- 3W into 3Ω (10% THD+N,V<sub>DD</sub>=5V)

- 0.04%THD+N (Pout=1W,V<sub>DD</sub>=5V)

- Filter-Free Class-D Architecture

- Up to 90% Efficiency

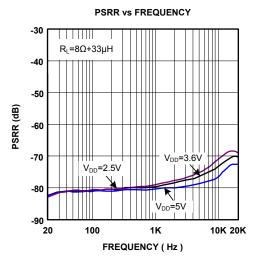

- High PSRR (-80dB at 217Hz)

- Low Quiescent Current (2.8mA)

- Low Shutdown Current (<0.1μÅ)</li>

- Power Supply Range: 2.5V~5.5V

- Over-Current Protection

- Over-Temperature Protection

- Undervoltage Protection

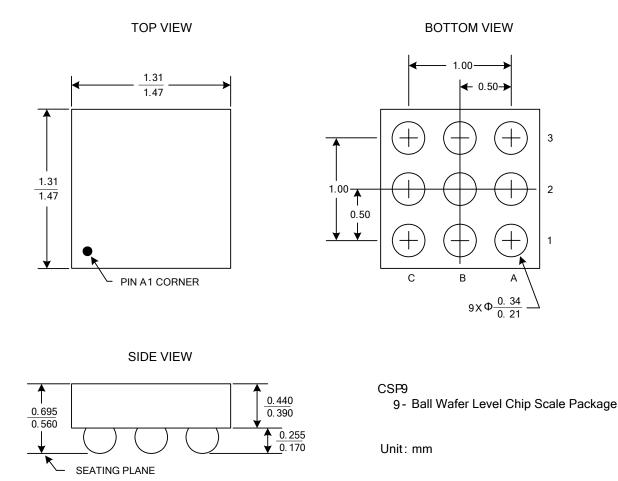

- Small 1.45mm×1.45mm CSP9 Package

- RoHS compliant, lead-free packages

### **Applications**

- Cellular Phones

- MP3/PMP

- GPS

- Digital Photo Frame

### Pin Configuration and Top Mark

#### AW8110CSR TOP VIEW AW8110CSR MARKING з 3 VON ) ( GND ) VOP 8110 (PVDD) SHUTDOW 2 2 GND ) XΥ (INN) (AVDD) INP ) в С в С 8110 - AW8110CSR XY - Manufacture Data Code

#### Figure 1 Pin Configuration and Top Mark of AW8110

COPYRIGHT ©2009 SHANGHAI AWINIC TECHNOLOGY CO., LTD. Page 1 of 14

### **General Description**

The AW8110 is a Non-Crack-Noise (NCN), Ultra-Low-EMI, filter-free, 3W, mono, Class-D audio amplifier. Unique NCN function, which adjusts the system gain automatically while detecting the "Crack" distortion of output signal, protects the speaker from damage at high power levels and brings the most comfortable listening experience to the customers.

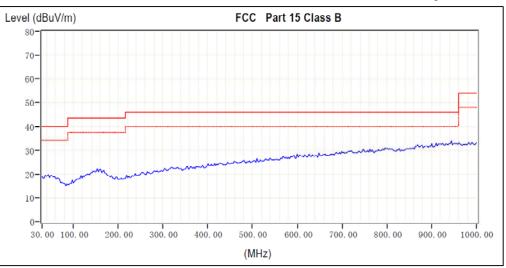

The AW8110 features the EEE (Enhanced Emission Elimination) function which greatly reduces EMI over the full bandwidth. The AW8110 achieves better than 20dB margin under FCC limits with 24 inch of cable.

The filter-free PWM architecture and internal gain setting reduces external components count, board area consumption, system cost and simplifies the design. In addition, The AW8110 offers efficiencies above 90%. The over-current, over-temperature and under-voltage protection is prepared inside of the device.

The AW8110 is available in an ultra small 1.45mm×1.45mm CSP9 package. The AW8110 is specified over the industrial temperature range of -40 $^{\circ}$ C to +85 $^{\circ}$ C.

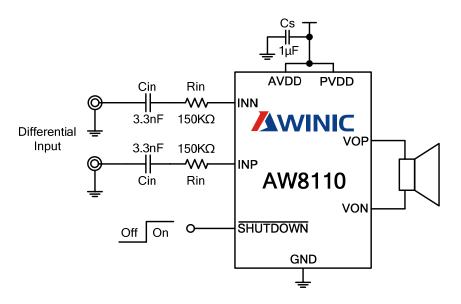

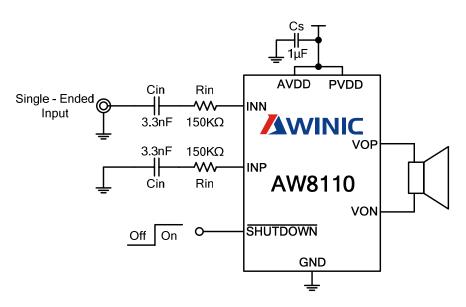

## **Typical Application**

Figure 2 AW8110 Application Schematic With Differential Input

Figure 3 AW8110 Application Schematic With Single-Ended Input

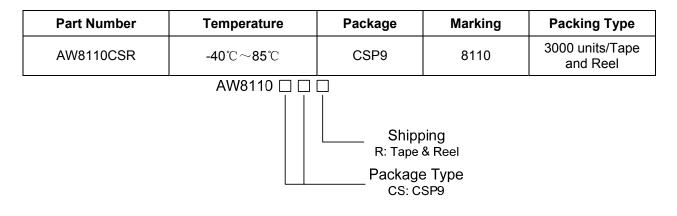

### **Ordering Information**

### Absolute Maximum Ratings(1)

| Parameter                                           | Unit                           |  |  |  |

|-----------------------------------------------------|--------------------------------|--|--|--|

| Supply voltage V <sub>DD</sub>                      | -0.3V to 6V                    |  |  |  |

| Input Voltage                                       | -0.3V to V <sub>DD</sub> +0.3V |  |  |  |

| Package Thermal Resistance $\theta_{JA}(2)$         | 90°C/W                         |  |  |  |

| Operating free-air temperature                      | -40℃ to 85℃                    |  |  |  |

| Maximum Junction Temperature T <sub>JMAX</sub>      | <b>125</b> ℃                   |  |  |  |

| Storage Temperature Range T <sub>STG</sub>          | -65℃ to 150℃                   |  |  |  |

| Lead Temperature (Soldering 10 Seconds)             | <b>260</b> ℃                   |  |  |  |

| ESD Rating(3)                                       |                                |  |  |  |

| HBM(human body model)                               | ±8KV                           |  |  |  |

| Latch-up                                            |                                |  |  |  |

| Test Condition :JEDEC STANDARD NO.78B DECEMBER 2008 | +IT:450mA<br>-IT:-450mA        |  |  |  |

**note1:** Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

**note2:** For the 9-Pin Flip-Chip CSP package, the  $\theta_{JA}$  is highly dependent of the PCB Heatsink area. For example,  $\theta_{JA}$  can equal 195°C/W with 50 mm2 total area and also 135°C/W with 500 mm2. When using ground and power planes, the value is around 90°C/W, as specified in table.

**note3:** The human body model is a 100pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin. Test method: MIL-STD-883G Method 3015.7.

### **Electrical Characteristics**

Test Condition:  $T_A=25^{\circ}C$  (Unless otherwise specified)

|                          | Parameter                            | Conditions                                                         | Min Typ               | Мах  | Units |

|--------------------------|--------------------------------------|--------------------------------------------------------------------|-----------------------|------|-------|

| Electric                 | al Characteristics                   |                                                                    |                       |      | 1     |

| VDD                      | Power voltage                        |                                                                    | 2.5                   | 5.5  | V     |

| VIH                      | High-level input voltage             |                                                                    | 1.3                   |      |       |

| VIL                      | Low-level input voltage              |                                                                    |                       | 0.35 |       |

| V <sub>os</sub>          | Output offset voltage                | $V_{IN}$ =0V,A <sub>V</sub> =3V/V,V <sub>DD</sub> =2.5V to 5.5V    | 5                     | 25   | mV    |

| Ι <sub>Q</sub>           | Quiescent current                    | V <sub>DD</sub> =3.6V                                              | 2.8                   |      | mA    |

| $I_{SD}$                 | Shutdown current                     | V <sub>DD</sub> =3.6V, SHUTDOWN =0V                                | 0.1                   |      | μA    |

| PSRR                     | Power supply rejection ratio         | 217Hz                                                              | -80                   |      | dB    |

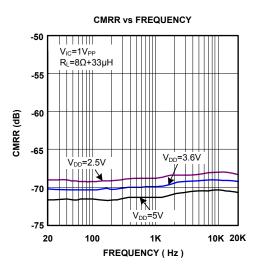

| CMRR                     | Common mode rejection ratio          |                                                                    | -70                   |      | dB    |

| $\mathbf{f}_{\text{SW}}$ | Switching frequency                  | V <sub>DD</sub> =2.5V to 5.5V                                      | 800                   |      | kHz   |

| Av                       | Gain                                 |                                                                    | <u>3×150kΩ</u><br>Rin |      | V/V   |

|                          | SHUTDOWN pin pull-down res           |                                                                    | 300                   |      | kΩ    |

| Operati                  | ng Characteristics                   |                                                                    |                       |      | 1     |

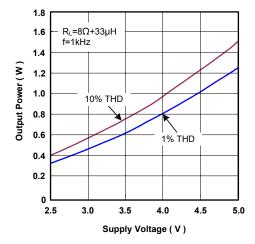

|                          | Output power<br>(NCNOFF mode )       | $R_L=8\Omega$ , THD+N=1%, f=1kHz, $V_{DD}=5V$                      | 1.25                  |      | W     |

|                          |                                      | $R_{L}{=}8\Omega, \ THD{+}N{=}1\%, \ f{=}1kHz, \ V_{DD}{=}4.2V$    | 0.85                  |      | W     |

|                          |                                      | $R_L=8\Omega$ , THD+N=10%, f=1kHz, $V_{DD}=5V$                     | 1.5                   |      | W     |

|                          |                                      | $R_{L}{=}8\Omega, \ THD{+}N{=}10\%, \ f{=}1kHz, \ V_{DD}{=}4.2V$   | 1.05                  |      | W     |

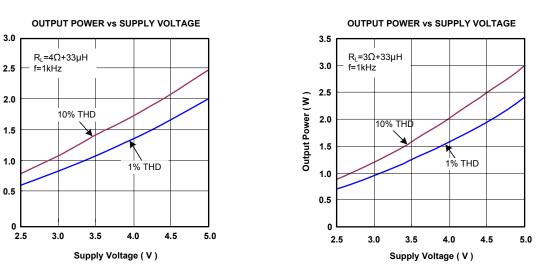

| Po                       |                                      | $R_L=4\Omega$ , THD+N=1%, f=1kHz, $V_{DD}=5V$                      | 2.0                   |      | W     |

|                          |                                      | $R_L=4\Omega$ , THD+N=1%, f=1kHz, $V_{DD}=4.2V$                    | 1.45                  |      | W     |

|                          |                                      | $R_L$ =4 $\Omega$ , THD+N=10%, f=1kHz, V <sub>DD</sub> =5V         | 2.45                  |      | W     |

|                          |                                      | $R_L\text{=}4\Omega, \text{ THD+N=10\%, f=1kHz, V}_DD\text{=}4.2V$ | 1.8                   |      | W     |

|                          |                                      | $R_L=3\Omega$ , THD+N=1%, f=1kHz, $V_{DD}=5V$                      | 2.4                   |      | W     |

|                          |                                      | $R_L=3\Omega$ , THD+N=1%, f=1kHz, $V_{DD}=4.2V$                    | 1.7                   |      | W     |

|                          |                                      | $R_L=3\Omega$ , THD+N=10%, f=1kHz, $V_{DD}=5V$                     | 3.0                   |      | W     |

|                          |                                      | $R_L$ =3 $\Omega$ , THD+N=10%, f=1kHz, V <sub>DD</sub> =4.2V       | 2.2                   |      | W     |

|                          | Total harmonic distortion plus noise | V <sub>DD</sub> =5V,Po=0.5W,R <sub>L</sub> =8Ω,f=1kHz              | 0.04                  |      | %     |

| THD+N                    |                                      | $V_{DD}$ =5V,Po=1W,R <sub>L</sub> =4 $\Omega$ ,f=1kHz              | 0.04                  |      | %     |

| η                        | Efficiency                           | VDD=5V,Po=0.8W,R <sub>L</sub> =8Ω,f=1kHz                           | 90                    |      | %     |

| t <sub>st</sub>          | Start-up time                        |                                                                    | 32                    |      | ms    |

| NCN                      |                                      |                                                                    |                       |      |       |

| A <sub>MAX</sub>         | Maximum attenuation gain             |                                                                    | -10                   |      | dB    |

#### **Pin Definition**

| No. | Symbol   | Description             |

|-----|----------|-------------------------|

| A1  | INP      | Positive audio input    |

| A2  | GND      | Ground                  |

| A3  | VON      | Negative audio output   |

| B1  | AVDD     | Analog power supply     |

| B2  | PVDD     | Power supply for output |

| B3  | GND      | Ground                  |

| C1  | INN      | Negative audio input    |

| C2  | SHUTDOWN | Shutdown pin            |

| C3  | VOP      | Positive audio output   |

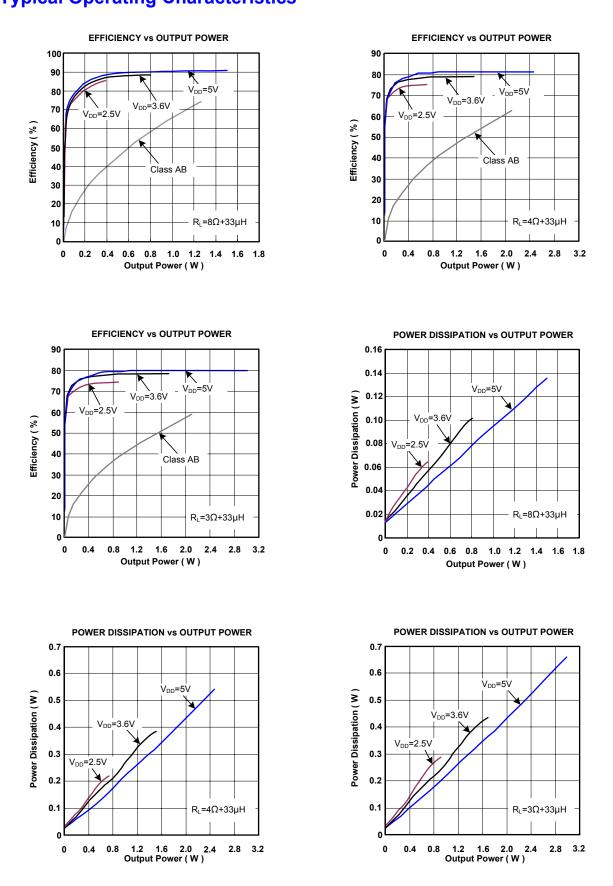

# Typical Operating Characteristics

TECHNOLOG

上海艾为电子技术有限公司

SHANGHAI AWINIC TECHNOLOGY CO., LTD.

COPYRIGHT ©2009 SHANGHAI AWINIC TECHNOLOGY CO., LTD. Page 6 of 14

TECHNOLOGY

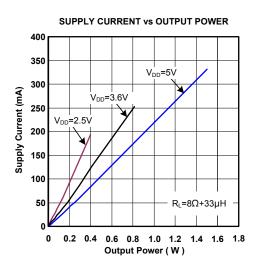

SUPPLY CURRENT vs OUTPUT POWER

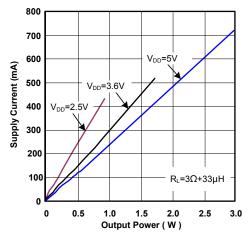

SUPPLY CURRENT vs OUTPUT POWER

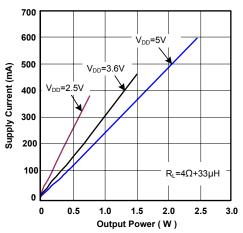

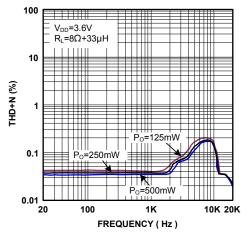

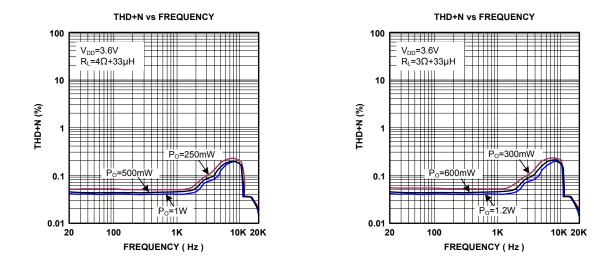

THD+N vs FREQUENCY

COPYRIGHT ©2009 SHANGHAI AWINIC TECHNOLOGY CO., LTD. Page 7 of 14

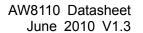

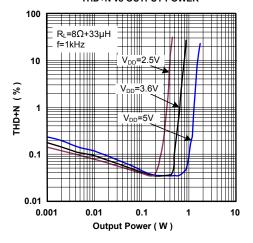

#### THD+N vs OUTPUT POWER

TECHNOLOG

100

10

1

0.1

0.01

Output Power (W)

0.001

(%) N+DHT

RL=3Ω+33µH

0.01

f=1kHz

THD+N vs OUTPUT POWER

V<sub>DD</sub>=2.5V

₿,

1

10

V<sub>DD</sub>=3.6

0.1

Output Power (W)

Ηů

V<sub>DD</sub>=5V

THD+N vs OUTPUT POWER

**OUTPUT POWER vs SUPPLY VOLTAGE**

COPYRIGHT ©2009 SHANGHAI AWINIC TECHNOLOGY CO., LTD. Page 8 of 14

上海艾为电子技术有限公司 SHANGHAI AWINIC TECHNOLOGY CO., LTD.

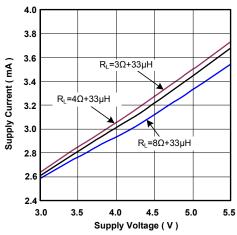

SUPPLY CURRENT vs SUPPLY VOLTAGE

### **Block Diagram**

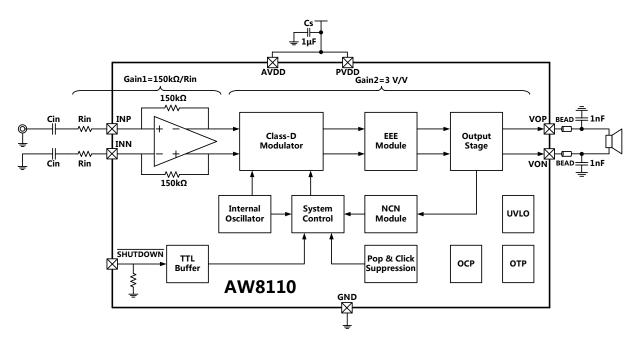

Figure 4 Functional Block Diagram of AW8110

### **Operation**

The AW8110 is a non-crack-noise (NCN), ultra-low-EMI, filter-free, 3W, mono, Class-D audio amplifier. It is capable of delivering 3 W of continuous output power with efficiency of 90% driving a  $3\Omega$  load from a 5.0 V supply. Unique NCN function, which adjusts the system gain automatically while detecting the "Crack" distortion of output signal, protects the speaker from damage at high power levels and brings the most comfortable listening experience to the customers.

The AW8110 features the EEE (Enhanced Emission Elimination) function which greatly reduces EMI over the full bandwidth. The AW8110 achieves better than 20dB margin under FCC limits with 24 inch of cable.

The filter-free PWM architecture and internal gain setting reduces external components count, board area consumption, system cost and simplifies the design. The over-current, over-temperature and undervoltage protection is prepared inside of the device, which prevent the device from damage during fault conditions. When the fault condition is removed, the AW8110 reactivate itself again.

#### **Filter-Free Modulation Scheme**

The AW8110 features a filter-free PWM architecture that reduces the LC filter of the traditional Class-D amplifier, increasing efficiency, reducing board area consumption and system cost.

#### **Pop-Click Suppression**

The AW8110 features unique timing control circuit, that comprehensively suppresses pop-click noise, eliminates audible transients on shutdown, wakeup, and power-up/down

#### **EEE Technology**

The AW8110 features a unique Enhanced Emission Elimination (EEE) technology, that controls fast transition on the output, greatly reduces EMI over the full bandwidth. The AW8110 achieves better than 20dB margin under FCC limits with 24 inch of cable, as shown in Figure 5.

Figure 5 EMI Test Spectrum Diagram

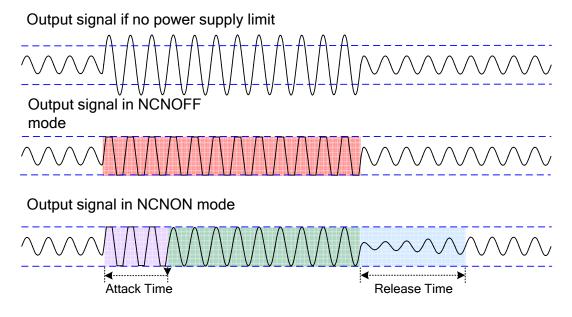

#### **NCN Function**

In audio application, output signal will be undesirable distortion caused by too large input and power supply voltage down with battery, and clipped output signal may cause permanent damage to the speaker. The AW8110 features unique Non-Crack-Noise (NCN) Function, which adjusts system gain automatically to generate desired output by detecting the "Crack" distortion of output signal, protects the speaker from damage at high power levels and brings the most comfortable listening experience to the customers. Attack Time is the time it takes to reduce the gain after the output has clipped.

Release Time is the time it takes for the gain to return to its normal level after clipped.

**Table 1 NCN Parameter**

| Attack Time | Release Time |

|-------------|--------------|

| 45ms        | 2.6s         |

Figure 6 NCN Function Diagram

#### Efficiency

Efficiency of a Class D amplifier is attributed to the switching operation of the output stage transistors. In a Class D amplifier, the output transistors act as current steering switches and consume negligible additional power. Any power loss associated with the Class D output stage is mostly due to the I<sup>2</sup>R loss of the MOSFET on-resistance and supply current. The AW8110 features efficiency of 90%.

#### **Protection Function**

When a short-circuit occurs between VOP/VON pin and VDD/GND or VOP and VON, the over-current circuit shutdown the device, preventing the device from being damaged. When the condition is removed, the AW8110 reactivate itself. When the junction temperature is high, the over-temperature circuit shutdown the device. The circuit switches back to normal operation when the temperature decreases to safe levels. The UVLO circuit will shutdown the device when power supply is low. AW8110 wake-up again when power supply becomes high.

COPYRIGHT ©2009 SHANGHAI AWINIC TECHNOLOGY CO., LTD. Page 12 of 14

### **Applications Information**

#### **Supply Decoupling Capacitor**

The AW8110 is a high-performance class-D audio amplifier that requires adequate power supply decoupling to ensure the efficiency is high and Total Harmonic Distortion (THD) is low. For higher frequency transients, a good low Equivalent-Series-Resistance (ESR) ceramic capacitor, typically 1 $\mu$ F, placed as close as possible to the device VDD pin works best. For filtering lower-frequency noise signals, a 10  $\mu$ F or greater capacitor placed near the audio power amplifier would also help.

#### **Input Resistors**

The input resistors set the gain of the amplifier according to equation as follow.

$$Gain = \frac{3 \times 150 \,\mathrm{k}\Omega}{\mathrm{Rin}} \quad \left(\frac{\mathrm{V}}{\mathrm{V}}\right)$$

The resistor matching is very important. CMRR, PSRR and THD diminish if resistor mismatch occurs. Therefore, it is recommended use 1% tolerance resistors or better to keep the performance optimized. Place the input resistors very close to the AW8110 to limit noise injection on the high-impedance nodes.

#### Input Capacitor

The input coupling capacitor blocks the DC vol-

tage at the amplifier input terminal. The input capacitors and input resistors form a high-pass filter with the corner frequency,  $f_{\rm c.}$

$$f_C = \frac{1}{2\pi RinCin}.$$

Setting the high-pass filter point high can block the 217Hz GSM noise coupled to inputs. Better matching of the input capacitors improves performance of the circuit and also help to suppress pop-click noise.

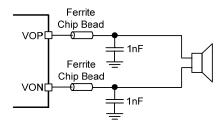

#### Ferrite Chip Bead and Capacitor

The AW8110 passed FCC and CE radiated emissions with no ferrite chip beads and capacitors with speaker trace wires 24 inch. Use ferrite chip beads and capacitors if device near the EMI sensitive circuits and/or there are long leads from amplifier to speaker, placed as close as possible to the output pin.

Figure 7 Ferrite Chip Bead and capacitor

### Package Description

AWINIC Technology cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in an AWINIC Technologies product. No intellectual property or circuit patent licenses are implied. AWINIC Technology reserves the right to change the circuitry and specifications without notice at any time.

单击下面可查看定价,库存,交付和生命周期等信息

>>AWINIC(艾为)