### **Over Voltage and Over Current Protection IC**

### **General Description**

The LP5305A is a highly integrated circuits, it used to protect low voltage system from abnormal high input voltage. The IC continuously check the input voltage, the input current, and the battery voltage. When the protection status is occur, the power MOS will turn off at the same time. The LP5305A is safety devices to ensure worked against accidents.

In case of the input voltage exceeds a OVP threshold voltage level, the power MOS will turn off within 1µs. The current limit can is adjustable by external resistor between ISET and GND. And the current is also limited to prevent charging the battery with an excessive current. The LP5305A also monitors the Li-ion battery voltage, when the battery voltage exceeds 4.35V, the IC will turn off the MOS.

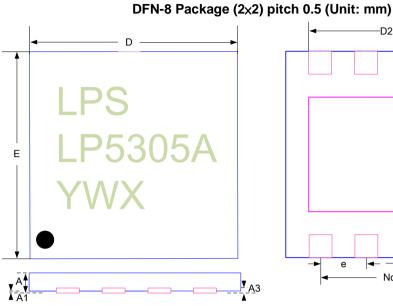

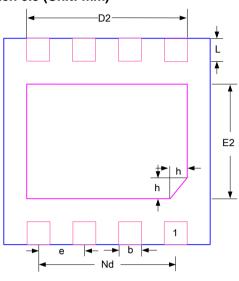

Other features include over temperature protection and under-voltage lockout (UVLO). The LP5305A is available in a space saving DFN-8 package.

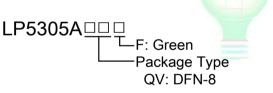

#### **Order Information**

#### **Features**

- Withstand High Input Voltage Up to 26V

- Adjustable Over Current Protection

- Input Over Voltage Protection

- Battery Over Voltage Protection

- High Accuracy Protection Thresholds

- Fault Signal Output

- Enable Control

- Under Voltage Lockout

- Output Short-Circuit Protection

- Over-Temperature Protection

- Available in DFN-8

- RoHS Compliant and Halogen Free

### **Applications**

- ♦ Cell Phones

- Digital Cameras

- ♦ Portable Instruments

#### **Marking Information**

| Device |                                                              | Marking | Package | Shipping |  |

|--------|--------------------------------------------------------------|---------|---------|----------|--|

|        | LP5305A                                                      | LPS     | DFN-8   | 4K/REEL  |  |

|        | 1-42.825                                                     | P5305A  |         |          |  |

|        |                                                              | YWX     |         |          |  |

|        | Y: Y is year code. W: W is week code. X: X is series number. |         |         |          |  |

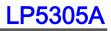

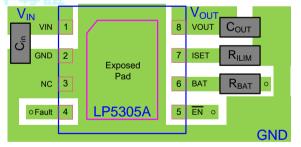

## **Typical Application Circuit**

Figure 1. Typical Application Circuit of LP5305A .

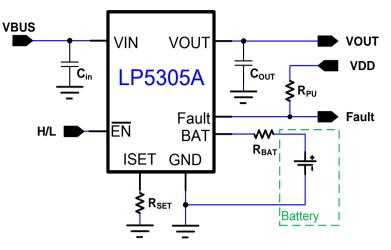

### **Pin Configuration**

Figure 2. Package Top View

### **Function Block Diagram**

Figure 3. Function Block Diagram

### **Functional Pin Description**

| Pin NO. | DFN8 | Description                                                          |  |  |

|---------|------|----------------------------------------------------------------------|--|--|

| VIN     | 1    | Power source input. Connect a ceramic capacitor between VIN and GND. |  |  |

| GND     | 2    | Ground.                                                              |  |  |

| NC      | 3    | No connect.                                                          |  |  |

| Fault   | 4    | Fault output pin. Open-drain output, device status.                  |  |  |

| EN      | 5    | Enable pin.                                                          |  |  |

| BAT     | 6    | Battery voltage detector input.                                      |  |  |

| ISET    | 7    | OCP level setting by an external resistor to GND.                    |  |  |

| VOUT    | 8    | Output through the power MOSFET.                                     |  |  |

|         | EP   | Exposed pad. Connect EP to GND is suggested.                         |  |  |

# Absolute Maximum Ratings Note1

| $\diamond$ | VIN to GND                                             | -0.3V to +30V   |

|------------|--------------------------------------------------------|-----------------|

| ¢          | VOUT to GND                                            | -0.3V to +7V    |

| ¢          | All Other Pin to GND                                   | -0.3V to +7V    |

| ¢          | Operating Junction Temperature Range (T <sub>J</sub> ) | -40°C to 150°C  |

| ¢          | Operation Ambient Temperature Range                    | -40°C to +105°C |

| ¢          | Storage Temperature Range                              | -65°C to +150°C |

| $\diamond$ | Maximum Soldering Temperature (at leads, 10sec)        | +260°C          |

**Note1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Thermal Information**

| Ŷ | Thermal Resistance      |            |

|---|-------------------------|------------|

|   | $DFN-8, \theta_{JA} ~ $ | 76.11 °C/W |

|   | DFN-8, θ <sub>JC</sub>  | 68.46 °C/W |

### **Recommended Operating Conditions**

| $\diamond$ | Input Voltage, V <sub>IN</sub>       | L P Semi     | 3.3V to 5V                   |

|------------|--------------------------------------|--------------|------------------------------|

| $\diamond$ | Output Current, IOUT                 | LowPowerSemi | 0.3A to 1.5A                 |

| $\diamond$ | OCP Set Resistance, R <sub>SET</sub> | 微源半導體        | 15k $\Omega$ to 90k $\Omega$ |

| ♦          | Junction Temperature, T <sub>J</sub> |              | 40°C to 125°C                |

### **Electrical Characteristics**

( $V_{IN} = 5V$ ,  $T_A = 25^{\circ}C$ , Unless Otherwise Specified)

| Parameter                                | Symbol                   | Test Conditions                                                        | Min | Тур   | Max | Units |

|------------------------------------------|--------------------------|------------------------------------------------------------------------|-----|-------|-----|-------|

| General Function                         |                          |                                                                        |     |       |     |       |

| Power Source Voltage                     | VIN                      | T <sub>J</sub> = +25 °C                                                | 3.3 | 5     | 26  | V     |

| Input UVLO Threshold                     | V <sub>UVLO</sub>        | V <sub>IN</sub> Rising                                                 | 2.5 | 2.7   | 2.9 | V     |

| UVLO Threshold Hysteresis                | $\Delta V_{\text{UVLO}}$ | Falling Hysteresis                                                     |     | 200   |     | mV    |

| Power On Deglitch Time                   | T <sub>Deglitch</sub>    |                                                                        |     | 8     |     | ms    |

| Soft Start Time                          | T <sub>SS</sub>          |                                                                        |     | 8.2   |     | ms    |

| Power Source Current                     | lin                      | V <sub>IN</sub> =5V, EN=L                                              |     | 400   |     | μΑ    |

| Shutdown Current                         | I <sub>SD</sub>          | V <sub>IN</sub> =5V, EN=H                                              |     | 55    |     | uA    |

| Thermal Shutdown Threshold               | T <sub>SD</sub>          |                                                                        |     | 140   |     | °C    |

| Thermal Shutdown Threshold<br>Hysteresis | $\Delta T_{SD}$          |                                                                        |     | 20    |     | °C    |

| Logic Function                           |                          |                                                                        | •   |       |     |       |

|                                          | V <sub>ENH</sub>         |                                                                        | 1.4 |       |     | V     |

| EN Threshold Voltage                     | VENL                     |                                                                        |     |       | 0.4 | V     |

| EN Input Resistance to GND               | L Tenemi                 | EN=2V                                                                  |     | 15    |     | uA    |

| FAULT Output Logic Low                   |                          | Sink 5mA                                                               |     | 0.2   |     | V     |

| FAULT Logic High Leakage Current         | Y                        | Fault=5V                                                               |     |       | 10  | uA    |

| Power MOS                                |                          |                                                                        | ·   |       |     |       |

| Switch On Resistance                     | R <sub>DS(ON)</sub>      | I <sub>OUT</sub> =1A                                                   |     | 160   | 250 | mΩ    |

| Regulation Function                      |                          |                                                                        | ·   |       |     |       |

| Output Voltage Regulation                | V <sub>LDO</sub>         | V <sub>IN</sub> =5.7V                                                  |     | 5.1   |     | V     |

| Protection Functions                     |                          |                                                                        | ·   |       |     |       |

| Input Over Voltage Protect threshold     | VIOVP                    | $V_{IN}$ from 5V to 10V                                                |     | 6.8   |     | V     |

| Input OVP threshold Hysteresis           | $\Delta V_{IOVP}$        | $V_{IN}$ from 10V to 5V                                                |     | 100   |     | mV    |

| Input OVP Recovery Delay Time            | Tovpr                    |                                                                        |     | 8.2   |     | ms    |

| Over Current Protection                  | I <sub>OCP</sub>         | R <sub>SET</sub> = 24.9K,<br>3.3V <v<sub>IN<v<sub>IOVP</v<sub></v<sub> |     | 1     |     | А     |

| OCP Blanking Time                        | Тоср                     |                                                                        |     | 200   |     | us    |

| Over Current Recover Delay               | T <sub>OCR</sub>         |                                                                        |     | 65    |     | ms    |

| Battery Voltage OVP                      | VBOVP                    | V <sub>IN</sub> =5V                                                    |     | 4.35  |     | V     |

| Battery OVP Hysteresis                   | ΔV <sub>BOVP</sub>       | V <sub>IN</sub> =5V                                                    |     | 0.275 |     | V     |

| Battery OVP Blanking Time                | T <sub>BOVP</sub>        | V <sub>IN</sub> =5V                                                    |     | 200   |     | us    |

| BAT Pin Leakage Current                  | Іват                     | V <sub>IN</sub> =5V, V <sub>BAT</sub> =4.4V                            |     |       | 10  | nA    |

Email: marketing@lowpowersemi.com www.lowpowersemi.com

#### **Application Information**

The LP5305A devices monitor the input voltage, battery voltage, and output current to protect the charging system of a Li-Ion battery. When enabled, the system is protected against input overvoltage by turning off an internal switch, immediately removing power from the charging circuit. For an over-current condition, the device limits the output current at the setting value, and if the over-current persists, the switch will turn off after a blanking time. Additionally, the device also monitors its own temperature and switches off if device too hot..

#### Under Voltage Lockout (UVLO)

The LP5305A had an UVLO internal circuit that enable the device once the voltage on the  $V_{IN}$  voltage exceeds the UVLO threshold voltage.

#### **Input Over Voltage Protection**

The LP5305A Input has an over voltage protection to protect the battery charging system. When the VIN voltage rises above 5.1V(Typ.), the system will turns the switch off.

#### **Battery Over Voltage Protection**

The battery overvoltage threshold  $V_{BOVP}$  is internally set to 4.35V. If the battery voltage exceeds the threshold, the switch is turned off, and the Fault pin is go low. Once the battery voltage drops to ( $V_{BOVP}$ - $\Delta V_{BOVP}$ ), the switch is turned back on. And the switch is turned off permanently, when battery overvoltage occurs 15 times in one charge cycle. For cleared this event, the VIN power or EN need to re-cycled.

#### **Over Temperature Protection**

The LP5305A device enters over temperature protection(OTP) if its junction temperature exceeds 140°C (Typ.). During over temperature protection none of the device's functions are available. To resume normal operation the junction temperature need cool down, and the outputs will restart.

#### **Enable Control**

The LP5305A has an enable pin which can be used to enable or disable the device. When the EN pin is driven high, the switch is turned off. The EN pin has an internal pull-down resistor can be floating.

#### Fault Flag

The FAULT pin is open-drain output.

- Input Over Voltage

- Output Over Current

- Battery Over Voltage

- Over Temperature

#### **Over Current Protection**

The Over Current threshold can adjustable by a external resistor RSET connected from the ISET pin to GND. The equation is apply under below:

#### I<sub>OCP</sub>=25000÷R<sub>SET</sub>

If the output current exceed the  $I_{OCP}$  threshold, the device limits the current for a blanking duration of  $T_{OC}$ . If the over current situation exceeds the  $T_{OC}$ , the switch will turned off, and the Fault pin is go low. The switch will re-soft start again after  $T_{OCR}$ . And the switch is turned off permanently, when over current event occurs 15 times in one charge cycle. For cleared this event, the VIN power or EN need to re-cycled

#### Layout Consideration

The proper PCB layout and component placement are critical for all circuit. LP5305A is meant to protect downstream circuit. Here are some suggestions to the layout design.

1. Connected all ground together with one uninterrupted ground plane, which include power ground and analog ground.

2. The input and output capacitor should be located as closed as possible to the chip and ground plane.

3. Other components should be located close to the chip.

Figure 4. Recommended PCB Layout Diagram

### **Outline Information**

| SYMBOL  | DIMENSION IN MILLIMETER |        |       |  |  |

|---------|-------------------------|--------|-------|--|--|

| STWIDUL | MIN                     | NOM    | МАХ   |  |  |

| А       | 0.450                   | 0. 500 | 0.550 |  |  |

| A1      | 1īli                    | 0.020  | 0.050 |  |  |

| A3      | 0.180                   | 0.200  | 0.250 |  |  |

| b       | 0.200                   | 0.250  | 0.300 |  |  |

| D       | 1.900                   | 2.000  | 2.100 |  |  |

| D2      | 1.500                   | 1.600  | 1.700 |  |  |

| E       | 1.900                   | 2.000  | 2.100 |  |  |

| E2      | 0.800                   | 0.900  | 1.100 |  |  |

| е       | 0.500 BSC               |        |       |  |  |

| Nd      | 1.500 BSC               |        |       |  |  |

| L       | 0.250                   | 0.300  | 0.350 |  |  |

| h       | 0.150                   | 0.200  | 0.250 |  |  |

单击下面可查看定价,库存,交付和生命周期等信息

>>LOW POWER(微源半导体)